1. Introduction

Power dissipation has assumed greater importance following the advent of portable battery driven devices such as laptops and cell-phones. Increasing a device’s power dissipation invariably results in increasing its temperature and reduces the battery life. The rise in temperature alters the device characteristics, and hence the reliability of the semiconductor device [

1].

Dynamic power dissipation has become a significant concern because of the revolution in transistor scaling. As technology scales down, the channel length decreases, resulting in lower thresholds and supply voltages even though this achieves reliable circuits with less packaging costs. However, downscaling the channel length opens the door to other power dissipation problems, which also affect circuit efficiency [

2]. The decreased die size and the increased number of transistors lead to a rapid increase in the power dissipation. The channel length and oxide thickness downscaling result in increasing the leakage current, and hence the leakage power, which is one form of static power dissipation.

Sources of power dissipation in metal oxide semiconductor (MOS) devices are both static and dynamic. Static power sources include the sub-threshold conduction when the transistor is in the OFF state [

3], the tunneling current through gate oxide, which increases as the gate oxide thickness decreases, and the reverse bias current. The static current is dominated by threshold leakage when the complementary MOS (CMOS) is in weak inversion. Dynamic power dissipation has two main sources, the charging and discharging of the load capacitance (

) and the short circuit effect when both N-Channel MOSFET (NMOS) and P-Channel MOSFET (PMOS) transistors are in saturation.

Several approaches have been proposed in the literature to reduce static and dynamic power dissipation. Some of these approaches aim to reduce power dissipation through targeting the device architecture, which is the main scope of this work, and others have focused on circuit design. To reduce static power dissipation, Anis et al. [

4] suggested using multi-threshold CMOS devices. A low threshold voltage for gate transistors that are in a critical path, and high threshold voltage for gate transistors in a non-critical path. This is due to the fact that sub-threshold conduction, which is one of the main causes of static power dissipation, decreases as the threshold voltage increases. However, this technique suffers from latency and complex fabrication.

Several methods have been used to reduce dynamic power dissipation in both BULK and SOI transistors including reducing the supply voltage

, load capacitance

, and the frequency

[

5]. Another published methodology for reducing dynamic power dissipation at the circuit-level is by clustering a number of gates and making one single large sleep transistor responsible for them [

3]. However, when the structure is unbalanced with complicated interconnections, this methodology is not preferable and sharing one sleep transistor will increase the resistance of the interconnections [

4]. Moreover, the size of the sleep transistor will get larger to compensate for the increased interconnect resistance. Innocenti et al. [

5] suggested decreasing the dynamic power dissipation caused by short circuit effect, using reduced transistor width. This technique reduced the dynamic power dissipation by 20% when the transistor width was reduced by 45%. Furthermore, dynamic power dissipation was reduced by 20% by reducing the voltage supply. However, this technique increases the static power dissipation because decreasing the supply voltage is associated with decreasing the threshold voltage in order to maintain the desired circuit performance.

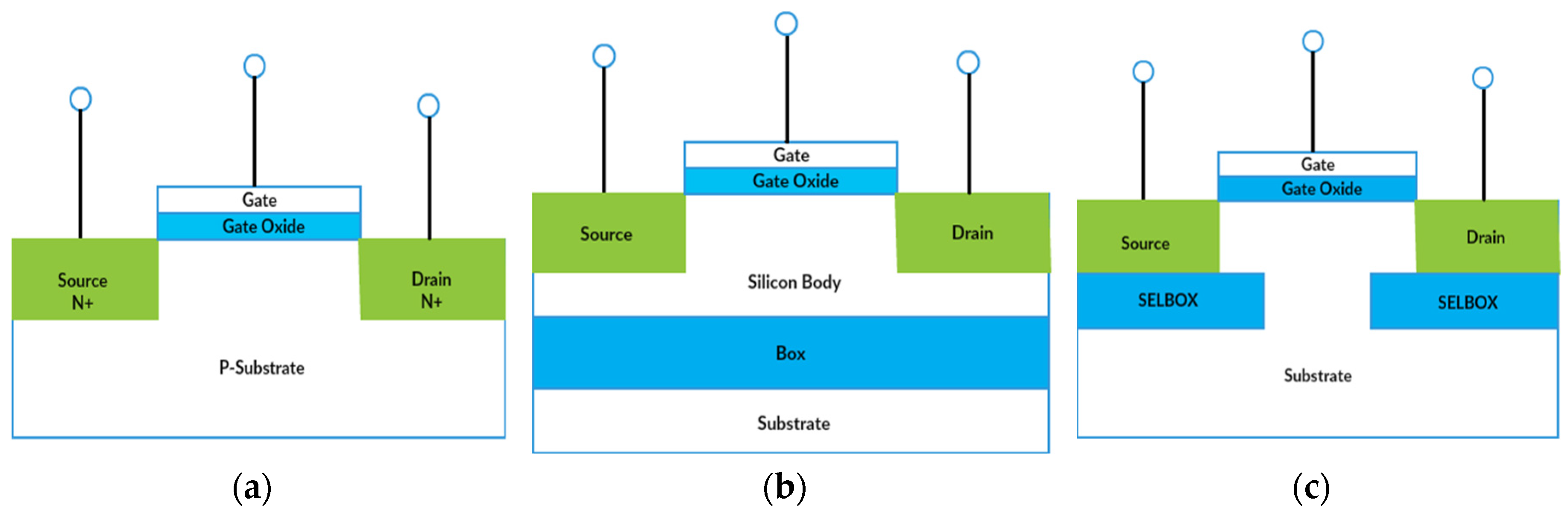

The conventional BULK transistor cross section shown in

Figure 1a has some limitations associated with relatively high power dissipation, short channel effects and low speed due to the device’s internal capacitances. The SOI MOSFET shown in

Figure 1b addresses several of the inherent limitations associated with BULK MOSFET devices. In SOI MOSFET devices, a layer of dielectric such as silicon dioxide is present in the silicon region below the source, drain and channel of the MOSFET. The newly introduced buried layer of oxide and vertical trench oxide electrically isolate the conduction region of the device from the lower substrate. The presence of buried oxide leads to a reduction in the parasitic capacitance leading to an overall improvement in the device performance [

6]. Employment of the oxide layer minimizes the leakage currents and offers latch-up free operation in SOI CMOS devices [

7].

In spite of the superior features of SOI MOSFET devices, the presence of the buried oxide layer leads to several undesirable effects such as the “self-heating effect” and “kink effect” [

8,

9]. The kink effect results from the accumulation of holes generated due to impact ionization at the drain end of the channel region. The device self-heating effect arises due to the poor thermal conductivity of the dielectric oxide layer and the associated temperature rise in the active device region. The kink effect leads to nonlinearity in the device current voltage characteristics. Self-heating leads to device failure if adequate measures are not taken to limit the temperature to safe levels.

The selective back oxide MOSFET (SELBOX MOSFET) was introduced as a remedial measure to minimize the issues associated with SOI MOSFET devices. In SOI MOSFET devices, the buried oxide (BOX) is present all the way from the regions below the source to the drain [

10]. However, in SELBOX MOSFET, the buried oxide is present at selected regions below the source, drain and partially below the channel, as shown in

Figure 1c. This structural modification enables heat transfer from the upper conduction region to the lower substrate and minimizes the problems due to self-heating in SOI MOSFET devices. Furthermore, in the modified structure with its low resistive gap between SELBOX segments, the SELBOX structure is effective in minimizing the rise in the body potential and the non-linearity in the output current voltage characteristics. The authors have conducted a detailed investigation on the SELBOX MOSFET and observed the abilities of the modified structure to reduce self-heating and kink effects [

8,

9,

11].

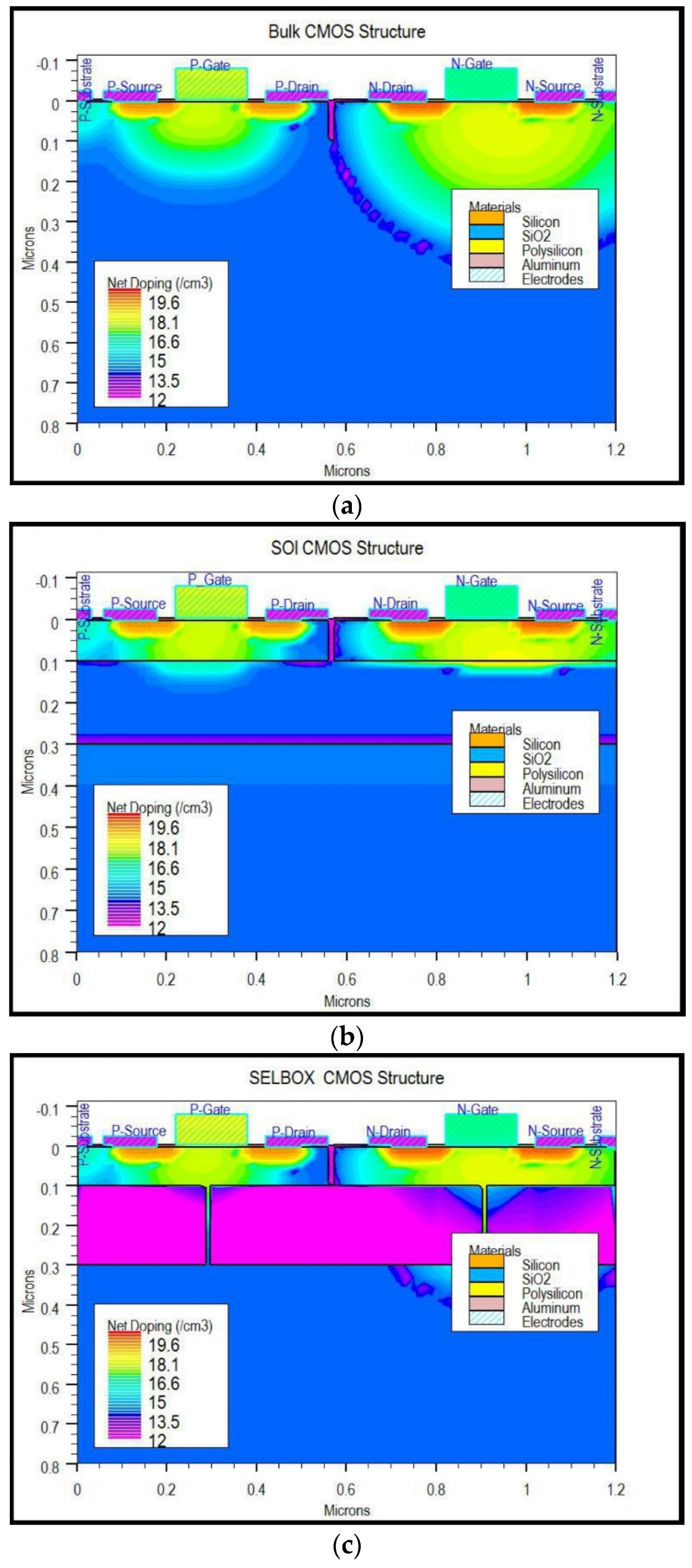

The presence of buried oxide has improved effects on the leakage currents in the CMOS units employing SOI and SELBOX MOSFETs as compared to the CMOS made of conventional BULK MOSFET devices. The reduction in the leakage currents results from the high resistive dielectric segments introduced in the structure by the oxide regions. Consequently, the on-state and off-state leakage currents and static power dissipation was found to be superior to BULK CMOS devices, as verified by authors in their previous work [

12].

One of the fundamental aspects that decides the frequency characteristics of a semiconductor device is the parasitic capacitance. The presence of buried oxide in SOI devices and in SELBOX devices reduces the parasitic capacitances. As a result, the frequency response of the circuits employing SOI and SELBOX was found to be superior to the BULK MOSFTs [

8]. Another important implication of reduced parasitic capacitance is the reduction in the charging and discharging currents when the CMOS unit turns on and off. With reduced charging and discharging currents, the power associated with the turn-on and off events will also be low. Hence, we hypothesize that using the SELBOX structure may reduce the dynamic power dissipation. Therefore, the main objective of this work is to investigate the dynamic power dissipation of the SELBOX structure and compare it with the BULK and SOI structures. The simulation of device fabrication was conducted using Silvaco TCAD tools [

13].

The rest of the paper is organized as follows:

Section 2 presents the methodology used for determining the dynamic power dissipation by calculations and simulation.

Section 3 describes the simulated fabrication of CMOS BULK, SOI and SELBOX devices.

Section 4 discusses the results followed by the conclusions and discussion in

Section 5.

2. Methodology

In this section we describe the mechanism behind dynamic power dissipation in CMOS inverter circuits. We also explain how to estimate this type of power dissipation using device parameters or from simulated voltage and current signals.

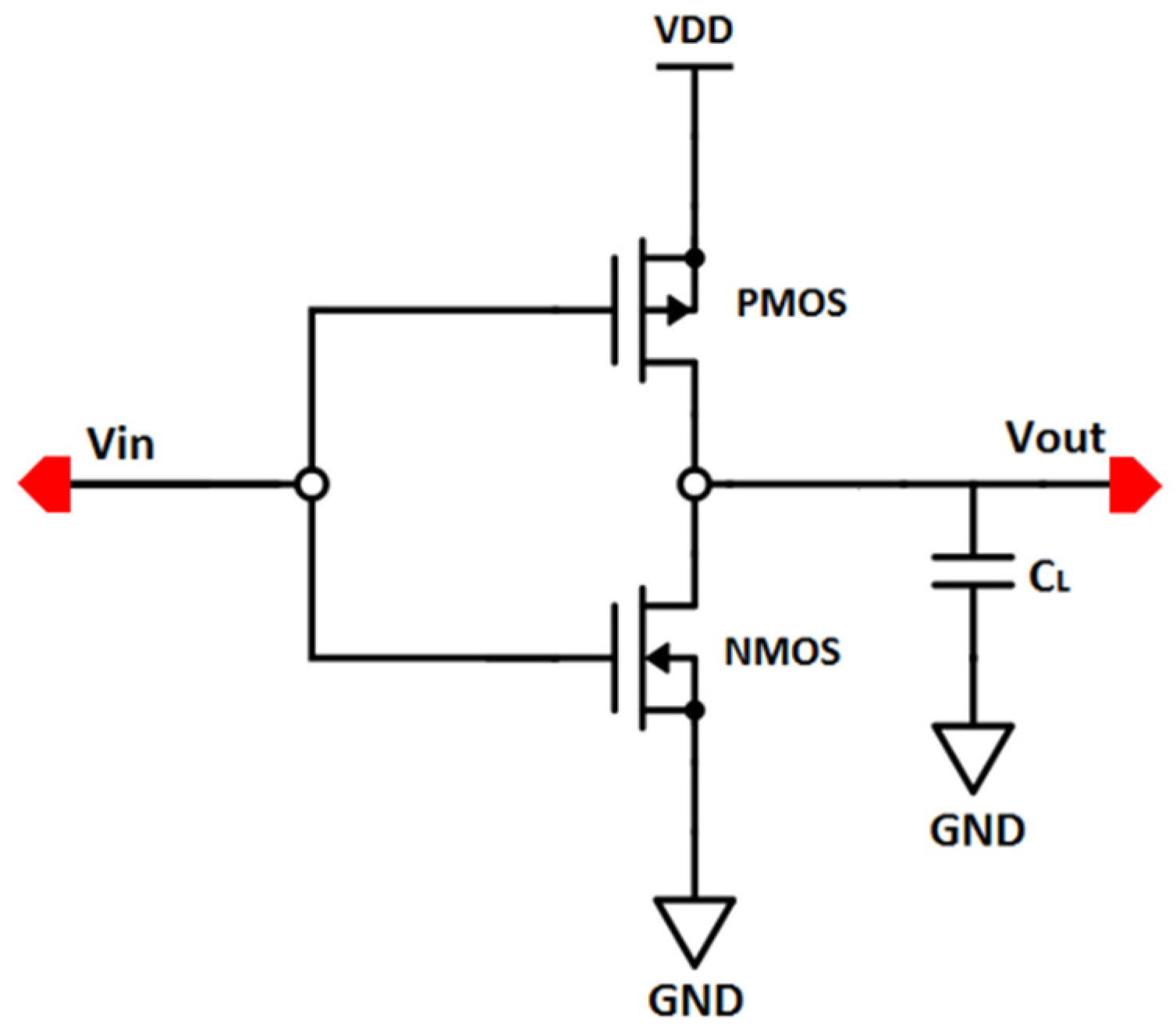

The CMOS inverter circuit is shown in

Figure 2. It is composed of a pull-up network, PMOS; and a pull-down network, NMOS and a driving load

.

When a pulse signal of 1.0 ps rise and fall time and 10 ns pulse width is applied to the input of the inverter, the output voltage takes time to fully charge or discharge

, as depicted in the output voltage

shown in

Figure 3. During the output voltage transition from a low to high state, load capacitance

is charged by current while dissipating power in PMOS resistance

. However, during the transition from a high to low state,

is discharged while power is dissipated in the NMOS resistance

. The dynamic power dissipation in BULK technology is the dominant factor in power dissipation in CMOS devices down to 180 nm, but is questionable in SOI and SELBOX [

3].

Theoretically, the dynamic power dissipation in the CMOS inverter may be computed using [

14]:

where

is the clock frequency,

is the supply voltage and

is the activity factor, which is the probability of the output switching from 0 to 1. As the signal used in this simulation work is a clock (pulse) signal,

is equal to 1 [

15].

includes the internal capacitances of the NMOS and PMOS in the CMOS inverter and the internal capacitances of the NMOS and PMOS of the load, assuming the CMOS inverter is driving another CMOS inverter as a load as depicted in Equation (2) [

16]:

where

and

are the gates that drain the capacitance of the NMOS and PMOS of the CMOS inverter, respectively.

and

are the drains to Bulk capacitance of the NMOS and PMOS in the CMOS inverter, respectively.

and

are the gate capacitance of the NMOS and PMOS of the CMOS inverter load.

is the wiring capacitance.

Another source of dynamic power dissipation is the short circuit power dissipation. During the transition from the ON to OFF state or from the OFF to ON state, there will be a period of time where both PMOS and NMOS transistors are conducting and the current will find a direct path between

and ground, thus resulting in short circuit current. The short circuit power dissipation is [

3]:

where voltage,

is the fall or rise time of the input signal and

is the clock frequency and

is a factor that depends on the transistor dimensions [

14].

If the device parameters and dimensions are available, we can estimate the average dynamic power dissipation in the CMOS inverter by adding the power dissipation in both PMOS and NMOS [

16]. It can be shown that the total average dynamic power dissipation is:

where

is the clock period. Furthermore, to determine the dynamic power dissipation in the simulated devices, we can use numerical integration of the used voltage and current signals:

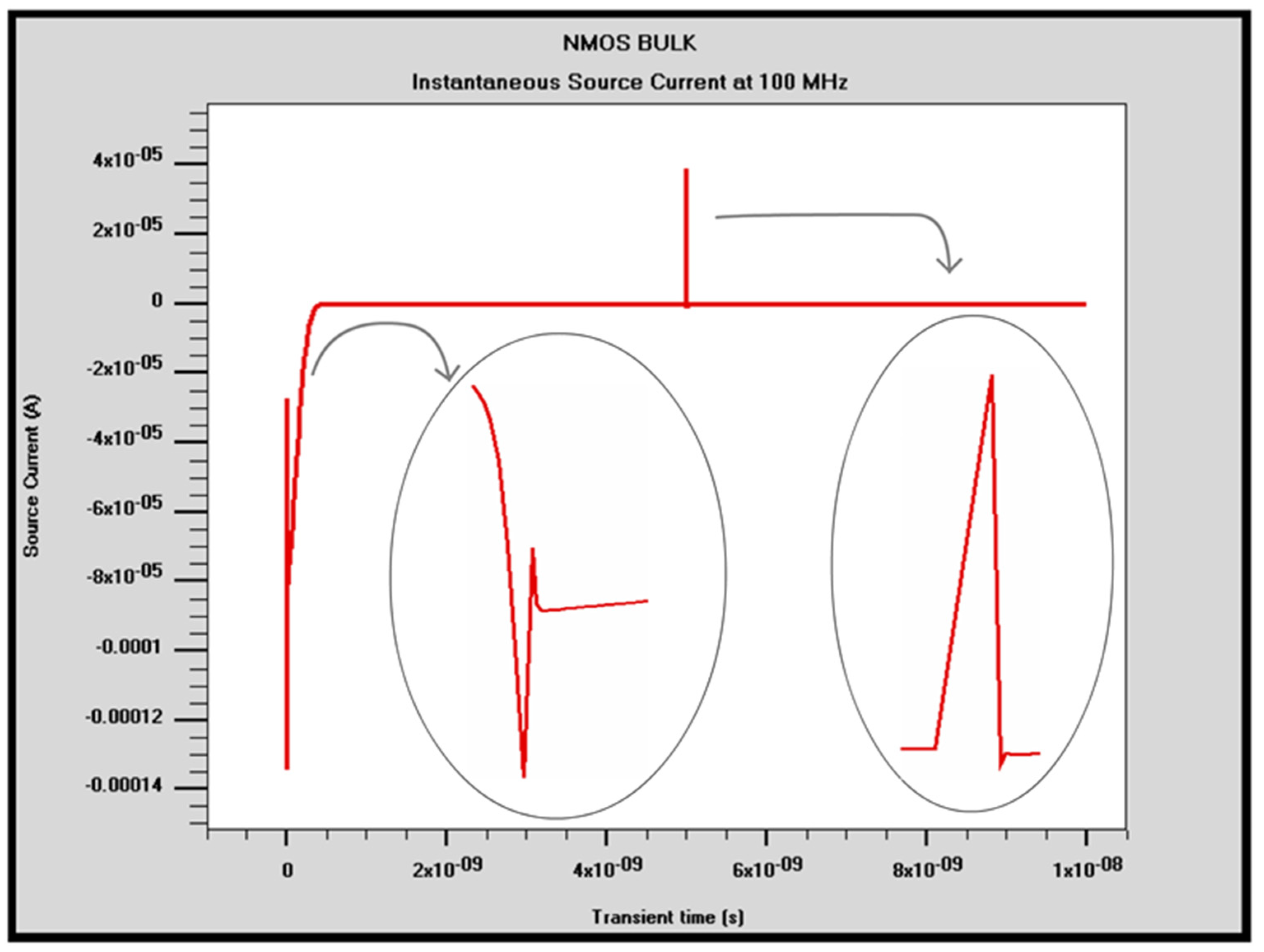

where

and

are the NMOS and PMOS source currents, respectively. Thus, if

f = 100 MHz, total average dynamic power dissipation can be estimated by integrating the voltage and current signals depicted in

Figure 3 and

Figure 4 using Equation (5). This method will be used later on in the Results section.

4. Results

In this section, we investigate the effect of varying the operating frequency on the dynamic power dissipation of the three CMOS architectures. First, was set to a typical load capacitance value of and the average dynamic power dissipation against frequency was obtained. Unfortunately, a discrete load capacitance may not be a realistic scenario. This is because the load capacitance is the sum of internal capacitances of the load device and it is assumed to be the same for the three structures. If a digital system is composed of CMOS devices of the same structure; such as a system where all devices are BULK, SOI or SELBOX, it is more realistic to assume that represents the internal capacitance of the CMOS load which has the same structure. This is an important test as it reveals the actual dynamic power dissipation which occurs in real electronic systems. Thus, in the second test, we investigated the dynamic power dissipation by considering a CMOS BULK driving a CMOS BULK, a CMOS SOI driving a CMOS SOI, and a CMOS SELBOX driving a CMOS SELBOX load. In both simulation tests, the dynamic power dissipation was calculated using Equations (4) and (5) described in the Methodology section.

4.1. Effect of Varying the Operating Frequency with Discrete

In this test, only the operating frequency was varied whilst keeping

and

fixed. The simulation was carried out by applying a pulse signal of

rise and fall times with the pulse width varying according to the selected frequency. The test was carried out for practical frequencies ranging from

to

.

is discrete and was assumed to be

. The supply voltage was set to

which is the standard supply voltage used for

technology [

18]. The CMOS inverter circuit used to carry out this test is shown in

Figure 2. The average dynamic power dissipation was calculated using Equation (5).

Table 6,

Table 7 and

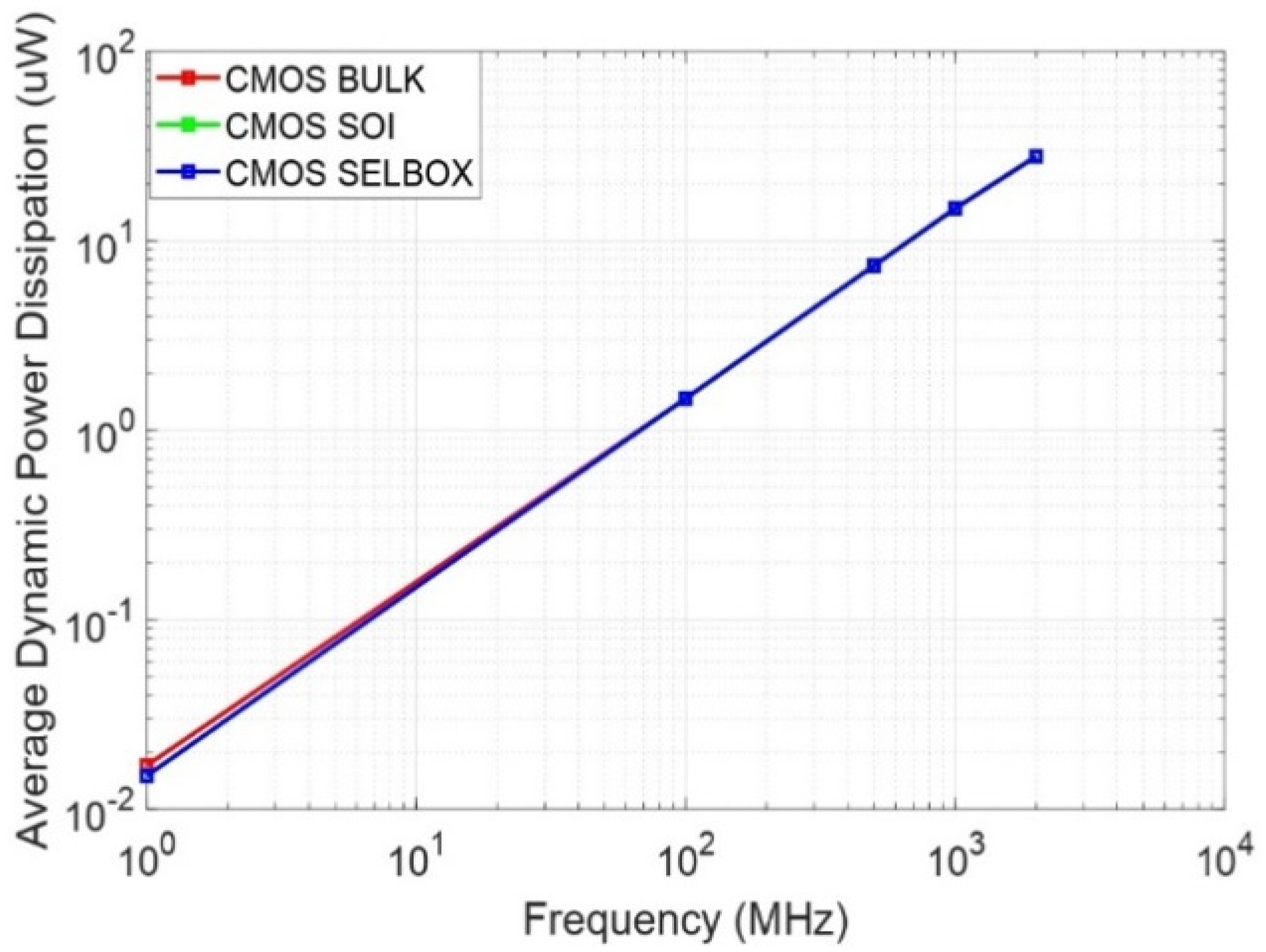

Table 8 show the average dynamic power dissipation for the three structures. The results indicate that as switching frequency increases, power dissipation increases as expected according to the model described in Equation (1). The average dynamic power dissipation of the three devices show very small differences at high and low frequencies. For instance, at 1 MHz, the average dynamic power dissipation of the BULK CMOS is higher than that of the SOI and SELBOX by 0.002 µW. However, at 2 GHz, the average dynamic power dissipation of the BULK is similar to that of SELBOX SOI and higher than SOI by 0.1 µW.

Figure 6 summarizes the CMOS BULK, SOI and SELBOX average dynamic power dissipation against frequency. It can be observed that the curves are linear, indicating identical behavior with very small differences. It can also be observed that as frequency increases, average dynamic power dissipation increases as expected. This is because

is discrete and assumed to be the same for the three devices. In addition, the channel resistance of the NMOS in all three devices is almost the same. The same applies to the channel resistance of the PMOS. However, their structural difference resides in the internal capacitance. All three devices have different internal capacitance, and hence

is not the same when it is considered as a lumped device. For instance, in the work of Narayanan et al., different values of

were found, that is,

,

and

for CMOS BULK, SOI and SELBOX, respectively [

8]. This case will be discussed further in the next subsection.

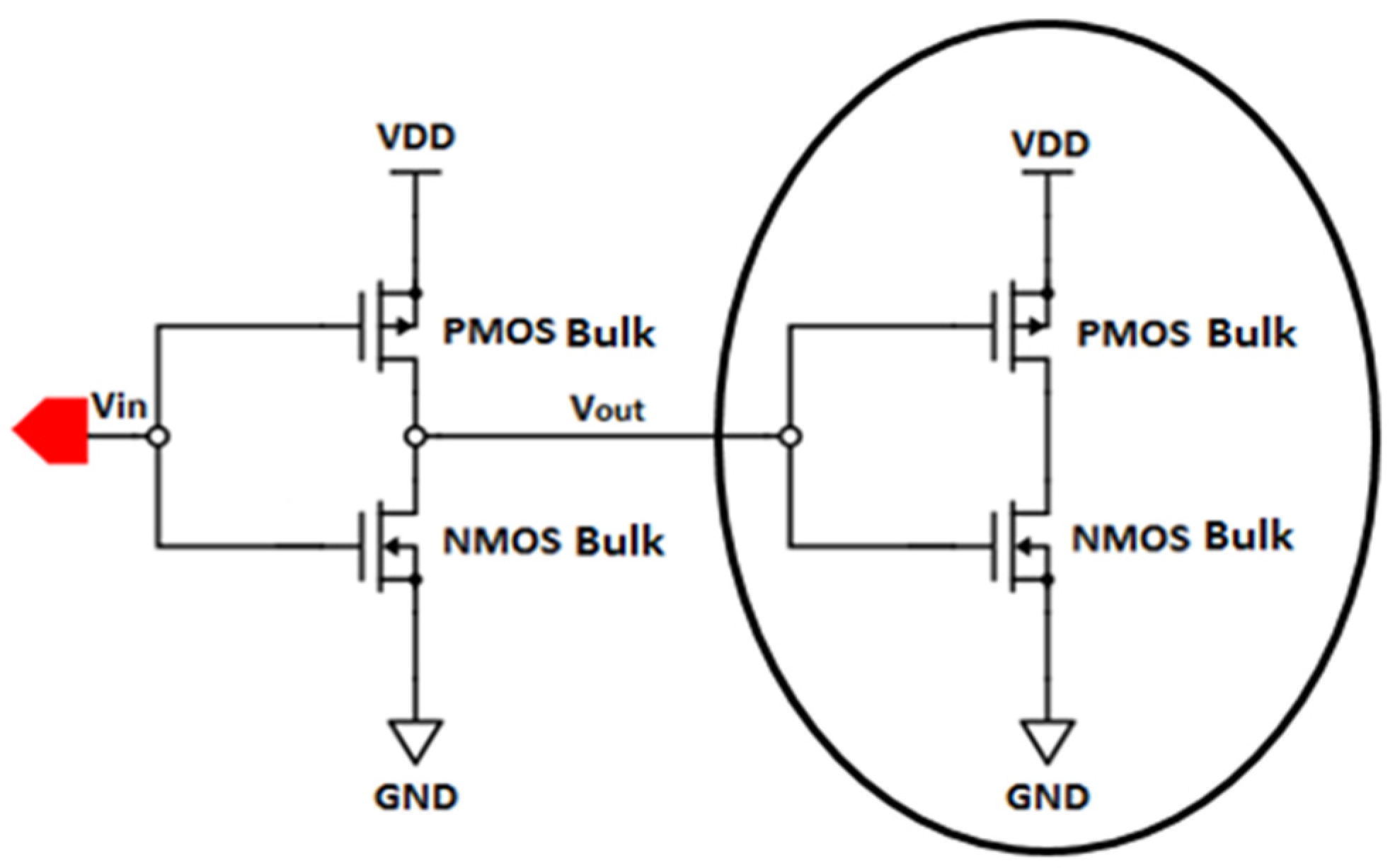

4.2. Effect of Varying the Operating Frequency with CMOS Load

A reasonable assumption is that all devices in a system have the same technology and structure. Thus, a CMOS BULK drives a CMOS BULK, a CMOS SOI drives a CMOS SOI and a CMOS SELBOX drives a CMOS SELBOX as a load. Based on this assumption, the CMOS BULK inverter circuit is presented as shown in

Figure 7, where the circled device is the load. The same circuit configuration applies to SOI and SELBOX inverter circuits. The same procedure described in the Methodology section was used to estimate the average dynamic power dissipation. However, in this simulation a similar CMOS device was used as the load instead of a capacitor.

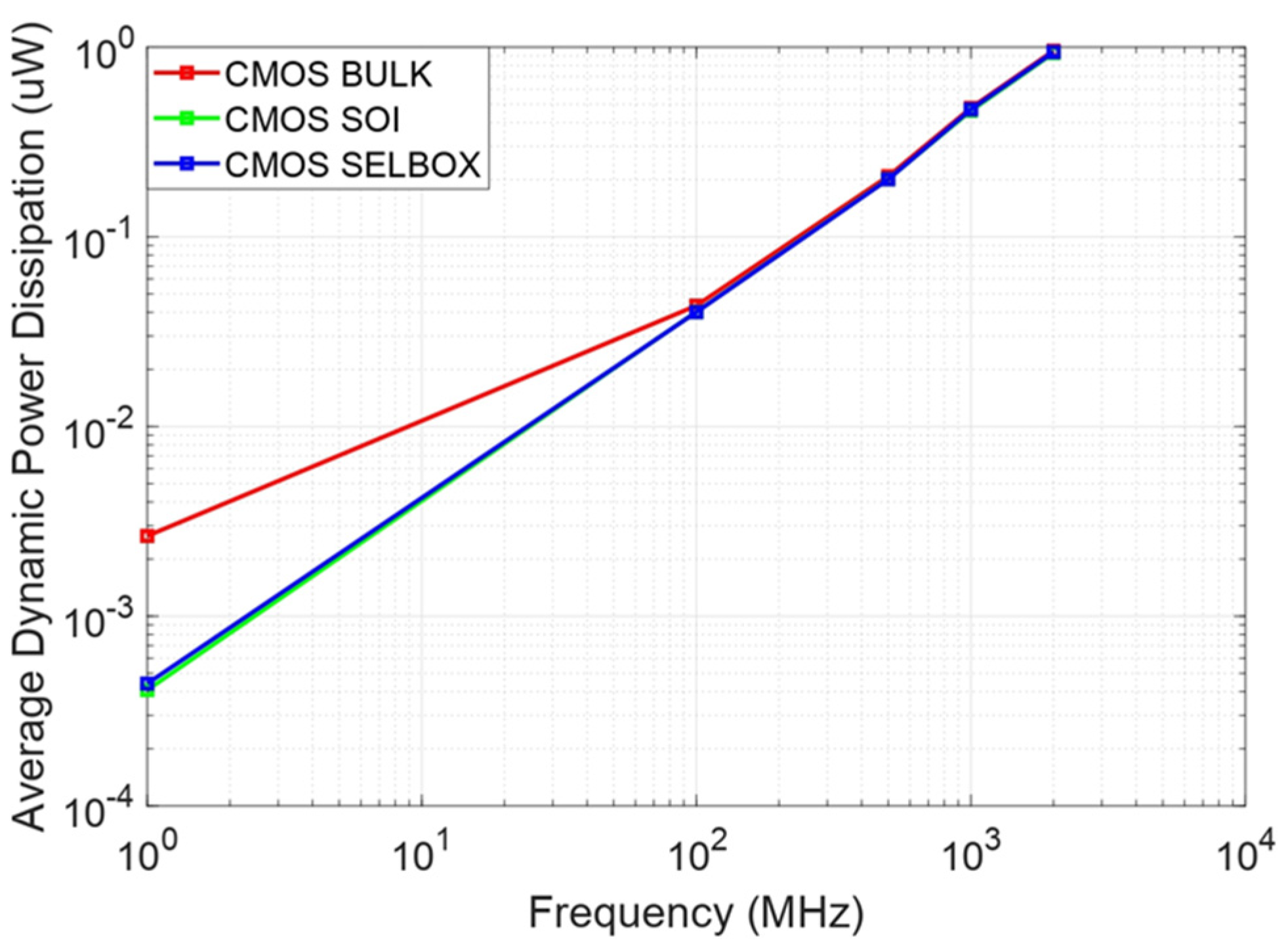

Table 9 lists the average dynamic power dissipation results for CMOS BULK, SOI and SELBOX. As frequency increases, the average dynamic power dissipation increases as expected.

Figure 8 shows the combined average dynamic power dissipation for the three structures. The results show that the CMOS BULK has the highest average dynamic power dissipation. CMOS SOI and SELBOX have very close average dynamic dissipation results. However, the CMOS SOI average dynamic power dissipation is slightly lower than that of CMOS SELBOX while the latter’s average dynamic power dissipation lies in between that of the CMOS BULK and SOI. This is because the CMOS SOI reduces the device’s parasitic capacitances more than the CMOS SELBOX, as a result of inserting the BOX layer. Moreover, the results in

Figure 8 show that the deviation in the average dynamic power dissipation of the three CMOS devices occurs at low frequencies. Yet, at high frequencies, the average dynamic power dissipation is almost the same for the CMOS BULK, SOI and SELBOX. This is because the parasitic capacitances behave like a resistor at high frequency, leading to higher average dynamic power dissipation. However, at low frequencies, the SOI and SELBOX structures exhibit lower parasitic capacitances than the BULK structure.

4.3. Dynamic Power Dissipation Using Device Parameters

This section presents the results obtained using the mathematical model of the average dynamic power dissipation of the CMOS BULK, SOI and SELBOX devices. Moreover, it provides a justification for the average dynamic power dissipation results when the operating frequency is varied.

The total power dissipation is the addition of the average dynamic power dissipation which is dissipated in the PMOS because of the charging and discharging of . Thus, the average dynamic power dissipation is calculated using Equation (4). The calculation of the average dynamic power dissipation when the operating frequency is is explained in the following paragraphs.

To calculate

and

, the time constants

and

are found from the CMOS inverter output in

Figure 3, where

is the time taken for the output to fall from 90% to 37% of its maximum value, which is 0.444 V. However,

is the time taken for the output to rise from 10% to 63% of its maximum value, which is equal to 0.756 V. Discharging and charging time constants

and

are equal to

and

s, respectively. Hence,

and

are found to be

Ω and

, respectively. Then, after finding

,

,

and

, the total average dynamic dissipation is calculated using Equation (4) to be

The same procedure was followed to calculate the average dynamic power dissipation in CMOS SOI and SELBOX.

Table 10 shows the calculated values of the average dynamic power dissipation in CMOS SOI and SELBOX at 100 MHz. It is worth mentioning that the same

CL value that was used in calculating the average dynamic power dissipation in CMOS BULK, was also used to find that of CMOS SOI and SELBOX.

Comparing the results of the simulation and the calculations for CMOS BULK, SOI and SELBOX, it can be seen that the results are the same with approximately 2.1% error. As such, the similarities in the simulation and calculation results show that the procedure for finding the dynamic power dissipation for the three CMOS devices in the simulation was reasonably accurate.

5. Conclusion and Discussion

In this work, the average dynamic power dissipation of the SELBOX structure was investigated and compared to that of SOI and BULK structures. The SELBOX’s properties enable it to have a low self-heating effect, eliminate the kink effect, and operate at high speed. Its structure reduces the device’s internal capacitances, and hence reduces the dynamic power dissipation compared to the BULK CMOS structure [

12,

19].

The dynamic power dissipation was investigated for the three CMOS architectures by varying the operating frequency. All test results showed that as frequency increases, average dynamic power dissipation increases. Moreover, the average dynamic power dissipation results for the three devices showed a similar behavior when the load was a discrete capacitor. This is because the load capacitance was assumed to be the same for the three devices and their channel resistances were almost the same. However, assuming the CMOS is driving a load that has the same structure reveals the actual load capacitance, and hence, the average dynamic power dissipation results showed differences for the three devices. The CMOS SELBOX has the lowest average dynamic power dissipation and the CMOS BULK has the highest although it is very close to that of the CMOS SOI.

Furthermore, it was noticed that the average dynamic power dissipation of the three CMOS devices is not the same at low frequencies. However, at high frequencies, the average dynamic power dissipation of the three devices are almost the same. This is because, at high switching frequency, the parasitic capacitances behave like a resistor, and hence losses increase, which results in increasing average dynamic power dissipation. On the other hand, the second test showed that as the load capacitance increases, the average dynamic power dissipation increases as expected.

Fair and exact comparison with state-of-the-art devices is challenging because of the different technology, materials and specifications that are used. In addition, most of the recent publications report the total power dissipation produced by the whole system rather than a single CMOS device. Nevertheless, we mention here the results of a couple of recent publications on the dynamic power dissipation. Baker stated in his book that a CMOS inverter designed using 50 nm and operated at 4 GHz produced 19.6 µW [

20]. At a system level, a CMOS inverter comparator based on 90 nm technology was reported in [

21]. The average reported power consumption was 24.3 μW.

In conclusion, the CMOS SELBOX structure is better than the CMOS SOI structure in eliminating kink and self-heating effects and shows almost the same average dynamic power dissipation as that of CMOS SOI. Also, the CMOS SELBOX structure is better than the CMOS BULK structure in providing reduced internal capacitances, and thus lower average dynamic power dissipation and better frequency characteristics.

The average dynamic power dissipation calculations were very close to those found from the simulation, with approximately 2.1% percentage of error.