Implementation of Ambipolar Polysilicon Thin-Film Transistors with Nickel Silicide Schottky Junctions by Low-Thermal-Budget Microwave Annealing

Abstract

:1. Introduction

2. Materials and Methods

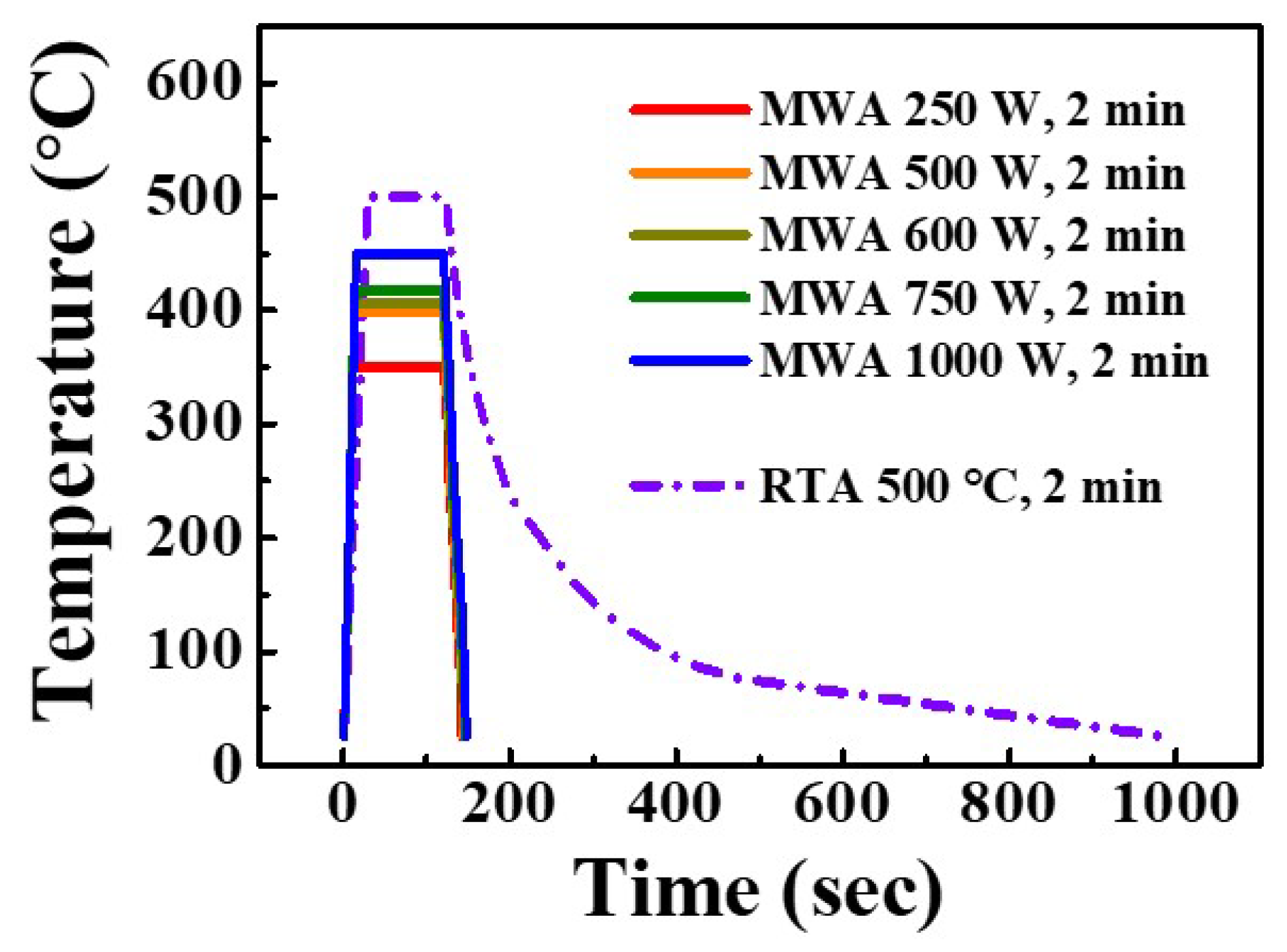

2.1. Nickel Deposition and Silicidation

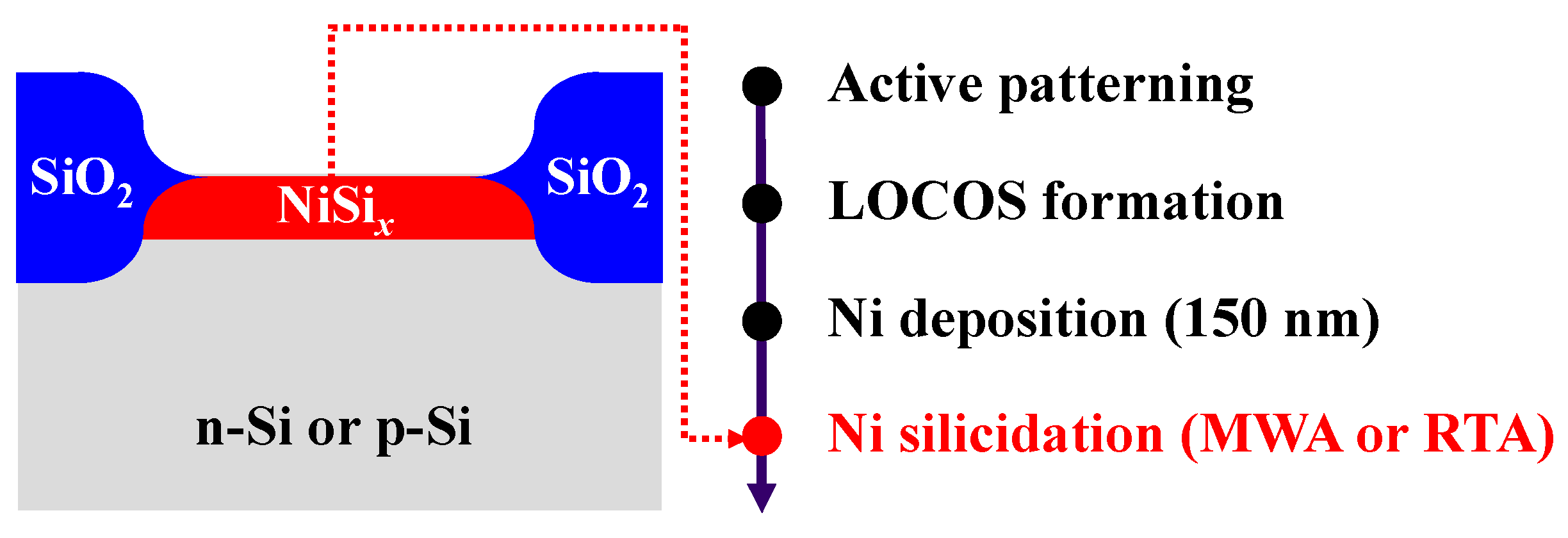

2.2. Fabrication of the NiSix SB-Diodes

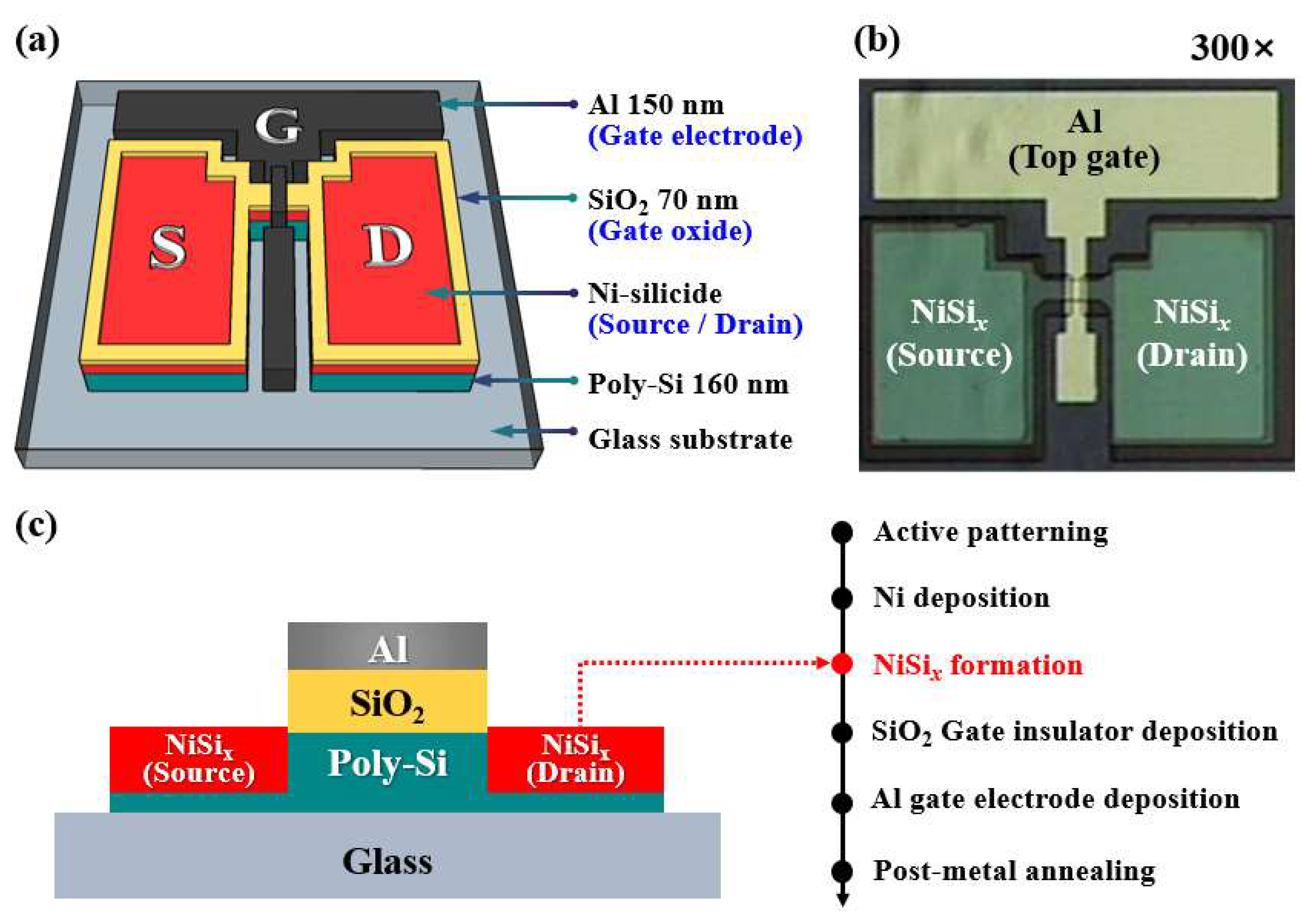

2.3. Fabrication of the NiSix SB-TFTs

2.4. Characterization of the NiSix SB-Diodes and SB-TFTs

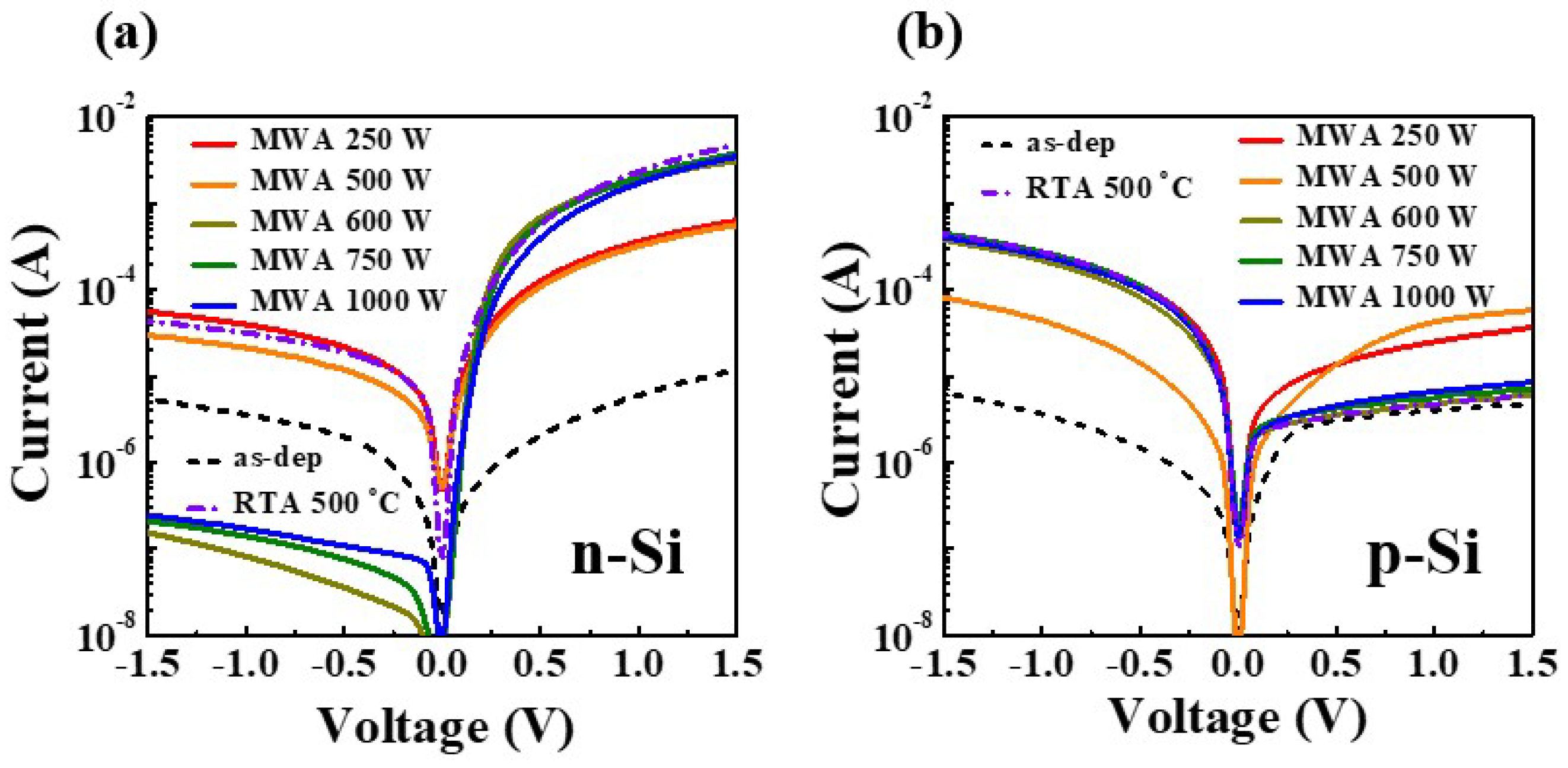

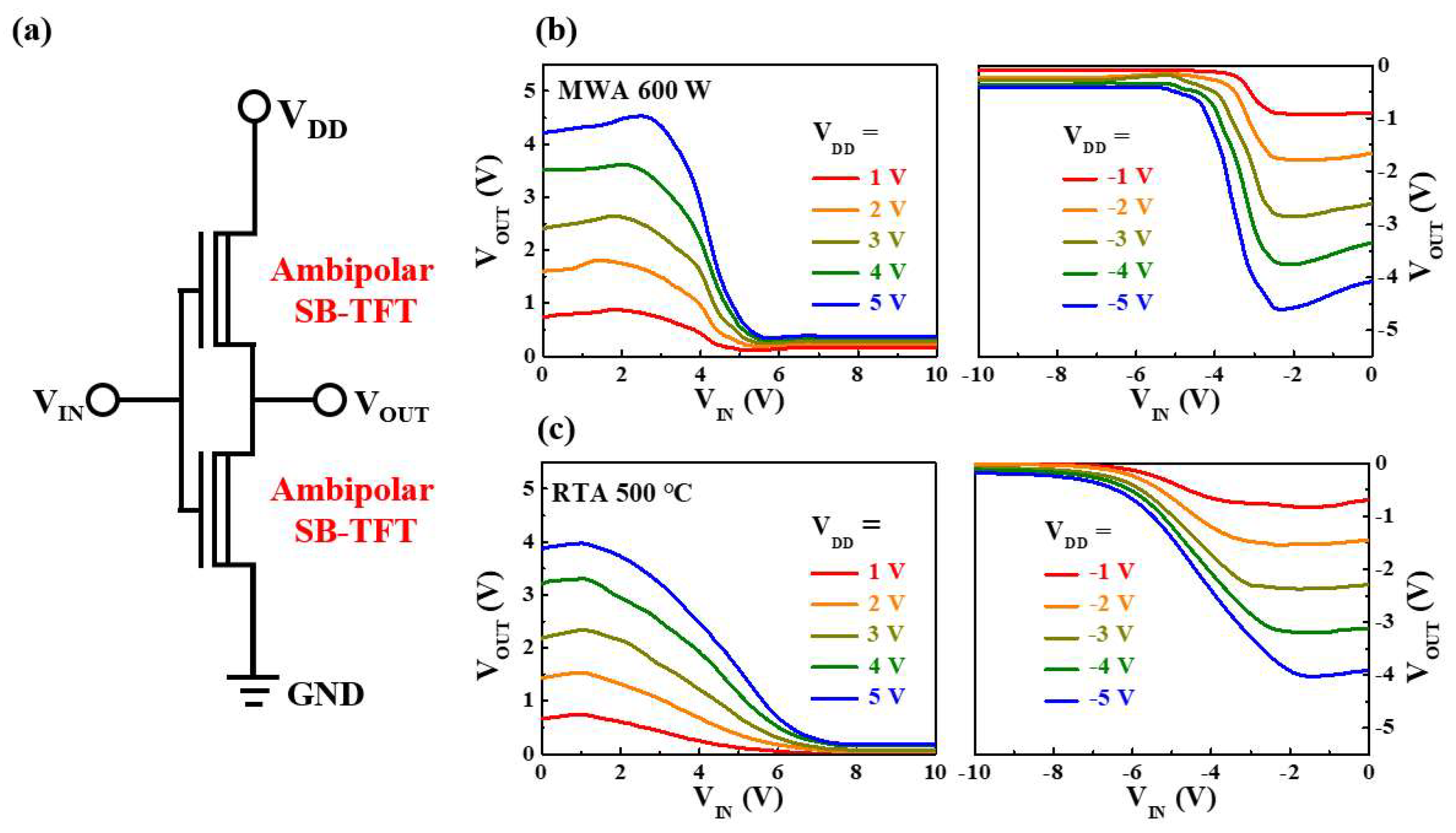

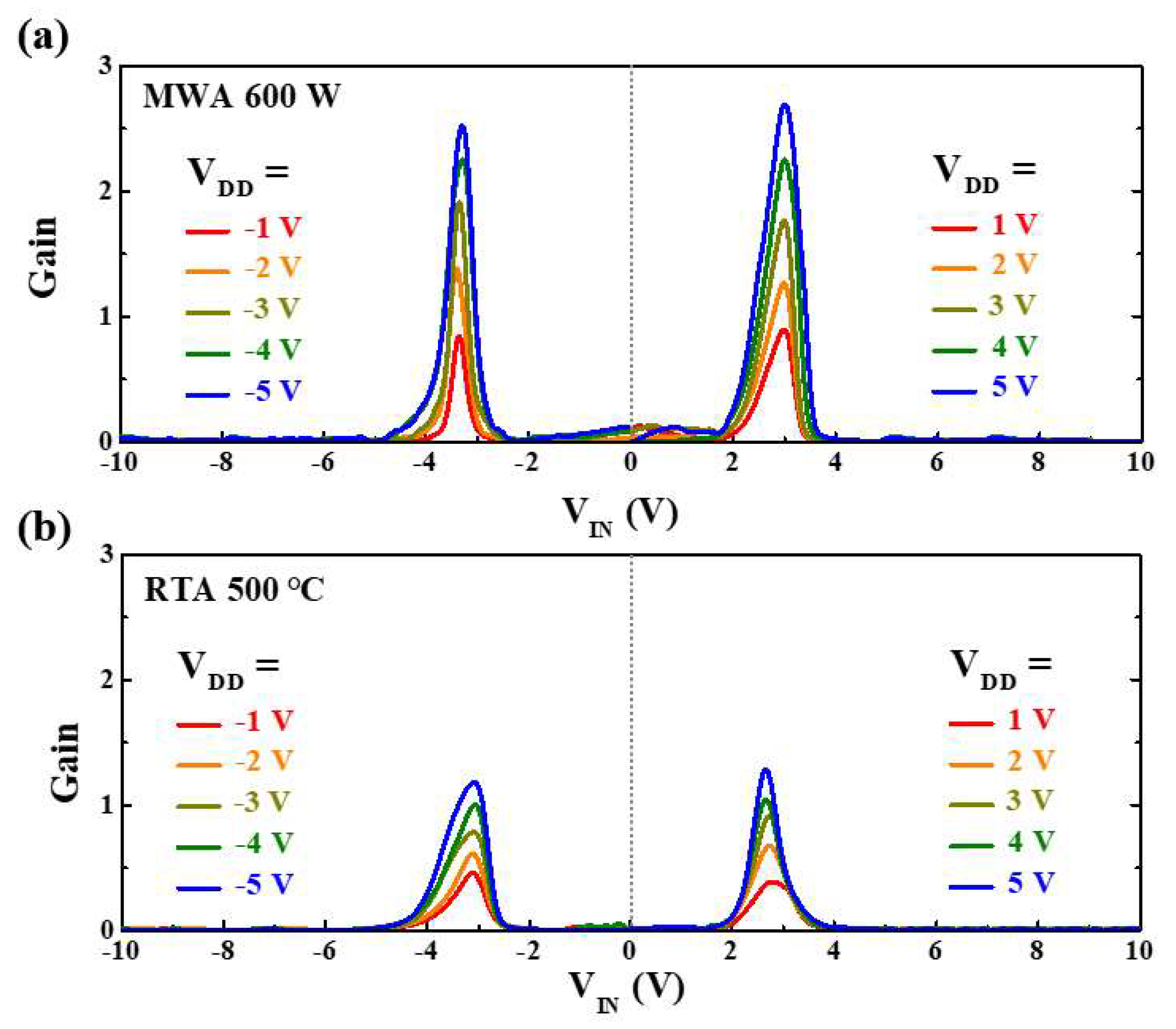

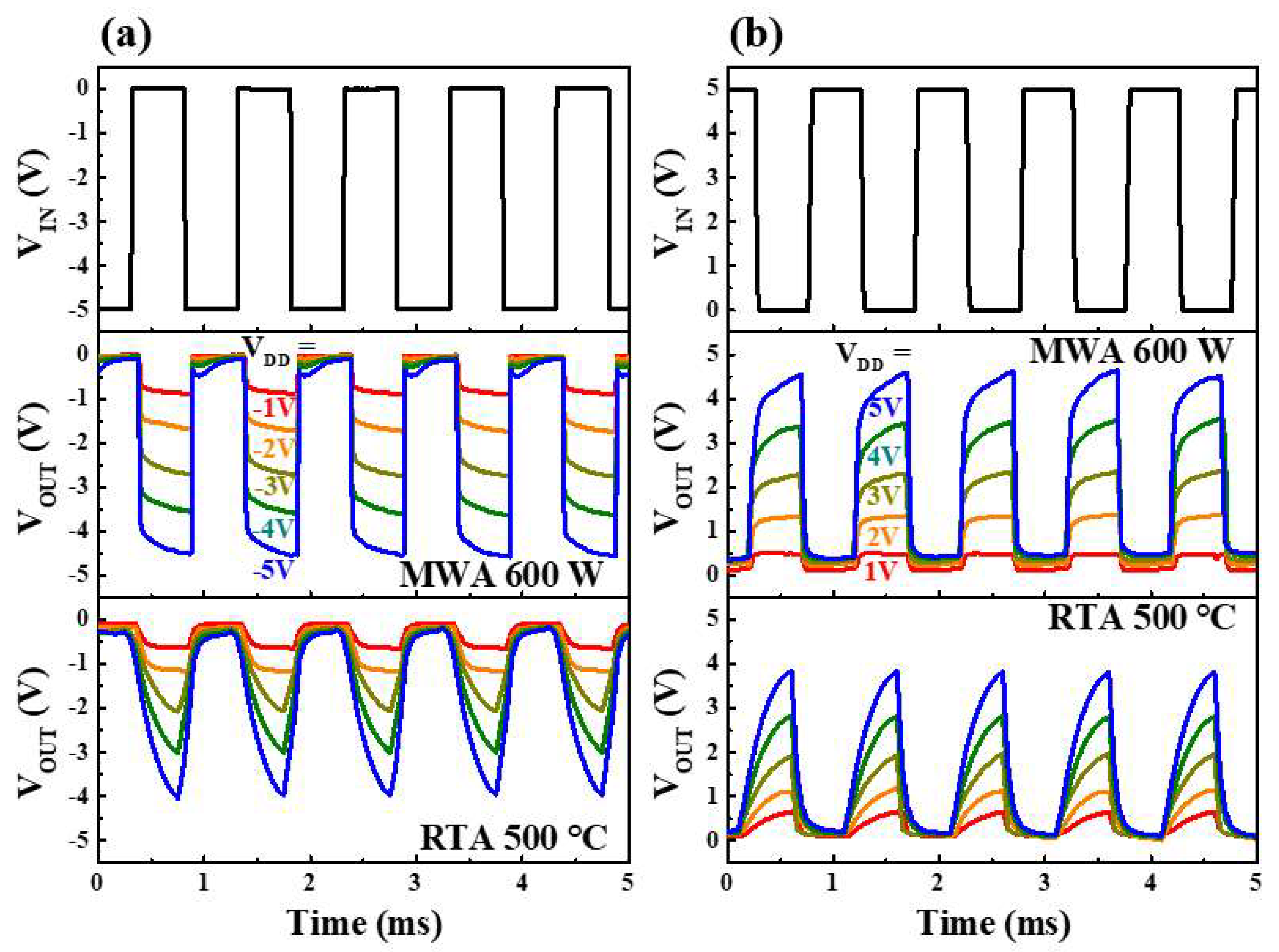

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Kittl, J.A.; Opsomer, K.; Torregiani, C.; Demeurisse, C.; Mertens, S.; Brunco, D.P.; Van Dal, M.J.H.; Lauwers, A. Silicides and germanides for nano-CMOS applications. Mater. Sci. Eng. B 2008, 154, 144–154. [Google Scholar] [CrossRef]

- Hoummada, K.; Perrin-Pellegrino, C.; Mangelinck, D. Effect of Pt addition on Ni silicide formation at low temperature: Growth, redistribution, and solubility. J. Appl. Phys. 2009, 106, 063511. [Google Scholar] [CrossRef]

- Julies, B.A.; Knoesen, D.; Pretorius, R.; Adams, D. A study of the NiSi to NiSi2 transition in the Ni–Si binary system. Thin Solid Film. 1999, 347, 201–207. [Google Scholar] [CrossRef]

- Schmitt, A.L.; Higgins, J.M.; Szczech, J.R.; Jin, S. Synthesis and applications of metal silicide nanowires. J. Mater. Chem. 2010, 20, 223–235. [Google Scholar] [CrossRef]

- Zhu, S.; Chen, J.; Li, M.-F.; Lee, S.J.; Singh, J.; Zhu, C.X.; Du, A.; Tung, C.H.; Chin, A.; Kwong, D.L. N-type Schottky barrier source/drain MOSFET using ytterbium silicide. IEEE Electron. Device Lett. 2004, 25, 565–567. [Google Scholar] [CrossRef]

- Jang, M.; Kim, Y.; Shin, J.; Lee, S. A 50-nm-gate-length erbium-silicided n-type Schottky barrier metal–oxide–semiconductor field-effect transistor. Appl. Phys. Lett. 2004, 84, 741–743. [Google Scholar] [CrossRef]

- Kedzierski, J.; Xuan, P.; Erik, E.K.; Anderson, H.; Bokor, J.; King, T.-J.; Hu, C. Complementary silicide source/drain thin-body MOSFETs for the 20 nm gate length regime. In Proceedings of the International Electron Devices Meeting 2000. Technical Digest. IEDM (Cat. No.00CH37138), San Francisco, CA, USA, 10–13 December 2000; pp. 57–60. [Google Scholar]

- Zhao, Q.T.; Kluth, P.; Winnerl, S.; Mantl, S. Fabrication of Schottky barrier MOSFETs on SOI by a self-assembly CoSi2-patterning method. Solid-State Electron. 2003, 47, 1183–1186. [Google Scholar] [CrossRef]

- Wang, C.; Snyder, J.P.; Tucker, J.R. Sub-40 nm PtSi Schottky source/drain metal–oxide–semiconductor field-effect transistors. Appl. Phys. Lett. 1999, 74, 1174–1176. [Google Scholar] [CrossRef]

- Guo, J.; Lundstrom, M. A computational study of thin-body, double- gate, Schottky barrier MOSFETs. IEEE Trans. Electron. Devices 2002, 49, 1897–1902. [Google Scholar]

- Kittl, J.A.; Lauwers, A.; Chamirian, O.; Van Dal, M.; Akheyar, A.; De Potter, M.; Lindsay, R.; Maex, K. Ni-and Co-based silicides for advanced CMOS applications. Microelectron. Eng. 2003, 70, 158–165. [Google Scholar] [CrossRef]

- Lauwers, A.; Steegen, A.; de Potter, M.; Lindsay, R.; Satta, A.; Bender, H.; Maex, K. Materials aspects, electrical performance, and scalability of Ni silicide towards sub-0.13 μm technologies. J. Vac. Sci. Technol. B 2001, 19, 2026–2037. [Google Scholar] [CrossRef]

- Dai, J.Y.; Guo, Z.R.; Tee, S.F.; Tay, C.L.; Er, E.; Redkar, S. Formation of cobalt silicide spikes in 0.18 μm complementary metal oxide semiconductor process. Appl. Phys. Lett. 2001, 78, 3091–3093. [Google Scholar] [CrossRef]

- Lavoie, C.; Detavernier, C.; Cabral, C.; d’Heurle, F.M.; Kellock, A.J.; Jordan-Sweet, J.; Harper, J.M.E. Effects of additive elements on the phase formation and morphological stability of nickel monosilicide films. Microelectron. Eng. 2006, 83, 2042–2054. [Google Scholar] [CrossRef]

- Ma, Z.; Zhou, S.; Zhou, C.; Xiao, Y.; Li, S.; Chan, M. Synthesis of Vertical Carbon Nanotube Interconnect Structures Using CMOS-Compatible Catalysts. Nanomaterials 2020, 10, 1918. [Google Scholar] [CrossRef] [PubMed]

- Ramly, M.M.; Omar, F.S.; Rohaizad, A.; Aspanut, Z.; Rahman, S.A.; Goh, B.T. Solid-phase diffusion controlled growth of nickel silicide nanowires for supercapacitor electrode. Appl. Surf. Sci. 2018, 456, 515–525. [Google Scholar] [CrossRef]

- Tam, P.L.; Nyborg, L. Sputter deposition and XPS analysis of nickel silicide thin films. Surf. Coat. Technol. 2009, 203, 2886–2890. [Google Scholar] [CrossRef]

- Kim, P.S.S.; Becker, A.; Ou, Y.; Julius, A.A.; Kim, M.J. Imparting magnetic dipole heterogeneity to internalized iron oxide nanoparticles for microorganism swarm control. J. Nanoparticle Res. 2015, 17, 1–15. [Google Scholar] [CrossRef]

- Lavoie, C.; d’Heurle, F.M.; Detavernier, C.; Cabral Jr., C. Towards implementation of a nickel silicide process for CMOS technologies. Microelectron. Eng. 2003, 70, 144–157. [Google Scholar] [CrossRef]

- Li, Z.H.; Jiang, Y.L.; Li, R.L.; Zhang, Y.W.; Cao, Y.F. Performance Improvement by Cold Xe Pre-Amorphization Implant for Nickel Silicidation of 28-nm PMOSFET. IEEE Electr. Device L. 2019, 40, 777–779. [Google Scholar] [CrossRef]

- Shen, K.H.; Chen, S.H.; Liu, W.T.; Wu, B.H.; Chen, L.J. Effective Schottky barrier lowering of Ni silicide/p-Si (100) using an ytterbium confinement structure for high performance n-type MOSFETs. Mater. Des. 2017, 114, 220–225. [Google Scholar] [CrossRef] [Green Version]

- Wong, A.S.W.; Chi, D.Z.; Loomans, M.; Ma, D.; Lai, M.Y.; Tjiu, W.C.; Chua, S.J.; Lim, C.W.; Greene, J.E. F-enhanced morphological and thermal stability of NiSi films on BF2+-implanted Si (001). Appl. Phys. Lett. 2002, 81, 5138–5140. [Google Scholar] [CrossRef]

- Bucher, E.; Schulz, S.; Luxsteiner, M.C.; Munz, P.; Gubler, U.; Greuter, F. Work function and barrier heights of transition metal silicides. Appl. Phys. Mater. Sci. Process. 1986, 40, 71–77. [Google Scholar] [CrossRef]

- Lu, J.P.; Miles, D.S.; DeLoach, J.; Yue, D.F.; Chen, P.J.; Bonifield, T.; Crank, S.; Yu, S.F.; Mehrad, F.; Obeng, Y.; et al. Nickel Salicide Process Technology for CMOS Devices of 90 nm Node and Beyond. In Proceedings of the 2006 International Workshop on Junction Technology, Shanghai, China, 15–16 May 2006. [Google Scholar]

- Pyo, J.Y.; Cho, W.J. Investigation of Parasitic Resistance Components in the Case of Microwave Irradiation in Poly-Si Annealing. J. Korean Phys. Soc. 2018, 73, 978–982. [Google Scholar] [CrossRef]

- Shin, J.W.; Cho, W.J. Microwave annealing effects of indium-tin-oxide thin films: Comparison with conventional annealing methods. Phys. Status Solidi A 2018, 215, 1700975. [Google Scholar] [CrossRef]

- Schulze, T.F.; Beushausen, H.N.; Hansmann, T.; Korte, L.; Rech, B. Accelerated interface defect removal in amorphous/crystalline silicon heterostructures using pulsed annealing and microwave heating. Appl. Phys. Lett. 2009, 95, 182108. [Google Scholar] [CrossRef]

- Chang, W.; Horwitz, J.S.; Carter, A.C.; Pond, J.M.; Kirchoefer, S.W.; Gilmore, C.M.; Chrisey, D.B. The effect of annealing on the microwave properties of Ba 0.5 Sr 0.5 TiO3 thin films. Appl. Phys. Lett. 1999, 74, 1033–1035. [Google Scholar] [CrossRef]

- Lee, Y.J.; Cho, T.C.; Chuang, S.S.; Hsueh, F.K.; Lu, Y.L.; Sung, P.J.; Chen, H.C.; Current, M.I.; Tseng, T.Y.; Chao, T.S.; et al. Low-temperature microwave annealing processes for future IC fabrication—A review. IEEE Trans. Electron Devices 2014, 61, 651–665. [Google Scholar] [CrossRef]

- Lee, Y.J.; Tsai, B.A.; Lai, C.H.; Chen, Z.Y.; Hsueh, F.K.; Sung, P.J.; Current, M.I.; Luo, C.W. Low-temperature microwave annealing for MOSFETs with high-k/metal gate stacks. IEEE Electron. Device Lett. 2013, 34, 1286–1288. [Google Scholar] [CrossRef]

- Hong, E.K.; Cho, W.J. Effect of microwave annealing on SOI MOSFETs: Post-metal annealing with low thermal budget. Microelectron. Reliab. 2018, 80, 306–311. [Google Scholar] [CrossRef]

- Cho, S.K.; Cho, W.J. Performance enhancement of electrospun IGZO-nanofiber-based field-effect transistors with high-k gate dielectrics through microwave annealing and postcalcination oxygen plasma treatment. Nanomaterials 2020, 10, 1804. [Google Scholar] [CrossRef] [PubMed]

- Rahman, M.K.; Nemouchi, F.; Chevolleau, T.; Gergaud, P.; Yckache, K. Ni and Ti silicide oxidation for CMOS applications investigated by XRD, XPS and FPP. Mater. Sci. Semicond. Processing 2017, 71, 470–476. [Google Scholar] [CrossRef]

- Bhaskaran, M.; Sriram, S.; Mitchell, D.R.G.; Short, K.T.; Holland, A.S.; Mitchell, A. Microstructural investigation of nickel silicide thin films and the silicide–silicon interface using transmission electron microscopy. Micron 2009, 40, 11–14. [Google Scholar] [CrossRef]

- Türüt, A.B.; Bati, B.; Kökçe, A.; Sağlam, M.; Yalçin, N. The bias-dependence change of barrier height of Schottky diodes under forward bias by including the series resistance effect. Physica Scripta. 1996, 53, 118. [Google Scholar] [CrossRef]

- Trinh, T.T.; Ryu, K.; Jang, K.; Lee, W.; Baek, S.; Raja, J.; Yi, J. Improvement in the performance of an InGaZnO thin-film transistor by controlling interface trap densities between the insulator and active layer. Semicond. Sci. Technol. 2011, 26, 085012. [Google Scholar] [CrossRef]

- Avis, C.; Jang, J. A high performance inkjet printed zinc tin oxide transparent thin-film transistor manufactured at the maximum process temperature of 300 C and its stability test. Electrochem. Solid St. 2010, 14, J9. [Google Scholar] [CrossRef]

- Lee, J.M.; Cho, I.T.; Lee, J.H.; Kwon, H.I. Bias-stress-induced stretched-exponential time dependence of threshold voltage shift in InGaZnO thin film transistors. Appl. Phys. Lett. 2008, 93, 093504. [Google Scholar] [CrossRef]

- Nomura, K.; Kamiya, T.; Hirano, M.; Hosono, H. Origins of threshold voltage shifts in room-temperature deposited and annealed a-In–Ga–Zn–O thin-film transistors. Appl. Phys. Lett. 2009, 95, 13502. [Google Scholar] [CrossRef]

| Parameters | Type | As−dep | MWA | RTA | ||||

|---|---|---|---|---|---|---|---|---|

| 250 W | 500 W | 600 W | 750 W | 1000 W | 500 °C | |||

| On current [A] | n | 1.2 × 10−5 | 6.3 × 10−4 | 5.7 × 10−4 | 3.1 × 10−3 | 3.8 × 10−3 | 3.5 × 10−3 | 4.8 × 10−3 |

| p | 6.4 × 10−6 | 4.1 × 10−4 | 8.1 × 10−5 | 3.8 × 10−4 | 4.5 × 10−4 | 4.1 × 10−4 | 4.5 × 10−4 | |

| Off current [A] | n | 5.4 × 10−6 | 5.6 × 10−5 | 3.0 × 10−5 | 1.6 × 10−7 | 2.1 × 10−7 | 2.5 × 10−7 | 4.3 × 10−5 |

| p | 4.8 × 10−6 | 3.7 × 10−5 | 5.8 × 10−5 | 6.0 × 10−6 | 7.2 × 10−6 | 8.6 × 10−6 | 6.0 × 10−6 | |

| On/Off ratio | n | 2.2 | 1.1 × 101 | 1.9 × 101 | 2.0 × 104 | 1.8 × 104 | 1.4 × 104 | 1.1 × 102 |

| p | 1.4 | 1.1 × 101 | 1.4 | 6.3 × 101 | 6.2 × 101 | 4.7 × 101 | 7.5 × 101 | |

| Ideality factor (η) | n | 1.32 | 1.56 | 1.55 | 1.55 | 1.55 | 1.55 | 1.59 |

| p | 1.17 | 1.12 | 1.17 | 1.17 | 1.17 | 1.17 | 1.39 | |

| Schottky barrier height (φb) [eV] | n | 0.85 | 0.81 | 0.83 | 0.83 | 0.83 | 0.83 | 0.88 |

| p | 1.02 | 0.99 | 0.92 | 0.92 | 0.92 | 0.92 | 1.07 | |

| Conduction | Silicidation | Total Parameter | ||||

|---|---|---|---|---|---|---|

| SS (mV/dec) | Mobility (cm2/V∙s) | VTH (V) | Ion/Ioff | Dit (cm2) | ||

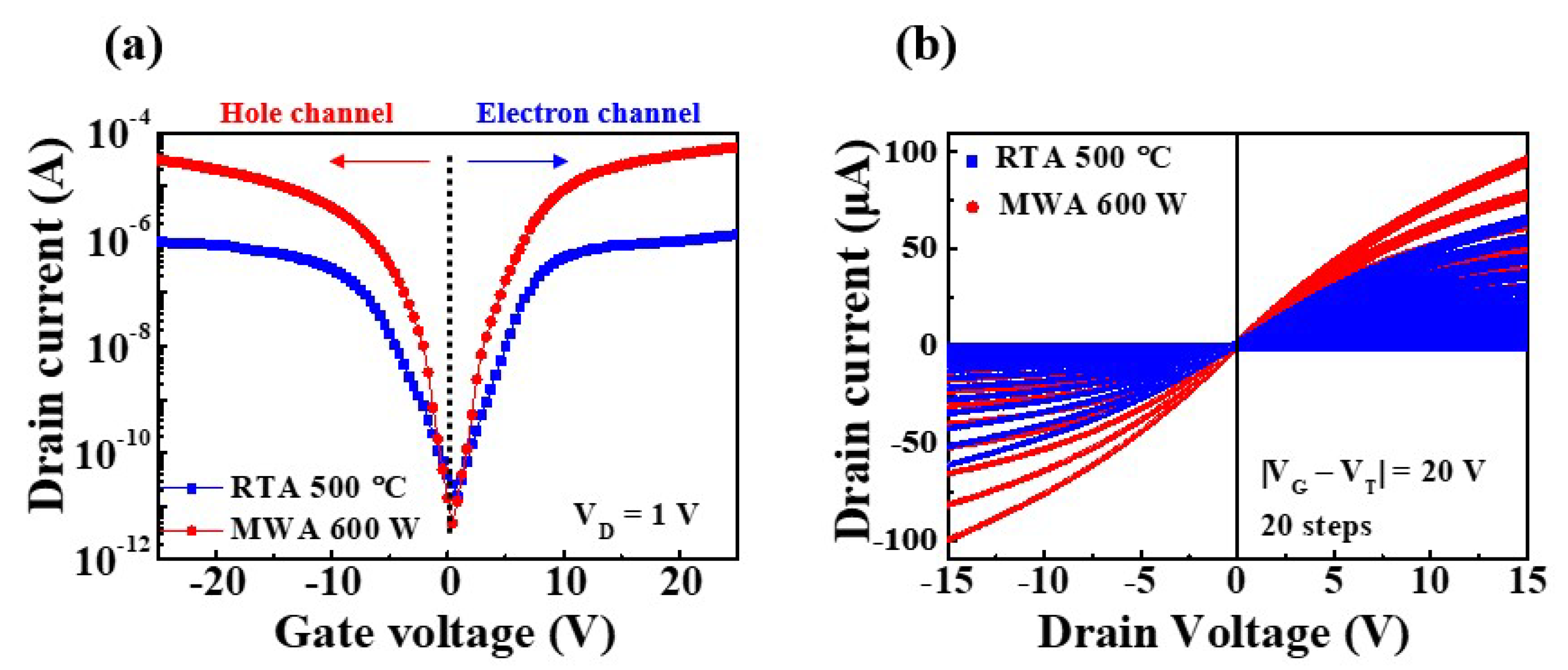

| p-type | MWA 600 W | 633.4 | 16.5 | 2.3 | 1.1 × 107 | 9.2 × 1012 |

| RTA 500 °C | 1201.1 | 4.9 | 3.4 | 7.2 × 104 | 1.8 × 1013 | |

| n-type | MWA 600 W | 629.2 | 20.3 | −1.4 | 6.8 × 106 | 9.1 × 1012 |

| RTA 500 °C | 1321.4 | 4.1 | −2.4 | 5.7 × 104 | 1.9 × 1013 | |

| Conduction | Silicidation | PBTS | NBTS | ||||

|---|---|---|---|---|---|---|---|

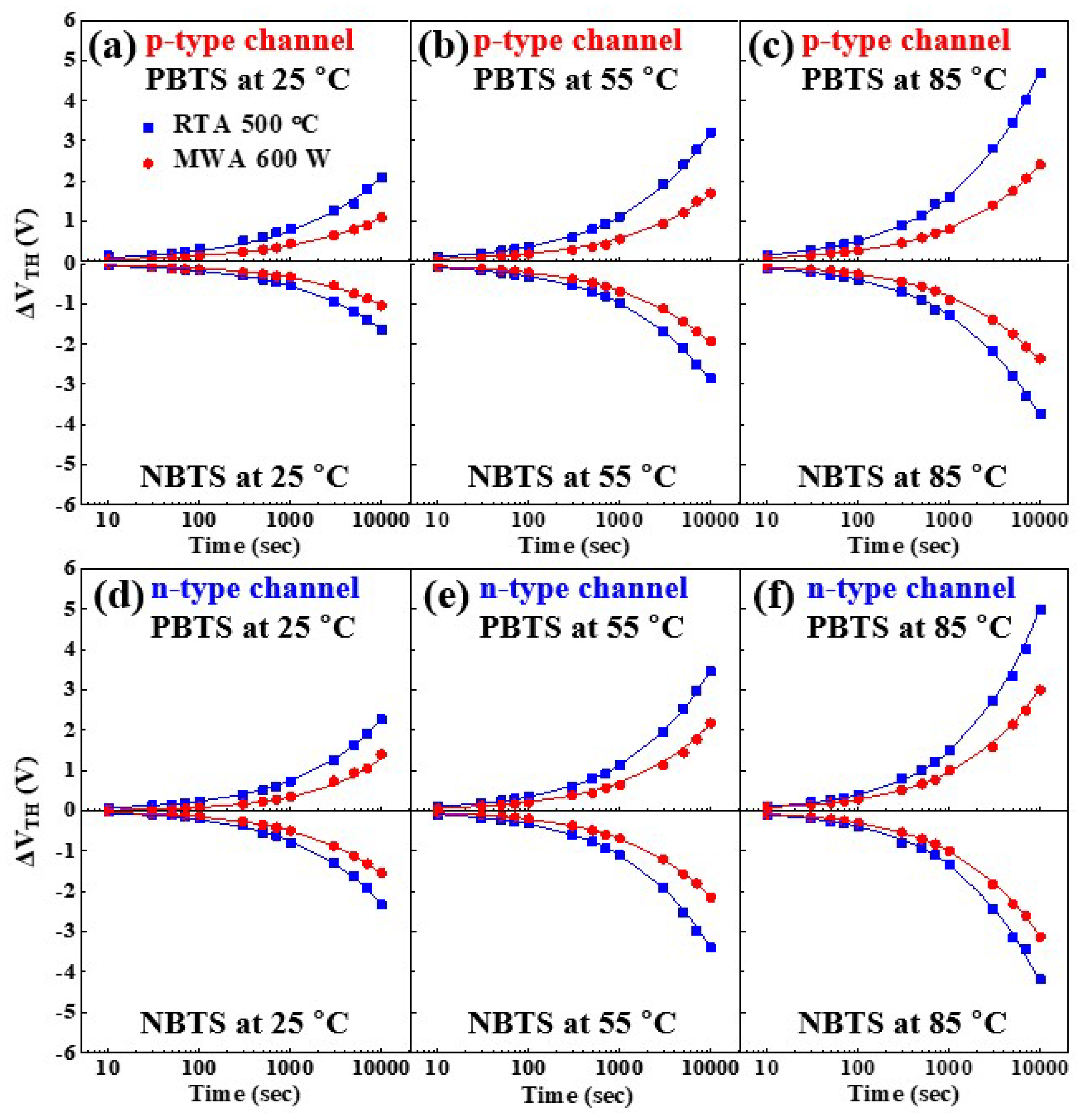

| 25 °C | 55 °C | 85 °C | 25 °C | 55 °C | 85 °C | ||

| p-type | MWA 600 W | 6.0 × 105 | 1.7 × 105 | 6.5 × 104 | 4.1 × 105 | 1.0 × 105 | 6.1 × 104 |

| RTA 500 °C | 1.2 × 105 | 3.5 × 104 | 1.4 × 104 | 1.6 × 105 | 4.1 × 104 | 2.1 × 104 | |

| n-type | MWA 600 W | 8.1 × 104 | 7.3 × 104 | 1.0 × 104 | 1.5 × 105 | 7.0 × 105 | 3.1 × 104 |

| RTA 500 °C | 7.0 × 104 | 2.4 × 104 | 8.6 × 103 | 7.0 × 104 | 2.5 × 104 | 1.5 × 104 | |

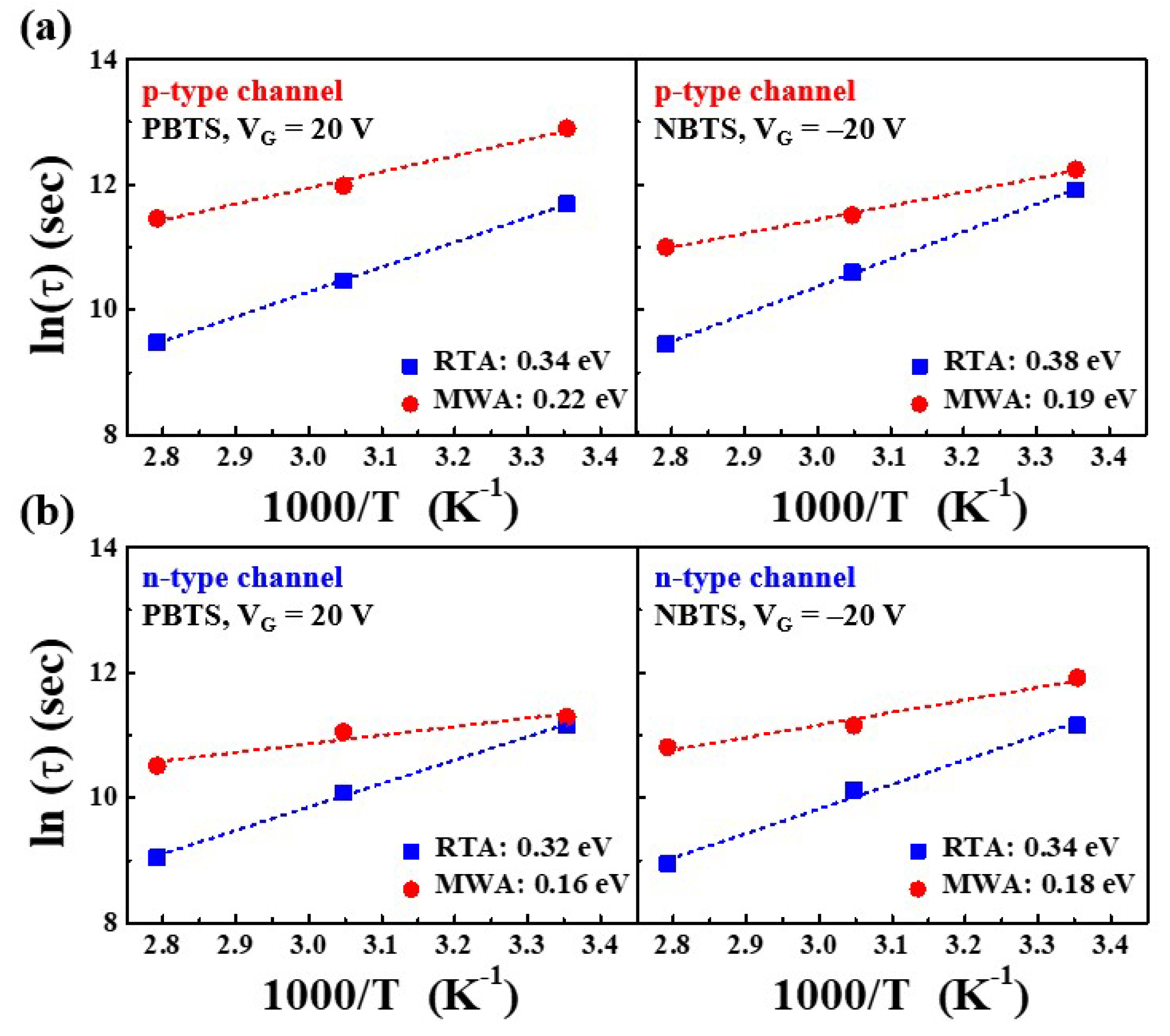

| Conduction | Silicidation | Average Effective Energy Barrier [eV] | |

|---|---|---|---|

| PBTS | NBTS | ||

| p-type | MWA 600 W | 0.22 | 0.19 |

| RTA 500 °C | 0.34 | 0.38 | |

| n-type | MWA 600 W | 0.16 | 0.18 |

| RTA 500 °C | 0.32 | 0.34 | |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Min, J.-G.; Lee, D.-H.; Kim, Y.-U.; Cho, W.-J. Implementation of Ambipolar Polysilicon Thin-Film Transistors with Nickel Silicide Schottky Junctions by Low-Thermal-Budget Microwave Annealing. Nanomaterials 2022, 12, 628. https://doi.org/10.3390/nano12040628

Min J-G, Lee D-H, Kim Y-U, Cho W-J. Implementation of Ambipolar Polysilicon Thin-Film Transistors with Nickel Silicide Schottky Junctions by Low-Thermal-Budget Microwave Annealing. Nanomaterials. 2022; 12(4):628. https://doi.org/10.3390/nano12040628

Chicago/Turabian StyleMin, Jin-Gi, Dong-Hee Lee, Yeong-Ung Kim, and Won-Ju Cho. 2022. "Implementation of Ambipolar Polysilicon Thin-Film Transistors with Nickel Silicide Schottky Junctions by Low-Thermal-Budget Microwave Annealing" Nanomaterials 12, no. 4: 628. https://doi.org/10.3390/nano12040628

APA StyleMin, J.-G., Lee, D.-H., Kim, Y.-U., & Cho, W.-J. (2022). Implementation of Ambipolar Polysilicon Thin-Film Transistors with Nickel Silicide Schottky Junctions by Low-Thermal-Budget Microwave Annealing. Nanomaterials, 12(4), 628. https://doi.org/10.3390/nano12040628