Area and Performance Estimates of Finite State Machines in Reconfigurable Systems

Abstract

1. Introduction

- Several area and performance estimates of FSMs, as well as estimates that are not directly related to the computation of the area or performance estimates of FSMs, are presented;

- For each estimate, and the expressions and algorithm for its computation are given;

- The efficiency of the estimates is verified on benchmarks of FSMs using the estimates in the sequential method of FSM state encoding [8];

- A comparison of different estimates was performed to determine their efficiency for optimizing the area and performance of FSMs;

- It has been shown that the use of the considered estimates in the method [8] allows to obtain solutions on average better in comparison with known methods;

- Recommendations on the practical use of the proposed estimates are given.

2. Related Works

- In addition, in [16], the lower delay bound is defined by inequality (9), and the upper delay bound is defined by inequality (10):

- In [17], when implementing FSMs in LUT-based FPGAs, the state number minimization method uses area, delay, and power consumption estimates. Here, the area of function f is calculated using expression (11), and the delay is calculated using expression (12):

3. Materials and Methods

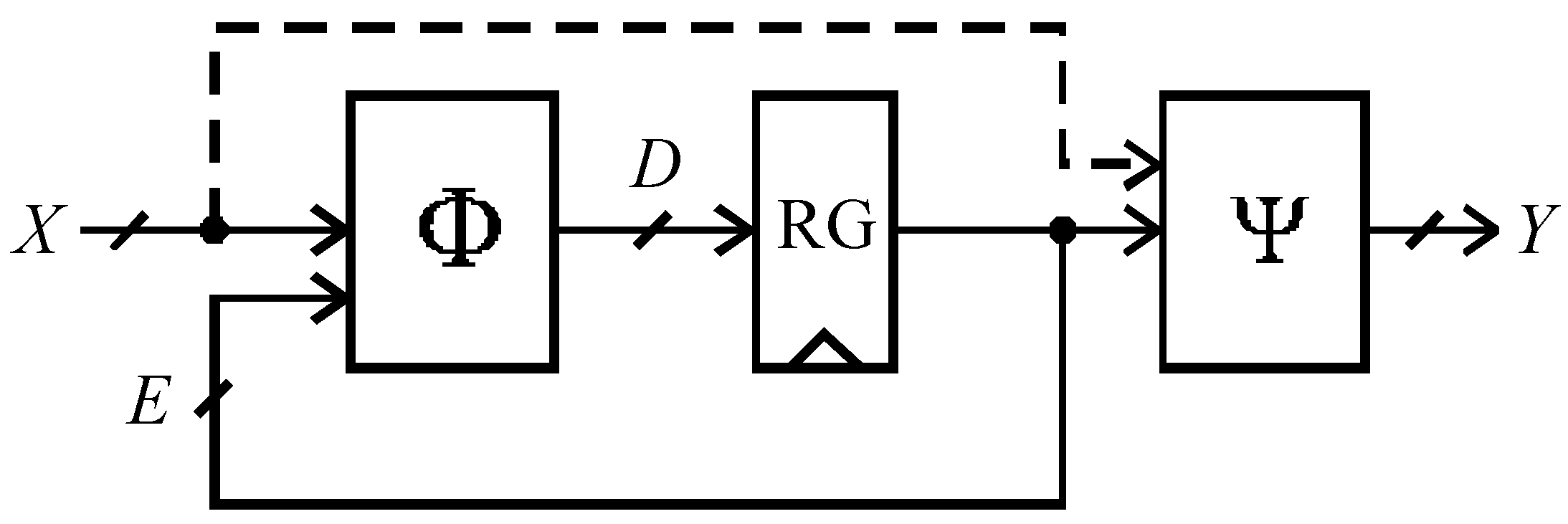

3.1. Representation of FSMs

3.2. Estimates of FSMs

3.2.1. Area Estimates

| Algorithm 1. Calculation of e_FPGA estimate. |

| INPUT: transition list. |

| OUTPUT: area. |

| area = 0; |

| for all r = 0 to R − 1 do // loop by transition functions of set D |

| X(dr) = Ø; // define the set X(dr), Ø is an empty set |

| for all t = 0 to T − 1 do // loop by FSM transitions |

| if K(nst,r) = 1 then // code K(nst,r) has one in bit r |

| for all j = 0 to L − 1 do // loop by input variables |

| if X(t,j) = 1 or X(t,j) = 0 then // xj affects the transition t |

| X(dr) = X(dr) U {xj}; // include xj in the set X(dr) |

| end if |

| end for |

| end if |

| end for |

| rank(dr) = |X(dr)| + R; // determine the rank of the function dr |

| if (rank(dr) <= n) then // calculate the area of the function dr |

| area(dr) = 1; |

| else |

| ; |

| end if |

| area = area + area(dr); // increasing the total area |

| end for |

| Return area. |

| Algorithm 2. Calculation of the e_CPLD estimate. |

| INPUT: transition list. OUTPUT: area. area = 0; for all r = 0 to R − 1 do // loop by transition functions of the set D area(dr) = 0; // determine the area of the function dr for all t = 0 to T − 1 do // loop by FSM transitions if K(nst,r) = 1 then // nst state code contains 1 area(dr) = area(dr) + 1; // increase the area of the function dr end if end for area = area + area(dr); // increasing the total area end for Return (area). |

| Algorithm 3. Calculation of the classic estimate. |

| INPUT: transition list. OUTPUT: area. area = 0; for all r = 0 to R − 1 do // loop on transition functions of the set D area(dr) = 0; // determine the estimate of the function dr for all t = 0 to T−1 do // loop by transitions of a finite automaton if K(nst,r) = 1 then // state code nst contains 1 area(dr) = area(dr) + 1; // count the number of minterms X(pt) = Ø; // define the set X(pt) for all j = 0 to L − 1 do if X(t,j) = 1 or X(t,j) = 0 then // xj affects the transition t X(pt) = X(pt) U {xj}; // xj is included in X(pt) end if end for area(dr) = area(dr) + | X(pt) | + R; // increase area(dr) end if area = area + area(dr); // increase the total area end for Return area. |

| Algorithm 4. Calculation of the terms estimate. |

| INPUT: transition list. OUTPUT: area. area = 0; for all r = 0 to R − 1 do // loop on transition functions of the set D area(dr) = 0; // determine the estimate of the function dr for all t = 0 to T − 1 do // loop by transitions of the FSM if K(nst,r) = end if end for else end if ); // increase area(dr) end if area = area + area(dr); // increase the total area end for end for Return area. |

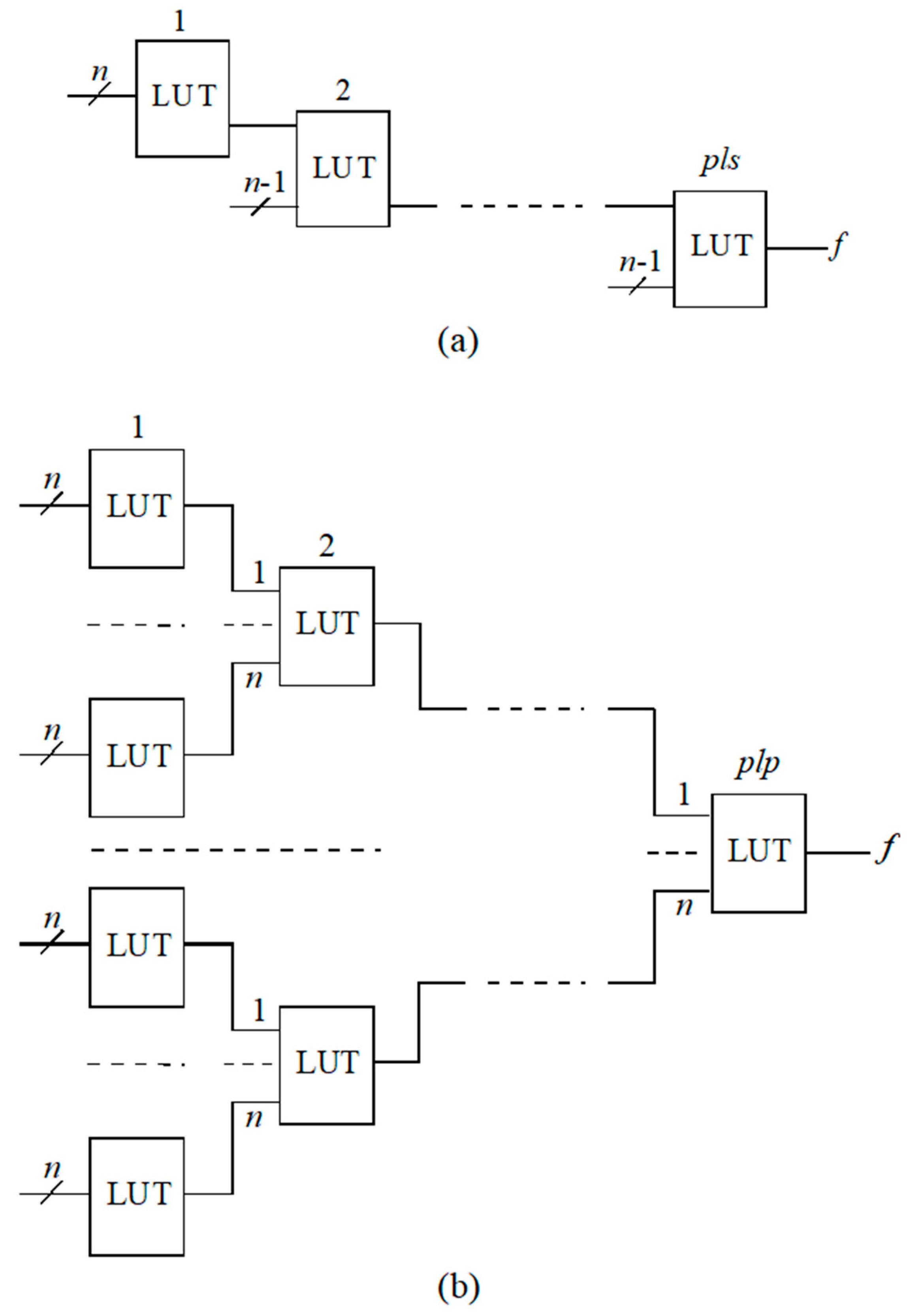

3.2.2. Performance Estimates

| Algorithm 5. Calculation of the seq_dec estimate. |

| INPUT: transition list. OUTPUT: cpl. cpl = 0; for all r = 0 to R − ; Determine the set X(dr) as in Algorithm 1; rank(dr) = |X(dr)| + R; // determine the rank of the function dr if rank(dr) <= n then // calculate the path length pls(dr) of the function dr pls(dr) = 1; else pls(dr) = ⌈(rang(dr) − n)/(n − 1)⌉; end if if pls(dr) > cpl then // determine the length of the critical path cpl = pls(dr); end if end for Return cpl. |

| Algorithm 6. Calculation of the par_dec estimate. |

| INPUT: transition list. OUTPUT: cpl. cpl = 0; for all r = 0 to R − Determine the set X(dr) as in Algorithm 1; rank(dr) = |X(dr)| + R; // determine the rank of the function dr plp(dr) = ⌈log(rang(dr))/logn⌉; // calculate the path length plp(dr) for dr if (plp(dr) > cpl) then // determine the length of the critical path cpl = plp(dr); end if end for Return cpl. |

3.2.3. Other Estimates for FSMs

| Algorithm 7. Calculation of the diff_w estimate. |

| INPUT: transition list. OUTPUT: max(w(dr)) − min(w(dr)). for all i = 0 to M − 1 do // determine the set of values C(si) C(si) = 0; // determine the number of transitions to the state si for all t = 0 to T − 1 do if nst = si then C(si) = C(si) + 1; end if end for end for for all r = 0 to R − 1 do // determine weights of functions dr w(dr) = 0; for all i = 0 to M − 1 do // loop on the FSM states if K(si,r) = 1 then // state code si has 1 in bit r w(dr) = w(dr) + C(si); end if end for end for max_w = −1; min_w = 10,000; // find the maximum and minimum values of weight for all r = 0 to R−1 do // loop by weights of functions dr if w(dr) > max_w then max_w = w(dr) end if if w(dr) < min_w then min_w = w(dr) end if end for Return (max_w − min_w); |

| Algorithm 8. Calculation of the max_w estimate. |

| INPUT: transition list. OUTPUT: max(w(dr)). Determine the set of values C(si), si ∈ S, as in Algorithm 7; Determine the weights w(dr) of functions dr, dr ∈ D, as in Algorithm 7; max_w = −1; // find the maximum value of weight for all r = 0 to R − 1 do // loop by weights of functions dr if w(dr) > max_w then max_w = w(dr); end if end for Return max_w. |

3.3. Example of Calculating FSM Evaluations

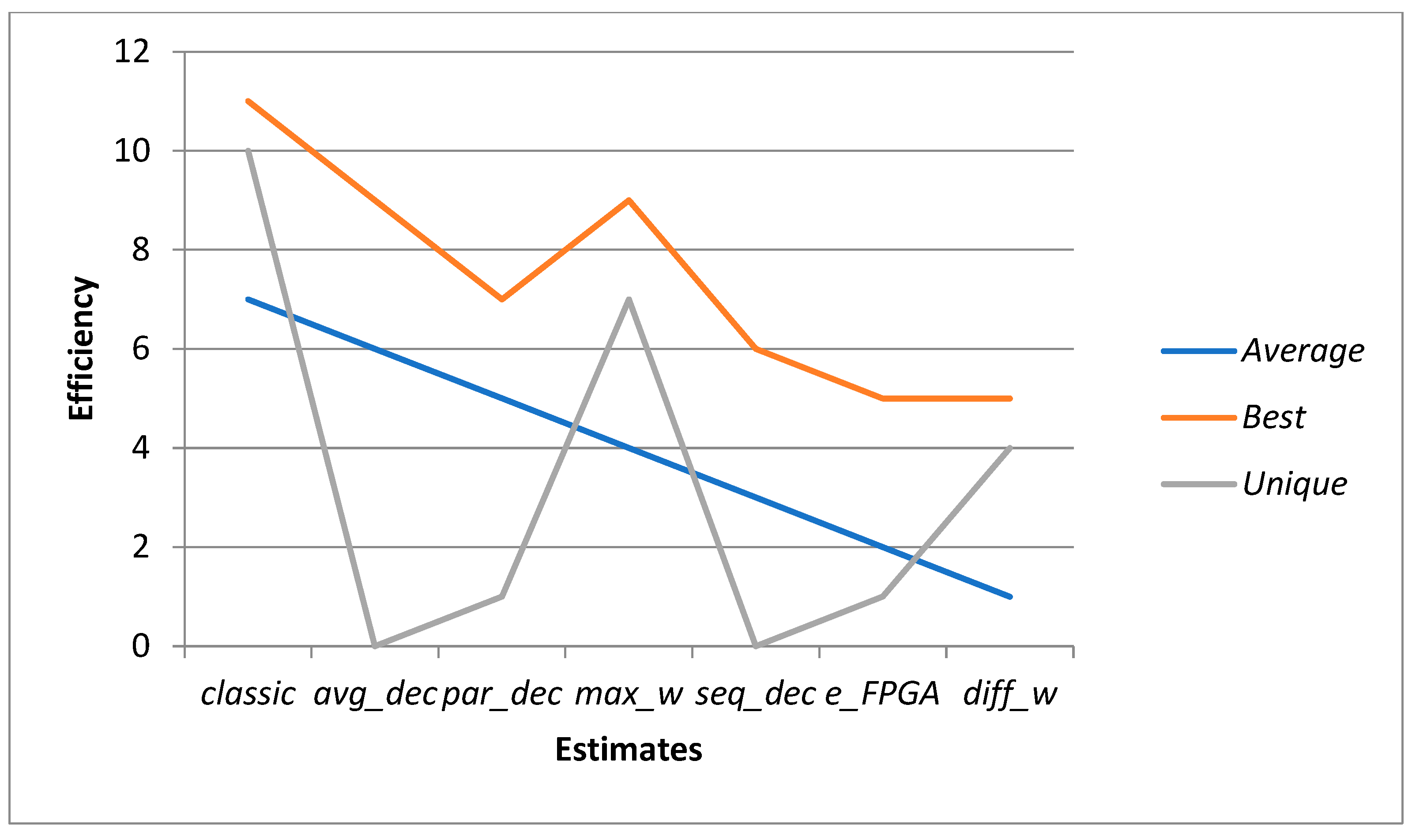

4. Results and Discussions

4.1. Results with Respect to the FSM Area

4.2. Results with Respect to the FSM Performance

4.3. Comparison of the Sequential State Coding Method Using Presented Estimates with Known Methods

5. Conclusions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Göhringer, D.; Podlubne, A.; Vargas, F.; Krstic, M. Self-Aware Reliable and Reconfigurable Computing Systems—An Overview. In Proceedings of the IEEE International Parallel and Distributed Processing Symposium Workshops (IPDPSW), San Francisco, CA, USA, 27–31 May 2024; pp. 124–129. [Google Scholar] [CrossRef]

- Badhoutiya, A.; Jaffer, Z.; Hussein, H.M.; Juyal, A.; Mittal, M.; Anand, R. Field Programmable Gate Array: An Extensive Review, Recent Trends, Challenges and Applications. In Proceedings of the 11th International Conference on Computing for Sustainable Global Development (INDIACom), New Delhi, India, 28 February 2024; pp. 1084–1090. [Google Scholar] [CrossRef]

- Barkalov, A.; Titarenko, L.; Mielcarek, K.; Mazurkiewicz, M. Hardware reduction for FSMs with extended state codes. IEEE Access 2024, 12, 42369–42384. [Google Scholar] [CrossRef]

- Salauyou, V.; Borecki, D.; Grzes, T. The Synthesis Method of High-Performance Finite State Machines in FPGA. In Proceedings of the Computer Information Systems and Industrial Management: 19th International Conference (CISIM 2020), Bialystok, Poland, 16–18 October 2020; pp. 97–107. [Google Scholar] [CrossRef]

- Grzes, T.N.; Solov’ev, V.V. Minimization of power consumption of finite state machines by splitting their internal states. J. Comput. Syst. Sci. Int. 2015, 54, 367–374. [Google Scholar] [CrossRef]

- Anderson, J.H.; Najm, F.N. Power estimate techniques for FPGAs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2004, 12, 1015–1027. [Google Scholar] [CrossRef]

- Goeders, J.B.; Wilton, S.J. VersaPower: Power estimate for diverse FPGA architectures. In Proceedings of the International Conference on Field-Programmable Technology, Seoul, Republic of Korea, 10–12 December 2012; pp. 229–234. [Google Scholar] [CrossRef]

- Salauyou, V.; Bułatow, W. Optimized Sequential State Encoding Methods for Finite-State Machines in Field-Programmable Gate Array Implementations. Appl. Sci. 2024, 14, 5594. [Google Scholar] [CrossRef]

- Brayton, R.K.; Rudell, R.; Sangiovanni-Vincentelli, A.; Wang, A.R. MIS: A multiple-level logic optimization system. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 1987, 6, 1062–1081. [Google Scholar] [CrossRef]

- Legl, C.; Wurth, B.; Eckl, K. A Boolean approach to performance-directed technology mapping for LUT-based FPGA designs. In Proceedings of the 33rd annual Design Automation Conference, Las Vegas, NV, USA, 3–7 June 1996; pp. 730–733. [Google Scholar] [CrossRef]

- Huang, J.D.; Jou, J.Y.; Shen, W.Z. ALTO: An iterative area/performance tradeoff algorithm for LUT-based FPGA technology mapping. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2000, 8, 392–400. [Google Scholar] [CrossRef]

- Yamashita, S.; Sawada, H.; Nagoya, A. An efficient framework of using various decomposition methods to synthesize LUT networks and its evaluation. In Proceedings of the Asia and South Pacific Design Automation Conference, Yokohama, Japan, 25–28 January 2000; pp. 253–258. [Google Scholar] [CrossRef]

- Calvino, A.T.; De Micheli, G.; Mishchenko, A.; Brayton, R. Enhancing Delay-Driven LUT Mapping with Boolean Decomposition. IEEE Trans. Comput.-Aided Des. Integr. Circuits Syst. 2024, in press. [Google Scholar] [CrossRef]

- Deniziak, S.; Wisniewski, M. A symbolic RTL synthesis for LUT-based FPGAs. In Proceedings of the 12th International Symposium on Design and Diagnostics of Electronic Circuits & Systems, Liberec, Czech Republic, 15–17 April 2009; pp. 102–107. [Google Scholar] [CrossRef]

- Hamed, B.A.; Salem, A.; Aly, G.M. Area estimate of LUT based designs. In Proceedings of the International Conference on Electrical, Electronic and Computer Engineering (ICEEC’04), Cairo, Egypt, 5–7 September 2004; pp. 39–42. [Google Scholar] [CrossRef]

- Atasu, K.; Todman, T.; Mencer, O.; Luk, W. Optimal implementation of combinational logic on look-up tables. In Proceedings of the Ph.D. Research in Microelectronics and Electronics, Istanbul, Turkey, 22 June 2008; pp. 153–156. [Google Scholar] [CrossRef]

- Klimowicz, A. Balanced Power, Performance and Area Transformation Procedure for Finite State Machines. In Proceedings of the IEEE International Conference on Systems, Man, and Cybernetics (SMC), Prague, Czech Republic, 9–12 October 2022; pp. 2313–2318. [Google Scholar] [CrossRef]

- Burgun, L.; Dictus, N.; Lopes, E.P.; Sarwary, C. A unified approach for FSM synthesis on FPGA architectures. In Proceedings of the Twentieth Euromicro Conference. System Architecture and Integration, Liverpool, UK, 8 September 1994; pp. 660–668. [Google Scholar] [CrossRef]

- Kubica, M.; Kania, D.; Kulisz, J. A technology mapping of FSMs based on a graph of excitations and outputs. IEEE Access 2019, 7, 16123–16131. [Google Scholar] [CrossRef]

- Yang, S. Logic Synthesis and Optimization Benchmarks User Guide; Version 3.0; Microelectronics Center of North Carolina (MCNC): Research Triangle Park, NC, USA, 1991; Available online: https://ddd.fit.cvut.cz/www/prj/Benchmarks/LGSynth91.pdf (accessed on 13 December 2024).

- Lin, B.; Newton, A.R. Synthesis of multiple level logic from symbolic high-level description languages. In Proceedings of the IFIP International Conference on VLSI, Munich, Germany, 16–18 August 1989; North-Holland: New York, NY, USA, 1989; pp. 187–196. [Google Scholar]

| t | pst | Xt | nst | Yt |

|---|---|---|---|---|

| 0 | s0 | --- | s1 | 001 |

| 1 | s1 | --0 | s2 | 110 |

| 2 | s1 | -01 | s3 | 101 |

| 3 | s1 | 011 | s4 | 100 |

| 4 | s1 | 111 | s5 | 010 |

| 5 | s2 | 0-- | s4 | 100 |

| 6 | s2 | 1-- | s5 | 010 |

| 7 | s3 | --- | s0 | 100 |

| 8 | s4 | --- | s0 | 000 |

| 9 | s5 | --- | s0 | 000 |

| Estimates | L | M | T | R | n |

|---|---|---|---|---|---|

| e_FPGA | + | - | - | + | + |

| e_CPLD | - | - | + | + | - |

| classic | + | - | + | + | - |

| terms | + | - | + | + | + |

| seq_dec | + | - | - | + | + |

| par_dec | + | - | - | + | + |

| avg_dec | + | - | - | + | + |

| diff_w | - | + | + | + | - |

| max_w | - | + | + | + | - |

| t | pst | K(pst) e2e1e0 | Xt x2x1x0 | nst | K(nst) d2d1d0 | Yt y2y1y0 |

|---|---|---|---|---|---|---|

| 0 | s0 | 000 | --- | s1 | 001 | 001 |

| 1 | s1 | 001 | --0 | s2 | 010 | 110 |

| 2 | s1 | 001 | -01 | s3 | 011 | 101 |

| 3 | s1 | 001 | 011 | s4 | 100 | 100 |

| 4 | s1 | 001 | 111 | s5 | 101 | 010 |

| 5 | s2 | 010 | 0-- | s4 | 100 | 100 |

| 6 | s2 | 010 | 1-- | s5 | 101 | 010 |

| 7 | s3 | 011 | --- | s4 | 100 | 100 |

| 8 | s4 | 100 | --- | s0 | 000 | 000 |

| 9 | s5 | 101 | --- | s0 | 000 | 000 |

| e_FPGA | e_CPLD | classic | terms | |

|---|---|---|---|---|

| area(d0) | 2 | 4 | 22 | 6 |

| area(d1) | 2 | 2 | 11 | 3 |

| area(d2) | 2 | 5 | 23 | 7 |

| area | 6 | 11 | 56 | 16 |

| rank(dr) | seq_dec | par_dec | avg_dec | |

|---|---|---|---|---|

| pls/plp(d0) | 6 | 2 | 2 | 2 |

| pls/plp(d1) | 5 | 2 | 2 | 2 |

| pls/plp(d2) | 6 | 2 | 2 | 2 |

| cpl | 2 | 2 | 2 |

| FSM | e_FPGA L1 | classic L2 | diff_w L3 | max_w L4 | seq_dec L5 | par_dec L6 | avg_dec L7 | Lmin |

|---|---|---|---|---|---|---|---|---|

| bbara | 32 | 26 | 37 | 28 | 32 | 32 | 32 | 26 |

| bbsse | 61 | 61 | 65 | 54 | 57 | 66 | 57 | 54 |

| beecount | 18 | 19 | 20 | 19 | 18 | 18 | 18 | 18 |

| cse | 86 | 83 | 85 | 80 | 86 | 86 | 86 | 80 |

| dk14 | 48 | 40 | 45 | 45 | 48 | 48 | 48 | 40 |

| dk15 | 15 | 15 | 14 | 15 | 15 | 15 | 15 | 14 |

| dk16 | 86 | 86 | 87 | 115 | 86 | 86 | 86 | 86 |

| dk17 | 12 | 13 | 12 | 21 | 12 | 12 | 12 | 12 |

| dk512 | 15 | 15 | 18 | 14 | 15 | 15 | 15 | 14 |

| ex1 | 109 | 108 | 112 | 103 | 109 | 106 | 106 | 103 |

| ex4 | 33 | 31 | 41 | 30 | 33 | 33 | 33 | 30 |

| ex5 | 18 | 20 | 26 | 21 | 18 | 18 | 18 | 18 |

| ex6 | 55 | 58 | 52 | 53 | 55 | 55 | 55 | 52 |

| ex7 | 20 | 23 | 36 | 26 | 20 | 20 | 20 | 20 |

| keyb | 73 | 72 | 100 | 75 | 73 | 73 | 73 | 72 |

| lion9 | 11 | 15 | 22 | 13 | 11 | 11 | 11 | 11 |

| planet | 199 | 201 | 203 | 199 | 195 | 190 | 195 | 190 |

| planet1 | 199 | 201 | 203 | 199 | 195 | 190 | 195 | 190 |

| pma | 148 | 153 | 149 | 154 | 162 | 141 | 162 | 141 |

| s1 | 190 | 146 | 180 | 147 | 190 | 190 | 190 | 146 |

| s1488 | 228 | 226 | 227 | 237 | 220 | 220 | 220 | 220 |

| s1494 | 218 | 234 | 223 | 226 | 223 | 223 | 223 | 218 |

| s298 | 929 | 954 | 1075 | 991 | 929 | 929 | 929 | 929 |

| s386 | 54 | 48 | 60 | 55 | 56 | 56 | 56 | 48 |

| s510 | 136 | 143 | 155 | 149 | 130 | 103 | 103 | 103 |

| s820 | 132 | 129 | 144 | 130 | 129 | 132 | 132 | 129 |

| s832 | 132 | 133 | 144 | 129 | 134 | 131 | 131 | 129 |

| sand | 199 | 231 | 228 | 220 | 199 | 199 | 199 | 199 |

| sse | 61 | 61 | 65 | 54 | 57 | 66 | 57 | 54 |

| styr | 190 | 186 | 183 | 186 | 190 | 190 | 190 | 183 |

| tbk | 274 | 265 | 273 | 262 | 274 | 274 | 274 | 262 |

| tma | 98 | 96 | 96 | 93 | 99 | 98 | 99 | 93 |

| train11 | 28 | 25 | 25 | 30 | 28 | 28 | 28 | 25 |

| Best | 9 | 8 | 5 | 9 | 10 | 13 | 10 | |

| Unique | 1 | 5 | 3 | 9 | 0 | 3 | 0 |

| FSM | e_FPGA L1/Lmin | classic L2/Lmin | diff_w L3/Lmin | max_w L4/Lmin | seq_dec L5/Lmin | par_dec L6/Lmin | avg_dec L7/Lmin |

|---|---|---|---|---|---|---|---|

| bbara | 1.231 | 1.000 | 1.423 | 1.077 | 1.231 | 1.231 | 1.231 |

| bbsse | 1.130 | 1.130 | 1.204 | 1.000 | 1.056 | 1.222 | 1.056 |

| beecount | 1.000 | 1.056 | 1.111 | 1.056 | 1.000 | 1.000 | 1.000 |

| cse | 1.075 | 1.038 | 1.063 | 1.000 | 1.075 | 1.075 | 1.075 |

| dk14 | 1.200 | 1.000 | 1.125 | 1.125 | 1.200 | 1.200 | 1.200 |

| dk15 | 1.071 | 1.071 | 1.000 | 1.071 | 1.071 | 1.071 | 1.071 |

| dk16 | 1.000 | 1.000 | 1.012 | 1.337 | 1.000 | 1.000 | 1.000 |

| dk17 | 1.000 | 1.083 | 1.000 | 1.750 | 1.000 | 1.000 | 1.000 |

| dk512 | 1.071 | 1.071 | 1.286 | 1.000 | 1.071 | 1.071 | 1.071 |

| ex1 | 1.058 | 1.049 | 1.087 | 1.000 | 1.058 | 1.029 | 1.029 |

| ex4 | 1.100 | 1.033 | 1.367 | 1.000 | 1.100 | 1.100 | 1.100 |

| ex5 | 1.000 | 1.111 | 1.444 | 1.167 | 1.000 | 1.000 | 1.000 |

| ex6 | 1.058 | 1.115 | 1.000 | 1.019 | 1.058 | 1.058 | 1.058 |

| ex7 | 1.000 | 1.150 | 1.800 | 1.300 | 1.000 | 1.000 | 1.000 |

| keyb | 1.014 | 1.000 | 1.389 | 1.042 | 1.014 | 1.014 | 1.014 |

| lion9 | 1.000 | 1.364 | 2.000 | 1.182 | 1.000 | 1.000 | 1.000 |

| planet | 1.047 | 1.058 | 1.068 | 1.047 | 1.026 | 1.000 | 1.026 |

| planet1 | 1.047 | 1.058 | 1.068 | 1.047 | 1.026 | 1.000 | 1.026 |

| pma | 1.050 | 1.085 | 1.057 | 1.092 | 1.149 | 1.000 | 1.149 |

| s1 | 1.301 | 1.000 | 1.233 | 1.007 | 1.301 | 1.301 | 1.301 |

| s1488 | 1.036 | 1.027 | 1.032 | 1.077 | 1.000 | 1.000 | 1.000 |

| s1494 | 1.000 | 1.073 | 1.023 | 1.037 | 1.023 | 1.023 | 1.023 |

| s298 | 1.000 | 1.027 | 1.157 | 1.067 | 1.000 | 1.000 | 1.000 |

| s386 | 1.125 | 1.000 | 1.250 | 1.146 | 1.167 | 1.167 | 1.167 |

| s510 | 1.320 | 1.388 | 1.505 | 1.447 | 1.262 | 1.000 | 1.000 |

| s820 | 1.023 | 1.000 | 1.116 | 1.008 | 1.000 | 1.023 | 1.023 |

| s832 | 1.023 | 1.031 | 1.116 | 1.000 | 1.039 | 1.016 | 1.016 |

| sand | 1.000 | 1.161 | 1.146 | 1.106 | 1.000 | 1.000 | 1.000 |

| sse | 1.130 | 1.130 | 1.204 | 1.000 | 1.056 | 1.222 | 1.056 |

| styr | 1.038 | 1.016 | 1.000 | 1.016 | 1.038 | 1.038 | 1.038 |

| tbk | 1.046 | 1.011 | 1.042 | 1.000 | 1.046 | 1.046 | 1.046 |

| tma | 1.054 | 1.032 | 1.032 | 1.000 | 1.065 | 1.054 | 1.065 |

| train11 | 1.120 | 1.000 | 1.000 | 1.200 | 1.120 | 1.120 | 1.120 |

| Av | 1.072 | 1.072 | 1.193 | 1.104 | 1.068 | 1.063 | 1.059 |

| FSM | e_FPGA F1 | classic F2 | diff_w F3 | max_w F4 | seq_dec F5 | par_dec F6 | avg_dec F7 | Fmax |

|---|---|---|---|---|---|---|---|---|

| bbara | 430 | 529 | 414 | 453 | 430 | 430 | 430 | 529 |

| bbsse | 324 | 335 | 321 | 349 | 357 | 320 | 357 | 357 |

| beecount | 633 | 632 | 601 | 632 | 633 | 633 | 633 | 633 |

| cse | 298 | 323 | 300 | 322 | 298 | 298 | 298 | 323 |

| dk14 | 457 | 423 | 576 | 479 | 457 | 457 | 457 | 576 |

| dk15 | 869 | 869 | 796 | 869 | 869 | 869 | 869 | 869 |

| dk16 | 375 | 371 | 398 | 262 | 375 | 375 | 375 | 398 |

| dk17 | 648 | 712 | 711 | 647 | 648 | 648 | 648 | 712 |

| dk512 | 578 | 640 | 639 | 654 | 578 | 578 | 578 | 654 |

| ex1 | 317 | 307 | 307 | 320 | 317 | 339 | 339 | 339 |

| ex4 | 464 | 545 | 393 | 496 | 464 | 464 | 464 | 545 |

| ex5 | 504 | 521 | 505 | 480 | 504 | 504 | 504 | 521 |

| ex6 | 384 | 358 | 408 | 381 | 384 | 384 | 384 | 408 |

| ex7 | 472 | 551 | 383 | 487 | 472 | 472 | 472 | 551 |

| keyb | 328 | 335 | 273 | 341 | 329 | 329 | 329 | 341 |

| lion9 | 636 | 587 | 461 | 606 | 636 | 636 | 636 | 636 |

| planet | 243 | 236 | 234 | 249 | 235 | 239 | 235 | 249 |

| planet1 | 243 | 236 | 234 | 249 | 235 | 239 | 235 | 249 |

| pma | 223 | 245 | 246 | 265 | 249 | 277 | 249 | 277 |

| s1 | 241 | 255 | 256 | 256 | 241 | 241 | 241 | 256 |

| s1488 | 235 | 239 | 223 | 233 | 227 | 227 | 227 | 239 |

| s1494 | 219 | 234 | 206 | 228 | 232 | 232 | 232 | 234 |

| s298 | 128 | 121 | 126 | 122 | 128 | 128 | 128 | 128 |

| s386 | 343 | 368 | 315 | 372 | 357 | 357 | 357 | 372 |

| s510 | 250 | 246 | 226 | 241 | 233 | 303 | 303 | 303 |

| s820 | 243 | 239 | 233 | 230 | 231 | 247 | 247 | 247 |

| s832 | 229 | 246 | 262 | 264 | 250 | 234 | 234 | 264 |

| sand | 244 | 230 | 226 | 229 | 244 | 244 | 244 | 244 |

| sse | 324 | 335 | 321 | 349 | 357 | 320 | 357 | 357 |

| styr | 241 | 242 | 230 | 250 | 241 | 241 | 241 | 250 |

| tbk | 192 | 206 | 199 | 188 | 192 | 192 | 192 | 206 |

| tma | 290 | 315 | 284 | 290 | 287 | 290 | 287 | 315 |

| train11 | 435 | 451 | 518 | 469 | 435 | 435 | 435 | 518 |

| Best | 5 | 11 | 5 | 9 | 6 | 7 | 9 | |

| Unique | 1 | 10 | 4 | 7 | 0 | 1 | 0 |

| FSM | e_FPGA Fmax/F1 | classic Fmax/F2 | diff_w Fmax/F3 | max_w Fmax/F4 | seq_dec Fmax/F5 | par_dec Fmax/F6 | avg_dec Fmax/F7 |

|---|---|---|---|---|---|---|---|

| bbara | 1.230 | 1.000 | 1.278 | 1.168 | 1.230 | 1.230 | 1.230 |

| bbsse | 1.102 | 1.066 | 1.112 | 1.023 | 1.000 | 1.116 | 1.000 |

| beecount | 1.000 | 1.002 | 1.053 | 1.002 | 1.000 | 1.000 | 1.000 |

| cse | 1.084 | 1.000 | 1.077 | 1.003 | 1.084 | 1.084 | 1.084 |

| dk14 | 1.260 | 1.362 | 1.000 | 1.203 | 1.260 | 1.260 | 1.260 |

| dk15 | 1.000 | 1.000 | 1.092 | 1.000 | 1.000 | 1.000 | 1.000 |

| dk16 | 1.061 | 1.073 | 1.000 | 1.519 | 1.061 | 1.061 | 1.061 |

| dk17 | 1.099 | 1.000 | 1.001 | 1.100 | 1.099 | 1.099 | 1.099 |

| dk512 | 1.131 | 1.022 | 1.023 | 1.000 | 1.131 | 1.131 | 1.131 |

| ex1 | 1.069 | 1.104 | 1.104 | 1.059 | 1.069 | 1.000 | 1.000 |

| ex4 | 1.175 | 1.000 | 1.387 | 1.099 | 1.175 | 1.175 | 1.175 |

| ex5 | 1.034 | 1.000 | 1.032 | 1.085 | 1.034 | 1.034 | 1.034 |

| ex6 | 1.063 | 1.140 | 1.000 | 1.071 | 1.063 | 1.063 | 1.063 |

| ex7 | 1.167 | 1.000 | 1.439 | 1.131 | 1.167 | 1.167 | 1.167 |

| keyb | 1.040 | 1.018 | 1.249 | 1.000 | 1.036 | 1.036 | 1.036 |

| lion9 | 1.000 | 1.083 | 1.380 | 1.050 | 1.000 | 1.000 | 1.000 |

| planet | 1.025 | 1.055 | 1.064 | 1.000 | 1.060 | 1.042 | 1.060 |

| planet1 | 1.025 | 1.055 | 1.064 | 1.000 | 1.060 | 1.042 | 1.060 |

| pma | 1.242 | 1.131 | 1.126 | 1.045 | 1.112 | 1.000 | 1.112 |

| s1 | 1.062 | 1.004 | 1.000 | 1.000 | 1.062 | 1.062 | 1.062 |

| s1488 | 1.017 | 1.000 | 1.072 | 1.026 | 1.053 | 1.053 | 1.053 |

| s1494 | 1.068 | 1.000 | 1.136 | 1.026 | 1.009 | 1.009 | 1.009 |

| s298 | 1.000 | 1.058 | 1.016 | 1.049 | 1.000 | 1.000 | 1.000 |

| s386 | 1.085 | 1.011 | 1.181 | 1.000 | 1.042 | 1.042 | 1.042 |

| s510 | 1.212 | 1.232 | 1.341 | 1.257 | 1.300 | 1.000 | 1.000 |

| s820 | 1.016 | 1.033 | 1.060 | 1.074 | 1.069 | 1.000 | 1.000 |

| s832 | 1.153 | 1.073 | 1.008 | 1.000 | 1.056 | 1.128 | 1.128 |

| sand | 1.000 | 1.061 | 1.080 | 1.066 | 1.000 | 1.000 | 1.000 |

| sse | 1.102 | 1.066 | 1.112 | 1.023 | 1.000 | 1.116 | 1.000 |

| styr | 1.037 | 1.033 | 1.087 | 1.000 | 1.037 | 1.037 | 1.037 |

| tbk | 1.073 | 1.000 | 1.035 | 1.096 | 1.073 | 1.073 | 1.073 |

| tma | 1.086 | 1.000 | 1.109 | 1.086 | 1.098 | 1.086 | 1.098 |

| train11 | 1.191 | 1.149 | 1.000 | 1.104 | 1.191 | 1.191 | 1.191 |

| Av | 1.088 | 1.055 | 1.113 | 1.072 | 1.080 | 1.071 | 1.069 |

| FSM | seq_code LS | Quartus LQ | JEDI LJ | s_method Lmin | LS/Lmin | LQ/Lmin | LJ/Lmin |

|---|---|---|---|---|---|---|---|

| bbara | 27 | 25 | 24 | 26 | 1.038 | 0.962 | 0.923 |

| bbsse | 60 | 59 | 62 | 54 | 1.111 | 1.093 | 1.148 |

| beecount | 18 | 18 | 21 | 18 | 1.000 | 1.000 | 1.167 |

| cse | 86 | 86 | 83 | 80 | 1.075 | 1.075 | 1.038 |

| dk14 | 44 | 37 | 40 | 40 | 1.100 | 0.925 | 1.000 |

| dk15 | 15 | 15 | 14 | 14 | 1.071 | 1.071 | 1.000 |

| dk16 | 81 | 81 | 87 | 86 | 0.942 | 0.942 | 1.012 |

| dk17 | 14 | 13 | 11 | 12 | 1.167 | 1.083 | 0.917 |

| dk512 | 15 | 16 | 13 | 14 | 1.071 | 1.143 | 0.929 |

| ex1 | 107 | 108 | 117 | 103 | 1.039 | 1.049 | 1.136 |

| ex4 | 33 | 36 | 30 | 30 | 1.100 | 1.200 | 1.000 |

| ex5 | 24 | 19 | 14 | 18 | 1.333 | 1.056 | 0.778 |

| ex6 | 57 | 56 | 58 | 52 | 1.096 | 1.077 | 1.115 |

| ex7 | 26 | 19 | 22 | 20 | 1.300 | 0.950 | 1.100 |

| keyb | 72 | 72 | 81 | 72 | 1.000 | 1.000 | 1.125 |

| lion9 | 11 | 11 | 9 | 11 | 1.000 | 1.000 | 0.818 |

| planet | 201 | 218 | 201 | 190 | 1.058 | 1.147 | 1.058 |

| planet1 | 201 | 218 | 201 | 190 | 1.058 | 1.147 | 1.058 |

| pma | 147 | 140 | 164 | 141 | 1.043 | 0.993 | 1.163 |

| s1 | 147 | 137 | 140 | 146 | 1.007 | 0.938 | 0.959 |

| s1488 | 218 | 226 | 232 | 220 | 0.991 | 1.027 | 1.055 |

| s1494 | 227 | 233 | 234 | 218 | 1.041 | 1.069 | 1.073 |

| s298 | 965 | 788 | 981 | 929 | 1.039 | 0.848 | 1.056 |

| s386 | 58 | 55 | 49 | 48 | 1.208 | 1.146 | 1.021 |

| s510 | 103 | 106 | 130 | 103 | 1.000 | 1.029 | 1.262 |

| s820 | 123 | 131 | 133 | 129 | 0.953 | 1.016 | 1.031 |

| s832 | 122 | 135 | 135 | 129 | 0.946 | 1.047 | 1.047 |

| sand | 222 | 220 | 228 | 199 | 1.116 | 1.106 | 1.146 |

| sse | 60 | 59 | 62 | 54 | 1.111 | 1.093 | 1.148 |

| styr | 175 | 215 | 185 | 183 | 0.956 | 1.175 | 1.011 |

| tbk | 266 | 266 | 282 | 262 | 1.015 | 1.015 | 1.076 |

| tma | 97 | 93 | 92 | 93 | 1.043 | 1.000 | 0.989 |

| train11 | 28 | 26 | 22 | 25 | 1.120 | 1.040 | 0.880 |

| Av | 1.065 | 1.044 | 1.038 | ||||

| Max | 1.333 | 1.200 | 1.262 | ||||

| Best | 8 | 8 | 9 | 16 | |||

| Unique | 4 | 5 | 7 | 11 |

| FSM | seq_code FS | Quartus FQ | JEDI FJ | s_method Fmax | Fmax/FS | Fmax/FQ | Fmax/FJ |

|---|---|---|---|---|---|---|---|

| bbara | 430 | 451 | 547 | 529 | 1.230 | 1.173 | 0.967 |

| bbsse | 345 | 397 | 341 | 357 | 1.035 | 0.899 | 1.047 |

| beecount | 633 | 636 | 637 | 633 | 1.000 | 0.995 | 0.994 |

| cse | 291 | 302 | 319 | 323 | 1.110 | 1.070 | 1.013 |

| dk14 | 471 | 595 | 596 | 576 | 1.223 | 0.968 | 0.966 |

| dk15 | 869 | 911 | 799 | 869 | 1.000 | 0.954 | 1.088 |

| dk16 | 374 | 372 | 333 | 398 | 1.064 | 1.070 | 1.195 |

| dk17 | 637 | 712 | 717 | 712 | 1.118 | 1.000 | 0.993 |

| dk512 | 642 | 642 | 668 | 654 | 1.019 | 1.019 | 0.979 |

| ex1 | 302 | 315 | 317 | 339 | 1.123 | 1.076 | 1.069 |

| ex4 | 539 | 539 | 545 | 545 | 1.011 | 1.011 | 1.000 |

| ex5 | 485 | 531 | 581 | 521 | 1.074 | 0.981 | 0.897 |

| ex6 | 387 | 454 | 393 | 408 | 1.054 | 0.899 | 1.038 |

| ex7 | 463 | 465 | 532 | 551 | 1.190 | 1.185 | 1.036 |

| keyb | 318 | 318 | 313 | 341 | 1.072 | 1.072 | 1.089 |

| lion9 | 636 | 640 | 684 | 636 | 1.000 | 0.994 | 0.930 |

| planet | 230 | 235 | 221 | 249 | 1.083 | 1.060 | 1.127 |

| planet1 | 230 | 235 | 221 | 249 | 1.083 | 1.060 | 1.127 |

| pma | 237 | 217 | 237 | 277 | 1.169 | 1.276 | 1.169 |

| s1 | 243 | 269 | 254 | 256 | 1.053 | 0.952 | 1.008 |

| s1488 | 224 | 230 | 206 | 239 | 1.067 | 1.039 | 1.160 |

| s1494 | 205 | 223 | 224 | 234 | 1.141 | 1.049 | 1.045 |

| s298 | 126 | 144 | 127 | 128 | 1.016 | 0.889 | 1.008 |

| s386 | 387 | 365 | 406 | 372 | 0.961 | 1.019 | 0.916 |

| s510 | 303 | 270 | 265 | 303 | 1.000 | 1.122 | 1.143 |

| s820 | 257 | 252 | 260 | 247 | 0.961 | 0.980 | 0.950 |

| s832 | 233 | 221 | 242 | 264 | 1.133 | 1.195 | 1.091 |

| sand | 215 | 219 | 231 | 244 | 1.135 | 1.114 | 1.056 |

| sse | 345 | 397 | 341 | 357 | 1.035 | 0.899 | 1.047 |

| styr | 247 | 237 | 224 | 250 | 1.012 | 1.055 | 1.116 |

| tbk | 215 | 215 | 202 | 206 | 0.958 | 0.958 | 1.020 |

| tma | 290 | 307 | 288 | 315 | 1.086 | 1.026 | 1.094 |

| train11 | 435 | 467 | 545 | 518 | 1.191 | 1.109 | 0.950 |

| Av | 1.073 | 1.035 | 1.040 | ||||

| Max | 1.230 | 1.276 | 1.195 | ||||

| Best | 1 | 7 | 11 | 16 | |||

| Unique | 0 | 6 | 10 | 15 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Salauyou, V. Area and Performance Estimates of Finite State Machines in Reconfigurable Systems. Appl. Sci. 2024, 14, 11833. https://doi.org/10.3390/app142411833

Salauyou V. Area and Performance Estimates of Finite State Machines in Reconfigurable Systems. Applied Sciences. 2024; 14(24):11833. https://doi.org/10.3390/app142411833

Chicago/Turabian StyleSalauyou, Valery. 2024. "Area and Performance Estimates of Finite State Machines in Reconfigurable Systems" Applied Sciences 14, no. 24: 11833. https://doi.org/10.3390/app142411833

APA StyleSalauyou, V. (2024). Area and Performance Estimates of Finite State Machines in Reconfigurable Systems. Applied Sciences, 14(24), 11833. https://doi.org/10.3390/app142411833