A Maximum Efficiency-86% Hybrid Power Modulator for 5G New Radio(NR) Applications

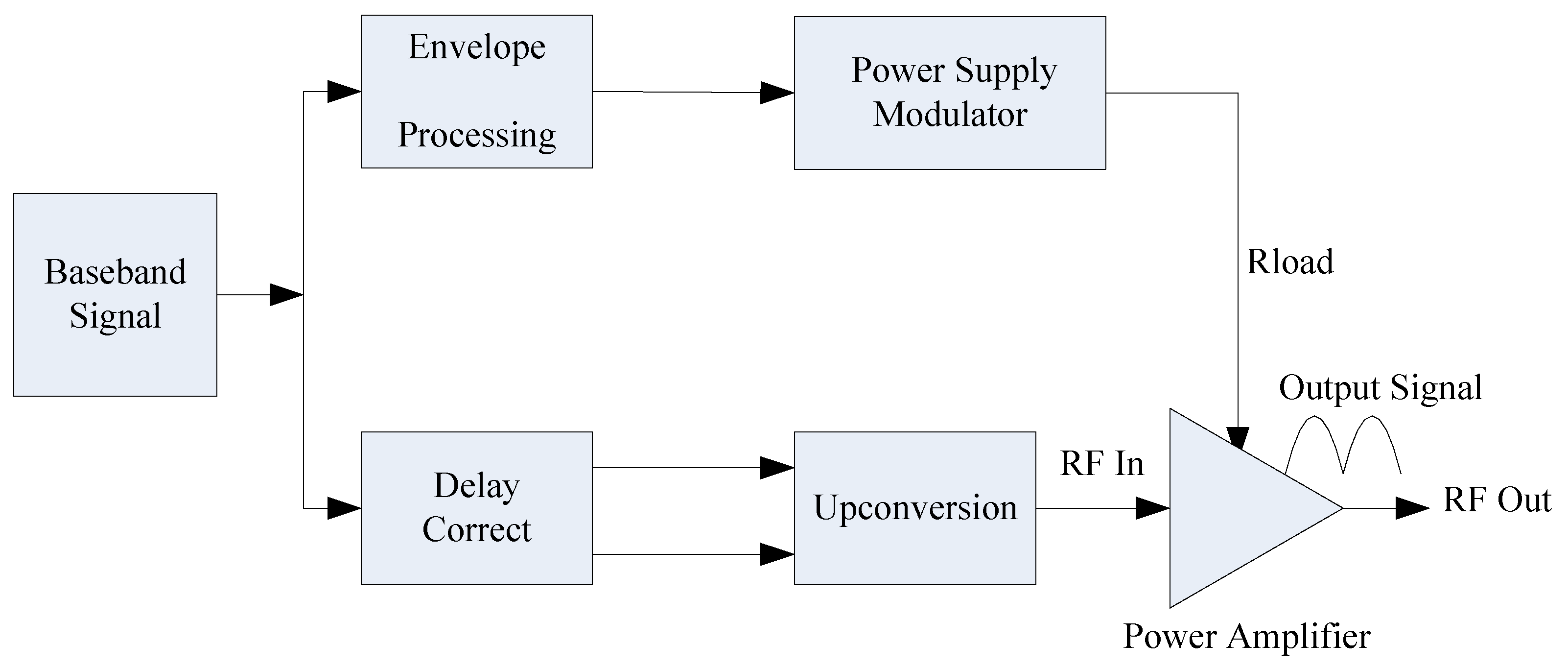

Abstract

1. Introduction

2. Technology and Methods

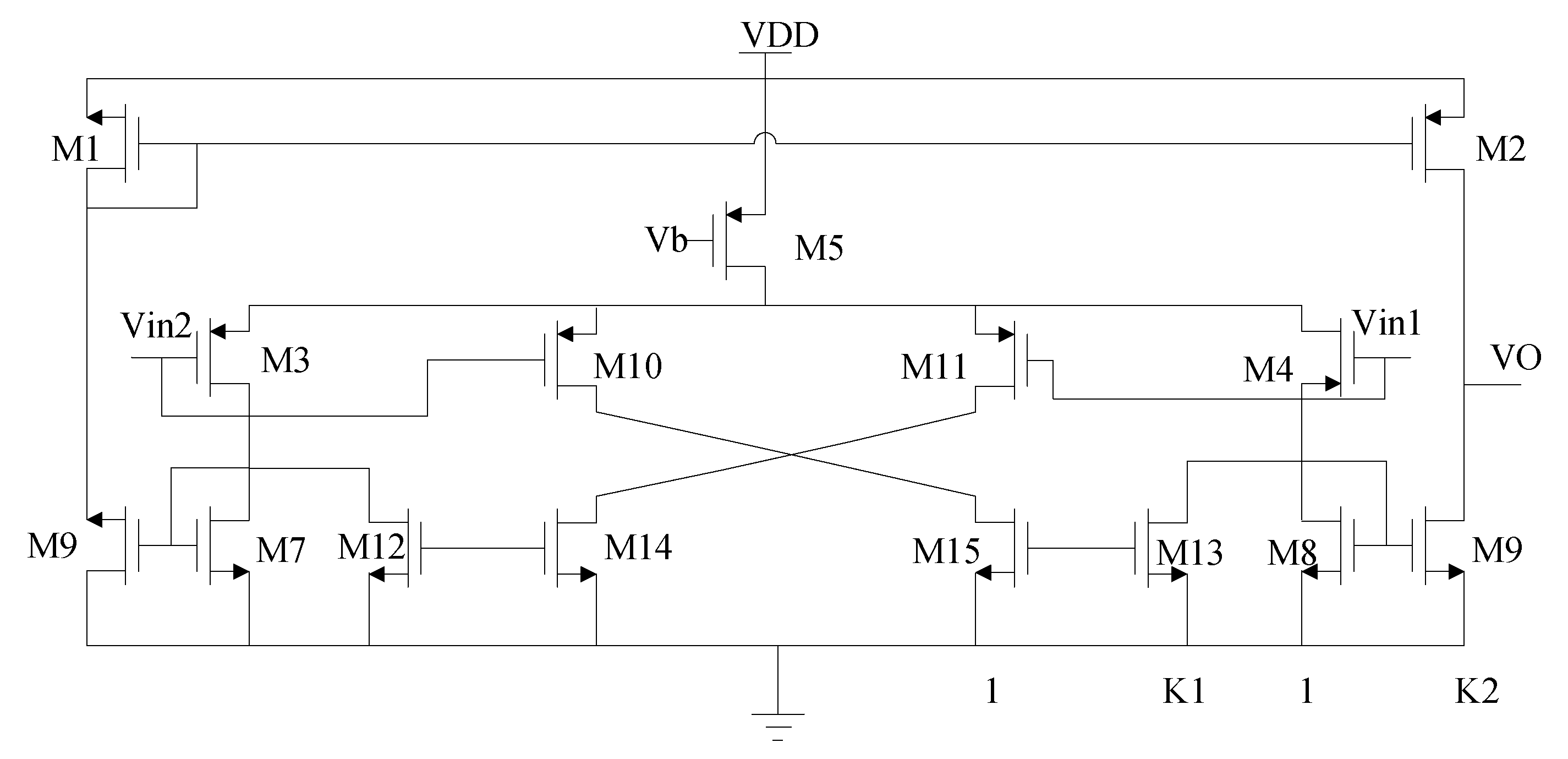

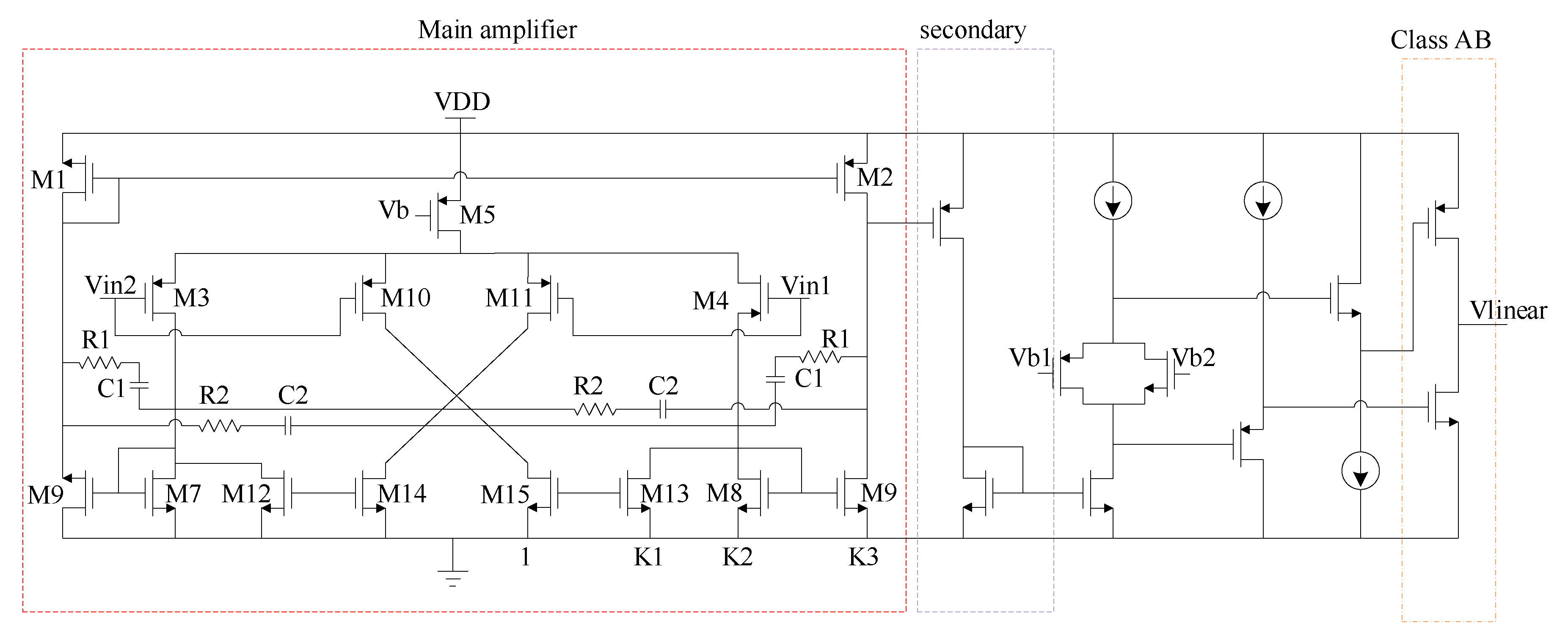

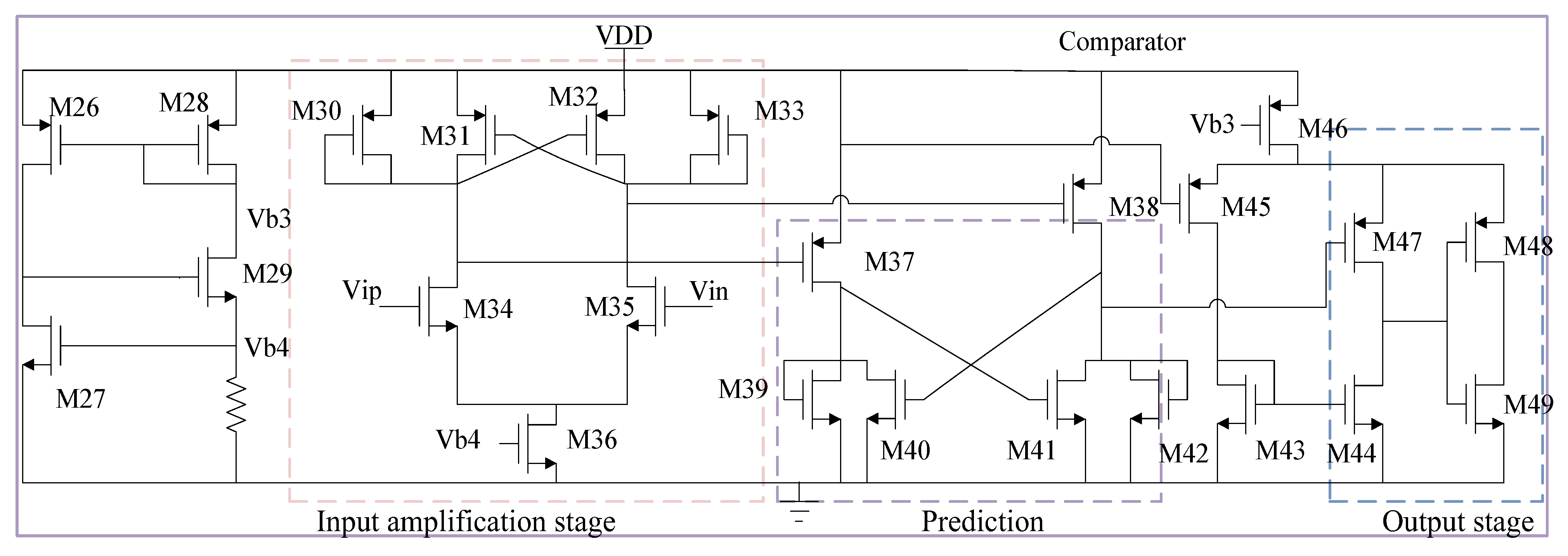

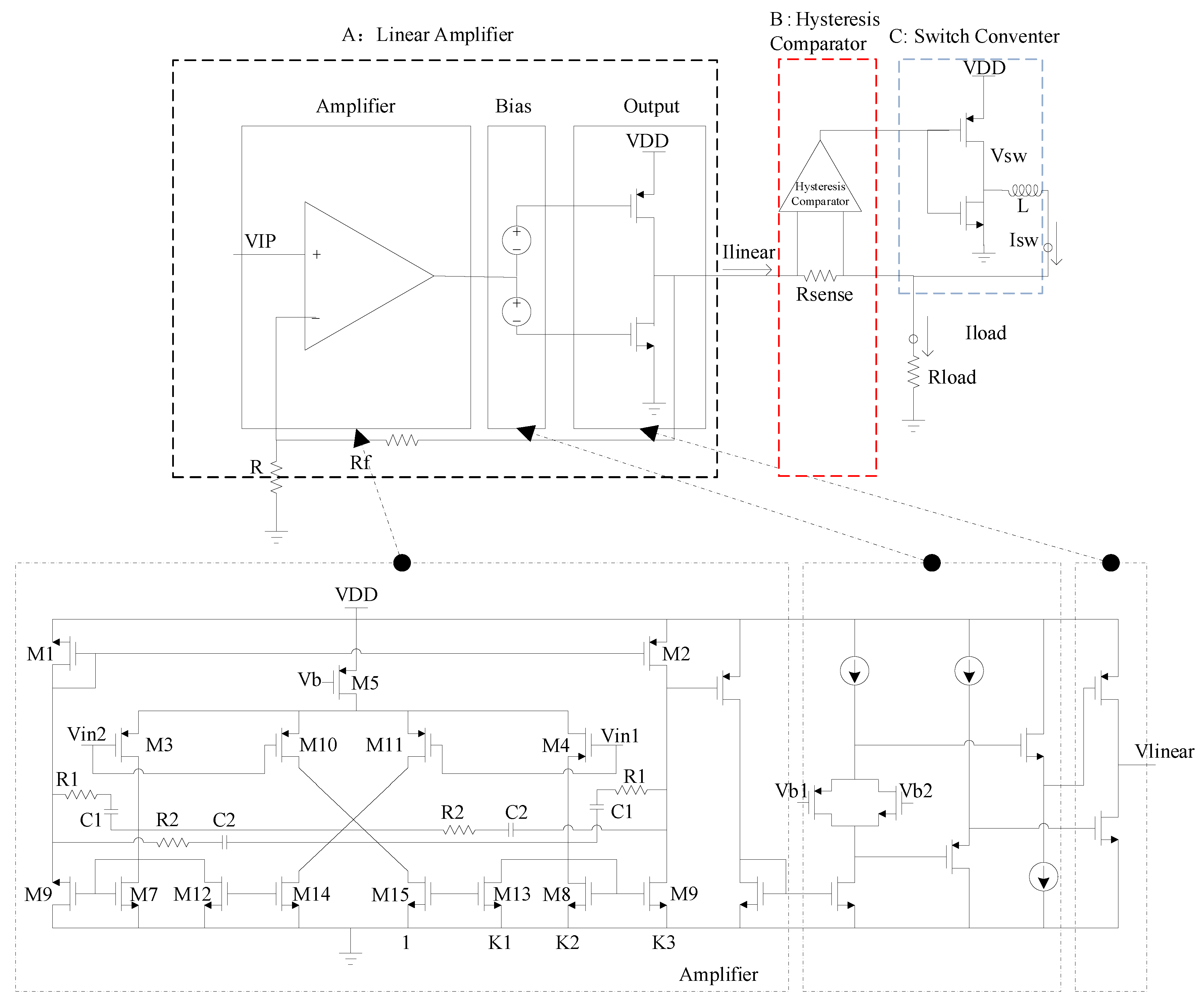

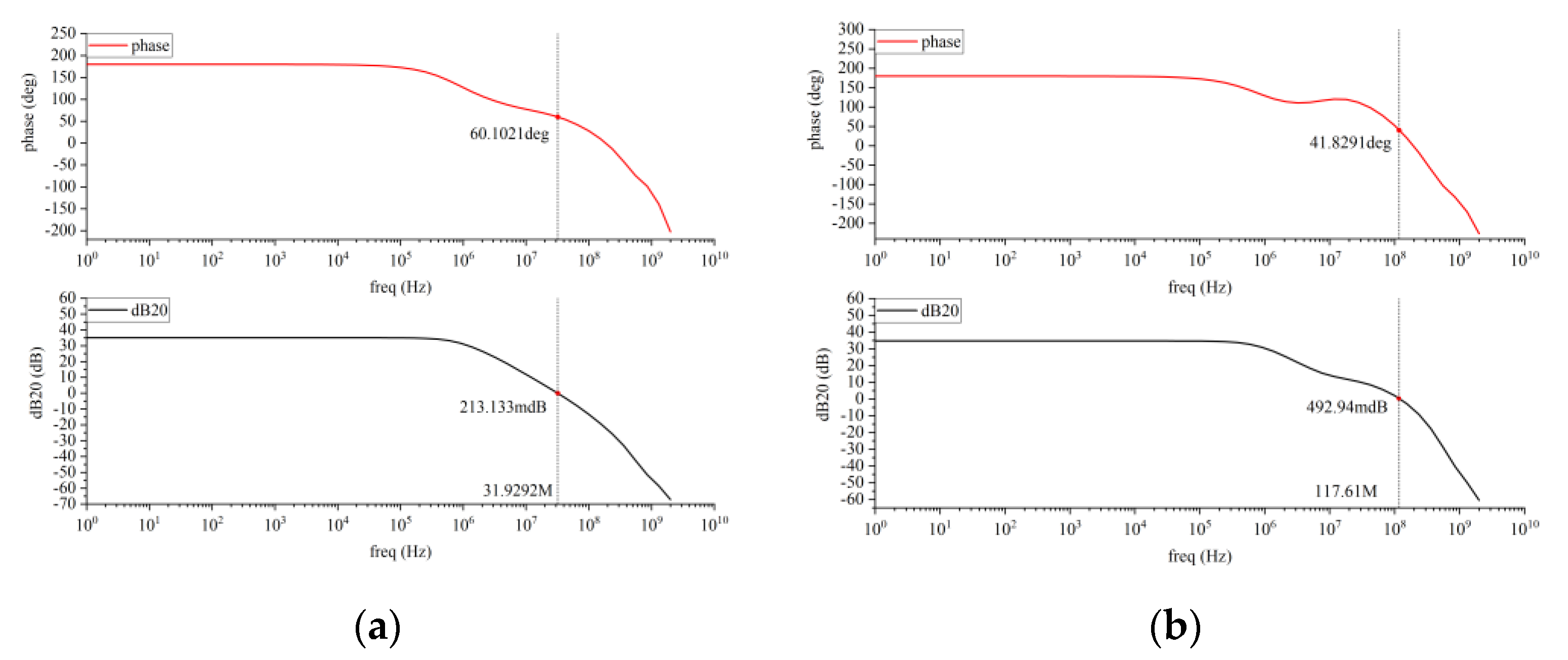

2.1. The Structure of the Linear Amplifier

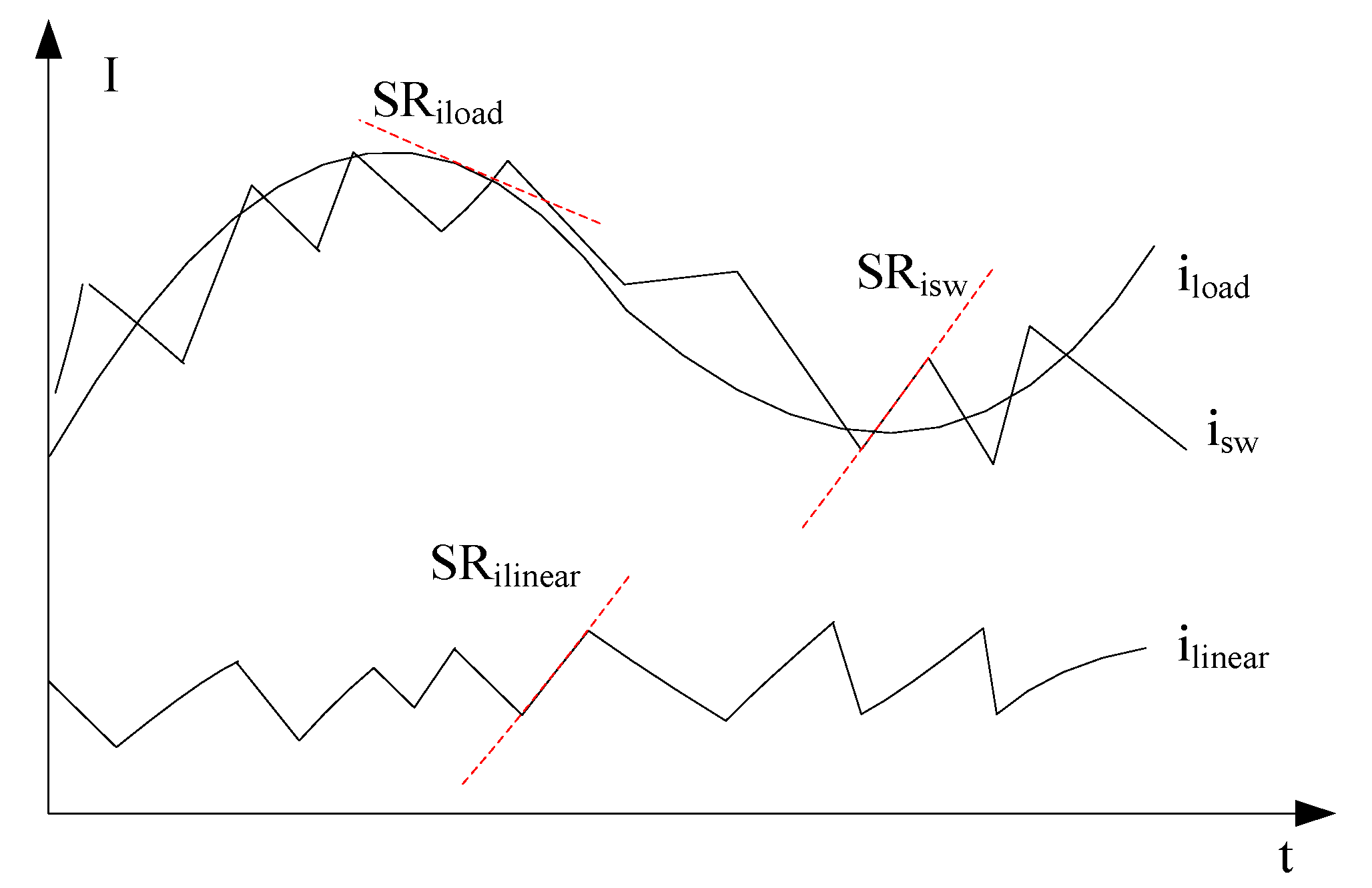

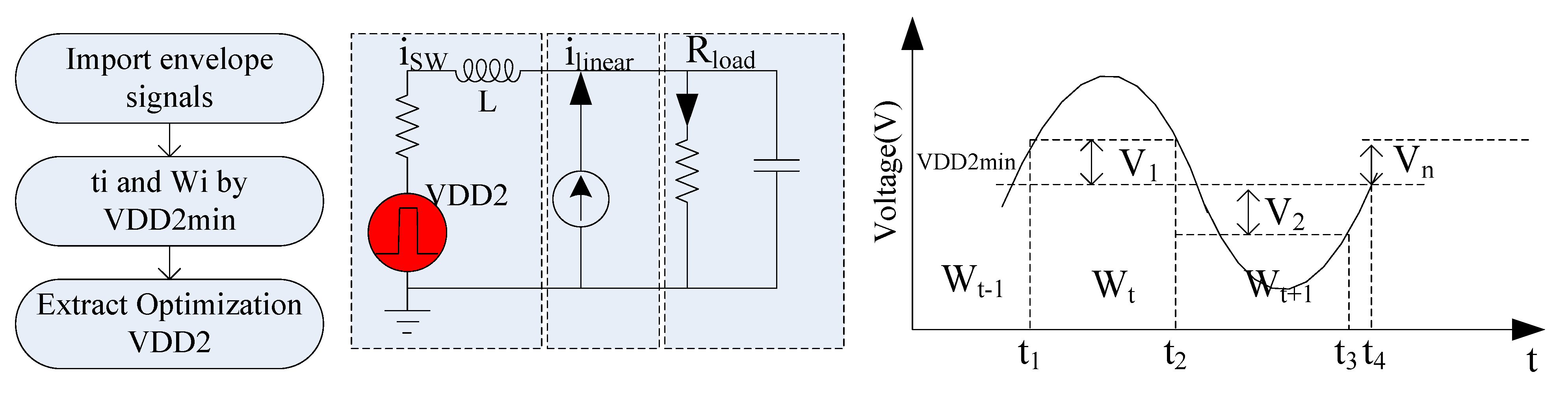

2.2. The Switching Converter and the Hysteresis Comparator

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Gupta, A.; Jha, E.R.K. A survey of 5G network: Architecture and emerging technologies. IEEE Access 2015, 3, 1206–1232. [Google Scholar] [CrossRef]

- Kawanishi, T.; Kanno, A.; Freire, H.S.C. Wired and wireless links to bridge networks: Seamlessly connecting radio and optical technologies for 5G networks. IEEE Microw. Mag. 2018, 19, 102–111. [Google Scholar] [CrossRef]

- Chih-Lin, I.; Han, S.; Xu, Z.; Wang, S.; Sun, Q.; Chen, Y. New paradigm of 5G wireless Internet. IEEE J. Sel. Areas Commun. 2016, 34, 474–482. [Google Scholar]

- Tsai, W.-T.; Peng, Z.-A.; Liou, C.-Y.; Mao, S.-G. Linearity and Noise Improvements of Driver-Stage Envelope-Injection Power Amplifier with Amplitude and Phase Shaping Functions for 5G New Radio Application. IEEE Access 2019, 7, 112384–112396. [Google Scholar] [CrossRef]

- Kim, J.; Son, J.; Jee, S.; Kim, S.; Kim, B. Optimization of Envelope Tracking Power Amplifier for Base-Station Applications. IEEE Trans. Microw. Theory Tech. 2013, 61, 1620–1627. [Google Scholar] [CrossRef]

- Mahmoudidaryan, P.; Mandal, D.; Bakkaloglu, B.; Kiae, S. 27.5 A 91%-Efficiency Envelope-Tracking Modulator Using Hysteresis-Controlled Three-Level Switching Regulator and Slew-Rate-Enhanced Linear Amplifier for LTE-80MHz Applications. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 17–21 February 2019. [Google Scholar]

- Renaud, L.; Baylon, J.; Gopal, S.; Hoque, M.A.; Heo, D. Analysis of Systematic Losses in Hybrid Envelope Tracking Modulators. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 1319–1330. [Google Scholar] [CrossRef]

- Wolff, N.; Heinrich, W.; Bengtsson, O. 100-MHz GaN-HEMT Class-G Supply Modulator for High-Power Envelope-Tracking Applications. IEEE Trans. Microw. Theory Tech. 2016, 65, 872–880. [Google Scholar] [CrossRef]

- Rodriguez, M.; Zhang, Y.; Maksimovic, D. High frequency PWM buck converters using GaN-on-SiCHEMTs. IEEE Trans. Power Electron. 2014, 29, 2462–2473. [Google Scholar] [CrossRef]

- Sepahvand, A.; Zhang, Y.; Maksimović, D. High efficiency 20–400 MHz PWM converters using air-core inductors and monolithic power stages in a normally-off GaN process. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016; pp. 580–586. [Google Scholar]

- Attili, I.B.; Mahmoud, S.A. Survey on Single Stage Amplifiers for Column Drivers in Active Matrix LCD Panels Leading to a Highly Linear Rail-to-Rail Robust Amplifier. IEEE Access 2019, 7, 166629–166647. [Google Scholar] [CrossRef]

- Yan, Z.; Mak, P.-I.; Law, M.-K.; Martins, R.P.; Maloberti, F. Nested-Current-Mirror Rail-to-Rail-Output Single-Stage Amplifier with Enhancements of DC Gain, GBW and Slew Rate. IEEE J. Solid-State Circuits 2015, 50, 2353–2366. [Google Scholar] [CrossRef]

- Sheeparamatti, A.; Bhat, M.V.; Srivatsa, M.P.; Nithin, M. Design of 3.3 V rail to rail operational amplifier for high resolution ADC driver amplifier. In Proceedings of the 2017 International Conference on Innovative Mechanisms for Industry Applications (ICIMIA), Bengaluru, India, 21–23 February 2017. [Google Scholar]

- Abdulaziz, M.; Nejdel, A.; Törmänen, M.; Sjöland, H. A 3.4 mW 65nm CMOS 5th order programmable active-RC channel select filter for LTE receivers. In Proceedings of the 2013 IEEE Radio Frequency Integrated Circuits Symposium (RFIC), Seattle, WA, USA, 2–4 June 2013. [Google Scholar]

- Abdulaziz, M.; Törmänen, M.; Sjöland, H. A Compensation Technique for Two-Stage Differential OTAs. IEEE Trans. Circuits Syst. II Express Briefs 2014, 61, 594–598. [Google Scholar] [CrossRef]

- Liu, S. Research and Implementation of Doherty RF Power Amplifier Based on Broadband Envelope Tracking Technology. Master’s thesis, Beijing University of Posts and Telecommunications, Beijing, China, 2015. [Google Scholar]

- Cao, T.; Liu, Y.; Yang, C.; Zhou, J. Circuits Optimization and System Linearization for High Efficiency and Wideband Envelope Tracking Architecture. J. Electron. Inf. 2020, 42, 787–794. [Google Scholar]

- Leng, W. Envelope-Tracking Supply Modulator with Trellis Search-Based Switching and 160 MHz Capability. In Proceedings of the 2021 IEEE Custom Integrated Circuits Conference (CICC), Austin, TX, USA, 25–30 April 2021. [Google Scholar]

- Lin, Y.-C.; Chen, Y.-J.E. A CMOS Envelope Tracking Supply Converter for RF Power Amplifiers of 5G NR Mobile Terminals. IEEE Trans. Power Electron. 2021, 36, 6814–6823. [Google Scholar] [CrossRef]

- Xiong, Y. High-Efficiency CMOS Envelope Amplifier Chip Design. Master’s thesis, University of Electronic Science and Technology, Chengdu, China, 2016. [Google Scholar]

- Wang, Y.; Ruan, X.; Jin, Q.; Xi, H.; Xiong, X.; Leng, Y.; Li, Y. Elimination of the Interaction of the Converters in Switch-Linear Hybrid Envelope Tracking Power Supplies. IEEE Trans. Power Electron. 2019, 35, 2053–2066. [Google Scholar] [CrossRef]

- Wang, Y.; Ruan, X.; Leng, Y.; Li, Y. Hysteresis Current Control for Multilevel Converter in Parallel-Form Switch-Linear Hybrid Envelope Tracking Power Supply. IEEE Trans. Power Electron. 2018, 34, 1950–1959. [Google Scholar] [CrossRef]

- Zhang, Y.; Strydom, J.; de Rooij, M.; Maksimović, D. Envelope tracking GaN power supply for 4G cell phone base stations. In Proceedings of the 2016 IEEE Applied Power Electronics Conference and Exposition (APEC), Long Beach, CA, USA, 20–24 March 2016. [Google Scholar]

- Sagneri, A.; Anderson, D.; Perreault, D. Optimization of integrated transistors for very high frequency dc-dc converters. IEEE Trans. Power Electron. 2013, 28, 3614–3626. [Google Scholar] [CrossRef]

- Zhang, Y.; Rodriguez, M.; Maksimovic, D. High frequency synchronous buck converter using GaN-on-SiC HEMTs. In Proceedings of the 2013 IEEE Energy Conversion Congress and Exposition, Denver, CO, USA, 15–19 September 2013. [Google Scholar]

- Zhang, Y.; Rodriguez, M.; Maksimovic, D. Output filter design in high-efficiency wide-bandwidth multi-phase buck envelope amplifiers. In Proceedings of the 2015 IEEE Applied Power Electronics Conference and Exposition (APEC), Charlotte, NC, USA, 15–19 March 2015. [Google Scholar]

- Sebastian, J.; Fernandez-Miaja, P.; Ortega-Gonzalez, F.; Patino, M.; Rodriguez, M. Design of a two-phase buck converter with fourth-order output filter for envelope amplifiers of limited bandwidth. IEEE Trans. Power Electron. 2014, 29, 5933–5948. [Google Scholar] [CrossRef]

- Liu, X.; Zhang, H.; Mok, P.K.T.; Luong, H.C. A Multi-Loop-Controlled AC-Coupling Supply Modulator with a Mode-Switching CMOS PA in an EER System With Envelope Shaping. IEEE J. Solid-State Circuits 2019, 54, 1553–1563. [Google Scholar] [CrossRef]

- Ziraksaz, F.; Nabavi, A. Design of a Linear Class AB Amplifier with 55dB Gain, 890MHz Bandwidth and Low Output Impedance for Envelope Tracking Supply Modulator. In Proceedings of the 2019 27th Iranian Conference on Electrical Engineering (ICEE), Yazd, Iran, 30 April–2 May 2019; pp. 253–257. [Google Scholar]

- Mahmoudidaryan, P.; Mandal, D.; Bakkaloglu, B.; Kiaei, S. Wideband Hybrid Envelope Tracking Modulator With Hysteretic-Controlled Three-Level Switching Converter and Slew-Rate Enhanced Linear Amplifier. IEEE J. Solid-State Circuits 2019, 54, 3336–3347. [Google Scholar] [CrossRef]

- Wu, P.Y.; Mok, P.K.T. A two-phase switching hybrid supply modulator for RF power amplifiers with 9% efficiency improvement. IEEE J. Solid-State Circuits 2010, 45, 2543–2556. [Google Scholar] [CrossRef]

- Hassan, M.; Larson, L.E.; Leung, V.W.; Asbeck, P.M. A combined series-parallel hybrid envelope amplifier for envelope tracking mobile terminal RF power amplifier applications. IEEE J. Solid-State Circuits 2012, 47, 1185–1198. [Google Scholar] [CrossRef]

- Sankman, J.; Song, M.K.; Ma, D. Switching-converter-only multiphase envelope modulator with slew rate enhancer for LTE power amplifier applications. IEEE Trans. Power Electron. 2016, 31, 817–826. [Google Scholar] [CrossRef]

- Amò, P.; Thomas, M.; Molata, V.; Jeřábek, T. Envelope modulator for multimode transmitters with AC-coupled multilevel regulators. In Proceedings of the 2014 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 9–13 February 2014. [Google Scholar]

- Qu, L.; Li, S.; Yu, K.; Zhang, G. Three level envelope modulator for envelope tracking power amplifier. Appl. Electron. Technol. 2019, 45, 70–73+82. [Google Scholar]

- Riehl, P.; Fowers, P.; Hong, H.-P.; Ashburn, M. An AC-coupled hybrid envelope modulator for HSUPA transmitters with 80% modulator efficiency. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013. [Google Scholar]

- Tan, M.; Ki, W.-H. An efficiency-enhanced hybrid supply modulator with single-capacitor current-integration control. IEEE J. Solid-State Circuits 2016, 51, 533–542. [Google Scholar]

- Pan, X.; Liu, H.; Zhang, H.; Xu, P.; Hong, Z. A dual-mode hybrid envelope tracking power modulator for RFPA. J. Fudan Univ. 2019, 58, 425–432. [Google Scholar]

- He, H.; Ge, T.; Kang, Y.; Guo, L.; Chang, J.S. A 40 MHz Bandwidth, 91% Peak Efficiency, 2.5 W Output Power Supply Modulator with Dual-Mode Sigma–Delta Control and Adaptive Biasing Amplifier for Multistandard Communications. IEEE Trans. Power Electron. 2020, 35, 9430–9442. [Google Scholar] [CrossRef]

- Hassan, M.; Asbeck, P.M.; Larson, L.E. A CMOS dual-switching power-supply modulator with 8% efficiency improvement for 20MHz LTE Envelope Tracking RF power amplifiers. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013. [Google Scholar]

- Chen, Z.; Xia, Q.; Dong, L.; Fan, S.; Han, K.; Guo, Z.; Xue, Z.; Geng, L. An Open Loop Digitally Controlled Hybrid Supply Modulator Achieving High Efficiency for Envelope Tracking with Baseband up to 200-MHz. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 4142–4153. [Google Scholar] [CrossRef]

- Kim, J.; Kim, D.; Cho, Y.; Kang, D.; Park, B.; Moon, K.; Koo, S.; Kim, B. Highly Efficient RF Transmitter Over Broad Average Power Range Using Multilevel Envelope-Tracking Power Amplifier. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 1648–1657. [Google Scholar] [CrossRef]

- Jing, Y.; Bakkaloglu, B. A High Slew-Rate Adaptive Biasing Hybrid Envelope Tracking Supply Modulator for LTE Applications. IEEE Trans. Microw. Theory Tech. 2017, 65, 3245–3256. [Google Scholar] [CrossRef]

- Lin, W.; Lin, Z.; Liu, C.; Chen, K.; Lin, Y.; Lin, J.; Tsai, T. A 20 MHz Low Dropout Controlled Current Sensor for Constant On-Time Based Envelop Tacking Supply Modulator for Radio Frequency Power Amplifier. In Proceedings of the 2018 IEEE International Symposium on Circuits and Systems (ISCAS), Florence, Italy, 27–30 May 2018; pp. 1–4. [Google Scholar]

| [41] | [42] | [43] | [44] | [39] | This Work | |

|---|---|---|---|---|---|---|

| Year | 2013 | 2015 | 2017 | 2018 | 2020 | 2022 |

| Technology (μm) | 0.18 | 0.18 | 0.18 | 0.18 | 0.18 | 0.18 |

| Structure | hybrid | hybrid | hybrid | hybrid | hybrid | hybrid |

| Supply (V) | 5.5 | 5 | 3.6 | 2.7–4.2 | 3.6 | 5,4.5 |

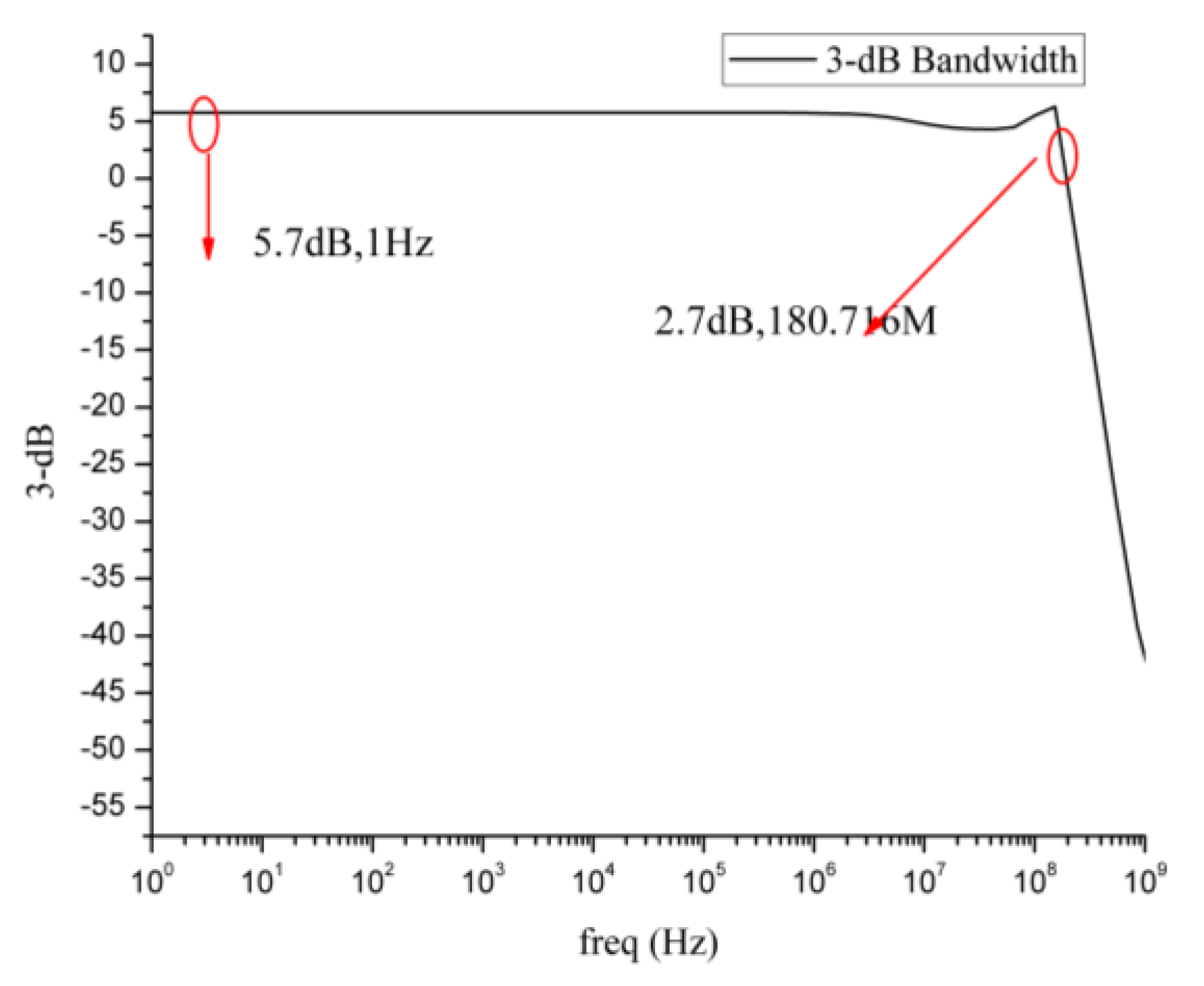

| Bandwidth (MHz) | 20 | 20 | 10 | 20 | 40 | 100 |

| Signal | LTE | 16QAM/ LTE | LTE/QPSK | LTE | LTE-A | OFDM |

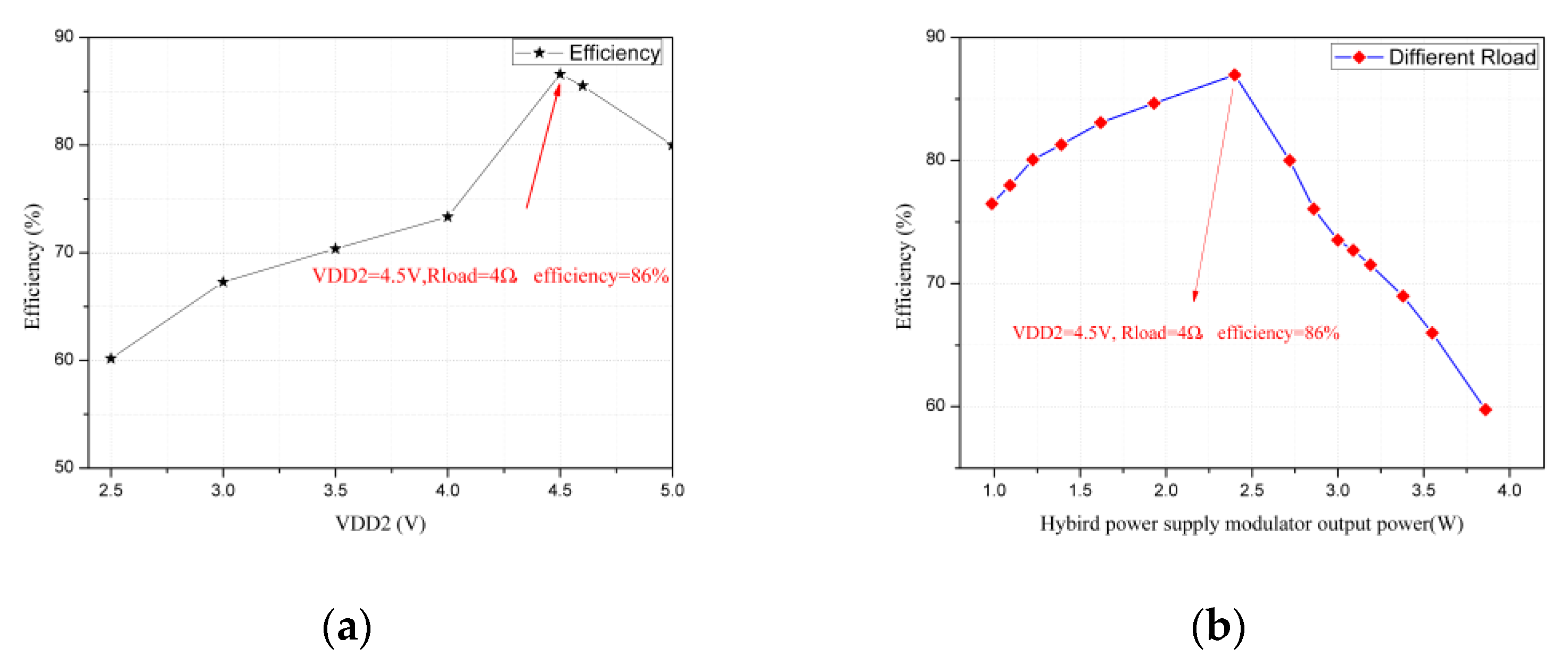

| Efficiency (%) | 83 | 75.9 | 83 | 78–86 | 85 | 86 |

| Output power (W) | 0.67 | 0.4 | >0.3 | 1 | 2.5 | 2.4 |

| PAPR (dB) | 6.7 | 7.5 | 7.24 | NA | NA | 8 |

| Core area (mm2) | NA | 1.4 | 1.1 | 0.78 | 0.6 | NA |

| Chip area (mm2) | 1.47 | NA | NA | NA | 2.25 | 1.44 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cui, X.; Qiu, X.; Leng, Y.; Liu, X.; Wu, T. A Maximum Efficiency-86% Hybrid Power Modulator for 5G New Radio(NR) Applications. Appl. Sci. 2022, 12, 12041. https://doi.org/10.3390/app122312041

Cui X, Qiu X, Leng Y, Liu X, Wu T. A Maximum Efficiency-86% Hybrid Power Modulator for 5G New Radio(NR) Applications. Applied Sciences. 2022; 12(23):12041. https://doi.org/10.3390/app122312041

Chicago/Turabian StyleCui, Xingli, Xin Qiu, Yongqing Leng, Xiaotian Liu, and Tianyu Wu. 2022. "A Maximum Efficiency-86% Hybrid Power Modulator for 5G New Radio(NR) Applications" Applied Sciences 12, no. 23: 12041. https://doi.org/10.3390/app122312041

APA StyleCui, X., Qiu, X., Leng, Y., Liu, X., & Wu, T. (2022). A Maximum Efficiency-86% Hybrid Power Modulator for 5G New Radio(NR) Applications. Applied Sciences, 12(23), 12041. https://doi.org/10.3390/app122312041