Abstract

Static corrective controllers are more efficient than dynamic ones since they consist of only logic elements, whereas their existence conditions are more restrictive. In this paper, we present a static corrective control scheme for fault diagnosis and fault tolerant control of input/state asynchronous sequential machines (ASMs) vulnerable to transient faults. The design flexibility of static controllers is enlarged by virtue of using a diagnoser and state bursts. Necessary and sufficient conditions for the existence of a diagnoser and static fault tolerant controller are presented, and the process of controller synthesis is addressed based on the derived condition. Illustrative examples on practical ASMs are provided to show the applicability of the proposed scheme.

1. Introduction

Aiming at compensating for the stable-state behavior of asynchronous sequential machines (ASMs), corrective control theory has been extensively studied in both theoretical [1,2,3,4,5] and experimental studies [6,7,8]. While the performance of corrective control is remarkable, especially in fault tolerant control against various kinds of faults [9,10,11], most of the developed controllers are dynamic ones having the form of ASMs with states, which need significant resource usage [7,8].

Static corrective controllers [12,13] are a promising alternative to dynamic ones. Consisting of only combinational logic with no states, static controllers are superior to dynamic ones in terms of not only resource usage, but also robustness against exogenous disturbances, as memory elements representing system states are frequently offended by faults [14,15]. On the other hand, they have a drawback in that their existence conditions are more restrictive than dynamic ones, due to the absence of the controller’s states. In this paper, a novel methodology of static fault tolerant control is proposed for ASMs subject to transient faults causing unauthorized state transitions. We address the existence condition and synthesis procedure for a static controller that realizes immediate fault recovery.

Compared with the prior work [12,13], this study has the following contributions. First, we show that static corrective control can be adopted to solve various control problems for ASMs. The objective in [12,13] was model matching, namely, refining the stable-state behavior of the closed-loop system to that of a reference model. The present work extends that of [12,13] so as to achieve fault diagnosis and fault tolerance. Next, the condition for designing a static controller is much improved. In [12,13], the flexibility of the static controller is restrictive since the control input is determined only by the external input and state feedback. To alleviate this harshness, we use a diagnoser that detects and isolates every fault occurrence and provides the fault information by switching an indicator signal. With this additional argument, the static controller is given greater easiness in generating the control input. The reachability condition required for the proposed controller is the same as that for dynamic ones. To facilitate the design of a diagnoser and controller, we utilize the state burst, or the fast sequence of transient states traversed by the machine during transitions.

As a similar subject to the present study, the diagnosability of discrete event systems (DESs) is much investigated in supervisory control of DESs [16,17,18,19,20]. The proposed diagnoser differs from these results in that while the diagnosers in supervisory control receive traces of inputs (events), the proposed diagnoser utilizes stable bursts traversed by the ASM. Moreover, the diagnosers in supervisory control cannot be applied to corrective control since they do not discriminate between stable and transient states, nor do they comply with fundamental mode operations.

Here, transient faults are referred to as short-lived violation of the system’s normal behavior, each fault showing no correlation with one another. Typical examples of transient faults include radiation particles, surging voltage, etc. Though not considered in this paper, there are other types of faults—permanent faults and intermittent ones. If the adverse effect of a fault persists indefinitely, it is classified as a permanent fault. Occurrences of permanent faults are mainly attributed to a physical defect or an inadequacy in the design of the system. On the other hand, an intermittent fault is a malfunction of a device or system that occurs at intervals. It may be caused by unstable or marginally stable hardware or inadequacy in the design, for example, by loose wires [21].

The outcome of transient faults caused by the adversarial input bears a strong resemblance to intelligent attacks in cyber–physical systems, where attackers may change the enablement of actuators commanded by a supervisor or sensor readings of the controlled system [22,23,24]. However, the adversarial input addressed in this study does not come from an intelligent entity; it is regarded as a randomly generated outer disturbance, e.g., single event upset (SEU) faults in radiation environments [14,15], or intrinsic faults occurring to the actuator [25,26,27]. Still, the considered fault situation is severe since the transient fault may occur at arbitrary moments.

Fault diagnosis and fault tolerant control is an area of active research not only in event-driven systems, but also in continuous-time dynamic systems. Notable among the recent results is [28] that addresses adverse effects on time delay between fault occurrence and fault accommodation in T–S fuzzy systems. Further, references [29,30] present active fault tolerant control for overcoming un-modeled actuator faults while considering time delay attributed to fault diagnosis. Transient faults in our study are conceptually similar to actuator faults, although the results of [25,26,27,29,30] are not applicable to controlling ASMs.

The remainder of this paper is organized as follows. In Section 2, we first address the mathematical formulation of input/state ASMs with transient faults and the overall structure of static fault tolerant control with a diagnoser. In Section 3, we present the operation of a diagnoser that can detect and isolate unauthorized transitions. Based on the fault indicator signal generated by the diagnoser, we elucidate in Section 4 the necessary and sufficient condition and synthesis procedure for a static corrective controller that realizes immediate fault recovery against every transient fault. Two illustrative examples are provided in Section 5 to demonstrate the design procedure of the proposed static controller. Finally, some conclusions are drawn in Section 6.

2. Preliminaries

For a finite set D, is the cardinality of D, and is the set of non-empty strings made of characters in D. For , is the length of p, p is a strict prefix of q if with . denotes the set of all strict prefixes of q. We also denote for some . Table 1 summarizes the notations used in this paper.

Table 1.

Nomenclature.

ASMs are classified as input/state machines in which the current state is given as the output, and input/output ones that generate the output different from the state. In this study, we focus our concern on input/state ASMs. An input/state ASM is modeled by a quadruple as follows:

where A is the input set, with is the state set, is the initial state, and is the state transition function partially defined on . A is divided into where and are the set of normal and adversarial inputs, respectively. is valid if is defined. A valid pair is stable if , and transient if . Let

denote the set of inputs that make stable and transient pairs with x, respectively.

Owing to the absence of a synchronizing clock, responds only to the input change. It rests in a stable pair with indefinitely as long as remains fixed. If changes to another value , engages in a chain of transient transitions as follows:

while a remains fixed. Provided that possesses no infinite cycles, reaches the next stable state as follows:

after k steps, where . As transient states are traversed instantaneously, it is convenient to describe this chain of transitions only in terms of stable states, omitting instantaneous transient transitions. To this end, the stable recursion function s [1,9] is defined on every valid pair as follows:

where is the next stable state of . If is a stable pair, . The chain of transient transitions characterized by s is termed a stable transition. In this study, is alternatively described as follows:

The domain of s is often extended to through the following relation:

where is said to be stably reachable from x if for some [1,9]. With , every state of is stably reachable in at most steps of stable transitions. Thus, the length of t is bounded by .

When goes through a stable transition, it generates a state burst [31], or a fast state sequence consisting of underlying transient states and next stable state. If each generated state is separately delivered to the controller, the resultant configuration has the state feedback control mechanism. If, on the other hand, the controller has access to the state burst, the closed-loop system is endowed with burst-feedback control. In this study, we utilize the burst feedback control scheme, as it gives more flexibility of controller synthesis, albeit needing an additional resource to record the state burst.

The state burst of a valid state–input pair is described as the following mapping:

denotes the state burst with respect to a valid pair , namely, is generated when takes the stable transition from . For instance, addressed in (1) and (2) leads to the following state burst:

For a state burst , let and be its first and last element, respectively. In terms of the foregoing notations, and .

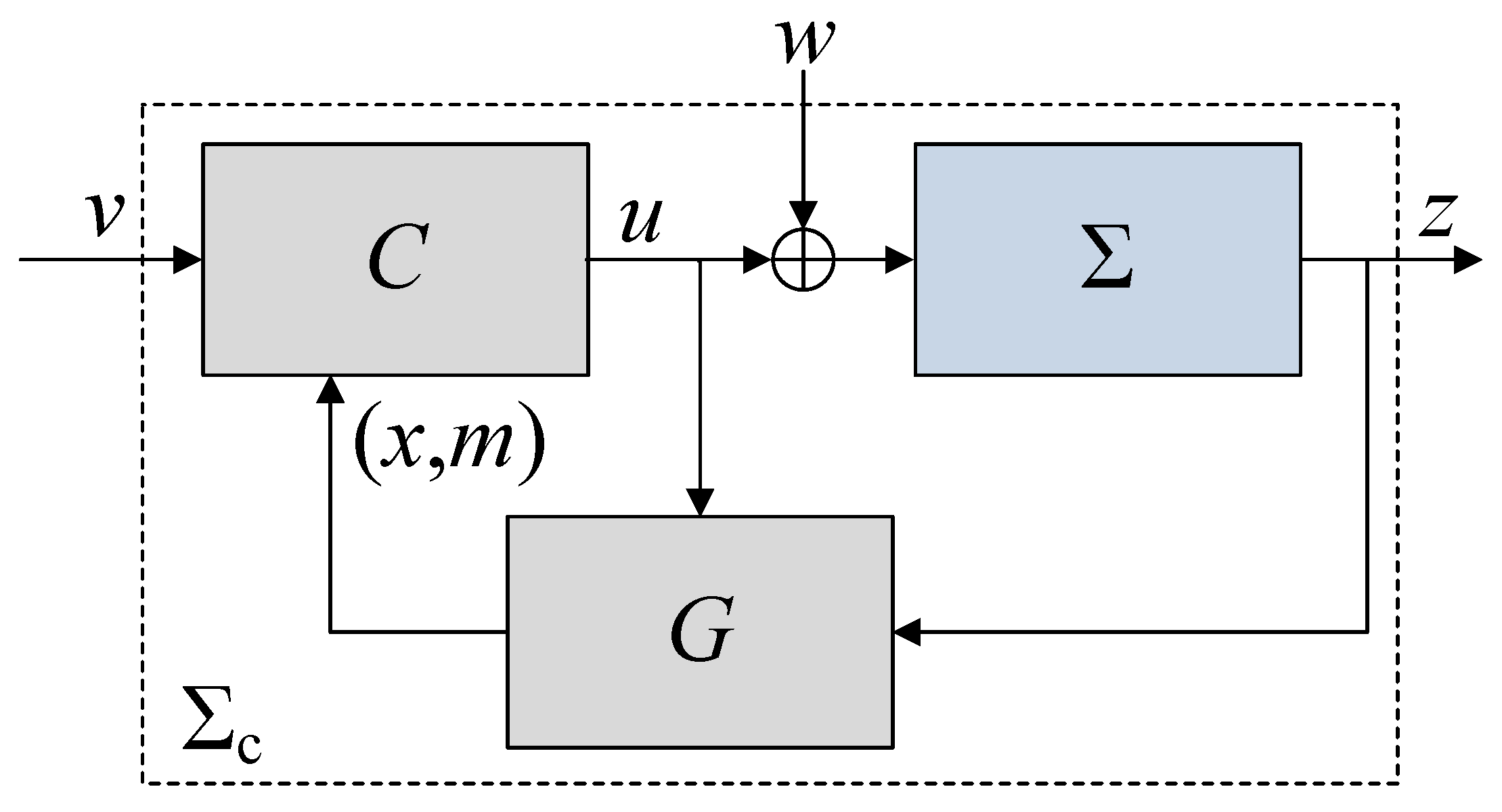

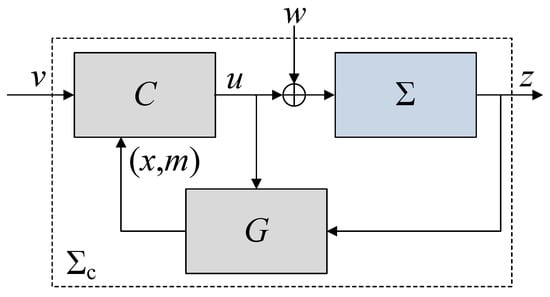

Figure 1 shows the proposed static fault tolerant corrective control system, where C is the static corrective controller, G is the diagnoser, is the external input, is the control input provided by C, is the adversarial input, is the state burst, and and are respectively the state feedback and the fault indicator signal generated by G. denotes the closed-loop system consisting of , C, and G. When w enters , it overrides u and causes a transient fault, forcing to undergo an unauthorized state transition whenever it is valid with respect to the current state. w represents an external disturbance that infiltrates into through the control input channel. As addressed before, a typical instance of w is an SEU fault [14,15] that upsets the logic value of memory bits expressing the control input. Inherent mechanical or electrical faults to the actuator can be also modeled by w.

Figure 1.

Static corrective control system with a diagnoser.

For , let

be the set of adversarial inputs that cause unauthorized transitions to when it stays at the stable state x, and let

be the set of states reaches as a result of a transient fault occurring at x. Note that w is unobservable from both C and G, which fits into the characteristics of adversarial entities.

G provides C with the next stable state and the fault indicator signal based on the state burst z and the control input u. Thus G has the following mapping:

With the state notation , indicates that has undergone a nominal stable transition. On the other hand, implies that has undergone an unauthorized transition from caused by an unspecified adversarial input .

Referring to Figure 1, C receives the input triplet and generates the control input u as the output. Being a static controller, C is represented by the following function:

During the normal behavior of , C just relays the external input to without modification. When a transient fault is diagnosed, C provides appropriate control input sequences. The control objective is to achieve immediate fault recovery, namely, to take from the faulty state to the original state at which the fault occurs before further change in the external input. Since neither C nor G is governed by a synchronizing clock, their operations are also conducted instantaneously under asynchrony. Hence the procedure of fault diagnosis and fault tolerant control can be completed before the external input changes to the next value, rendering to show the normal input/state behavior as if no fault has happened.

is assumed to preserve fundamental mode operations [32], wherein no two variables change simultaneously. Under the fundamental mode, w is supposed to occur to only when stays at a stable state. This is not a burdensome constraint since the speed of transient transitions is so fast that the possibility of fault occurrences during the transitions is negligible. Hence the stable state at which the fault occurs serves as the goal state for the corresponding fault tolerant control. In a similar sense, it is also supposed that v is not altered during the correction procedure.

Remark 1.

Whereas the present study focuses on transient faults of which influence on the machine vanishes right after its occurrence, there exist other kinds of faults differing in the durability of their influences. If the adverse effect persists for a finite time after initial occurrence, the fault is termed an intermittent fault [33]; if the effect remains indefinitely (or irreversible), it is termed a permanent fault [34]. For input/state ASMs, fault recovery is impossible for either intermittent or permanent faults since immediate return to the original state cannot be implemented. The latter problem can be tackled for input/output ASMs, where the output differs from the present state [35], or switched ASMs that possess redundant states which may substitute faulty states [8].

Remark 2.

In the field of DESs, the stability and stabilizability of the system under static feedback control means that starting from any arbitrary initial state, the system can (or can be controlled to) go to a “legal state” and stay there after a finite number of transitions [36]. In our problem setting, the original state at which a fault occurs can be regarded as a legal state. With no infinite cycles, further, fault recovery implies that Σ must be controlled to the original state in finite steps of stable transitions. In this sense, the fault tolerant controllability of Σ is equivalent to the stabilizability of DESs in supervisory control. Note that a stable pair just implies that x is a fixed point of f, irrelevant to the stability of Σ.

3. Diagnoser

For G to determine whether or not a transient fault occurs, and of the current state burst z are investigated with respect to . Assume first that . This implies that undergoes a nominal stable transition . To signify this, we assign the fault indicator signal . Accordingly, G is set to be if .

On the other hand, assume that . This elucidates that the latest stable transition is caused not by u, but by such that and . In this case, we assign , where i is the index of the state at which the fault occurs, i.e., . Hence if and .

Once a transient fault is diagnosed, is controlled to return to the original state via a chain of stable transitions. This means that after diagnosing a transient fault, G receives a sequence of pairs of state bursts and control inputs characterizing nominal stable transitions. Since the procedure of fault recovery persists until reaches , G must continue to give the same fault indicator signal unless the state feedback is received. Thus m of is set to be unchanged if , , and , where is the previous value of m.

Finally, assume that fault recovery is accomplished as reaches . Upon receiving the state feedback , G must signify the end of the recovery procedure. Hence G is designed to generate at this phase, or if , , and .

Combining the above discussions, we encapsulate the algorithm of fault detection and isolation by G.

Proposition 1.

Algorithm 1 is correct, i.e., fault detection and isolation is characterized by m.

| Algorithm 1: Fault detection and isolation by G with and (the previous value of m): |

|

Proof.

In Algorithm 1, the value of m is 0 at either Step 2.b or Step 3.b. The algorithm goes to Step 2.b when . As this indicates the execution of the nominal stable transition , no transient fault occurs. Step 3.b implies that after a transient fault at (), recovers the normal behavior by reaching . Hence corresponds to no fault occurrence or fault recovery. On the other hand, m is assigned a non-zero index at either Step 2.a or Step 3.a. Since both steps represent an unauthorized transition from or failure of returning to , serves as the indicator for fault detection and isolation. □

A formal definition of G is constructed from the above algorithm as follows:

where ‘-’ in the second line implies ‘unchanged’.

To comply with fundamental mode, G should provide C with only when stays at a stable state. To this end, the end of every stable transition must be identified. In the nominal transitions, it is easily done by referring to z and u since the current stable transition will end at . In the case of unauthorized transitions, however, one must determine it only by referring to z, as w is unobservable. The latter property is termed fault detectability [31]. The condition for fault detectability with respect to the state burst is that any state burst generated during the unauthorized transition is not a strict prefix of another one (Theorem 3.7 of [31]). The underlying reason is obvious as elicited in the following.

Proposition 2.

For with , Σ is fault detectable at x if and only if , with .

Proof.

(Only if) Assume that is fault detectable at x but for some . Assume further that while u remains unchanged, G receives the changed state burst . Then, one cannot determine whether occurs so that reaches the faulty state , or occurs so that is on its way to the corresponding faulty state , passing through the intermediate transient state . This contradicts the assumption of fault detectability at x.

(If) Suppose that G receives (w is unknown) such that . Since for all with , one can identify the end of the unauthorized transition merely by referring to z. Hence is fault detectable at x. □

4. Controller Synthesis

A necessary condition for taking from a beginning state to a goal state via corrective control is that the goal state is stably reachable from the beginning state, namely, an input string exists with which stably reaches the goal state [9]. Such input strings are utilized by the controller in building feedback paths. For static controllers, another significant condition must be satisfied with respect to the set of utilized input sequences. Slightly relaxing the notion presented in [12,13], we define the implementability of static corrective controllers.

Definition 1.

A static corrective controller is said to be implementable with respect to a set of control input sequences if by utilizing S, the controller’s output is uniquely determined by each input combination of the controller.

Implementability is necessary for the integrity of the static controller since having no states, the static controller must always generate a unique output with respect to each input combination.

The constraint on implementability makes it impossible to apply the previous static controller [12,13] to fault recovery. To validate the latter assertion, assume that undergoes an unauthorized transition from x to by () during which both external and control inputs remain . Assume further that x is stably reachable from , e.g., for . If we use the previous static controller

with no indicator signal as its argument, we must assign the output b to the input combination to start the correction procedure, that is, . However, may be a valid pair of , e.g., . Then, in the normal behavior of , must provide a as the control input without modification, i.e., one must design such that to maintain the nominal stable transition from . Since this conflicts with the foregoing assignment , the previous static corrective controller cannot be applied to the present problem.

The use of G and the addition of the related argument m to C resolve the aforementioned predicament. m is retained as i throughout the recovery procedure for the unauthorized transition from . Further, G gives C only the next stable state, discarding the underlying transient states. Hence the proposed static controller achieving fault recovery against can be designed if and only if is stably reachable from every , which equals the following condition for the existence of a corresponding dynamic controller.

Lemma 1

([31]). Given Σ with for , a dynamic corrective controller exists that achieves fault recovery against if and only if the following holds:

Provided that the above condition is valid, we design the proposed static controller . First, if , C just relays the external input to the control input channel, as no transient fault occurs. For this purpose, we set the following:

To design the operation of fault recovery, take an arbitrary faulty state and denote a proper input string by with . Denote further by the intermediate stable states traverses when it undertakes the chain of stable transitions in response to t, i.e., the following:

where and . Suppose that is staying at a stable pair when infiltrates into such that . The input pair of G changes to at this time, where and . Since , G generates according to (3). Receiving at the instant of the fault occurrence, C commences the correction procedure by generating until reaches . Transient states underlying between and need not be considered since they are discarded by G. Hence we set C as follows:

As soon as the state feedback changes to , C provides , which takes toward , and so on. The following assignment materializes these recursive operations of C.

Fault recovery is accomplished when reaches in response to . m is reset to 0 at this time. Since , C generates a again as the control input according to (6).

By Definition 1, the control input sequences should be selected in such a way that C is implementable. We assert that if the reachability condition for a dynamic corrective controller is valid for every with , one can find a set of input sequences for which C is implementable.

Proposition 3.

Proof.

If , the implementability of C with respect to is ensured trivially since only one input string is used as the control input sequence for the transient fault. Else if , consider with . By assumption, and exist such that . Let and be the set of intermediate stable states traverses when undertakes the chain of stable transitions from to and from to , respectively. Then, we have the following:

If , the use of t and r satisfies the implementability of C since each feedback path contains no common state. Otherwise, passes through a common state when it is driven by C along two state trajectories and . Specifically, assume the following:

where and ( and ). If , the implementability of C is still valid with respect to since C will generate the same output () in response to . Else if , we adjust one of t and r as follows to satisfy the implementability. First, the suffix lengths and are compared. Suppose that . Next, the suffix of t is substituted by the corresponding part of r, i.e., we induce an alternative input string from t and r as follows:

Since by the definition of t and r, can be used instead of t for fault recovery from to . It is clear that C is implementable with respect to the derived input sequence. Since m is distinctive with respect to , the latter implies the implementability of C. □

In the above proof, the suffix of the previous input sequence with a longer length () is replaced by the shorter one (). This is intended to reduce the computational load of the controller by taking a shorter feedback path.

Theorem 1.

Given the configuration of Figure 1, assume that for all of Σ. Then, C achieving fault recovery against transient faults by exists if and only if every unauthorized transition is fault detectable and , , is stably reachable from .

Proof.

(If) Since every unauthorized transition is fault detectable, we can design G by applying (3). In addition, since is stably reachable from every state of , by Proposition 3 we can find a set of control input sequences with which C is implementable and can design C by referring to (6)–(8). According to the foregoing discussions, is immune against any unauthorized transitions by .

(Only if) In view of Figure 1, the existence of C implies that the next stable state of every stable transition is identified solely by observing z. Hence every unauthorized transition is fault detectable by Proposition 2. Since C has access to only by changing u, fault recovery ensures that for all with and for all , exists which takes from to via a chain of stable transitions. □

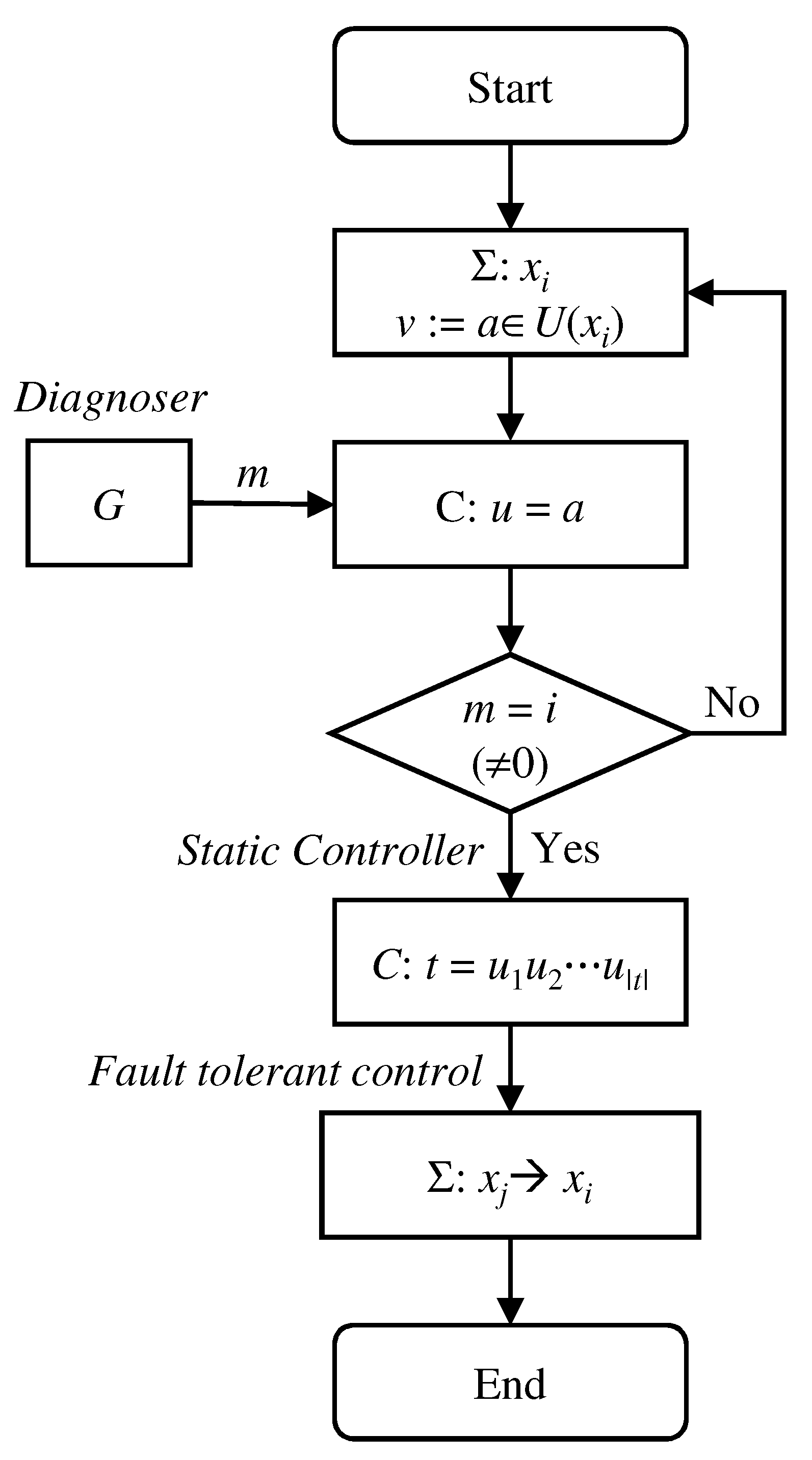

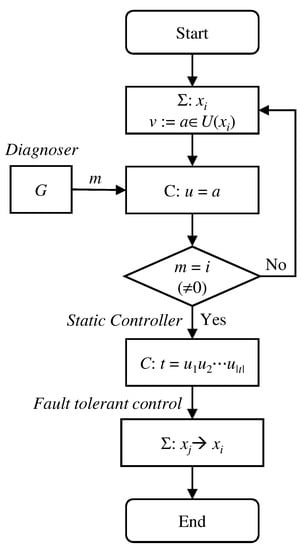

Figure 2 illustrates the flowchart elucidating the execution of the proposed static corrective controller for achieving fault tolerance. Compared with dynamic controllers [31], the improvement of computational load in controller synthesis is obvious. The dynamic controller needs to define maximum states for the correction procedure of each unauthorized transition. Since there may be maximally unauthorized transitions, the size (or number of states) of the overall controller has the complexity of . On the other hand, the proposed static controller is much more efficient, as it needs no states. Of course, G requires memory elements as the state burst and the previous output must be recorded. Since the maximum length of the state burst is , the construction of G is computed in , which is a mild degradation of resource usage. Note that a symbolic computation algorithm for inducing feasible control input sequences addressed in (5) is presented in the prior work [1,2]. Further, numerical algorithms avoiding tedious symbolic computations are found in the recent results [37,38].

Figure 2.

Flowchart of the proposed static corrective control scheme.

5. Illustrative Examples

5.1. Home Security System

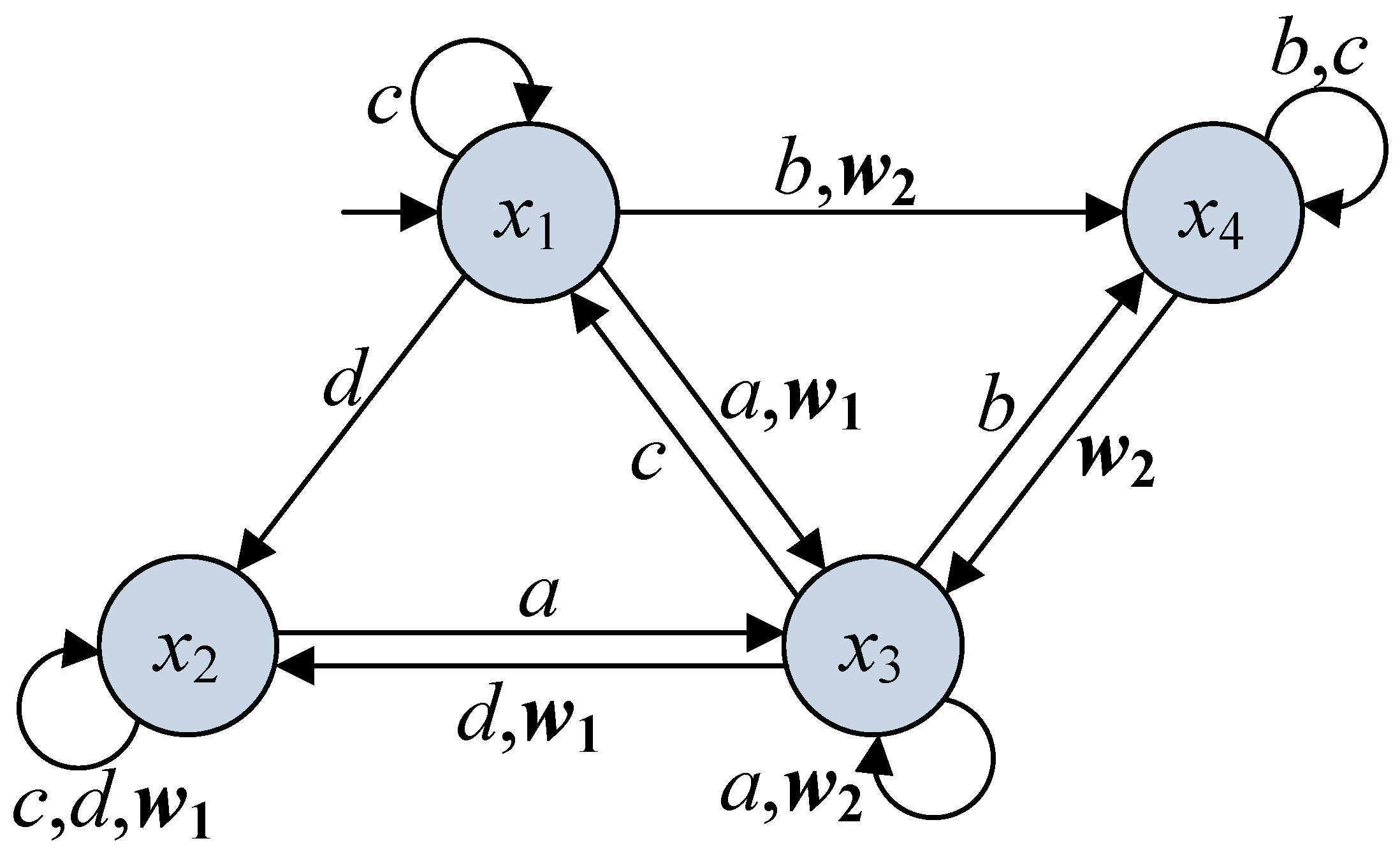

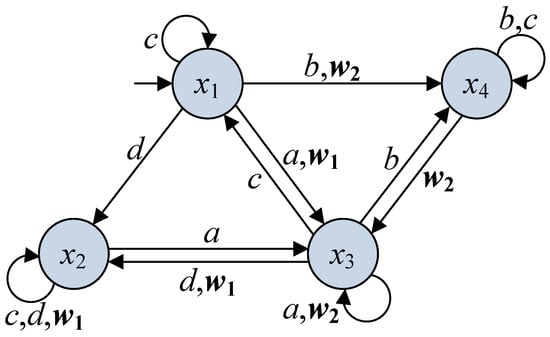

Consider whose state flow diagram is shown in Figure 3, where , , and . represents a home security system [12], where is the initial state and – are three alarm states that are reached by break-in events d, a, and b, respectively. c is the reset signal that is activated only at .

Figure 3.

State flow diagram of a home security system .

As an example instance, let us take the case of with and . To check the fault detectability, derive the state bursts caused by the elements of as and . Since and vice versa, is fault detectable at by Proposition 2.

If G receives or while u is equal to c, the unauthorized transition by or is diagnosed with certainty since and .

Referring to Figure 3, is stably reachable from every state of , e.g., and . By Theorem 1, C exists which achieves fault recovery against . To check the implementability of C associated with and c, and defined in (9) are derived as and . Although is non-empty, both and c have the common input c for . Hence they can be used as the control input sequences while guaranteeing the implementability of C.

The design procedure of C is straightforward. Since and , the control inputs with respect to are assigned in line with (7) and (8) as follows:

When an unauthorized transition occurs so that m changes to 1 and the state feedback to or , C activates the recovery procedure by performing the above operations. When reaches , m is reset to 0, and upon receiving from G, C terminates the recovery procedure. To this end, set C as follows:

Since the fault detectability condition in Proposition 2 and the reachability condition (5) are valid for the other states as well, the design of G and C for the rest of states and inputs can be similarly conducted.

As a comparative study, let us try to achieve the above fault tolerant control by the previous static controller receiving no fault indicator signal (see (4)). Assume that occurs when has been staying at so that is forced to reach . In a similar way to (10), must generate a to initiate the correction procedure, namely, . However, since in Figure 3, already has the assignment for ensuring the nominal transition. As this contradicts the foregoing operation, one cannot design that accomplishes fault tolerant control for .

5.2. Asynchronous Error Counter

As the second example, we apply the proposed scheme to fault tolerant control for asynchronous error counters embedded in the satellite computers [39]. Since SEU faults caused by cosmic rays in space corrupt logic values of memory elements in the computers, periodic memory scrubbing is needed based on the amount of accumulated errors. Error counters play the role of detecting and recording the error occurrences by transferring to specific states that characterize the degree of error occurrences.

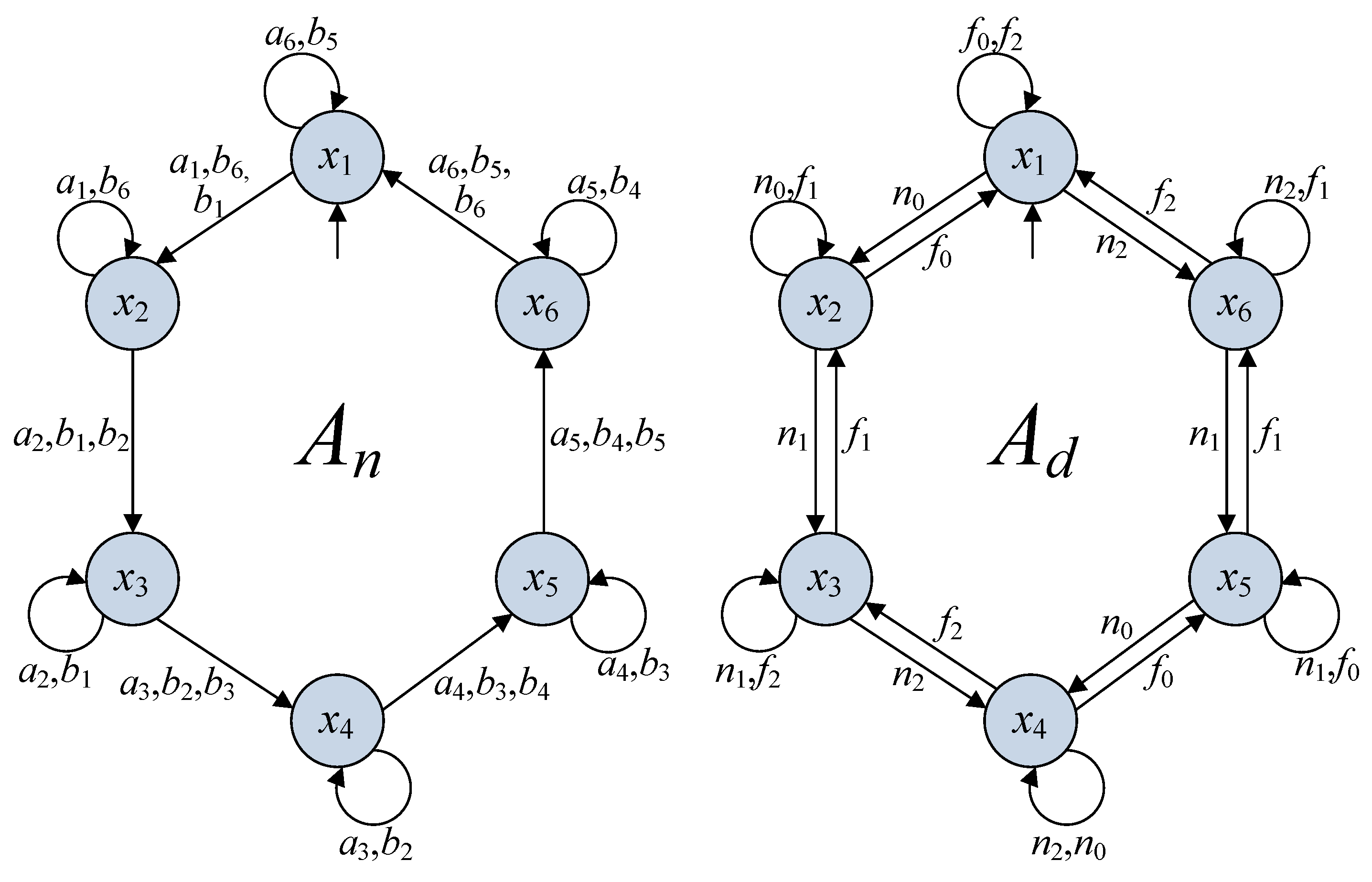

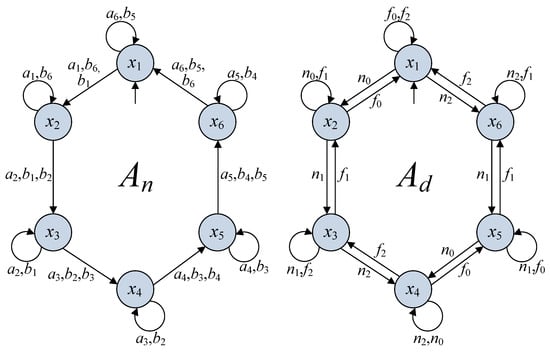

Consider an asynchronous 6-error counter whose state flow diagram is shown in Figure 4, where , , and . receives two kinds of error signals: with one-step resolution and with two-step resolution. Typical examples of and are 1-bit and 2-bit errors that frequently occur in space-born digital systems [14,15]. It is assumed that every character of can be generated for control purposes. In accordance with the meaning of each signal, advances one state in response to and two states in response to as depicted in Figure 4.

Figure 4.

State flow diagram of an asynchronous 6-error counter : state transitions with respect to are drawn on the left, and those with respect to are on the right.

counts maximally six occurrences of ’s and three occurrences of ’s, after which is reset to . Supposing that is implemented as a digital circuit, we assign a three-bit binary number to each state as follows: , , , , , and .

Working in space, all the memory elements corresponding to are also exposed to SEU faults. In , and represent an SEU fault that upsets the logic value of from 0 to 1 and from 1 to 0, respectively, . The control goal is to design G and C, if any, that accomplish fault diagnosis and fault recovery against any adversarial input of .

By observing Figure 4, we can derive each and , e.g., for ,

It is found that , . Let us investigate fault detectability for the existence of G. For instance, consider the case of . The state bursts produced by are and . Since and vice versa, any unauthorized transitions occurring at are fault detectable by Proposition 2. In fact, fault detectability is ensured for the rest of the states and thus G can be designed.

To construct G, we continue to concern the case of . A fault occurrence at is diagnosed when the state burst is observed to change to either or , while the control input remains unchanged. According to the first line of (3), G is set to be () as follows:

When is under the procedure of fault recovery, G must not change m as defined in the second line of (3). For the case of , the latter operation is materialized by setting the following:

Finally, when reaches the original state , m is reset to 0 as defined in the third line of (3). The operation of G at the other states is designed in a similar manner.

To determine the existence of C, we now investigate stable reachability between and . An examination of Figure 4 shows that for all , is stably reachable from every state of . For instance, is stably reachable from via an input string (), and from via an input string (). By Theorem 1, therefore, C exists which achieves fault recovery against transient faults by .

C is constructed in line with (6)–(8). Let us keep focusing on the fault recovery to . As addressed above, we employ and in activating the correction procedure from and , respectively. Upon receiving , traverses two intermediate stable states and . With m fixed to 1, C is designed with respect to and as follows:

On the other hand, transfers from directly to in response to , so C is designed as , . As (11) already contains this operation, it serves as the correction procedure realizing fault recovery to .

When reaches , m is reset to 0. Upon receiving from G, C terminates the recovery procedure. To this end, set C as follows:

It is clear from (11) and (12) that the selected control input sequences preserve the implementability. The operation of C for the other states is attained by adopting (11) and (12). Since all the interactions between C, G, and are conducted in an asynchronous mechanism, the correction procedure can be accomplished instantaneously before further change of the external input.

6. Conclusions and Challenges

We have shown that static corrective controllers can solve the problem of fault diagnosis and fault tolerant control for input/state ASMs subject to transient faults. The state burst is used as feedback to design a diagnoser that detects and isolates any transient fault. Since the static controller receives only the stable state and fault indicator signal from the diagnoser, the reachability condition for designing the controller is greatly enhanced compared with the previous result. We have addressed the existence conditions for the diagnoser and static controller and formal algorithms for their synthesis in the framework of corrective control. The case studies on the home security system and the asynchronous error counter validate the applicability of the proposed control scheme.

Since the closed-loop system with the proposed static corrective controller preserves fundamental mode operations, we can code the system in very high speed integrated circuit hardware description language (VHDL) so as to implement it on configurable semiconductor devices such as field-programmable gate arrays (FPGAs); refer to [6,7,8] for the relevant prior work. We expect that the implementation of the closed-loop system will take significantly fewer resources than the case of dynamic corrective controllers, albeit the addition of the diagnoser G. The design and implementation of the proposed static corrective control scheme on digital systems will be conducted as a further study.

While the ASM in this study has the form of an input/state machine, many practical ASMs are modeled by input/output machines. Hence establishing a static corrective control scheme for input/output ASMs is an important future research topic. Further, although only transients faults were considered in this paper, fault tolerant control for other types of faults, e.g., permanent faults and intermittent ones, may be solved in input/output ASMs as addressed in Remark 1. Hence applying the proposed static control methodology to overcoming such faults in input/output ASMs is also an interesting future research topic.

Author Contributions

Conceptualization, J.-M.Y.; funding acquisition, J.-M.Y., S.-J.P., and S.W.K.; supervision, J.-M.Y.; methodology, S.-J.P. and S.W.K.; formal analysis, J.-M.Y.; software and hardware, S.W.K.; writing—original draft preparation, J.-M.Y.; writing—reviewing and editing, S.-J.P. and S.W.K. All authors have read and agreed to the published version of the manuscript.

Funding

This research was supported in part by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (no. NRF-2021R1I1A3040696), in part by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (no. NRF-2018R1A5A1025137), and in part by Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (no. NRF-2016R1D1A1B02012959).

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Geng, X.; Hammer, J. Input/output control of asynchronous sequential machines. IEEE Trans. Autom. Control 2005, 50, 1956–1970. [Google Scholar] [CrossRef]

- Venkatraman, N.; Hammer, J. On the control of asynchronous sequential machines with infinite cycles. Int. J. Control 2006, 79, 764–785. [Google Scholar] [CrossRef]

- Xu, X.; Hong, Y. Matrix approach and model matching of asynchronous sequential machines. IEEE Trans. Autom. Control 2013, 58, 2974–2979. [Google Scholar] [CrossRef]

- Wang, J.; Han, X.; Chen, Z.; Zhang, Q. Model matching of input/output asynchronous sequential machines based on the semi-tensor product of matrices. Future Gener. Comput. Syst. 2018, 83, 468–475. [Google Scholar] [CrossRef]

- Wang, B.; Feng, J.E.; Meng, M. Model matching of switched asynchronous sequential machines via matrix approach. Int. J. Control 2019, 92, 2430–2440. [Google Scholar] [CrossRef]

- Yang, J.-M.; Kwak, S.W. Realizing fault-tolerant asynchronous sequential machines using corrective control. IEEE Trans. Control Syst. Technol. 2010, 18, 1457–1463. [Google Scholar] [CrossRef]

- Yang, J.-M.; Kwak, S.W. Output feedback control of asynchronous sequential machines with disturbance inputs. Inf. Sci. 2014, 259, 87–99. [Google Scholar] [CrossRef]

- Yang, J.-M.; Kwak, S.W. Fault tolerance in switched ASMs with intermittent faults. IET Control Theory Appl. 2017, 11, 1443–1449. [Google Scholar] [CrossRef]

- Murphy, T.E.; Geng, X.; Hammer, J. On the control of asynchronous machines with races. IEEE Trans. Autom. Control 2003, 48, 1073–1081. [Google Scholar] [CrossRef] [Green Version]

- Peng, J.; Hammer, J. Input/output control of asynchronous sequential machines with races. Int. J. Control 2010, 83, 125–144. [Google Scholar] [CrossRef]

- Yang, J.-M. A simple fault tolerant control for input/output asynchronous sequential machines. Automatica 2015, 52, 76–82. [Google Scholar] [CrossRef]

- Yang, J.-M.; Hammer, J. Static state feedback control of asynchronous sequential machines. Int. J. Gen. Syst. 2016, 45, 830–863. [Google Scholar] [CrossRef]

- Wang, B.; Feng, J.E. A matrix approach for the static correction problem of asynchronous sequential machines. Int. J. Control Autom. Syst. 2020, 18, 477–485. [Google Scholar] [CrossRef]

- Caron, P.; Inguimbert, C.; Artola, L.; Ecoffet, R.; Bezerra, F. Physical mechanisms of proton-induced single-event upset in integrated memory devices. IEEE Trans. Nucl. Sci. 2019, 66, 1404–1409. [Google Scholar] [CrossRef]

- He, G.; Zheng, S.; Jing, N. A hierarchical scrubbing technique for SEU mitigation on SRAM-based FPGAs. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2020, 28, 2134–2145. [Google Scholar] [CrossRef]

- Sampath, M.; Sengupta, R.; Lafortune, S.; Sinnamohideen, K.; Teneketzis, D. Diagnosability of discrete-event systems. IEEE Trans. Autom. Control 1995, 40, 1555–1575. [Google Scholar] [CrossRef] [Green Version]

- Zad, S.H.; Kwong, R.H.; Wonham, W.M. Fault diagnosis in discrete-event systems: Framework and model reduction. IEEE Trans. Autom. Control 2003, 48, 1199–1212. [Google Scholar] [CrossRef]

- Zaytoon, J.; Lafortune, S. Overview of fault diagnosis methods for discrete event systems. Annu. Rev. Control 2013, 37, 308–320. [Google Scholar] [CrossRef]

- Santoro, L.P.; Moreira, M.V.; Basilio, J.C. Computation of minimal diagnosis bases of discrete-event systems using verifiers. Automatica 2017, 77, 93–102. [Google Scholar] [CrossRef]

- Zhu, G.; Li, Z.; Wu, N.; Al-Ahmari, A. Fault identification of discrete event systems modeled by Petri nets with unobservable transitions. IEEE Trans. Syst. Man Cybern. Syst. 2019, 49, 333–345. [Google Scholar] [CrossRef]

- Siewiorek, D.P.; Swarz, R.S. Reliable Computer Systems, 2nd ed.; Digital Press: Bedford, MA, USA, 1992. [Google Scholar]

- Carvalho, L.K.; Wu, Y.C.; Kwong, R.; Lafortune, S. Detection and mitigation of classes of attacks in supervisory control systems. Automatica 2018, 97, 121–133. [Google Scholar] [CrossRef] [Green Version]

- Humayed, A.; Lin, J.; Li, F.; Luo, B. Cyber-physical systems security—A survey. IEEE Internet Things J. 2017, 4, 1802–1831. [Google Scholar] [CrossRef]

- Su, R. Supervisor synthesis to thwart cyber attack with bounded sensor reading alterations. Automatica 2018, 94, 35–44. [Google Scholar] [CrossRef] [Green Version]

- Li, Y.X.; Yang, G.H. Adaptive fuzzy decentralized control for a class of large-scale nonlinear systems with actuator faults and unknown dead zones. IEEE Trans. Syst. Man Cybern. Syst. 2017, 47, 729–740. [Google Scholar] [CrossRef]

- Jin, X.; Qin, J.; Shi, Y.; Zheng, W.X. Auxiliary fault tolerant control with actuator amplitude saturation and limited rate. IEEE Trans. Syst. Man Cybern. Syst. 2018, 48, 1816–1825. [Google Scholar] [CrossRef]

- Huang, C.; Naghdy, F.; Du, H. Delta operator-based model predictive control with fault compensation for steer-by-wire systems. IEEE Trans. Syst. Man Cybern. Syst. 2020, 50, 2257–2272. [Google Scholar] [CrossRef]

- Shen, Q.; Jiang, B.; Shi, P. Adaptive fault diagnosis for T–S fuzzy systems with sensor faults and system performance analysis. IEEE Trans. Fuzzy Syst. 2014, 22, 274–285. [Google Scholar] [CrossRef]

- Shen, Q.; Jiang, B.; Shi, P. Active fault-tolerant control against actuator fault and performance analysis of the effect of time delay due to fault diagnosis. Int. J. Control Autom. Syst. 2017, 15, 537–546. [Google Scholar] [CrossRef]

- Shen, Q.; Jiang, B.; Shi, P. Adaptive fault tolerant control against actuator faults. Int. J. Adapt. Control Signal Process. 2017, 31, 147–162. [Google Scholar] [CrossRef]

- Yang, J.-M.; Hammer, J. Asynchronous sequential machines with adversarial intervention: The use of bursts. Int. J. Control 2010, 83, 956–969. [Google Scholar] [CrossRef]

- Kohavi, Z.; Jha, Z. Switching and Finite Automata Theory, 3rd ed.; Cambridge University Press: Cambridge, UK, 2010. [Google Scholar]

- Xie, G.; Yang, J.; Yang, Y. An improved sparse autoencoder and multilevel denoising strategy for diagnosing early multiple intermittent faults. IEEE Trans. Syst. Man Cybern. Syst. 2021. [Google Scholar] [CrossRef]

- Oreifej, R.S.; Al-Haddad, R.; Zand, R.; Ashraf, R.A.; DeMara, R.F. Survivability modeling and resource planning for self-repairing reconfigurable device fabrics. IEEE Trans. Cybern. 2017, 48, 780–792. [Google Scholar] [CrossRef] [PubMed]

- Yang, J.-M.; Kwak, S.W. Fault diagnosis and fault-tolerant control of input/output asynchronous sequential machines. IET Control Theory Appl. 2012, 6, 1682–1689. [Google Scholar] [CrossRef]

- Özveren, C.M.; Willsky, A.S.; Antsaklis, P.J. Stability and stabilizability of discrete event dynamic systems. J. ACM 1991, 38, 729–751. [Google Scholar] [CrossRef]

- Wang, B.; Feng, J.E.; Meng, M. Matrix approach to model matching of composite asynchronous sequential machines. IET Control Theory Appl. 2017, 11, 2122–2130. [Google Scholar] [CrossRef]

- Wang, J.; Han, X.; Chen, Z.; Zhang, Q. Calculating skeleton matrix of asynchronous sequential machines based on the semi-tensor product of matrices. IET Control Theory Appl. 2017, 11, 2131–2139. [Google Scholar] [CrossRef]

- Gao, Z.; Zhu, J.; Han, R.; Xu, Z.; Ullah, A.; Reviriego, P. Design and implementation of configuration memory SEU-tolerant viterbi decoders in SRAM-based FPGAs. IEEE Trans. Nanotechnol. 2019, 18, 691–699. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).