Investigation of Heavy-Ion Induced Single-Event Transient in 28 nm Bulk Inverter Chain

Abstract

1. Introduction

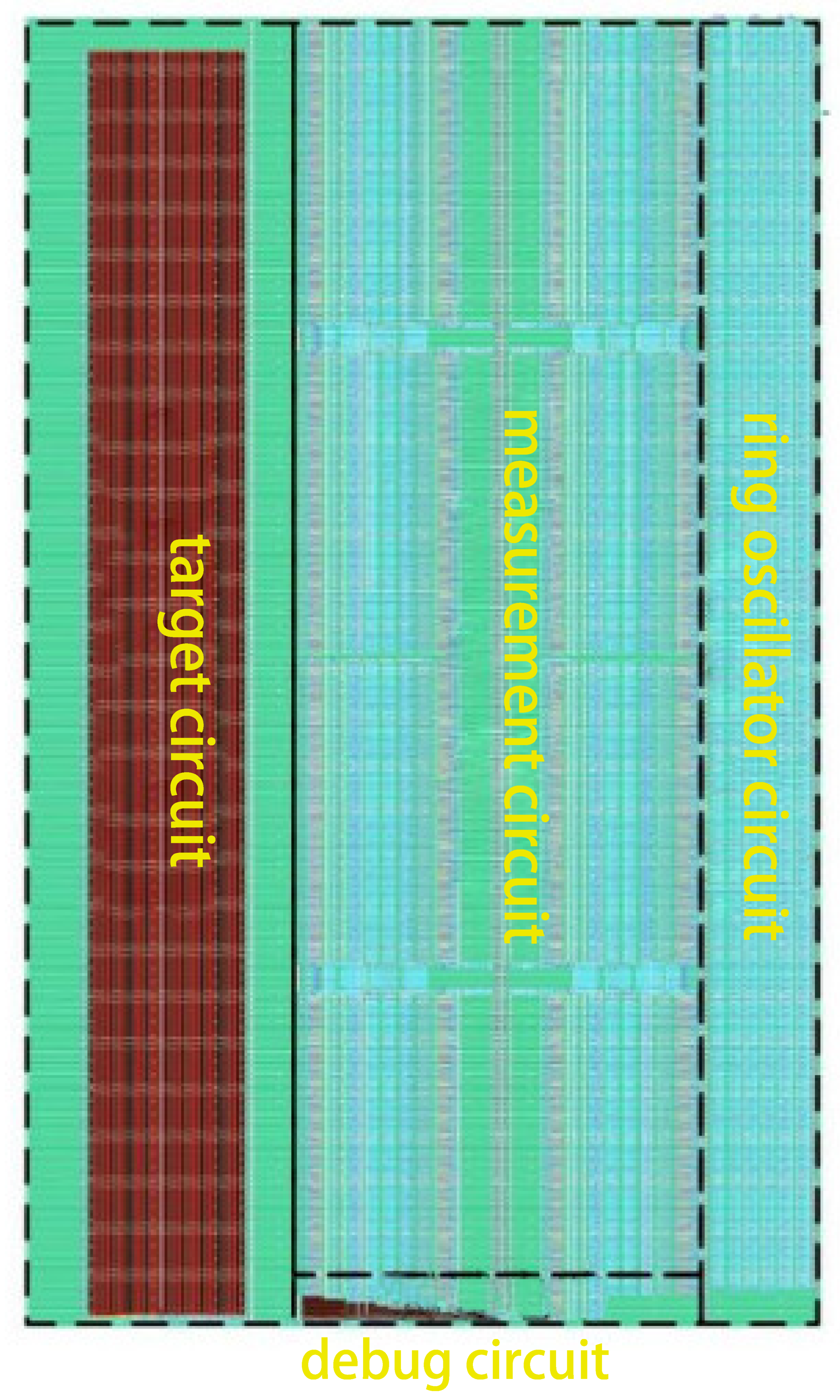

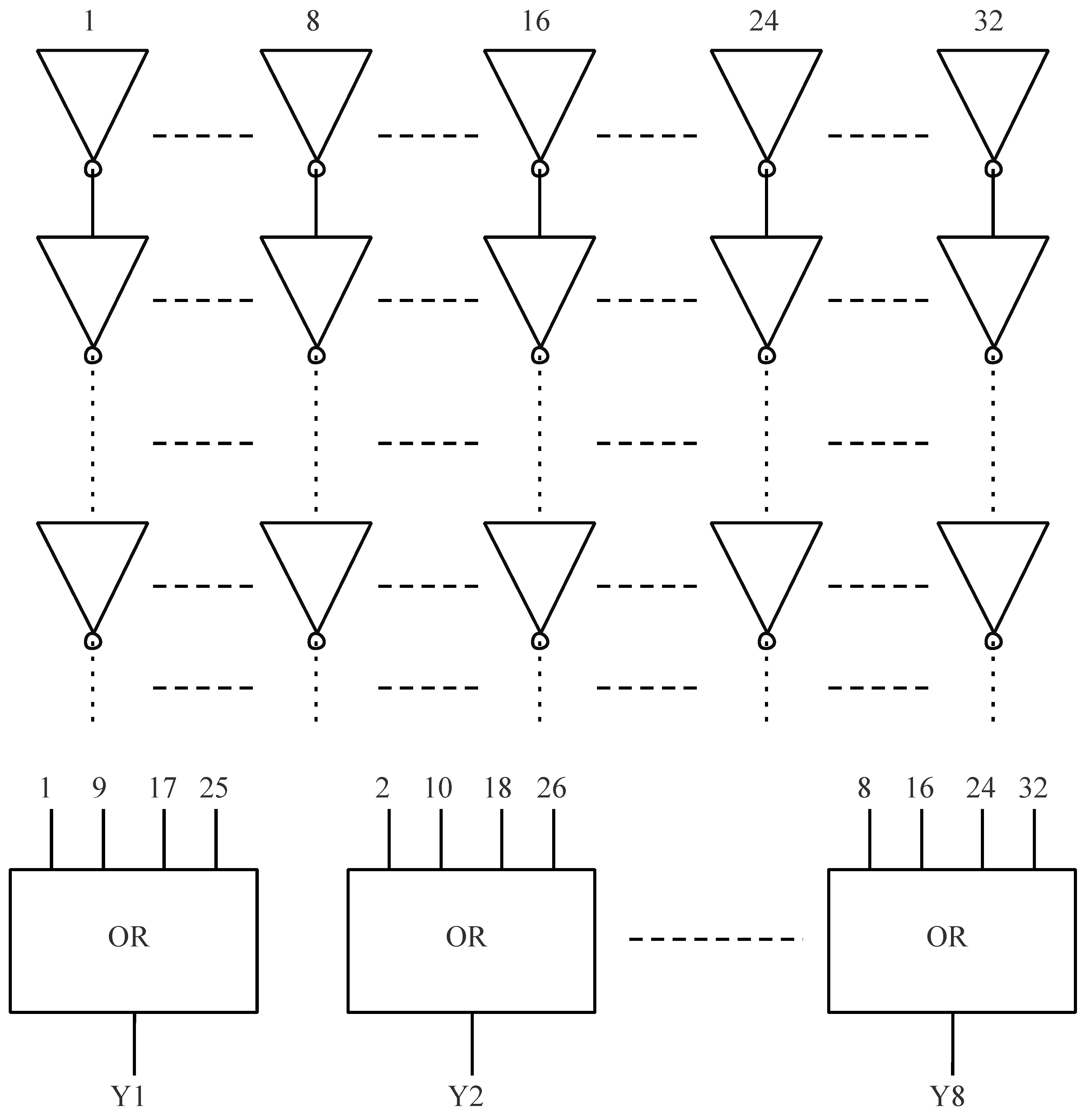

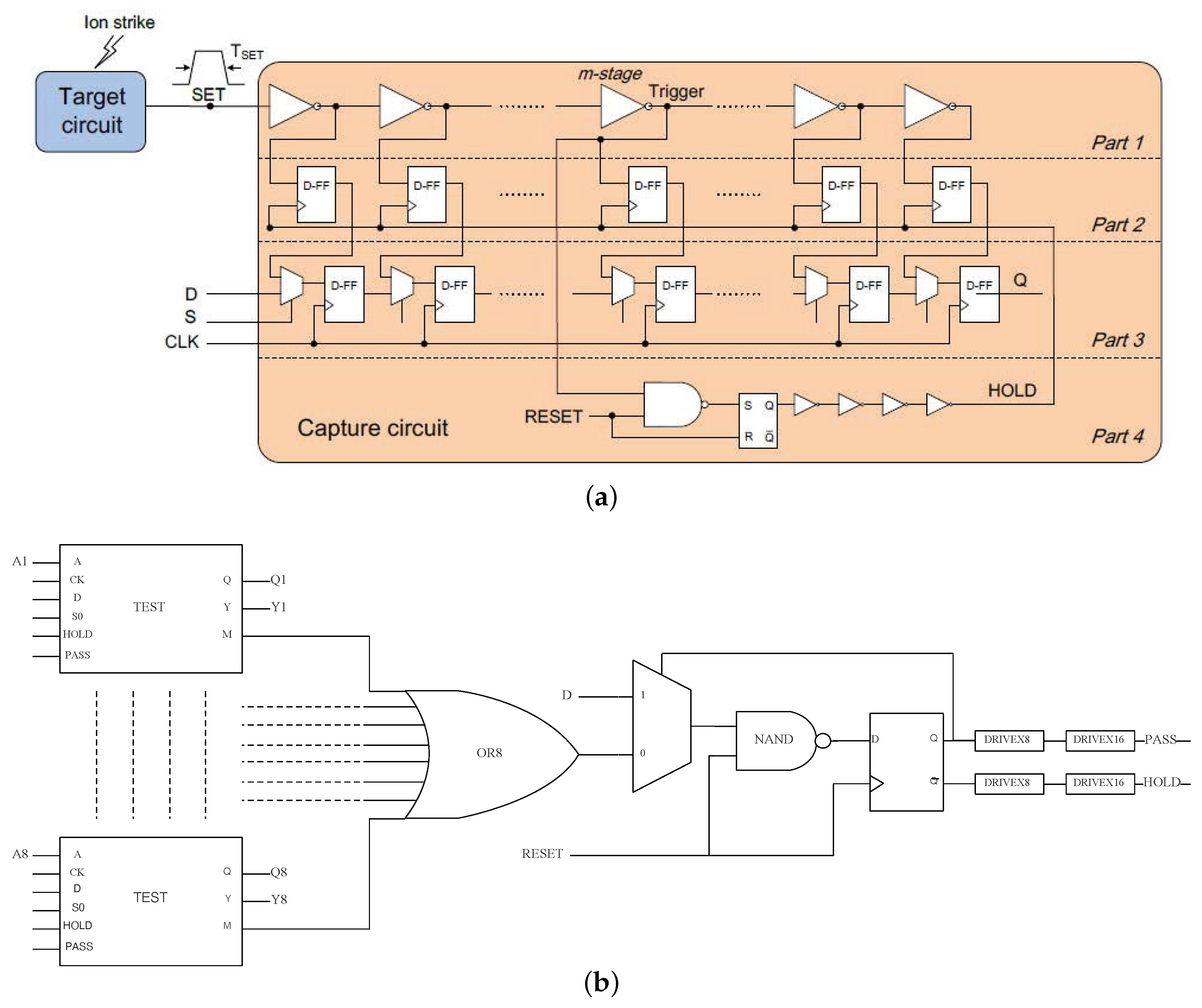

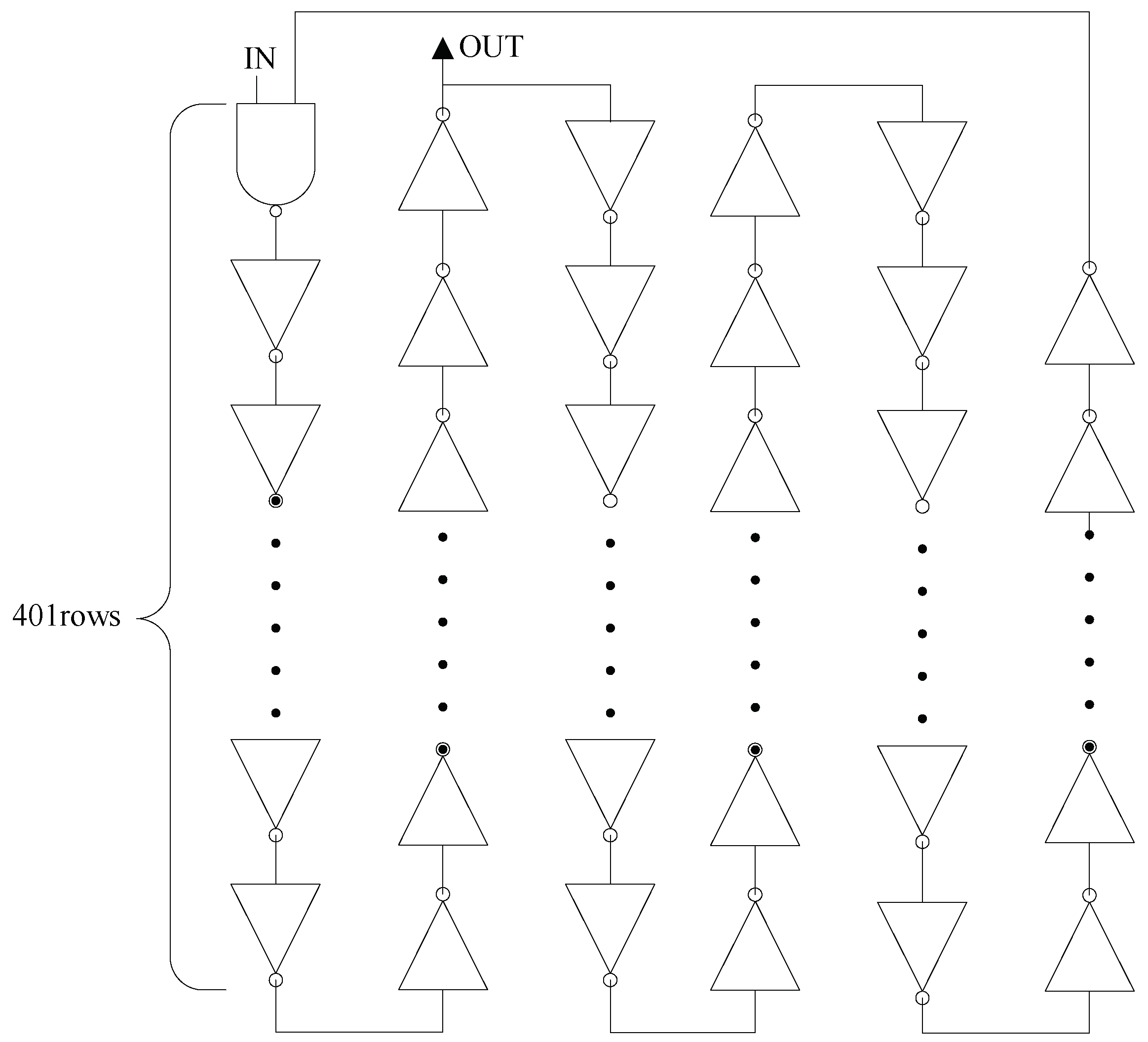

2. Test Chip Structure

3. Experimental Setup

4. Experimental Results

4.1. Inverter Delay and Broadening Factor

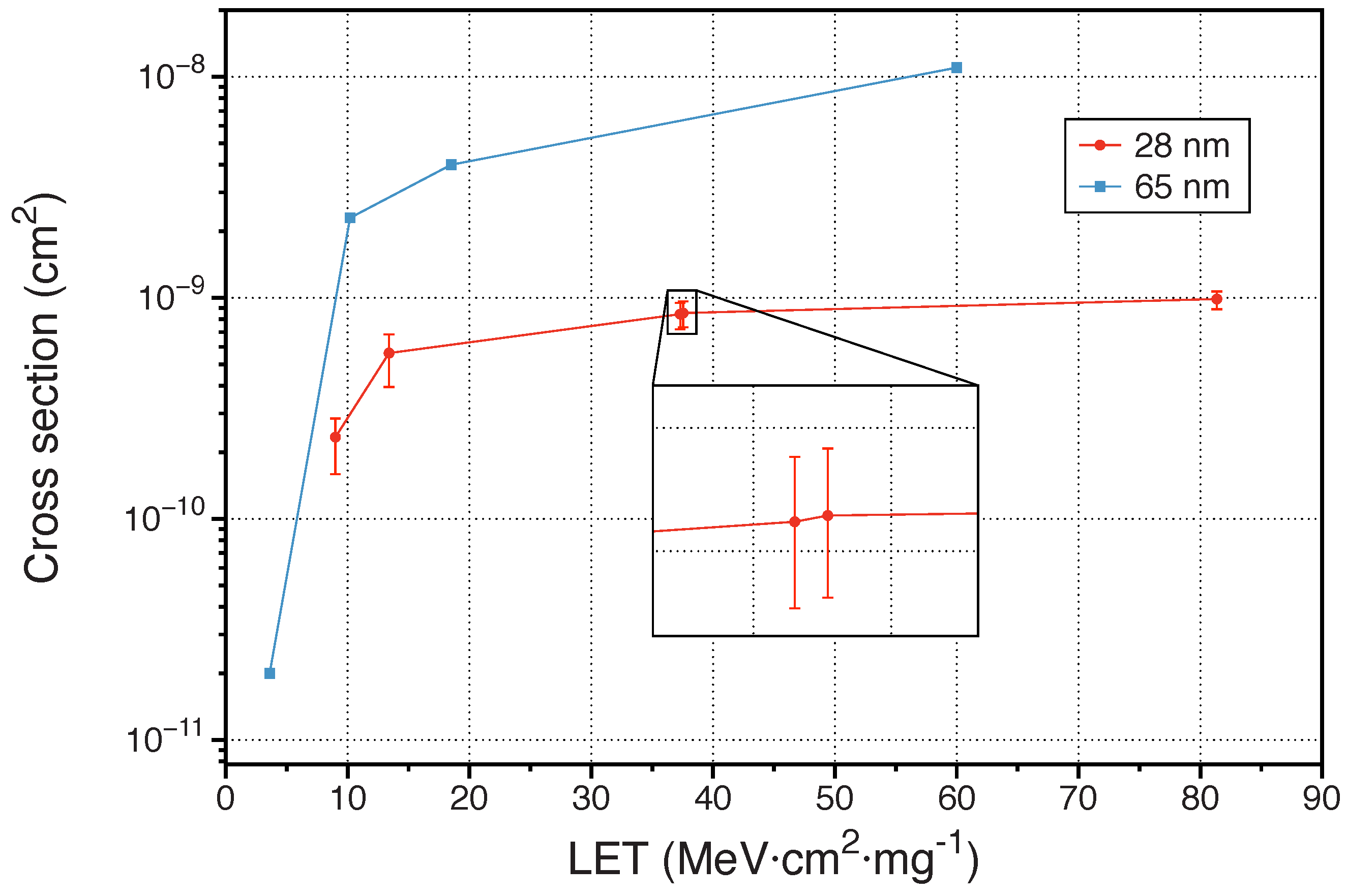

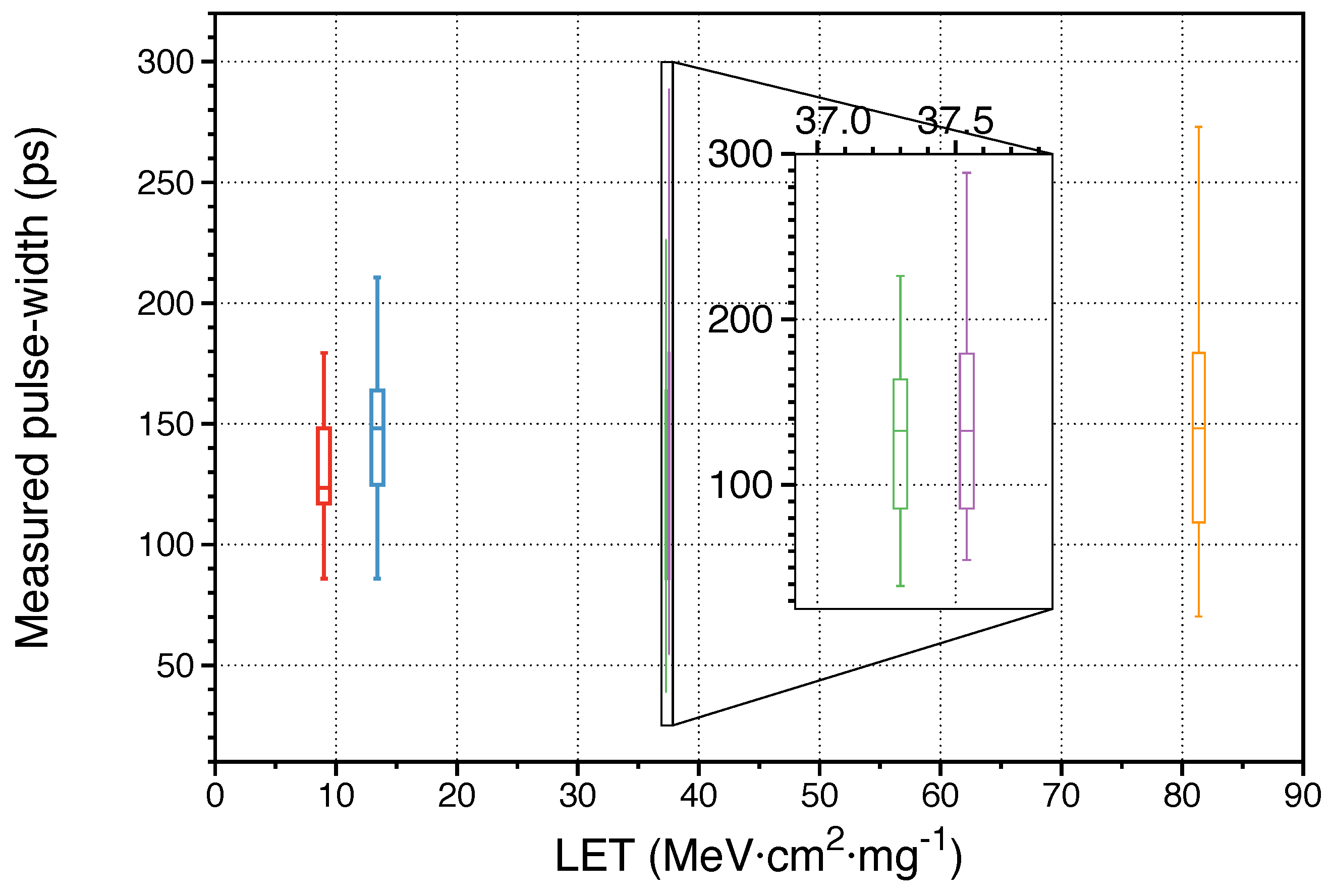

4.2. SET Characterization

5. Discussion

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Dodd, P.; Shaneyfelt, M.; Schwank, J.; Felix, J. Current and future challenges in radiation effects on CMOS electronics. IEEE Trans. Nucl. Sci. 2010, 57, 1747–1763. [Google Scholar] [CrossRef]

- Ferlet-Cavrois, V.; Massengill, L.W.; Gouker, P. Single event transients in digital CMOS—A review. IEEE Trans. Nucl. Sci. 2013, 60, 1767–1790. [Google Scholar] [CrossRef]

- Song, R.; Shao, J.; Liang, B.; Chi, Y.; Chen, J. Characterization of P-hit and N-hit single-event transient using heavy ion microbeam. IEICE Electron. Express 2019. [Google Scholar] [CrossRef]

- Huang, P.; Chen, S.; Chen, J. Single event upset induced by single event double transient and its well-structure dependency in 65-nm bulk CMOS technology. Sci. China Inf. Sci. 2016, 59, 042411. [Google Scholar] [CrossRef]

- Andjelkovic, M.; Petrovic, V.; Nenadovic, M.; Breitenreiter, A.; Krstic, M.; Kraemer, R. Design of an On-chip System for the SET Pulse Width Measurement. In Proceedings of the 2017 Euromicro Conference on Digital System Design (DSD), Vienna, Austria, 30 August–1 September 2017; pp. 111–118. [Google Scholar]

- Glorieux, M.; Evans, A.; Ferlet-Cavrois, V.; Boatella-Polo, C.; Alexandrescu, D.; Clerc, S.; Gasiot, G.; Roche, P. Detailed SET measurement and characterization of a 65 nm bulk technology. IEEE Trans. Nucl. Sci. 2016, 64, 81–88. [Google Scholar] [CrossRef]

- Chen, R.; Chen, W.; Guo, X.; Shen, C.; Zhang, F.; Zheng, L.; Zhao, W.; Ding, L.; Luo, Y.; Guo, H.; et al. Improved on-chip self-triggered single-event transient measurement circuit design and applications. Microelectron. Reliab. 2017, 71, 99–105. [Google Scholar] [CrossRef]

- Huang, P.; Chen, S.; Chen, J.; Liang, B.; Chi, Y. Heavy-ion-induced charge sharing measurement with a novel uniform vertical inverter chains (UniVIC) SEMT test structure. IEEE Trans. Nucl. Sci. 2015, 62, 3330–3338. [Google Scholar] [CrossRef]

- Evans, A.; Glorieux, M.; Alexandrescu, D.; Polo, C.B.; Ferlet-Cavrois, V. Single event multiple transient (SEMT) measurements in 65 nm bulk technology. In Proceedings of the 2016 16th European Conference on Radiation and Its Effects on Components and Systems (RADECS), Bremen, Germany, 19–23 September 2016; pp. 1–6. [Google Scholar]

- Zhao, W.; He, C.; Chen, W.; Chen, R.; Cong, P.; Zhang, F.; Wang, Z.; Shen, C.; Zheng, L.; Guo, X.; et al. Single-event multiple transients in guard-ring hardened inverter chains of different layout designs. Microelectron. Reliab. 2018, 87, 151–157. [Google Scholar] [CrossRef]

- Benedetto, J.; Eaton, P.; Mavis, D.; Gadlage, M.; Turflinger, T. Digital single event transient trends with technology node scaling. IEEE Trans. Nucl. Sci. 2006, 53, 3462–3465. [Google Scholar] [CrossRef]

- Narasimham, B.; Bhuva, B.L.; Schrimpf, R.D.; Massengill, L.W.; Gadlage, M.J.; Amusan, O.A.; Holman, W.T.; Witulski, A.F.; Robinson, W.H.; Black, J.D.; et al. Characterization of digital single event transient pulse-widths in 130-nm and 90-nm CMOS technologies. IEEE Trans. Nucl. Sci. 2007, 54, 2506–2511. [Google Scholar] [CrossRef]

- Gadlage, M.J.; Ahlbin, J.R.; Narasimham, B.; Bhuva, B.L.; Massengill, L.W.; Reed, R.A.; Schrimpf, R.D.; Vizkelethy, G. Scaling trends in SET pulse widths in sub-100 nm bulk CMOS processes. IEEE Trans. Nucl. Sci. 2010, 57, 3336–3341. [Google Scholar] [CrossRef]

- Ahlbin, J.; Gadlage, M.; Ball, D.; Witulski, A.; Bhuva, B.; Reed, R.; Vizkelethy, G.; Massengill, L. The effect of layout topology on single-event transient pulse quenching in a 65 nm bulk CMOS process. IEEE Trans. Nucl. Sci. 2010, 57, 3380–3385. [Google Scholar] [CrossRef]

- Zhang, J.; Chen, J.; Huang, P.; Li, S.; Fang, L. The Effect of Deep N+ Well on Single-Event Transient in 65 nm Triple-Well NMOSFET. Symmetry 2019, 11, 154. [Google Scholar] [CrossRef]

- Chi, Y.; Song, R.; Shi, S.; Liu, B.; Cai, L.; Hu, C.; Guo, G. Characterization of single-event transient pulse broadening effect in 65 nm bulk inverter chains using heavy ion microbeam. IEEE Trans. Nucl. Sci. 2016, 64, 119–124. [Google Scholar] [CrossRef]

- Li, H.; Wu, L.; Yang, B.; Jiang, Y. Analysis of single event transient pulse-width in 65 nm commercial radiation-hardened logic cell. J. Semicond. 2017, 38, 085009. [Google Scholar] [CrossRef]

- Mitrović, M.; Hofbauer, M.; Goll, B.; Schneider-Hornstein, K.; Swoboda, R.; Steindl, B.; Voss, K.O.; Zimmermann, H. Experimental investigation of single-event transient waveforms depending on transistor spacing and charge sharing in 65-nm CMOS. IEEE Trans. Nucl. Sci. 2017, 64, 2136–2143. [Google Scholar] [CrossRef]

- Ferlet-Cavrois, V.; Paillet, P.; McMorrow, D.; Torres, A.; Gaillardin, M.; Melinger, J.; Knudson, A.; Campbell, A.; Schwank, J.; Vizkelethy, G.; et al. Direct measurement of transient pulses induced by laser and heavy ion irradiation in deca-nanometer devices. IEEE Trans. Nucl. Sci. 2005, 52, 2104–2113. [Google Scholar] [CrossRef]

- Narasimham, B.; Ramachandran, V.; Bhuva, B.L.; Schrimpf, R.D.; Witulski, A.F.; Holman, W.T.; Massengill, L.W.; Black, J.D.; Robinson, W.H.; McMorrow, D. On-chip characterization of single-event transient pulsewidths. IEEE Trans. Device Mater. Reliab. 2006, 6, 542–549. [Google Scholar] [CrossRef]

| DC Sets.Num. | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| Stages.Count | 6 | 10 | 16 | 20 | 26 | 30 | 36 | 40 |

| Ion | Energy [MeV] | Incident Range [m] | LET [] | Flux [] | Fluence [] |

|---|---|---|---|---|---|

| 28Si12+ | 143 | 54.5 | 9.0 | ||

| 35Cl13+ | 150 | 42.8 | 13.4 | ||

| 74Ge19+ | 208 | 30.3 | 37.3 | ||

| 86Kr26+ | 482.7 | 58.8 | 37.54 | ||

| 181Ta31+ | 1400.8 | 83.3 | 81.35 |

| DC Sets.Num. | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 |

|---|---|---|---|---|---|---|---|---|

| Expected pulse-width [ps] | 46.8 | 78 | 124.8 | 156 | 202.8 | 234 | 280.8 | 312 |

| Captured pulse-width [ps] | 0 | 85.8 | 132.6 | 179.4 | 226.2 | 257.4 | 304.2 | 335.4 |

| Passed INV count | 0 | 150 | 156 | 156 | 152 | 152 | 156 | 158 |

| Broadening factor [ps/stage] | 0 | 0.052 | 0.050 | 0.150 | 0.153 | 0.153 | 0.150 | 0.148 |

| LET [] | 9.0 | 13.4 | 37.3 | 37.54 | 81.35 |

|---|---|---|---|---|---|

| Average width [ps] | 128.7 | 130.6 | 131.4 | 139.4 | 154.7 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wu, A.; Liang, B.; Chi, Y.; Wu, Z. Investigation of Heavy-Ion Induced Single-Event Transient in 28 nm Bulk Inverter Chain. Symmetry 2020, 12, 624. https://doi.org/10.3390/sym12040624

Wu A, Liang B, Chi Y, Wu Z. Investigation of Heavy-Ion Induced Single-Event Transient in 28 nm Bulk Inverter Chain. Symmetry. 2020; 12(4):624. https://doi.org/10.3390/sym12040624

Chicago/Turabian StyleWu, Anquan, Bin Liang, Yaqing Chi, and Zhenyu Wu. 2020. "Investigation of Heavy-Ion Induced Single-Event Transient in 28 nm Bulk Inverter Chain" Symmetry 12, no. 4: 624. https://doi.org/10.3390/sym12040624

APA StyleWu, A., Liang, B., Chi, Y., & Wu, Z. (2020). Investigation of Heavy-Ion Induced Single-Event Transient in 28 nm Bulk Inverter Chain. Symmetry, 12(4), 624. https://doi.org/10.3390/sym12040624