The ESD Robustness and Protection Technology of P-GaN HEMT

Abstract

1. Introduction

2. ESD Evaluation Models and Evaluation Methods

2.1. Electrostatic Discharge Models

2.1.1. Human Body Model (HBM)

2.1.2. Machine Model (MM)

2.1.3. Charged Device Model (CDM)

2.2. Transmission Line Pulse (TLP) Testing Platform

3. ESD Robustness of P-GaN HEMT’s Gate Structure

4. ESD Protection Technology for P-GaN HEMT’s Gate Structure

4.1. Unidirectional ESD Protection Technology

4.1.1. Resistive Voltage-Division and Diode Voltage-Division Unidirectional ESD Protection Technologies [12,13,14,16,20]

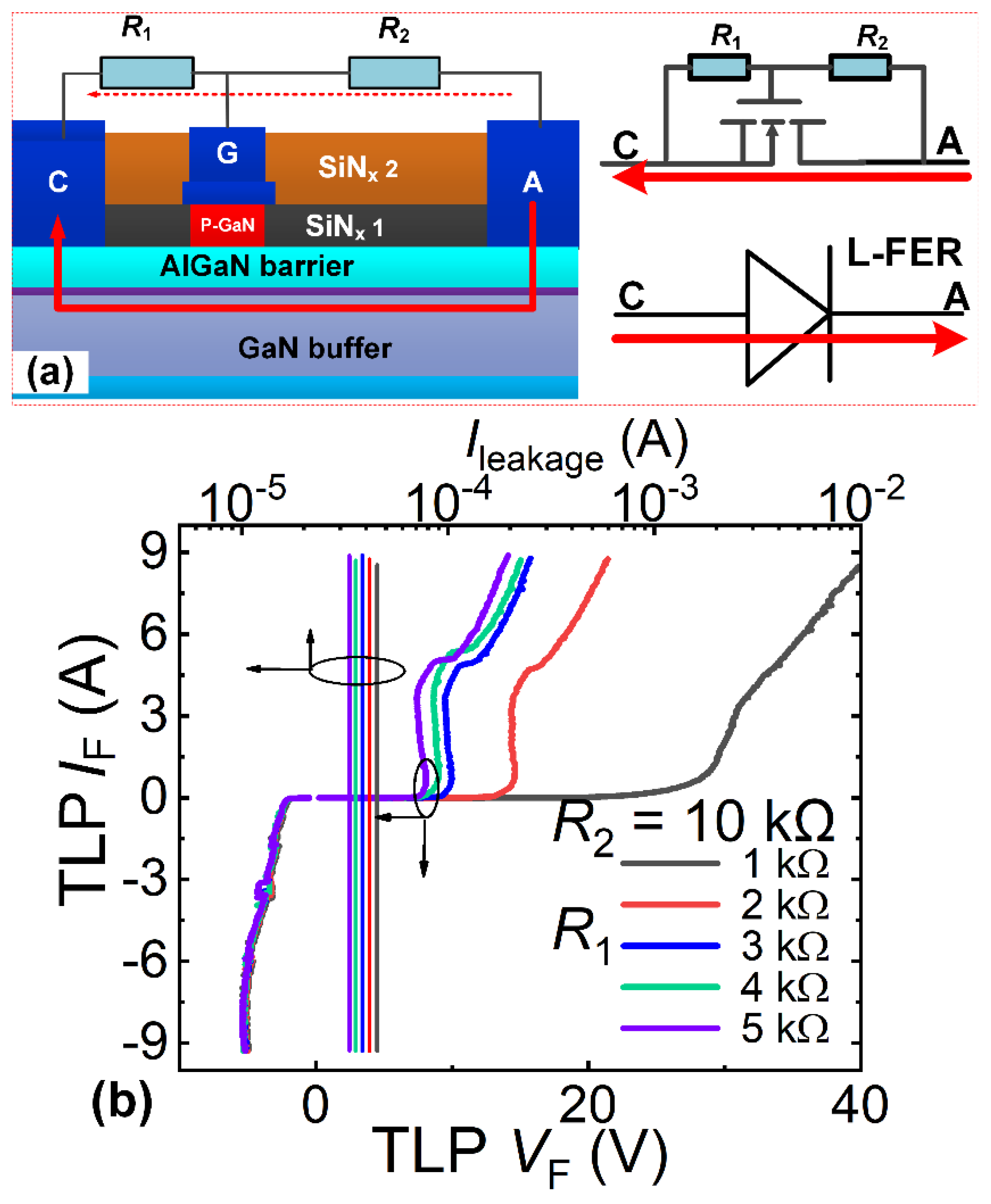

4.1.2. Operating Principle and Characteristics of Resistive Voltage-Division Structure [13,14,20]

4.1.3. Operating Principle and Characteristics of Diode Voltage-Division Structure [12,16]

4.1.4. Transient Charge Modulation-Based Unidirectional ESD Protection [15]

4.2. Bidirectional ESD Protection Technology

4.2.1. Resistive Voltage-Division Bidirectional ESD Protection Technology [20]

4.2.2. Diode Voltage-Division Bidirectional ESD Protection Technology [21]

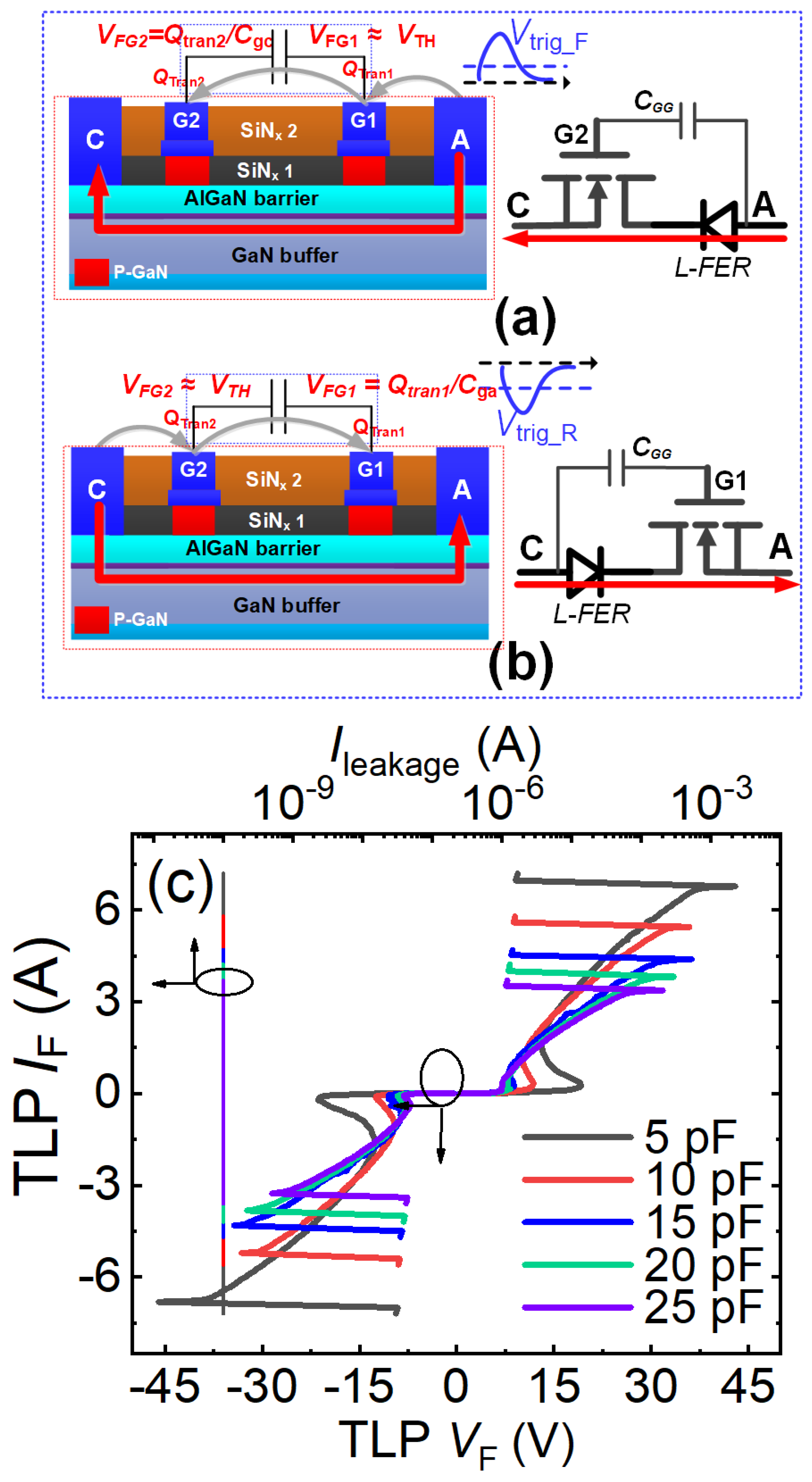

4.2.3. Transient Charge Modulation-Based Bidirectional ESD Protection [18,19]

- ◆

- With Common-Drain Bidirectional Switch as Discharge Path

- ◆

- With Common-Source Bidirectional Switch as Discharge Path

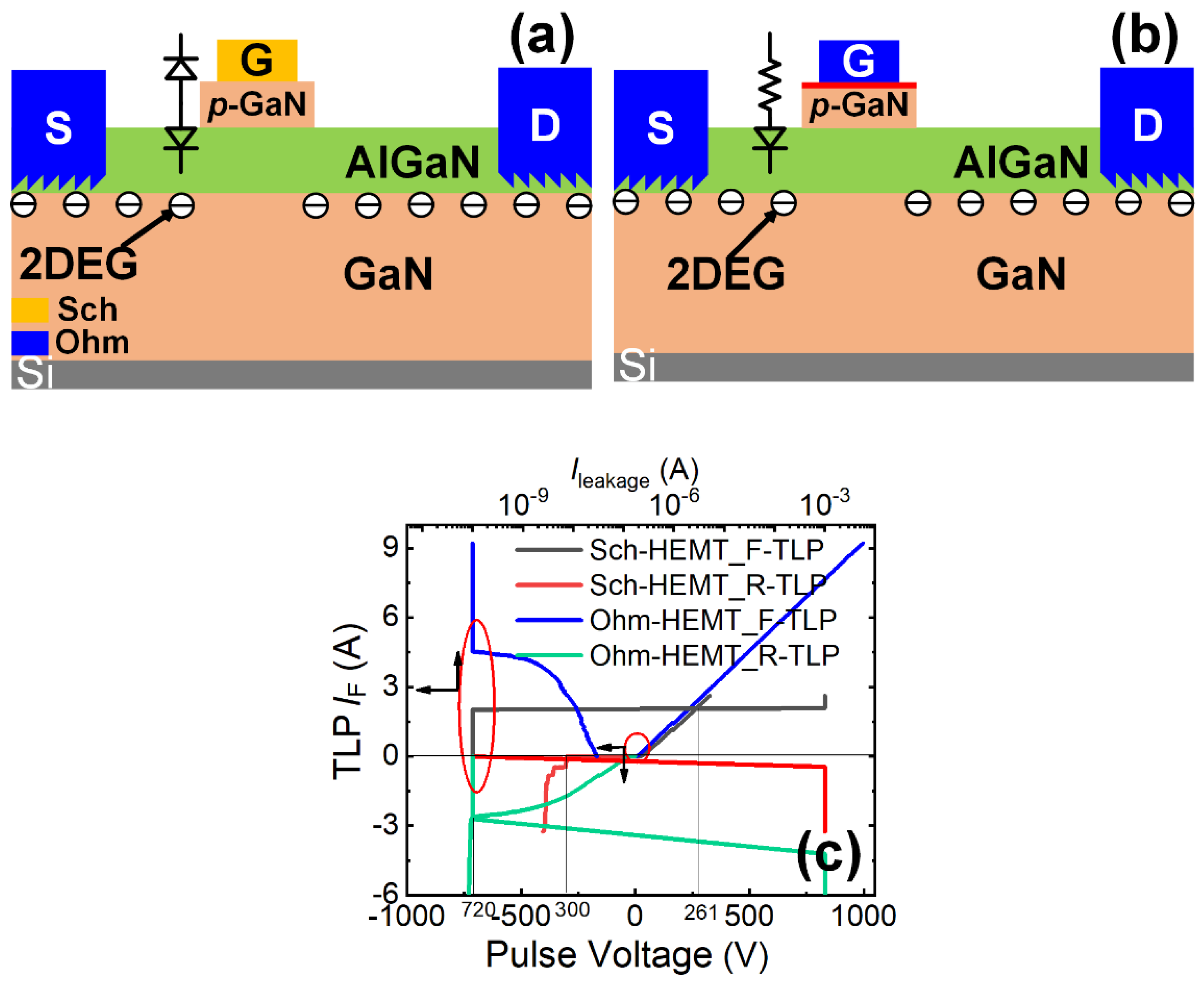

4.3. Ohm/Sch Hybrid (Hyb.) Gate Technology [27]

5. Prospect

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Chen, K.J.; Haberlen, O.; Lidow, A.; Tsai, C.L.; Ueda, T.; Uemoto, Y.; Wu, Y. GaN-on-Si Power Technology: Devices and Applications. IEEE Trans. Electron Devices 2017, 64, 779–795. [Google Scholar] [CrossRef]

- Sun, N.; Huang, H.; Sun, Z.; Wang, R.; Li, S.; Tao, P.; Ren, Y.; Song, S.; Wang, H.; Li, S.; et al. Improving Gate Reliability of 6-in E-Mode GaN-Based MIS-HEMTs by Employing Mixed Oxygen and Fluorine Plasma Treatment. IEEE Trans. Electron Devices 2022, 69, 82–87. [Google Scholar] [CrossRef]

- Wei, J.; Zhang, L.; Zheng, Z.; Song, W.; Yang, S.; Chen, K.J. ON-Resistance Analysis of GaN Reverse-Conducting HEMT with Distributive Built-in SBD. IEEE Trans. Electron Devices 2022, 69, 644–649. [Google Scholar] [CrossRef]

- Rossetto, I.; Meneghini, M.; Barbato, M.; Rampazzo, F.; Marcon, D.; Meneghesso, G.; Zanoni, E. Demonstration of Field-and Power-Dependent ESD Failure in AlGaN/GaN RF HEMTs. IEEE Trans. Electron Devices 2015, 62, 2830–2836. [Google Scholar] [CrossRef]

- Shankar, B.; Raghavan, S.; Shrivastava, M. ESD Reliability of AlGaN/GaN HEMT Technology. IEEE Trans. Electron Devices 2019, 66, 3756–3763. [Google Scholar] [CrossRef]

- Kuzmík, J.; Pogany, D.; Gornik, E.; Javorka, P.; Kordoš, P. Electrostatic Discharge Effects in AlGaN/GaN High-Electron-Mobility Transistors. Appl. Phys. Lett. 2003, 83, 4655–4657. [Google Scholar] [CrossRef]

- Chen, W.; Wong, K.; Chen, K. Single-Chip Boost Converter Using Monolithically Integrated AlGaN/GaN Lateral Field-Effect Rectifier and Normally off HEMT. IEEE Electron Device Letters 2009, 30, 430–432. [Google Scholar] [CrossRef]

- Kong, C.; Zhou, J.; Kong, Y.; Ni, J.; Chen, T. Monolithically Integrated E/D Mode MIS GaN HEMTs and Inverters on Si Substrate. In Proceedings of the International Conference on Electron Devices and Solid-State Circuits (EDSSC), Chengdu, China, 18–20 June 2014; pp. 1–2. [Google Scholar]

- Li, X.; Amirifar, N.; Geens, K.; Zhao, M.; Guo, W.; Liang, H.; You, S.; Posthuma, N.; De Jaeger, B.; Stoffels, S.; et al. GaN-on-SOI: Monolithically Integrated All-GaN ICs for Power Conversion. In Proceedings of the International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 4.4.1–4.4.4. [Google Scholar]

- Ren, J.; Liu, C.; Tang, C.W.; Lau, K.M.; Sin, J.K.O. Switching Characteristics of Monolithically Integrated Si-GaN Cascoded Rectifiers. In Proceedings of the International Symposium on Power Semiconductor Devices and ICs (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 223–226. [Google Scholar]

- Li, X.; Geens, K.; Guo, W.; You, S.; Zhao, M.; Fahle, D.; Odnoblyudov, V.; Groeseneken, G.; Decoutere, S. Demonstration of GaN integrated half-bridge with on-chip drivers on 200-mm engineered substrates. IEEE Electron Device Lett. 2019, 40, 1499–1502. [Google Scholar] [CrossRef]

- Zhou, C.; Guan, Y.; Shen, J.; Liao, H.; Zhao, Q.; He, C.; Wu, Y.; Lin, W.; Zhang, T.; Chen, Y.; et al. On-Chip Gate ESD Protection for AlGaN/GaN E-Mode Power HEMT Delivering >2kV HBM ESD Capability. In Proceedings of the 2017 Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Raleigh, NC, USA, 30 October–1 November 2019; pp. 175–176. [Google Scholar]

- Xin, Y.; Chen, W.; Sun, R.; Wang, F.; Deng, X.; Li, Z.; Zhang, B. Simulation Study of a High Gate-to-Source ESD Robustness Power p-GaN HEMT with Self-Triggered Discharging Channel. IEEE Trans. Electron Devices 2021, 68, 4536–4542. [Google Scholar] [CrossRef]

- Xin, Y.; Chen, W.; Sun, R.; Wang, F.; Liu, C.; Deng, X.; Li, Z.; Zhang, B. Experimental Demonstration of an Integrated Bidirectional Gate ESD Protection Structure for p-GaN Power HEMTs. IEEE Electron Device Letters 2024, 44, 209–212. [Google Scholar] [CrossRef]

- Shi, Y.; Chen, Y.; Huang, Y.; He, Z.; Chen, W.; Sun, R.; Yao, B.; Wang, H.; Xiao, Q.; Lu, G.; et al. A Novel Gate-to-Source ESD Protection Clamp for GaN HEMT. IEEE Trans. Electron Devices 2022, 69, 3648–3653. [Google Scholar] [CrossRef]

- Shi, Y.; He, Z.; Huang, Y.; Cai, Z.; Chen, Y.; Liu, C.; Liu, C.; Chen, W.; Sun, R.; Lu, G. Experimental Investigation and Model Analysis on a GaN Electrostatic Discharge Clamp. J. Electron Devices Soc. 2022, 10, 976–981. [Google Scholar] [CrossRef]

- Sagawa, M.; Miki, H.; Mori, Y.; Shimizu, H.; Shima, A. Evaluation of Gate Oxide Reliability in 3.3 kV 4H-SiC DMOSFET with J-Ramp TDDB Methods. In Proceedings of the 2018 International Symposium on Power Semiconductor Devices and ICs (ISPSD), Chicago, IL, USA, 13–17 May 2018; pp. 363–366. [Google Scholar]

- Liu, C.; Shi, Y.; He, Z.; Cai, Z.; Huang, X.; Chen, Y.; Chen, W.; Sun, R.; Lu, G.; Zhang, B. A GaN Lateral Bidirectional ESD Clamp Based on the Floating-Gate MBS and a Regulating Capacitor. IEEE Trans. Electron Devices 2023, 71, 510–515. [Google Scholar] [CrossRef]

- Yao, B.; Shi, Y.; Wang, H.; Xu, X.; Chen, Y.; He, Z.; Xiao, Q.; Wang, L.; Lu, G.; Li, H.; et al. A Novel Bidirectional AlGaN/GaN ESD Protection Diode. Micromachines 2022, 13, 135. [Google Scholar] [CrossRef]

- He, Z.; Shi, Y.; Huang, Y.; Chen, Y.; Wang, H.; Wang, L.; Lu, G.; Xin, Y. A Novel AlGaN/GaN Transient Voltage Suppression Diode with Bidirectional Clamp Capability. Micromachines 2022, 13, 299. [Google Scholar] [CrossRef] [PubMed]

- Ma, Y.; Li, S.; Li, M.; Lu, W.; Wang, L.; Ma, J.; Ye, R.; Wei, J.; Zhang, L.; Zhang, C.; et al. Monolithically Integrated Bidirectional Gate ESD Protection Scheme of p-GaN Power HEMT by Dual-Gate Device Technology. IEEE Trans. Power Electron. 2025, 40, 2721–2725. [Google Scholar] [CrossRef]

- Shi, Y.; He, Z.; Huang, Y.; Cai, Z.; Chen, Y.; Cheng, L.; Chen, W.; Sun, R.; Liu, C.; Lu, G.; et al. A Comparative Study on G-to-S ESD Robustness of the Ohmic-Gate and Schottky-Gate p-GaN HEMTs. IEEE Trans. Electron Devices 2023, 70, 2229–2234. [Google Scholar] [CrossRef]

- Shi, Y.; Zhao, D.; Shen, Z.; Wu, L.; He, L.; Jiang, X.; Yang, G.; Xiao, Q.; Chen, X.; Chen, Y.; et al. The ESD Robustness of Schottky-Gate p-GaN HEMT under Different States. IEEE Trans. Electron Devices 2025, 72, 4810–4816. [Google Scholar] [CrossRef]

- Sayadi, L.; Iannaccone, G.; Sicre, S.; Sicre, S.; Häberlen, O. Threshold voltage instability in p-GaN gate AlGaN/GaN HFETs. Trans. Electron Devices 2018, 65, 2454–2460. [Google Scholar] [CrossRef]

- He, J.; Tang, G.; Chen, K.J. VTH instability of p-GaN gate HEMTs under static and dynamic gate stress. Electron Device Lett. 2018, 39, 1576–1579. [Google Scholar] [CrossRef]

- Shi, Y.; Zhou, Q.; Cheng, Q.; Wei, P.; Zhu, L.; Wei, D.; Zhang, A.; Chen, W.; Zhang, B. Carrier transport mechanisms underlying the bidirectional VTH shift in p-GaN gate HEMTs under forward gate stress. Trans. Electron Devices 2019, 66, 876–882. [Google Scholar] [CrossRef]

- Ma, Y.; Li, S.; Wang, L.; Yang, H.; Lu, W.; Li, M.; Ma, J.; Ye, R.; Wang, D.; Zhou, J.; et al. Improved Gate ESD Behaviors of p-GaN Power HEMTs by Hybrid Gate Technology. In Proceedings of the 2024 International Symposium on Power Semiconductor Devices and ICs, Bremen, Germany, 2–6 June 2024; IEEE: Bremen, Germany, 2024; pp. 1–4. [Google Scholar]

- Li, X.; Pan, Z.; Hao, W.; Miao, R.; Yue, Z.; Wang, A. On-Chip ESD Protection: Device Innovation. IEEE Electron Devices Rev. 2024, 1, 1–15. [Google Scholar] [CrossRef]

- Hao, W.; Pan, Z.; Li, X.; Miao, R.; Yue, Z.; Wang, A. On-Chip ESD Protection: Design Innovation. IEEE Electron Devices Rev. 2024, 2, 32–51. [Google Scholar] [CrossRef]

- Wang, C.; Wang, X.S.; Zhang, F.; Li, C.; Di, M.; Wang, A. ESD and RF Switch Co-Design in SOI CMOS for Smartphones from 2G to 5G. In Proceedings of the 2018 Texas Symposium on Wireless and Microwave Circuits and Systems (WMCS), Waco, TX, USA, 5–6 April 2018; pp. 1–4. [Google Scholar]

- Fujiwara, S. ESD Robustness Enhancement Study of Ultra-High-Voltage JFET With Ballast Structure. IEEE Trans. Device Mater. Reliab. 2017, 17, 616–623. [Google Scholar] [CrossRef]

- Fujiwara, S.; Burton, R. ESD Robust 800V SCR-JFET with p+ Ballast Structure. In Proceedings of the 2016 38th Electrical Overstress/Electrostatic Discharge Symposium (EOS/ESD), Garden Grove, CA, USA, 11–16 September 2016; pp. 1–6. [Google Scholar]

- Kim, S.; LaFonteese, D.; Zhu, D.; Sridhar, D.S.; Pendharkar, S.; Endoh, H.; Boku, K. A New ESD Self-Protection Structure for 700V High Side Gate Drive IC. In Proceedings of the 2017 29th International Symposium on Power Semiconductor Devices and IC’s (ISPSD), Sapporo, Japan, 28 May–1 June 2017; pp. 467–470. [Google Scholar]

- Vashchenko, V.A.; Gallerano, A.; Shibkov, A. On Chip ESD Protection of 600V Voltage Node. In Proceedings of the 2011 IEEE 23rd International Symposium on Power Semiconductor Devices and ICs, San Diego, CA, USA, 23–26 May 2011; pp. 128–131. [Google Scholar]

- Ker, M.-D.; Hsu, K.-C. Overview of On-Chip Electrostatic Discharge Protection Design with SCR-Based Devices in CMOS Integrated Circuits. IEEE Trans. Device Mater. Reliab. 2005, 5, 235–249. [Google Scholar]

- Ker, M.-D.; Lin, K.-H.; Chuang, C.-H. MOS-Bounded Diodes for On-Chip ESD Protection in a 0.15-μm Shallow-Trench-Isolation Salicided CMOS Process. In Proceedings of the 2003 International Symposium on VLSI Technology, Systems and Applications, Hsinchu, Taiwan, 6–8 October 2003; pp. 84–87. [Google Scholar]

- Li, X.; Pan, Z.; Hao, W.; Miao, R.; Yue, Z.; Wang, A. Interposer-Based ESD Protection: A Potential Solution for μ-Packaging Reliability of 3D Chips. Micromachines 2025, 16, 488. [Google Scholar] [CrossRef]

- Khazhinsky, M.; Harb, M.; Meng, K.-H. ESD and Latch-Up Design Verification Challenges in Packaged Parts and Modules. In Proceedings of the 2024 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 15–18 July 2024. [Google Scholar]

- Emon, A.I.; Carlton, H.; Harris, J.; Krone, A.; Hassan, M.U.; Mirza, A.B.; Hossain, M.; Rashid, A.U.; Chen, Y.; Luo, F.; et al. Design and Optimization of Gate Driver Integrated Multichip 3-D GaN Power Module. IEEE Trans. Transp. Electrif. 2022, 8, 4391–4407. [Google Scholar] [CrossRef]

- Sun, R.; Lai, J.; Chen, W.; Zhang, B. GaN Power Integration for High Frequency and High Efficiency Power Applications: A Review. IEEE Access 2020, 8, 15529–15542. [Google Scholar] [CrossRef]

- Rosenbaum, E.; Shukla, V.; Keel, M.-S. ESD Protection Networks for 3D Integrated Circuits. In Proceedings of the 2011 IEEE International 3D Systems Integration Conference (3DIC), Osaka, Japan, 31 January–2 February 2012. [Google Scholar]

- Khodadadian, E.Z. Investigating the Effect of the DC Block Capacitor on Residual Current in a System-Level ESD-Protected Circuit. IEEE Electromagn. Compat. Mag. 2023, 12, 39–45. [Google Scholar] [CrossRef]

- Liang, C.-Y.; Ker, M.-D. Electrostatic Discharge Protection Design with Wide Bandwidth Matching Network for Radio-Frequency Integrated Circuits. IEEE Trans. Microw. Theory Tech. 2025, 73, 6162–6171. [Google Scholar] [CrossRef]

- Charvaka, D.; Gossner, H. (Eds.) System Level ESD Co-Design; John Wiley & Sons: Hoboken, NJ, USA, 2015. [Google Scholar]

- Vladislav, A.V.; Shibkov, A. System-Level and Discrete Components ESD. In ESD Design for Analog Circuits; Springer: Boston, MA, USA, 2010; pp. 395–444. [Google Scholar]

- Extremely Low Capacitance Bidirectional ESD Protection Diode. Available online: https://www.nexperia.cn/product/PESD5V0X1BCL-Q (accessed on 24 April 2023).

- Ultra Low Capacitance Quadruple Rail-to-Rail ESD Protection. Available online: https://www.nexperia.cn/product/PRTR5V0U4D-Q (accessed on 8 July 2022).

- GaNFast™ Power IC. Available online: https://navitassemi.com/wp-content/plugins/gb-navitas-stock-checker/product_files/NV6115-Datasheet.pdf (accessed on 22 July 2024).

- InnoSwitch4-QR. 2024. Available online: https://www.powerint.cn/sites/default/files/documents/innoswitch4-qr_family_data_sheet_zh-hans.pdf?language=zh-hans (accessed on 1 February 2024).

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Shi, Y.; Chen, Y.; He, L.; Chen, X.; Chen, Y.; Lu, G. The ESD Robustness and Protection Technology of P-GaN HEMT. Micromachines 2025, 16, 1269. https://doi.org/10.3390/mi16111269

Shi Y, Chen Y, He L, Chen X, Chen Y, Lu G. The ESD Robustness and Protection Technology of P-GaN HEMT. Micromachines. 2025; 16(11):1269. https://doi.org/10.3390/mi16111269

Chicago/Turabian StyleShi, Yijun, Yantao Chen, Liang He, Xinghuan Chen, Yuan Chen, and Guoguang Lu. 2025. "The ESD Robustness and Protection Technology of P-GaN HEMT" Micromachines 16, no. 11: 1269. https://doi.org/10.3390/mi16111269

APA StyleShi, Y., Chen, Y., He, L., Chen, X., Chen, Y., & Lu, G. (2025). The ESD Robustness and Protection Technology of P-GaN HEMT. Micromachines, 16(11), 1269. https://doi.org/10.3390/mi16111269