A 7.6-nW 1-kS/s 10-Bit SAR ADC for Biomedical Applications

Abstract

1. Introduction

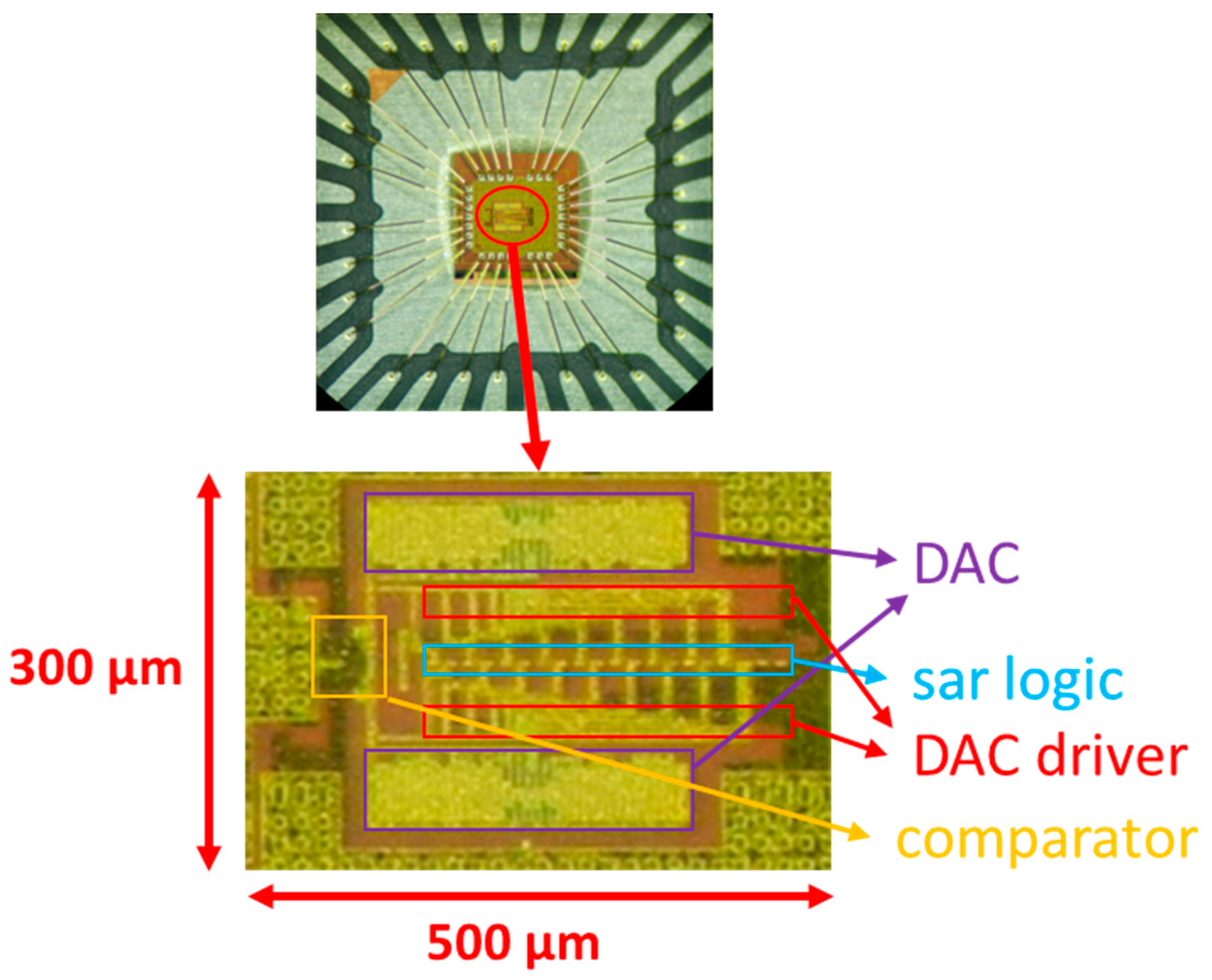

2. Proposed ADC Architecture

2.1. Switching Scheme

2.2. Automatic ON/OFF Comparator

2.3. Automatic ON/OFF SAR Logic

2.4. DAC Driver Circuit

2.5. Capacitor Array

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Weibo, H.; Yen-Ting, L.; Tam, N.; Lie, D.Y.C.; Ginsburg, B.P. An 8-Bit Single-Ended Ultra-Low-Power SAR ADC With a Novel DAC Switching Method and a Counter-Based Digital Control Circuitry. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1726–1739. [Google Scholar] [CrossRef]

- Aneesh, K.; Manoj, G.; Sam, S.S. Design Approaches of Ultra-Low Power SAR ADC for Biomedical Systems—A Review. J. Circuits Syst. Comput. 2022, 31, 2230009. [Google Scholar] [CrossRef]

- Mao, W.; Li, Y.; Heng, C.; Lian, Y. A Low Power 12-bit 1-kS/s SAR ADC for Biomedical Signal Processing. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 477–488. [Google Scholar] [CrossRef]

- Hou, Y.; Qu, J.; Tian, Z.; Atef, M.; Yousef, K.; Lian, Y.; Wang, G. A 61-nW Level-Crossing ADC with Adaptive Sampling for Biomedical Applications. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 56–60. [Google Scholar] [CrossRef]

- Kamata, T.; Ueda, M.; Hirai, Y.; Tani, S.; Asano, T.; Isami, S.; Kurata, T.; Tatsumi, K.; Matsuoka, T. An analog front-end employing 87 dB SNDR stochastic SAR-ADC for a biomedical sensor. In Proceedings of the 2017 15th IEEE International New Circuits and Systems Conference (NEWCAS), Strasbourg, France, 25–28 June 2017; pp. 301–304. [Google Scholar] [CrossRef]

- Zhangming, Z.; Yuhua, L. A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC in 0.18-um CMOS for Medical Implant Devices. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 2167–2176. [Google Scholar] [CrossRef]

- Byung-Geun, L. Power and Bandwidth Scalable 10-b 30-MS/s SAR ADC. IEEE Trans. Very Large Scale Integr. VLSI Syst. 2015, 23, 1103–1110. [Google Scholar] [CrossRef]

- Ginsburg, B.P.; Chandrakasan, A.P. An energy-efficient charge recycling approach for a SAR converter with capacitive DAC. In Proceedings of the 2005 IEEE International Symposium on Circuits and Systems, Kobe, Japan, 23–26 May 2005; pp. 184–187. [Google Scholar] [CrossRef]

- Yan, Z.; Chi-Hang, C.; Chio, U.F.; Sai-Weng, S.; Seng-Pan, U.; Martins, R.P.; Maloberti, F. A 10-bit 100-MS/s Reference-Free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 2010, 45, 1111–1121. [Google Scholar] [CrossRef]

- Liu, C.C.; Chang, S.J.; Huang, G.Y.; Lin, Y.Z. A 10-bit 50-MS/s SAR ADC With a Monotonic Capacitor Switching Procedure. IEEE J. Solid-State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- Johns, D.; Martin, K. Analog Integrated Circuit Design; John Wiley & Sons, Inc.: New York, NY, USA, 1997. [Google Scholar]

- Hill, N.J.; Gupta, D.; Brunner, P.; Gunduz, A.; Adamo, M.A.; Ritaccio, A.; Schalk, G. Recording Human Electrocorticographic (ECoG) Signals for Neuroscientific Research and Real-time Functional Cortical Mapping. J. Vis. Exp. 2012, e3993. [Google Scholar] [CrossRef] [PubMed]

- Wang, J.; Tang, L.; Bronlund, J.E. Surface EMG Signal Amplification and Filtering. Int. J. Comput. Appl. 2013, 82, 15–22. [Google Scholar] [CrossRef]

- Kumar, J.S.; Bhuvaneswari, P.T.V. Analysis of Electroencephalography (EEG) Signals and Its Categorization—A Study. Procedia Eng. 2012, 38, 2525–2536. [Google Scholar] [CrossRef]

- Hu, Y.; Yi, Z.; He, Z.; Li, B. Energy-efficient, area-efficient, high-accuracy and low-complexity switching scheme for SAR ADC. IEICE Electron. Expr. 2017, 14, 20170428. [Google Scholar] [CrossRef][Green Version]

- Hu, Y.; Liu, A.; Li, B.; Wu, Z. Closed-loop charge recycling switching scheme for SAR ADC. Electron. Lett. 2017, 53, 66–68. [Google Scholar] [CrossRef]

- Hu, Y.; Chen, L.; Chen, H.; Wen, Y.; Zhang, H.; Wu, Z.; Li, B. A 7.6-nW 1-kS/s 10-bit SAR ADC for Biomedical Applications. In Proceedings of the 2019 IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Bangkok, Thailand, 11–14 November 2019; pp. 129–132. [Google Scholar] [CrossRef]

- Harpe, P.; Cantatore, E.; van Roermund, A. A 10b/12b 40 kS/s SAR ADC With Data-Driven Noise Reduction Achieving up to 10.1b ENOB at 2.2 fJ/Conversion-Step. IEEE J. Solid-State Circuits 2013, 48, 3011–3018. [Google Scholar] [CrossRef]

- Zhang, D.; Alvandpour, A. A 12.5-ENOB 10-kS/s Redundant SAR ADC in 65-nm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 244–248. [Google Scholar] [CrossRef]

- Wenliang, G.; Guoxing, W.; Kuan-Ting, L.; Kea-Tiong, T. A 10-bit 1kS/s-30kS/s successive approximation register analog-to-digital converter for biological signal acquisition. In Proceedings of the 2013 6th International Conference on Biomedical Engineering and Informatics, Hangzhou, China, 16–18 December 2013; pp. 403–407. [Google Scholar] [CrossRef]

- Yen-Po, C.; Dongsuk, J.; Yoonmyung, L.; Yejoong, K.; Zhiyoong, F.; Inhee, L.; Langhals, N.B.; Kruger, G.; Oral, H.; Berenfeld, O.; et al. An Injectable 64 nW ECG Mixed-Signal SoC in 65 nm for Arrhythmia Monitoring. IEEE J. Solid-State Circuits 2015, 50, 375–390. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Hu, Y.; Tang, B.; Hu, L.; Liang, H.; Li, B.; Wu, Z.; Liu, X. A 7.6-nW 1-kS/s 10-Bit SAR ADC for Biomedical Applications. Micromachines 2022, 13, 2110. https://doi.org/10.3390/mi13122110

Hu Y, Tang B, Hu L, Liang H, Li B, Wu Z, Liu X. A 7.6-nW 1-kS/s 10-Bit SAR ADC for Biomedical Applications. Micromachines. 2022; 13(12):2110. https://doi.org/10.3390/mi13122110

Chicago/Turabian StyleHu, Yunfeng, Bin Tang, Lexing Hu, Haibo Liang, Bin Li, Zhaohui Wu, and Xiaojia Liu. 2022. "A 7.6-nW 1-kS/s 10-Bit SAR ADC for Biomedical Applications" Micromachines 13, no. 12: 2110. https://doi.org/10.3390/mi13122110

APA StyleHu, Y., Tang, B., Hu, L., Liang, H., Li, B., Wu, Z., & Liu, X. (2022). A 7.6-nW 1-kS/s 10-Bit SAR ADC for Biomedical Applications. Micromachines, 13(12), 2110. https://doi.org/10.3390/mi13122110