Effects of Annealing Temperature Combinations in InOx/AlOx Heterostructure for High-Performance and Stable Solution-Processed Junctionless Transistors

Abstract

1. Introduction

2. Materials and Methods

2.1. Preparation of Oxide Precursor Solutions

2.2. Fabrication of Devices

2.3. Analysis of Thin Films and Devices

3. Results and Discussion

3.1. Concept and Operation of JL TFTs

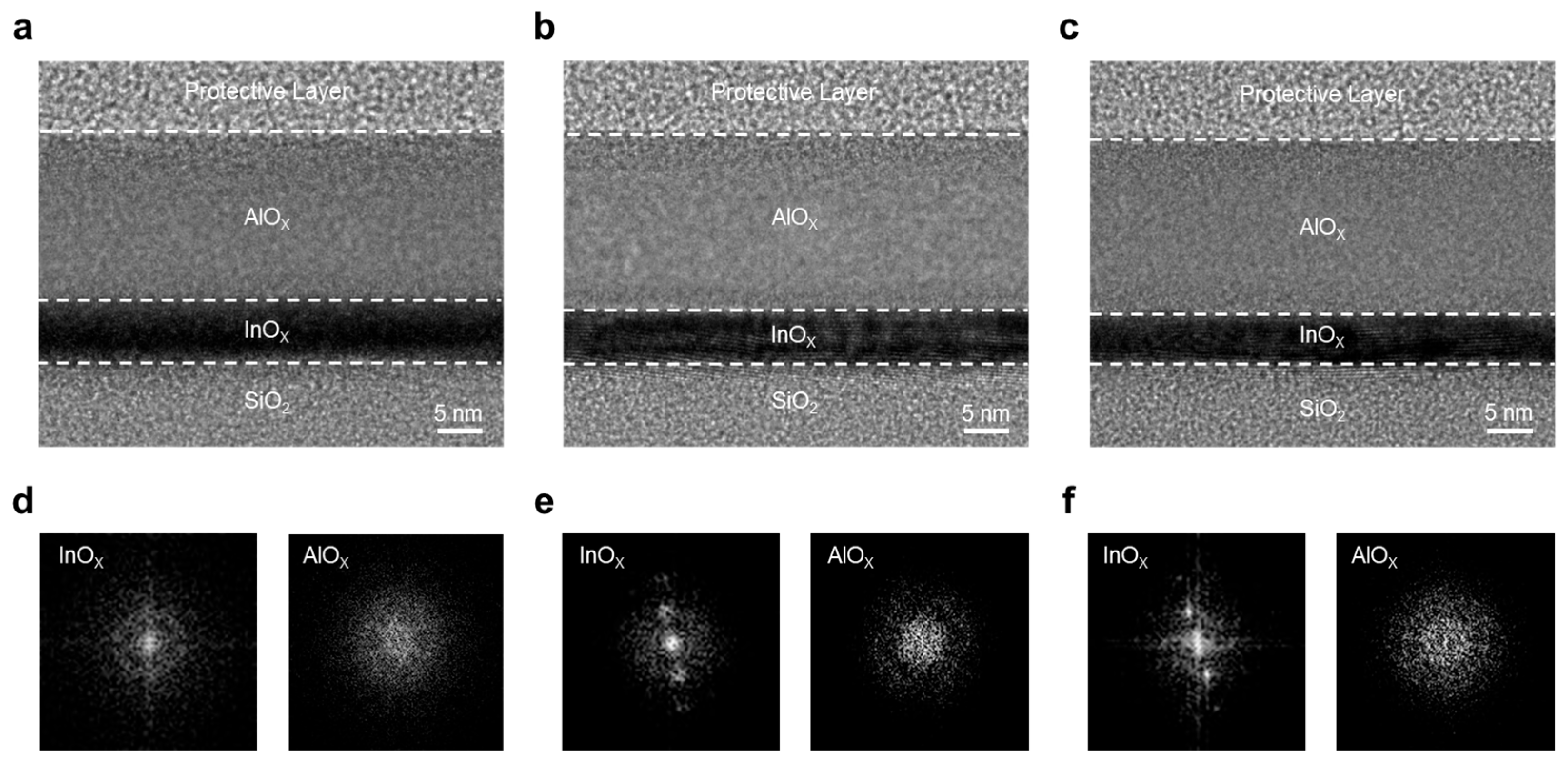

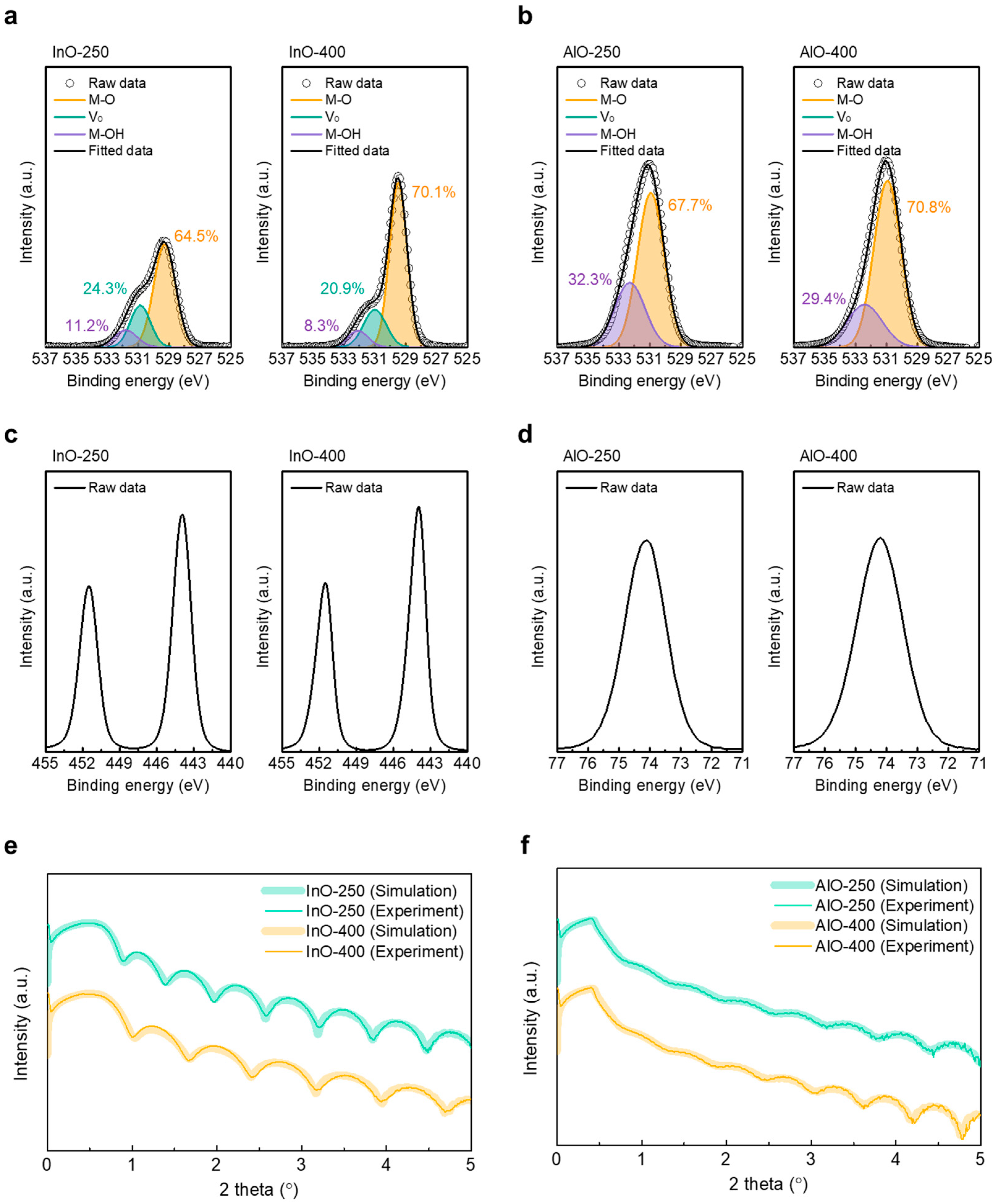

3.2. Effects of Annealing Temperature on the Structural and Chemical Characteristics of the InOx Semiconductor and AlOx CL

3.3. Electrical Characteristics of InOx/AlOx Heterostructure JL TFTs

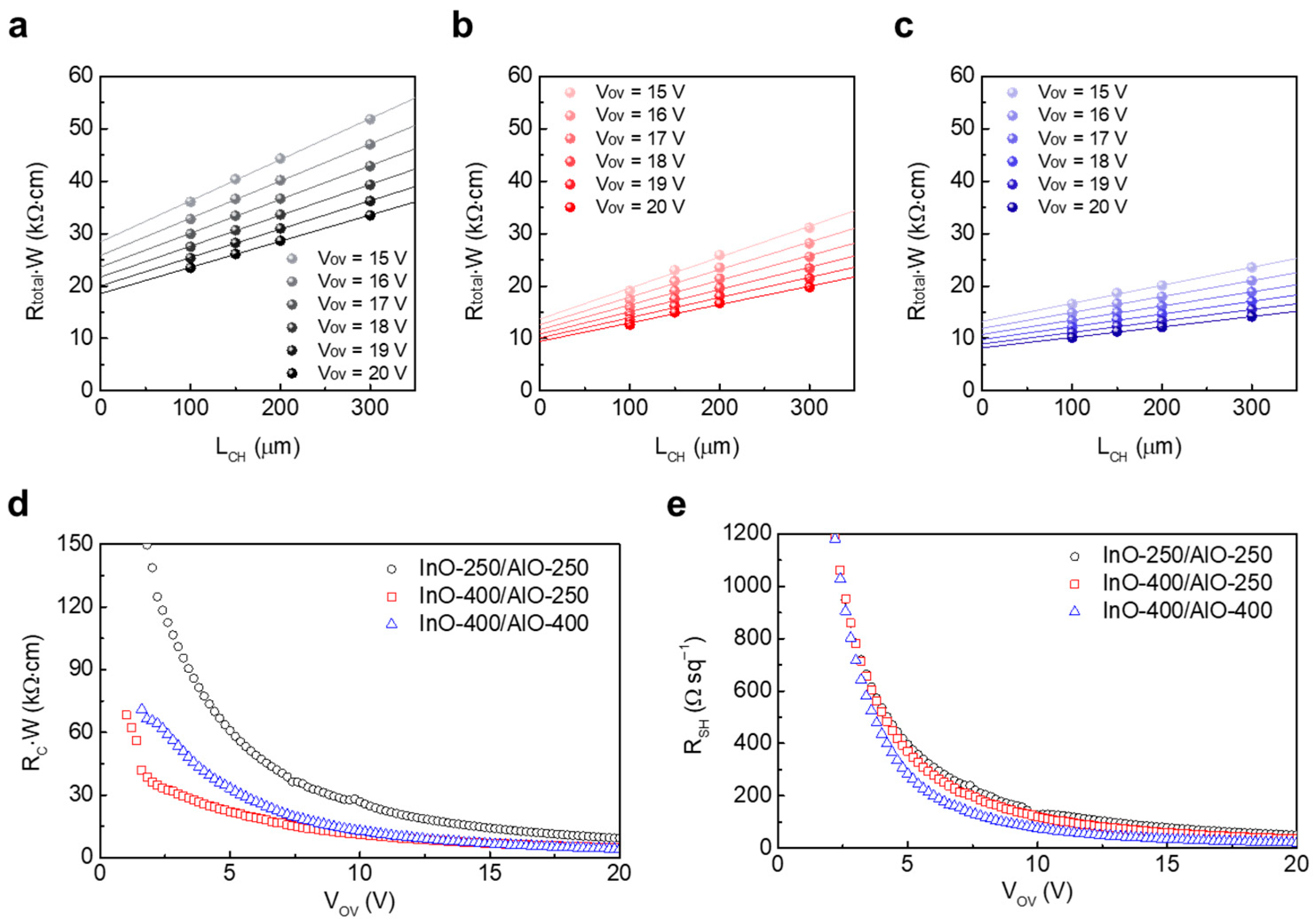

3.4. Contact and Channel Resistance of InOx/AlOx Heterostructure JL TFTs

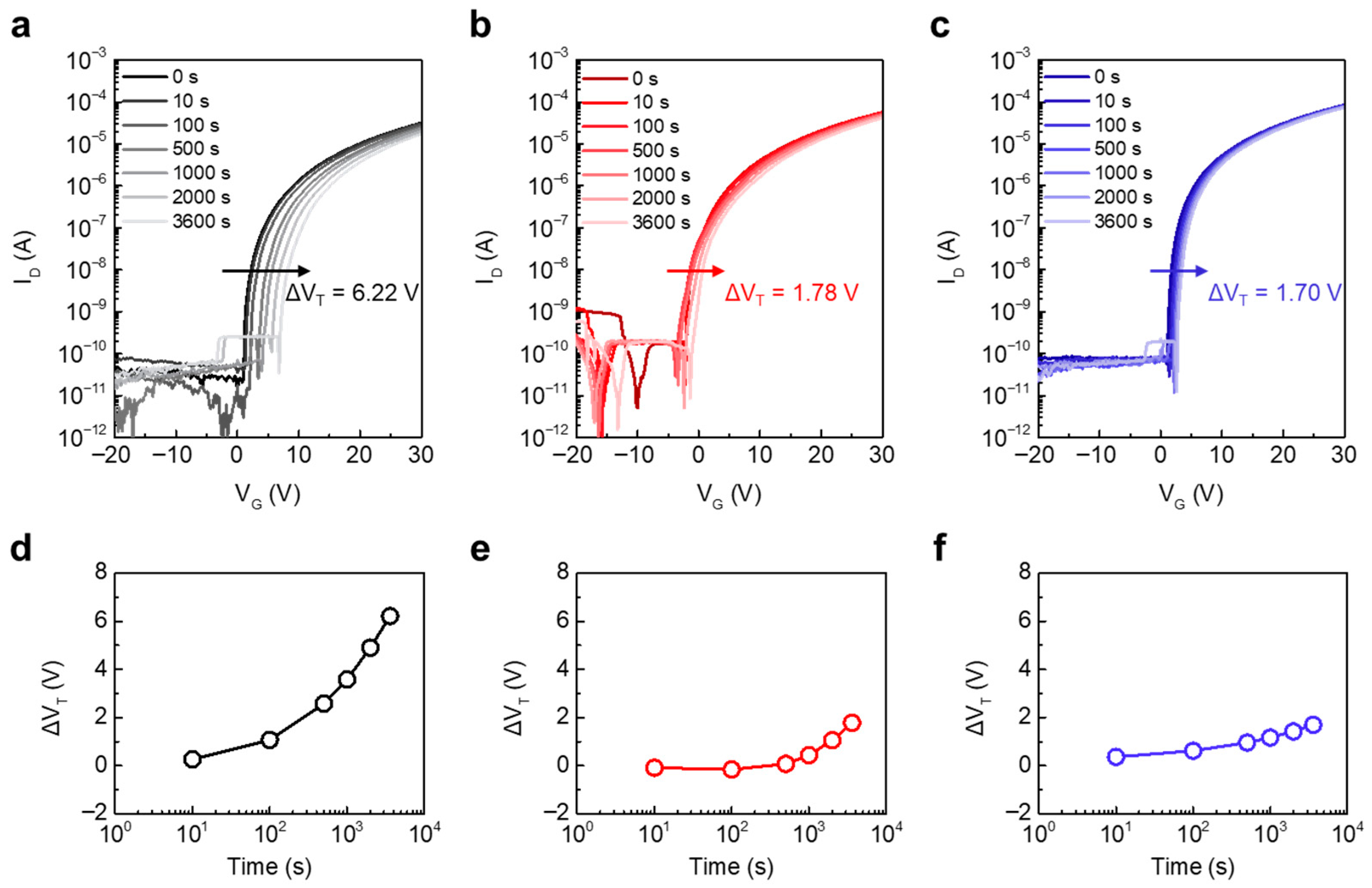

3.5. Positive Bias Stability of InOx/AlOx Heterostructure JL TFTs

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A review of Recent Advances. Adv. Mater. 2012, 24, 2945–2986. [Google Scholar] [CrossRef]

- Kamiya, T.; Hosono, H. Material characteristics and applications of transparent amorphous oxide semiconductors. NPG Asia Mater. 2010, 2, 15–22. [Google Scholar] [CrossRef]

- Ishibe, T.; Tomeda, A.; Komatsubara, Y.; Kitaura, R.; Uenuma, M.; Uraoka, Y.; Yamashita, Y.; Nakamura, Y. Carrier and phonon transport control by domain engineering for high-performance transparent thin film thermoelectric generator. Appl. Phys. Lett. 2021, 118, 151601. [Google Scholar] [CrossRef]

- Gong, L.; Wei, M.; Yu, R.; Ohta, H.; Katayama, T. Significant Suppression of Cracks in Freestanding Perovskite Oxide Flexible Sheets Using a Capping Oxide Layer. ACS Nano 2022, 16, 21013–21019. [Google Scholar] [CrossRef] [PubMed]

- Park, J.S.; Maeng, W.-J.; Kim, H.-S.; Park, J.-S. Review of recent developments in amorphous oxide semiconductor thin-film transistor devices. Thin Solid Films 2012, 520, 1679–1693. [Google Scholar] [CrossRef]

- Jang, Y.; Park, J.; Kang, J.; Lee, S.-Y. Amorphous InGaZnO (a-IGZO) Synaptic Transistor for Neuromorphic Computing. ACS Appl. Electron. Mater. 2022, 4, 1427–1448. [Google Scholar] [CrossRef]

- Choi, Y.; Park, W.-Y.; Kang, M.S.; Yi, G.-R.; Lee, J.-Y.; Kim, Y.-H.; Cho, J.H. Monolithic Metal Oxide Transistors. ACS Nano 2015, 9, 4288–4295. [Google Scholar] [CrossRef]

- Yu, X.; Marks, T.J.; Facchetti, A. Metal oxides for optoelectronic applications. Nat. Mater. 2016, 15, 383–396. [Google Scholar] [CrossRef]

- Kim, J.H.; Rim, Y.S.; Kim, H.J. Homojunction Solution-Processed Meta Oxide Thin-Film Transistors Using Passivation-Induced Channel Definition. ACS Appl. Mater. Interfaces 2014, 6, 4819–4822. [Google Scholar] [CrossRef]

- Hong, S.; Na, J.W.; Lee, I.S.; Kim, H.T.; Kang, B.H.; Chung, J.; Kim, H.J. Simultaneously Defined Semiconducting Channel Layer Using Electrohydrodynamic Jet Printing of a Passivation layer for Oxide Thin-Film Transistors. ACS Appl. Mater. Interfaces 2020, 12, 39705–39712. [Google Scholar] [CrossRef]

- Kim, H.J.; Park, K.; Kim, H.J. High-performance vacuum-processed metal oxide thin-film transistors: A review of recent developments. J. Soc. Inf. Disp. 2020, 28, 591–622. [Google Scholar] [CrossRef]

- Kumomi, H.; Nomura, K.; Kamiya, T.; Hosono, H. Amorphous oxide channel TFTs. Thin Solid Films 2008, 516, 1516–1522. [Google Scholar] [CrossRef]

- Tückmantel, C.; Kalita, U.; Haeger, T.; Theisen, M.; Pfeiffer, U.; Riedl, T. Amorphous indium-gallium-zinc-oxide TFTs patterned by self-aligned photolithography overcoming the GHz threshold. IEEE Electron Device Lett. 2020, 41, 1786–1789. [Google Scholar] [CrossRef]

- Saha, J.K.; Jang, J. Saturation Mobility of 100 cm2 V–1 s–1 in ZnO Thin-Film Transistors through Quantum Confinement by a Nanoscale In2O3 Interlayer Using Spray Pyrolysis. ACS Nano 2024, 18, 30484–30496. [Google Scholar] [CrossRef] [PubMed]

- Wen, P.; Peng, C.; Ding, X.; Chen, F.H.; Yan, G.; Xu, L.; Li, J.; Li, X.; Zhang, J. High mobility crystallized stacked-channel thin-film transistors induced by low-temperature thermal annealing. Appl. Phys. Lett. 2025, 126, 023506. [Google Scholar] [CrossRef]

- Ahn, B.D.; Jeon, H.-J.; Sheng, J.; Park, J.; Park, J.-S. A review on the recent developments of solution processes for oxide thin film transistors. Semicond. Sci. Technol. 2015, 30, 064001. [Google Scholar] [CrossRef]

- Ding, Y.; Fan, C.; Fu, C.; Meng, Y.; Liu, G.; Shan, F. High-performance indium oxide thin-film transistors with aluminum oxide passivation. IEEE Electron Device Lett. 2019, 40, 1949–1952. [Google Scholar] [CrossRef]

- Lee, K.; Kim, Y.-H.; Yoon, S.-M.; Kim, J.; Oh, M.S. Effects of channel thickness on oxide thin film transistor with double-stacked channel layer. J. Korean Phys. Soc. 2017, 71, 561–564. [Google Scholar] [CrossRef]

- Conley, J.F. Instabilities in amorphous oxide semiconductor thin-film transistors. IEEE Trans. Device Mater. Reliab. 2010, 10, 460–475. [Google Scholar] [CrossRef]

- Zheng, S.; Wang, C.; Lv, S.; Dong, L.; Li, Z.; Xin, Q.; Song, A.; Zhang, J.; Li, Y. Enhancement in Performance and Reliability of Fully Transparent a-IGZO Top-Gate Thin-Film Transistors by a Two-Step Annealing Treatment. Nanomaterials 2025, 15, 460. [Google Scholar] [CrossRef]

- Kim, D.-K.; Seo, K.-H.; Kwon, D.-H.; Jeon, S.-H.; Hwang, Y.-J.; Wang, Z.; Park, J.; Lee, S.-H.; Jang, J.; Kang, I.M.; et al. Viable strategy to minimize trap states of patterned oxide thin films for both exceptional electrical performance and uniformity in sol–gel processed transistors. Chem. Eng. J. 2022, 441, 135833. [Google Scholar] [CrossRef]

- Acharya, V.; Agarwal, K.; Mondal, S. Electronic materials for solution-processed TFTs. Mater. Res. Express 2023, 10, 082002. [Google Scholar] [CrossRef]

- Nguyen, C.P.C.; Trinh, T.T.; Raja, J.; Le, A.H.T.; Lee, Y.-J.; Dao, V.A.; Yi, J. Source/drain metallization effects on the specific contact resistance of indium thin zinc oxide thin film transistors. Mater. Sci. Semicond. Process 2015, 39, 649–653. [Google Scholar] [CrossRef]

- Lee, J.; Eun, J.-S.; Na, J.-H.; Park, W.; Park, J.-H.; Feng, J.; Jang, J.; Kang, I.M.; Park, J.; Zhang, X.; et al. Verifying the physical role of upper-active layer on charge transport together with bias stability in bilayer-channel oxide thin-film transistors. Surf. Interfaces 2024, 51, 104624. [Google Scholar] [CrossRef]

- Kim, T.H.; Park, W.; Oh, S.; Kim, S.-Y.; Yamada, N.; Kobayashi, H.; Jang, H.Y.; Nam, J.H.; Habazaki, H.; Lee, B.H.; et al. Unveiling the Role of Al2O3 Interlayer in Indium-Gallium-Zinc-Oxide Transistors. Phys. Status Solidi A 2021, 218, 2000621. [Google Scholar] [CrossRef]

- Hinuma, Y.; Gake, T.; Oba, F. Band alignment at surfaces and heterointerfaces of Al2O3, Ga2O3, In2O3, and related group-III oxide polymorphs: A first-principles study. Phys. Rev. Mater. 2019, 3, 084605. [Google Scholar] [CrossRef]

- Gupta, B.; Hossain, M.A.; Sharma, A.; Zhang, D.; Tan, H.H.; Jagadish, C.; Cathpole, K.; Hoex, B.; Karuturi, S. Recent Advances in Materials Design Using Atomic Layer Deposition for Energy Applications. Adv. Funct. Mater. 2022, 32, 2109105. [Google Scholar] [CrossRef]

- Yeh, C.-C.; Zan, H.-W.; Soppera, O. Solution-Based Micro-and Nanoscale Metal Oxide Structures Formed by Direct Patterning for Electro-Optical Applications. Adv. Mater. 2018, 30, 1800923. [Google Scholar] [CrossRef]

- Meng, Y.; Liu, G.; Liu, A.; Song, H.; Hou, Y.; Shin, B.; Shan, F. Low-temperature fabrication of high performance indium oxide thin film transistors. RSC Adv. 2015, 5, 37807–37813. [Google Scholar] [CrossRef]

- Ruzgar, S.; Caglar, Y.; Caglar, M. The influence of low indium composition ratio on sol-gel solution-deposited amorphous zinc oxide thin film transistors. J. Mater. Sci.-Mater. Electron. 2020, 31, 11720–11728. [Google Scholar] [CrossRef]

- Hsu, C.-C.; Chou, C.-H.; Chen, Y.-T.; Jhang, W.-C. A Study of Solution-Processed Zinc-Tin-oxide Semiconductors for Thin-Film Transistors. IEEE Trans. Electron Devices 2019, 66, 26312636. [Google Scholar] [CrossRef]

| Samples | Density (g/cm−3) | Thickness (nm) | Roughness (nm) |

|---|---|---|---|

| InO-250 | 5.66693 | 14.1193 | 0.7452 |

| InO-400 | 6.18673 | 11.4268 | 0.7080 |

| AlO-250 | 2.71072 | 13.3954 | 0.7961 |

| AlO-400 | 2.65632 | 13.9451 | 0.6466 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Park, J.; Gil, D.; Park, S.J.; Ahn, J.W.; Choi, M.; Lang, P.; Jang, J.; Kim, D.-K.; Bae, J.-H. Effects of Annealing Temperature Combinations in InOx/AlOx Heterostructure for High-Performance and Stable Solution-Processed Junctionless Transistors. Materials 2025, 18, 5142. https://doi.org/10.3390/ma18225142

Park J, Gil D, Park SJ, Ahn JW, Choi M, Lang P, Jang J, Kim D-K, Bae J-H. Effects of Annealing Temperature Combinations in InOx/AlOx Heterostructure for High-Performance and Stable Solution-Processed Junctionless Transistors. Materials. 2025; 18(22):5142. https://doi.org/10.3390/ma18225142

Chicago/Turabian StylePark, Jinhong, Dohyeon Gil, Se Jin Park, Jae Wook Ahn, Minsu Choi, Philippe Lang, Jaewon Jang, Do-Kyung Kim, and Jin-Hyuk Bae. 2025. "Effects of Annealing Temperature Combinations in InOx/AlOx Heterostructure for High-Performance and Stable Solution-Processed Junctionless Transistors" Materials 18, no. 22: 5142. https://doi.org/10.3390/ma18225142

APA StylePark, J., Gil, D., Park, S. J., Ahn, J. W., Choi, M., Lang, P., Jang, J., Kim, D.-K., & Bae, J.-H. (2025). Effects of Annealing Temperature Combinations in InOx/AlOx Heterostructure for High-Performance and Stable Solution-Processed Junctionless Transistors. Materials, 18(22), 5142. https://doi.org/10.3390/ma18225142