How to Achieve Efficiencies beyond 22.1% for CdTe-Based Thin-Film Solar Cells

Abstract

1. Introduction

2. Experimental Evidence

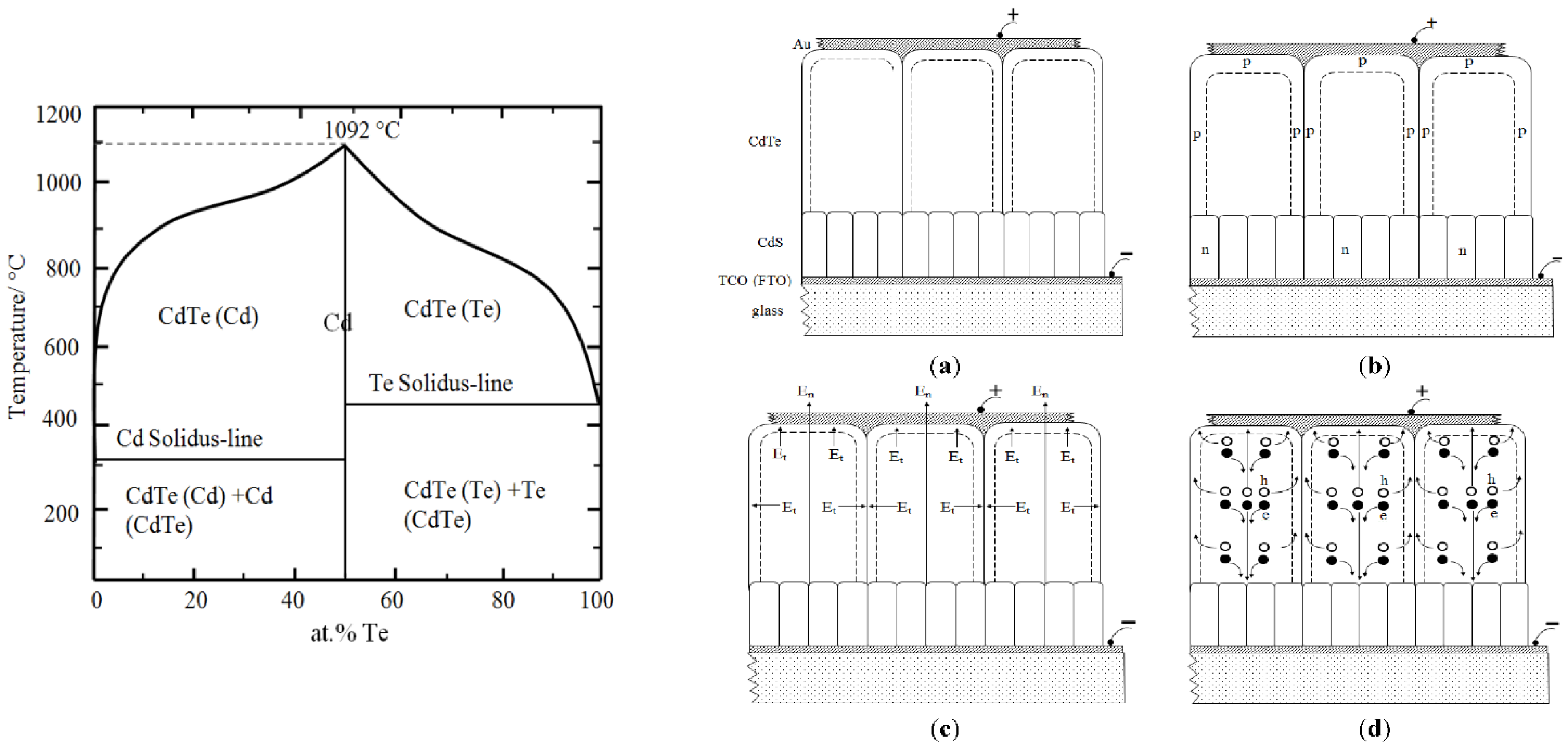

2.1. Intrinsic Doping of CdTe

- Summary of Section 2.1

- (i).

- Composition of CdTe is highly sensitive and depends on the growth conditions used.

- (ii).

- Intrinsic doping by variation in composition is possible for CdTe layers. Te-rich CdTe produces p-type material, and Cd-rich CdTe produces n-type material.

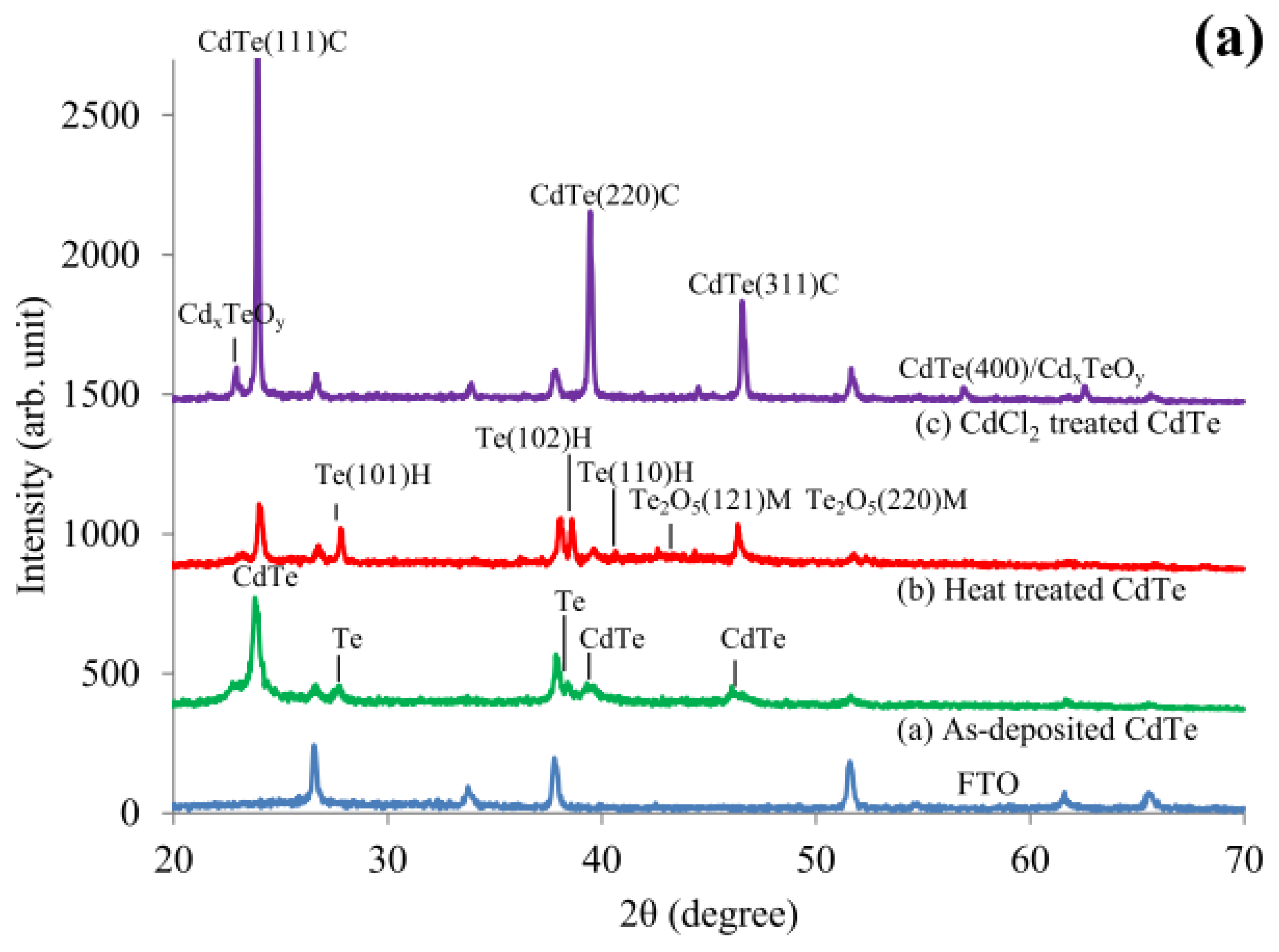

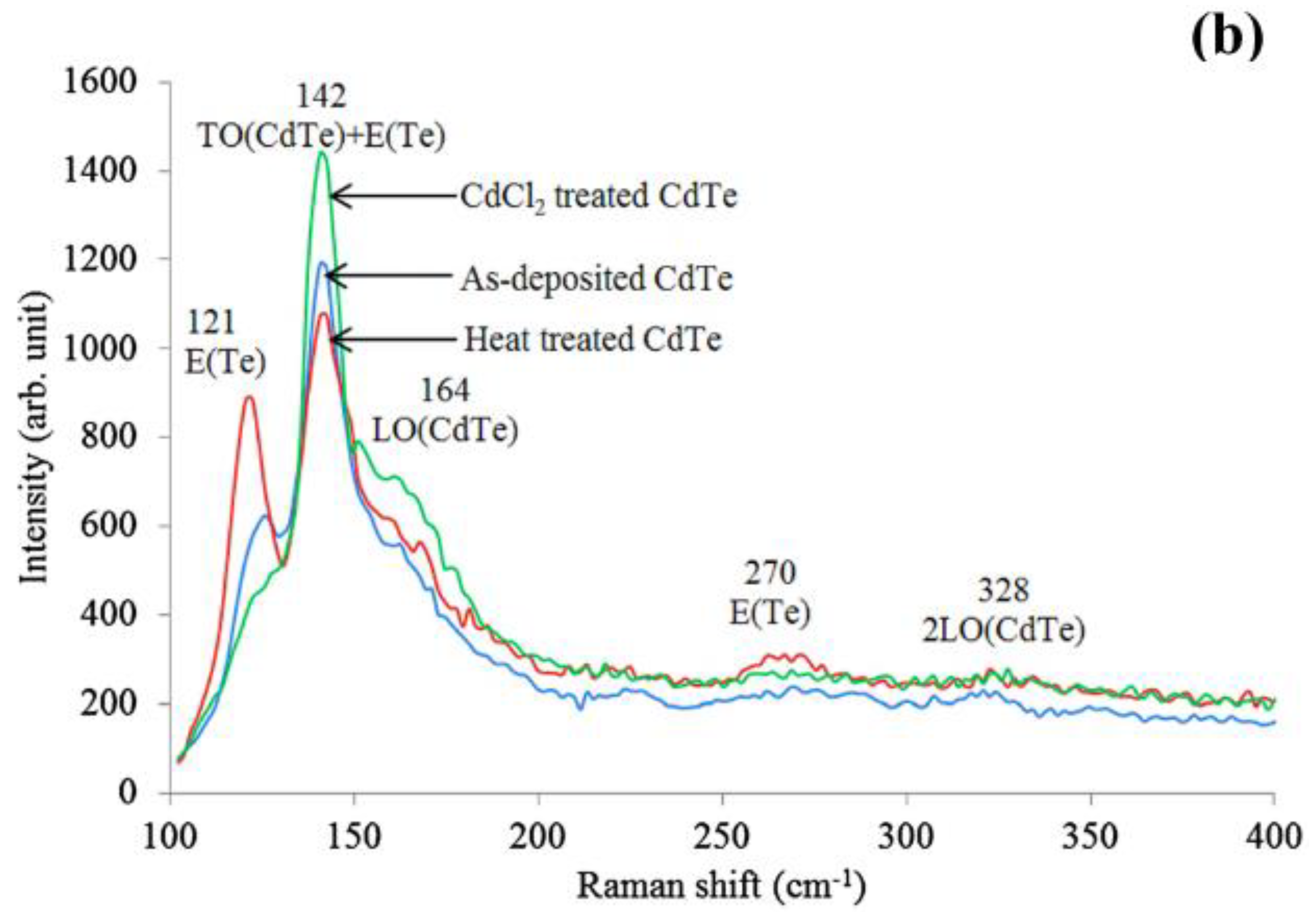

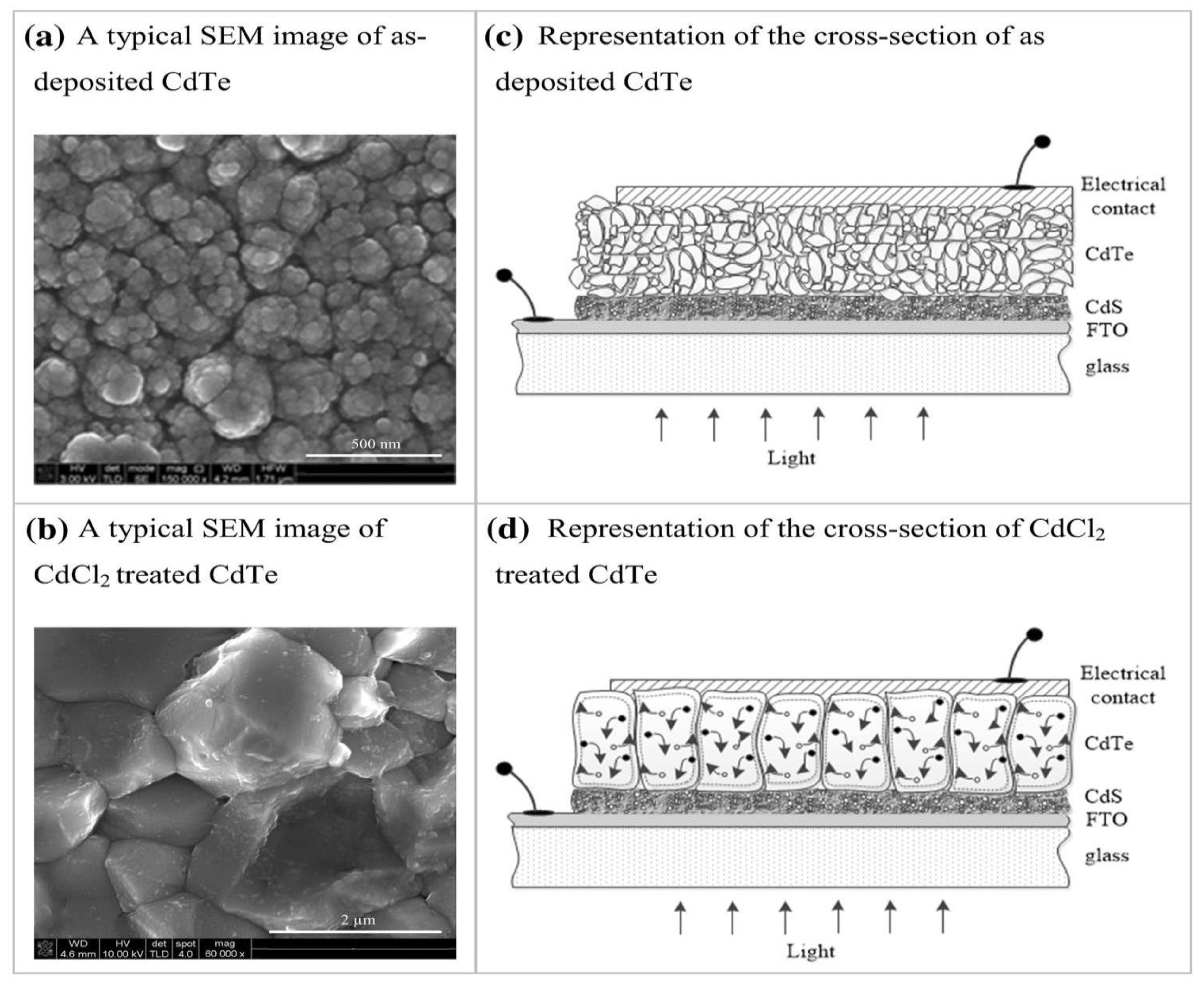

2.2. Material Improvement by CdCl2 Treatment

- Summary of Section 2.2

- (i).

- removes any precipitated and excess Te from the CdTe layers, improving stoichiometry, and can even shift the composition towards Cd-rich CdTe layers;

- (ii).

- improves crystal growth, and forms large columnar type crystals extending from front to rear of the device structure;

- (iii).

- drastically reduces mid-bandgap defects in CdTe, reducing charge carrier recombination (see PL results in Section 2.3);

- (iv).

- activates grain boundaries, minimises charge-carrier recombination and contributes positively towards PV performance (see Section 2.7).

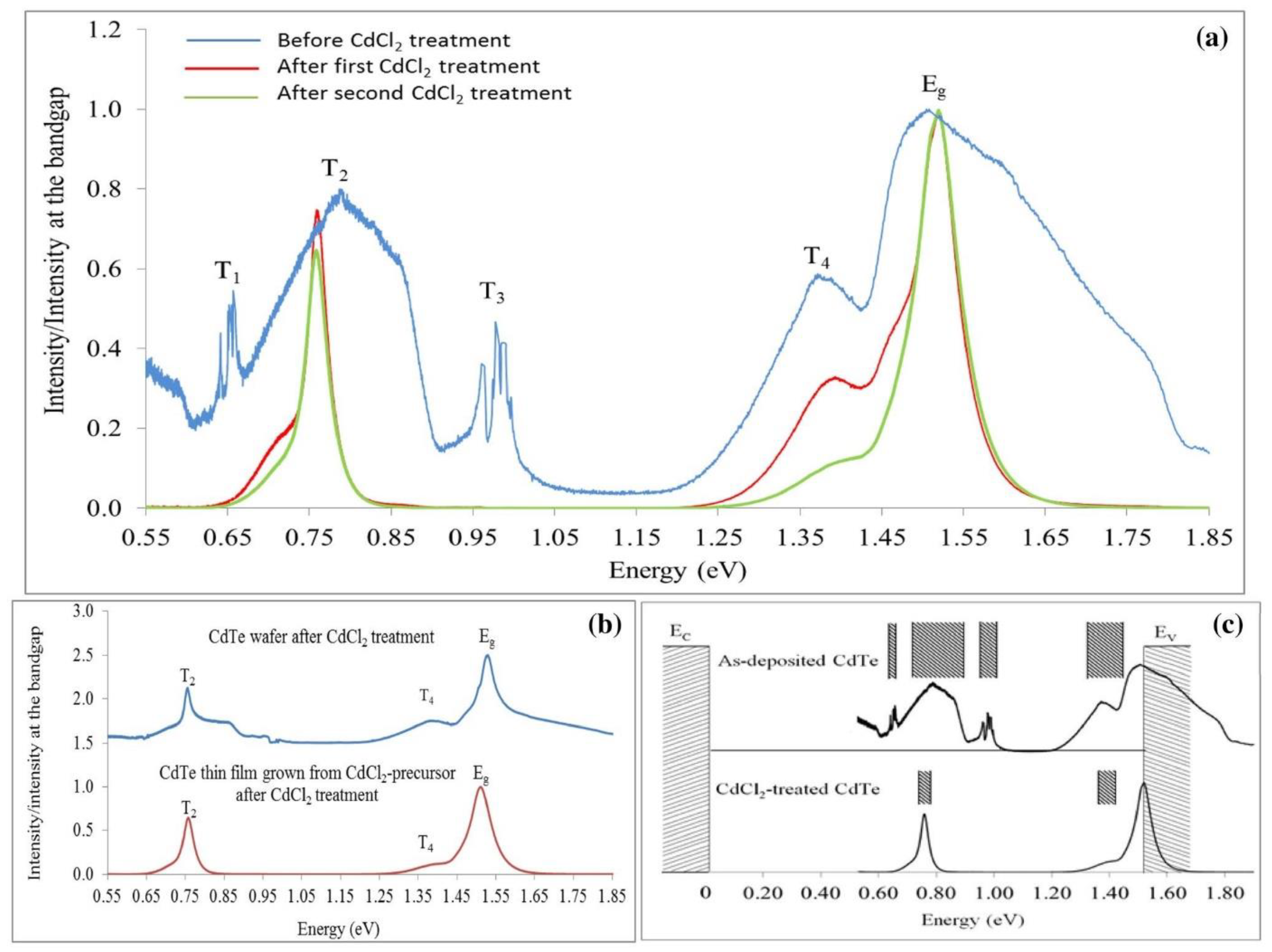

2.3. Low Concentration of Mid-Gap Defects in Cd-Rich CdTe when Compared to Te-Rich CdTe

2.3.1. PL from Single Crystal Surfaces

2.3.2. PL from Electroplated CdTe Thin Films

- Summary of Section 2.3

- (i).

- Te-rich CdTe surfaces and thin films are full of mid-gap killer centres. The Fermi level is pinned at ~0.73 eV when devices are fabricated.

- (ii).

- Cd-rich CdTe surfaces have reduced mid-gap defects and are more highly suited for fabricating electronic devices than Te-rich CdTe surfaces.

- (iii).

- Cd-rich CdTe surfaces and thin films minimise mid-gap killer centres and enhance defects closer to the valence band to produce Fermi level pinning ~0.96 eV. These materials therefore minimise charge carrier recombination process in devices made on Cd-rich materials and surfaces.

- (iv).

- CdCl2 treatment removes mid-gap defects and also minimises other defects within the energy band gap.

2.4. Fermi Level Pinning at n-CdTe/Metal Interface

- Summary of Section 2.4

- (i).

- To form good rectifying contacts with large Schottky barriers at n-CdTe/metal interface, a Cd-rich CdTe surface should be used.

- (ii).

- To help and support the Fermi level pinning closer to the valence band, a trace of p-dopant, such as Cu or Sb in the metal contact can be used. Large amounts of Cu, however, will diffuse into the n-CdTe layer and increase the series resistance via self-compensation, degrading the device.

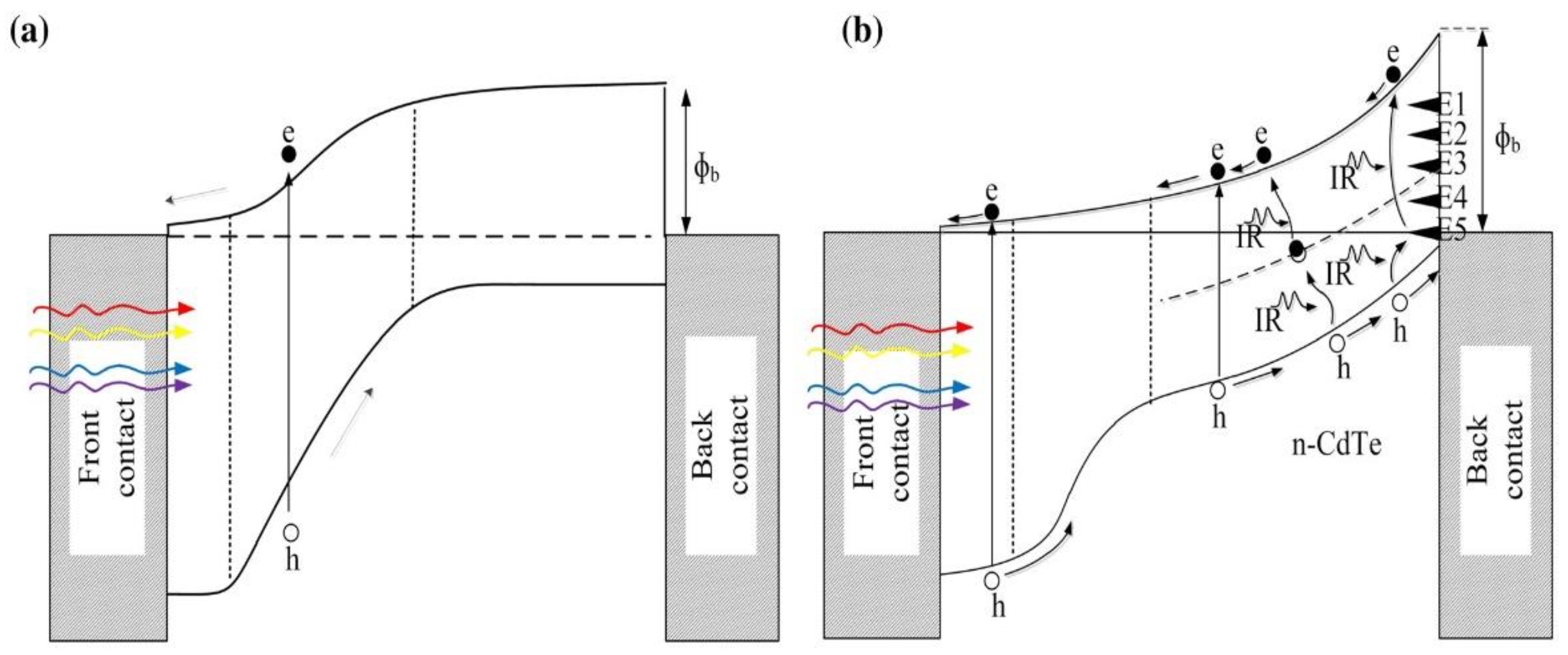

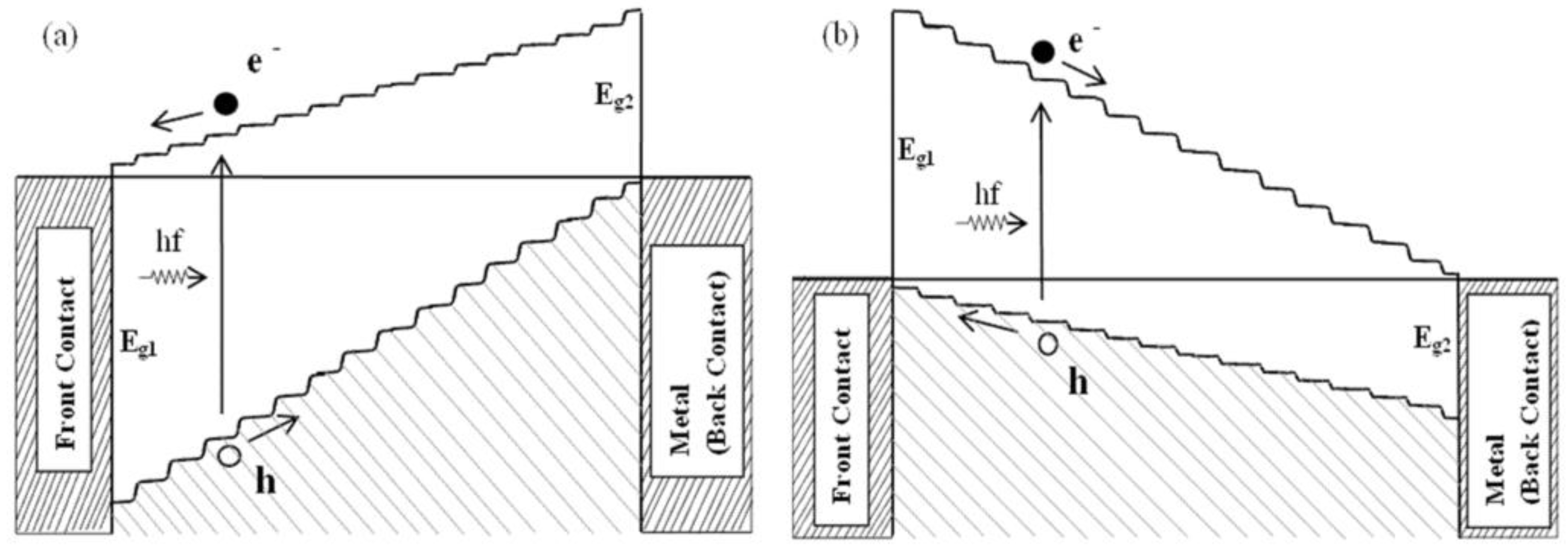

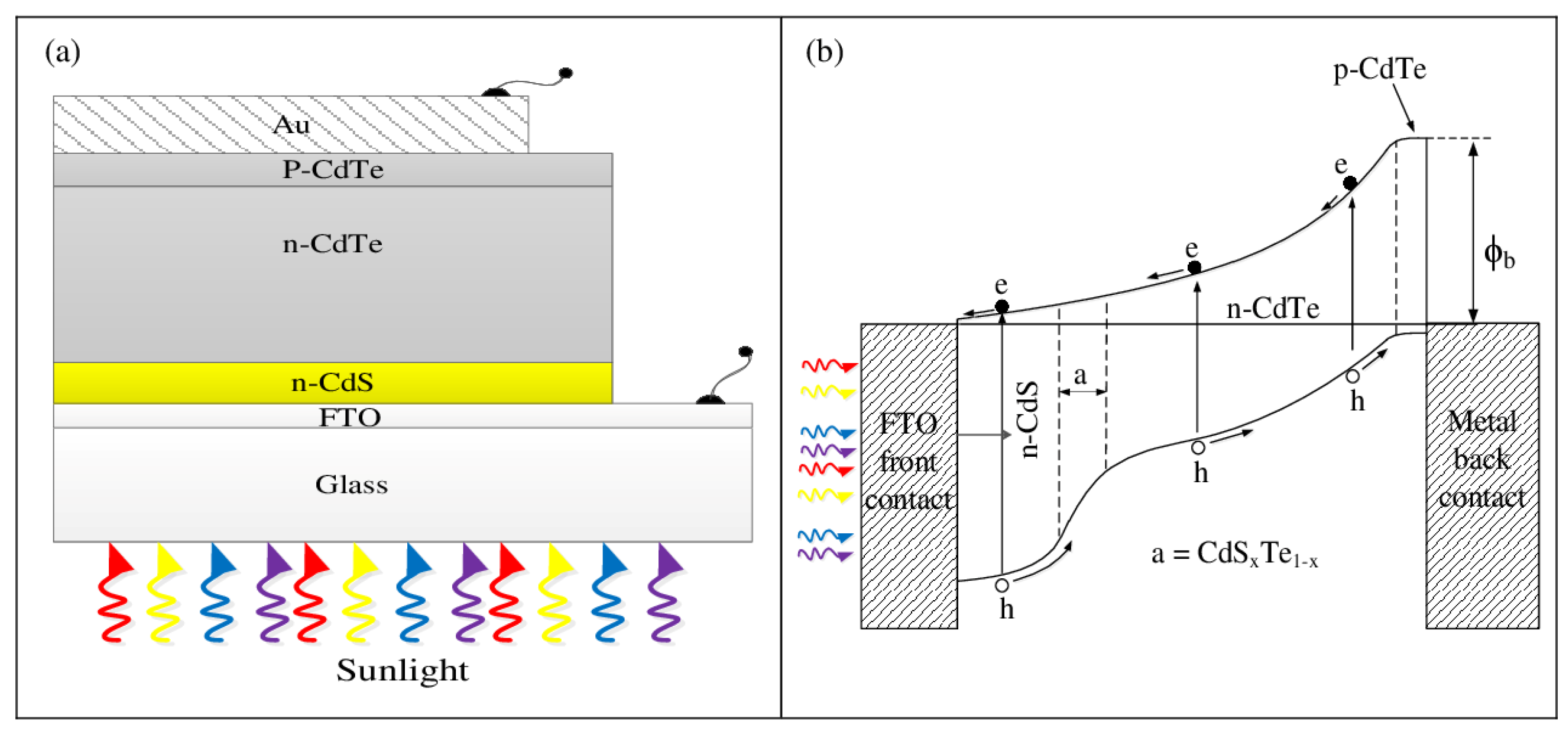

2.5. Two Possible Device Configurations for CdS/CdTe Structure

- Summary of Section 2.5

- (i).

- When the CdTe is grown as a p-type (Te-rich) material, the device is a simple n-p junction. The back electrical contact should be a low-resistance ohmic contact.

- (ii).

- When the CdTe is grown as an n-type (Cd-rich) material, the device is a combination of n-n hetero-junction combined with a large Schottky barrier at the back. These two rectifying interfaces support each other, and therefore should perform better than the single n-p junction.

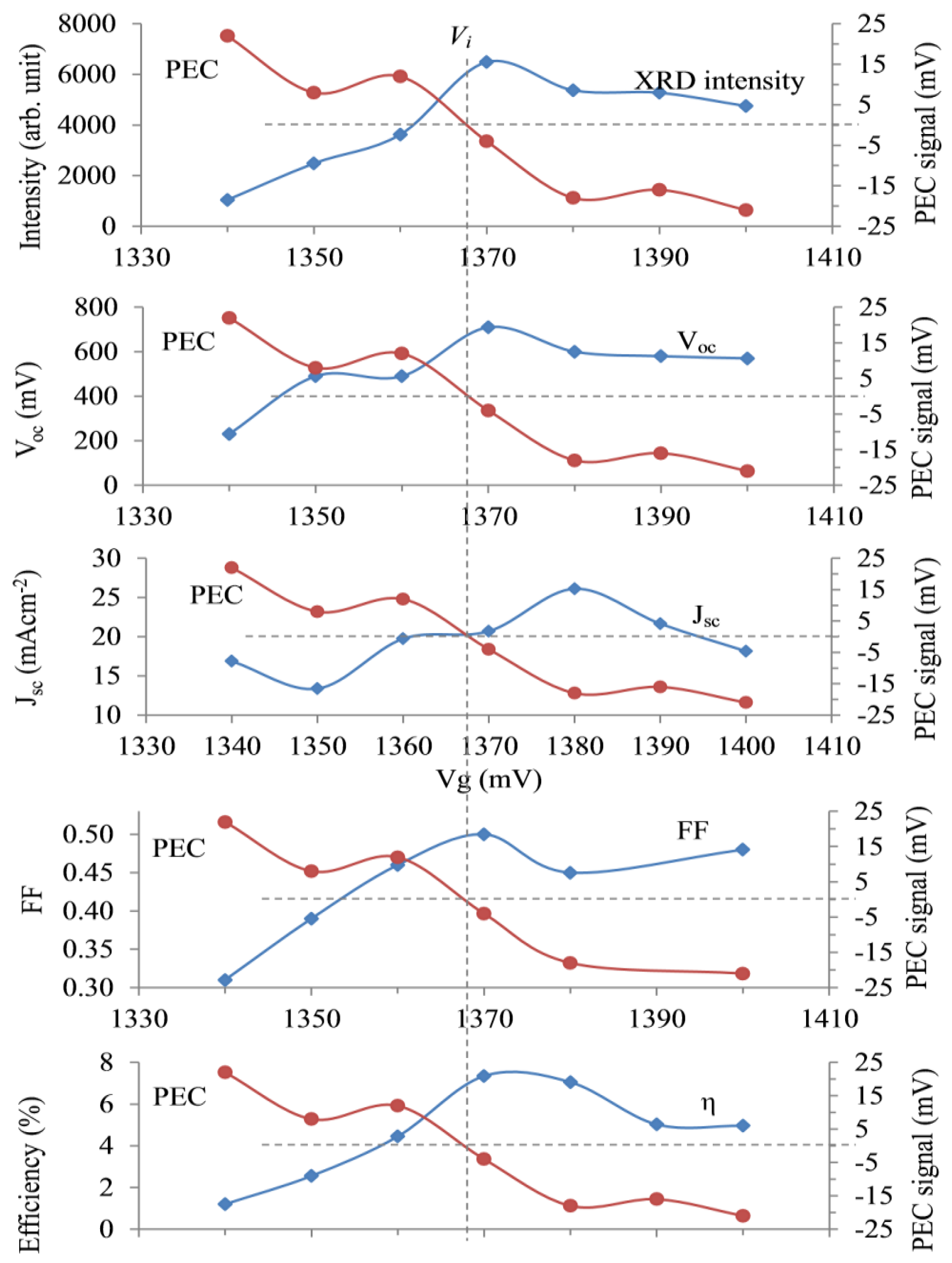

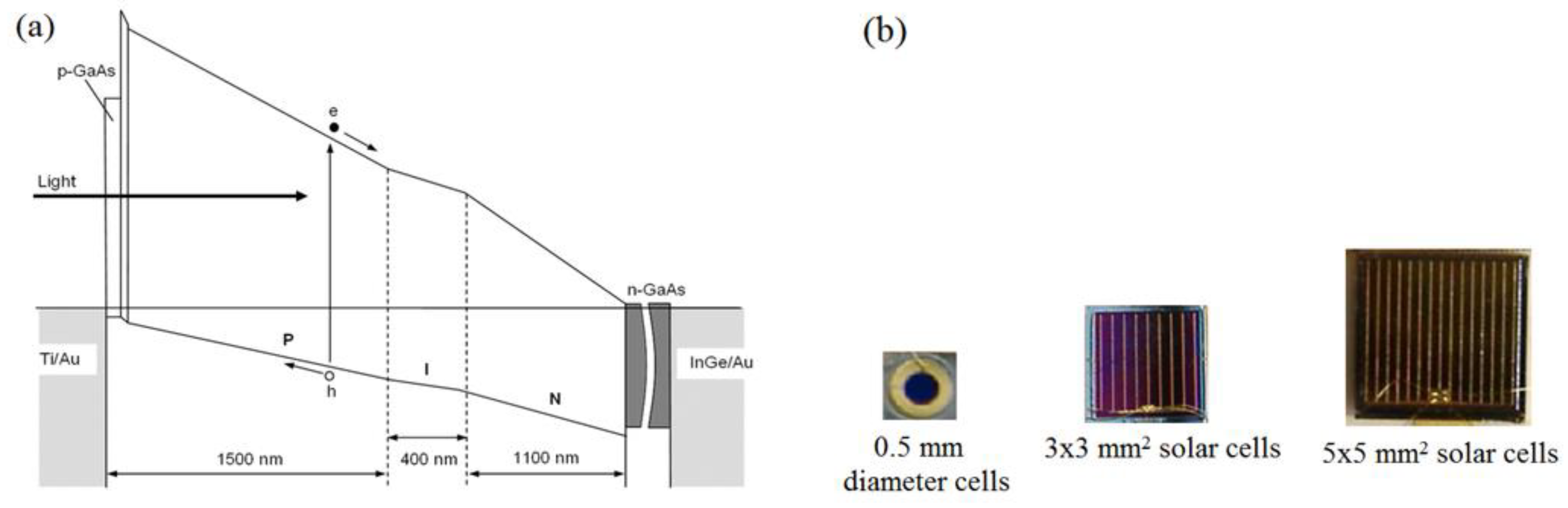

2.6. Achieving Better Performance from n-CdS/n-CdTe Structures

- Summary of Section 2.6

- (i).

- All four solar cell parameters, Voc, Jsc, FF and efficiency produced by glass/FTO/n-CdS/n-CdTe/Au structures were better than those produced by glass/FTO/n-CdS/p-CdTe/Au structures.

- (ii).

- Therefore, in order to develop high efficiency solar cells, Cd-rich n-CdTe should be used rather than Te-rich p-CdTe material.

2.7. Activation of Grain Boundaries by CdCl2 Treatment to Positively Contribute to the PV Effect

- Summary of Section 2.7

- (i).

- Columnar type or rod-type materials in thin-film solar cells are more suitable for the development of high-efficiency solar cells.

- (ii).

- CdCl2 treatment activate grain boundaries, minimise charge-carrier recombination and contribute positively to improving PV performance.

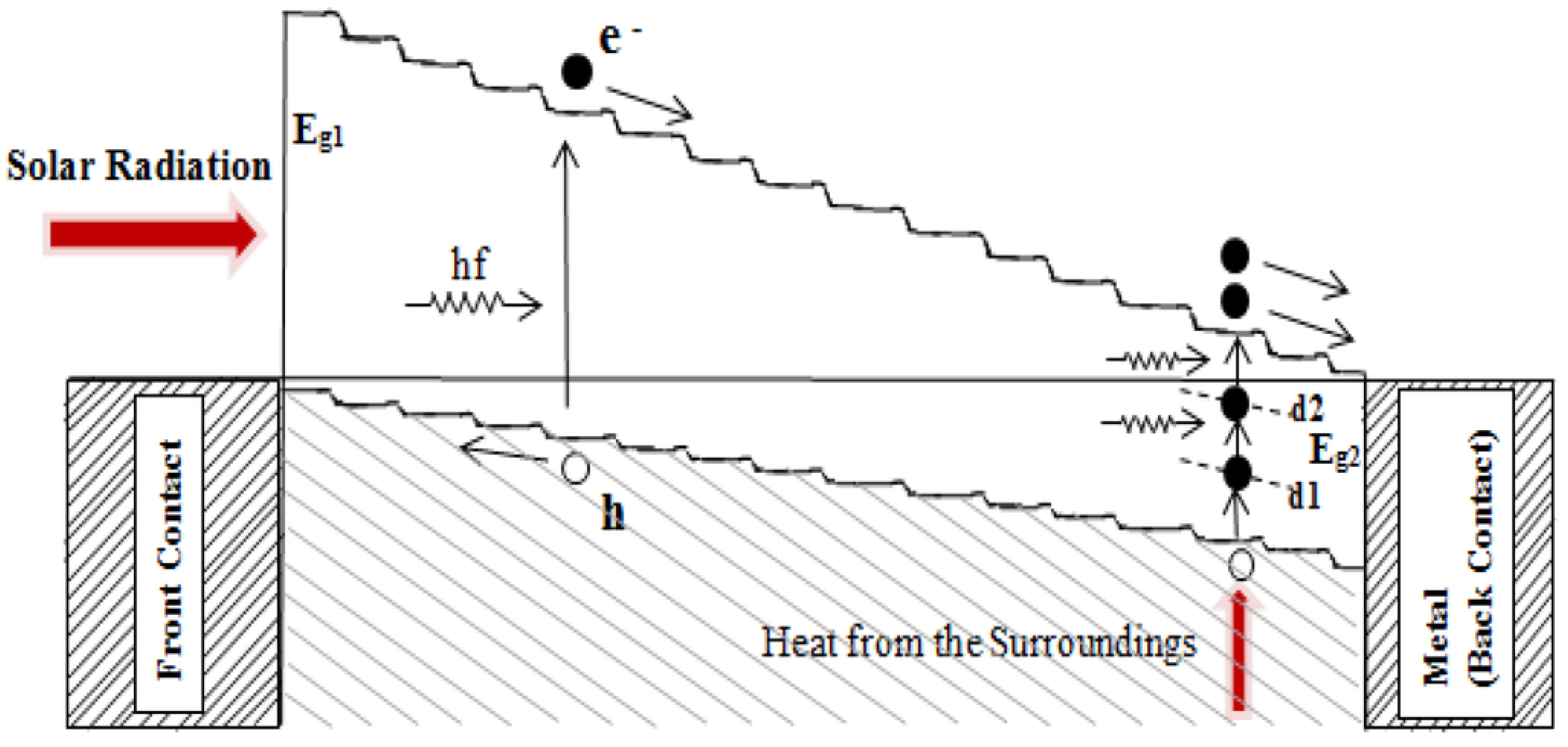

2.8. Graded Bandgap Multilayer Devices for Effective Harvesting of All Photons

- Summary of Section 2.8

- (i).

- Graded band gap devices can be produced on both n-type and p-type window materials, incorporating contributions from impact ionisation and the impurity PV effect.

- (ii).

- These devices can absorb more photons in UV, visible and IR regions of the sun’s spectrum and make use of IR radiation from the surroundings.

- (iii).

- Since the concept is experimentally proven with impressive cell parameters, future efforts should be focused on the development of next-generation high-efficiency graded band gap solar cells based on p-type window layer, using low-cost, scalable and manufacturable techniques.

3. The Ways Forward

3.1. Modify CSS Method for Producing n-CdTe Material

3.2. Improve Material Layers Further and Activate Grain Boundaries to Positively Contribute to PV Effect

3.3. Improve the Device by Adding Se to the Front of the Device

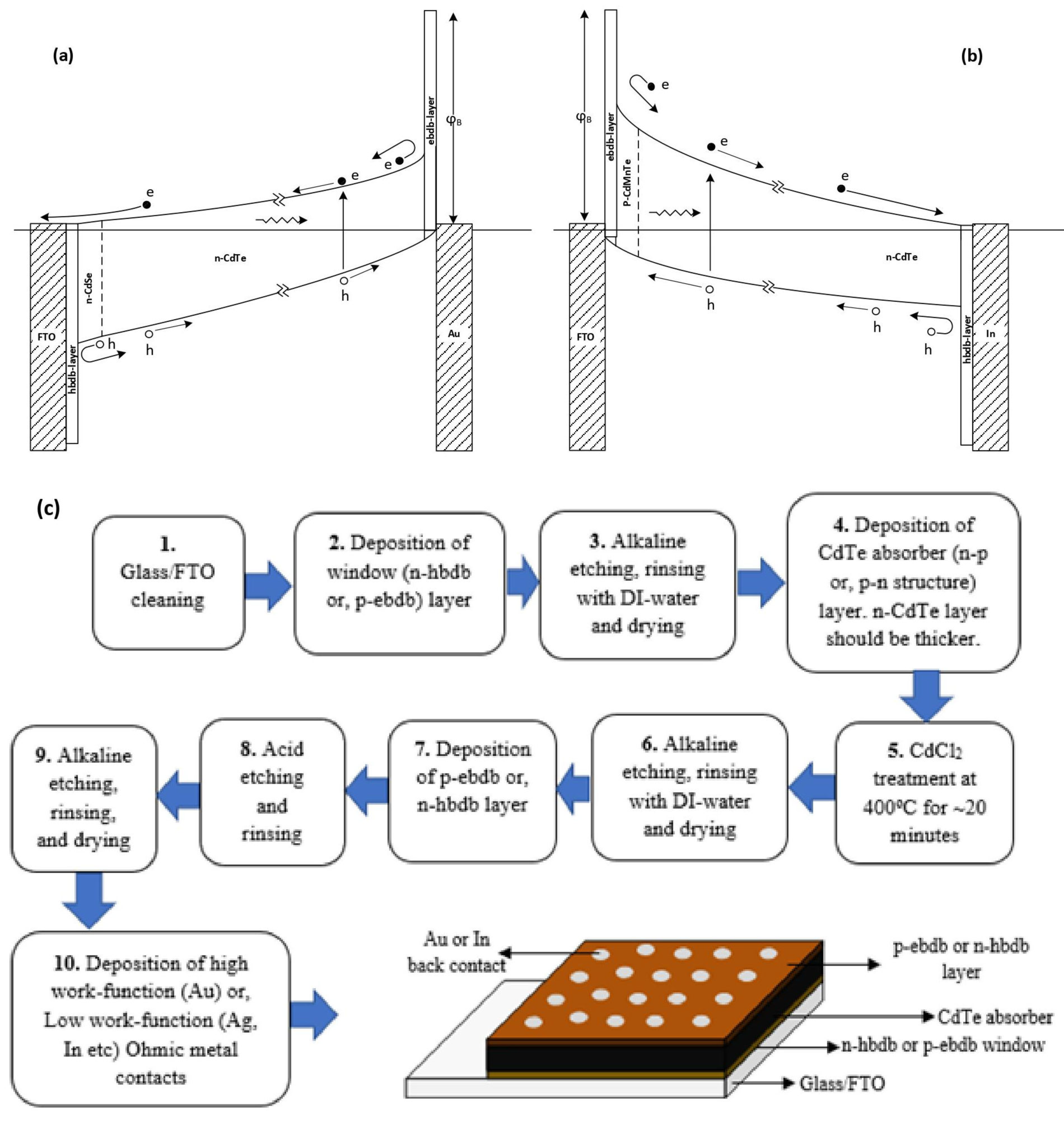

3.4. Improve Device by Adding ebdb and hbdb Layers to the Solar Cell Structure

- Summary of Section 3

- (i).

- Because of the higher vapour pressure of Te, CSS-CdTe is intrinsically Te-rich, is p-type in electrical conduction and produces comparatively lower efficiencies. To produce Cd-rich, n-CdTe and hence high efficiencies, the CSS method should be modified to introduce Cd vapour transport into the growth chamber.

- (ii).

- Grain boundaries are activated by CdCl2 treatment to positively contribute to the PV action.

- (iii).

- The band gap at the front of the solar cell is graded by the addition of elements such as Se to improve PV activity of the device.

- (iv).

- Suitable ebdb and hbdb layers are added to guide the direction of charge carrier flow in PV solar cells.

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Cunningham, D.; Rubcich, M.; Skinner, D. Cadmium telluride PV module manufacturing at BP Solar. Prog. Photovolt. Res. Appl. 2002, 10, 159–168. [Google Scholar] [CrossRef]

- Ferekides, C.S.; Marinskiy, D.; Viswanathan, V.; Tetali, B.; Palekis, V.; Selvaraj, P.; Morel, D.L. High efficiency CSS CdTe solar cells. Thin Solid Film. 2000, 361–362, 520–526. [Google Scholar] [CrossRef]

- Wu, X.; Keane, J.C.; Dhere, R.G.; DeHart, C.; Albin, D.S.; Duda, A.; Gessert, T.A.; Ashar, S.; Levi, D.H.; Sheldon, P. 16.5%-efficient CdS/CdTe polycrystalline thin film solar cells. In Proceedings of the 17th European Photovoltaic Solar Energy Conference, Munich, Germany, 22–26 October 2001; pp. 995–1000. [Google Scholar]

- Razykov, T.M.; Ferekides, C.S.; Morel, D.; Stefanakos, E.; Ullal, H.S.; Upadhyaya, H.M. Solar photovoltaic electricity: Current status and future prospects. Sol. Energy 2011, 85, 1580–1608. [Google Scholar] [CrossRef]

- First Solar CdTe Cell Hits 22.1% Efficiency. Available online: https://optics.org/news/7/2/29 (accessed on 15 October 2022).

- Dharmadasa, I.M. Advances in Thin Film Solar Cells, 2nd ed.; Pan Stanford Publishing Ltd.: Singapore, 2018. [Google Scholar]

- Ojo, A.A.; Cranton, W.M.; Dharmadasa, I.M. Next Generation Multilayer Graded Bandgap Solar Cells; Springer: Berlin/Heidelberg, Germany, 2018; ISBN 978-3-319-96666-3. [Google Scholar]

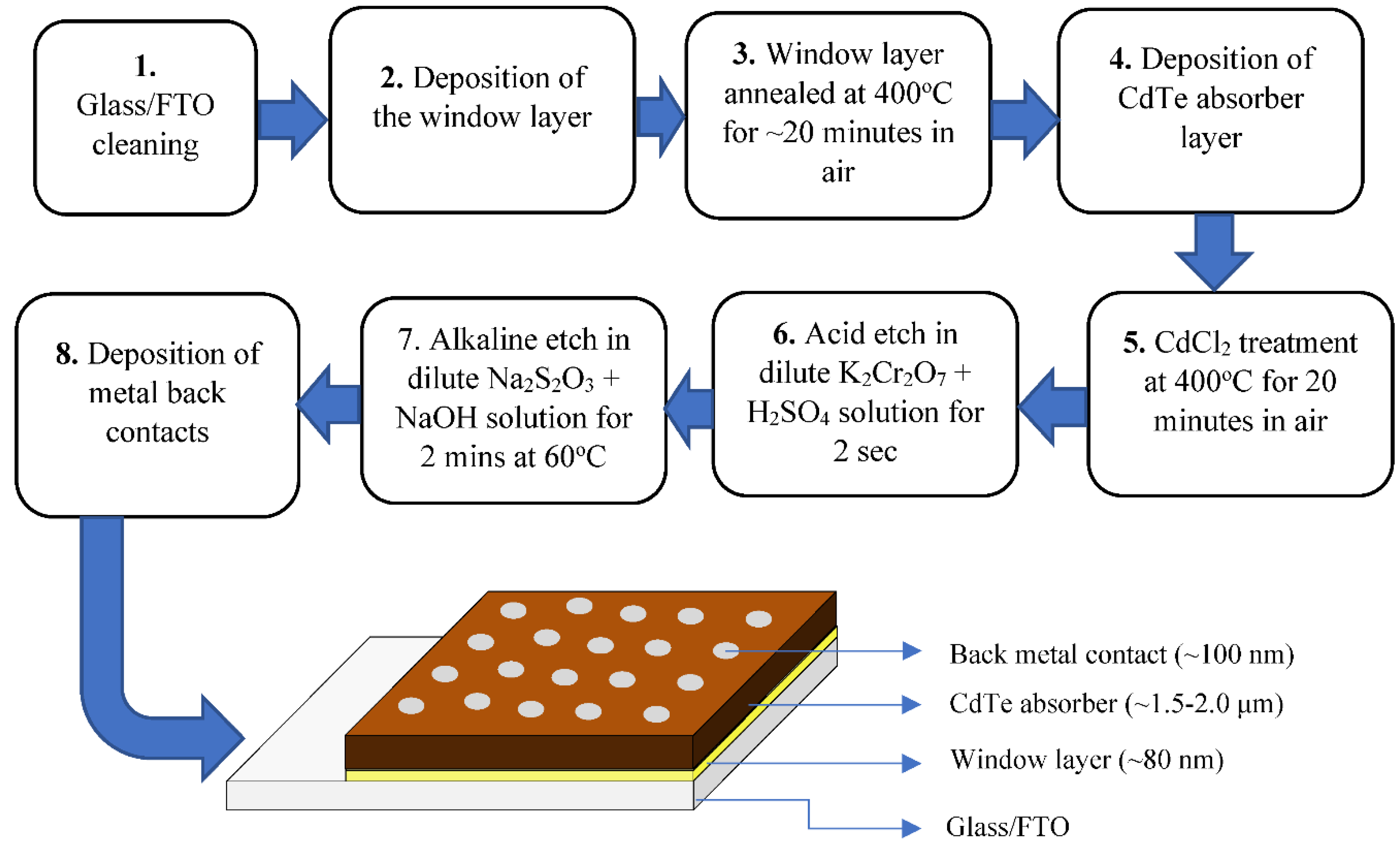

- Dharmadasa, I.M.; Bingham, P.A.; Echendu, O.K.; Salim, H.I.; Druffel, T.; Dharmadasa, R.; Sumanasekera, G.U.; Dharmasena, R.R.; Dergacheva, M.B.; Mit, K.A.; et al. Fabrication of CdS/CdTe-based thin film solar cells using an electro-chemical technique. Coatings 2014, 4, 380–415. [Google Scholar] [CrossRef]

- Dennison, S. Dopant and impurity effects in electrodeposited CdS/CdTe thin films for photovoltaic applications. J. Mater. Chem. 1994, 4, 41. [Google Scholar] [CrossRef]

- Khan, M.A.; Shah, N.A.; Ali, A.; Basharat, M.; Hannan, M.A.; Maqsood, A. Fabrication and Characterization of Cd-Enriched CdTe thin Films by Close Spaced Sublimation; Free Library by Farlex: Huntingdon Valley, PA, USA, 2009. [Google Scholar]

- Evani, V.K. Improving Doping and Minority Carrier Lifetime of CdTe/CdS Solar Cells by In-Situ Control of CdTe Stoichiometry. Ph.D. Thesis, University of South Florida, Tampa, FL, USA, 2017. [Google Scholar]

- Nakayama, N.; Matsumoto, H.; Yamaguchi, K.; Ikagami, S.; Hioki, Y. Ceramic thin film CdTe solar cell. Jan. J. Appl. Phys. 1976, 15, 2281–2282. [Google Scholar] [CrossRef]

- Fritsche, J.; Gunst, S.; Golusda, E.; Lejard, M.C.; Thißen, A.; Mayer, T.; Klein, A.; Wendt, R.; Gegenwart, R.; Bonnet, D.; et al. Surface analysis of CdTe thin film solar cells. Thin Solid Film. 2001, 387, 161–164. [Google Scholar] [CrossRef]

- Dharmadasa, I.M. Review of the CdCl2 Treatment Used in CdS/CdTe Thin Film Solar Cell Development and New Evidence towards Improved Understanding. Coatings 2014, 4, 282–307. [Google Scholar] [CrossRef]

- Compann, A.; Bhat, A. Laser-driven physical vapor deposition for thin-film CdTe solar cells. Int. J. Sol. Energy 1992, 12, 155–169. [Google Scholar] [CrossRef]

- Potter, M.D.G.; Halliday, D.P.; Cousin, M.; Durose, K. A study of the effects of varying cadmium chloride treatment on the luminescent properties of CdTe/CdS thin film solar cells. Thin Solid Films 2000, 361–362, 248–252. [Google Scholar] [CrossRef]

- Mazzamuto, S.; Vailant, L.; Bosio, A.; Romeo, N.; Armani, N.; Salviati, G. A study of the CdTe treatment with a Freon gas such as CHF2Cl. Thin Solid Film. 2008, 16, 7079–7083. [Google Scholar] [CrossRef]

- Jayatirtha, H.N.; Henderson, D.O.; Burger, A.; Volz, M.P. Study of tellurium precipitates in CdTe crystals. Appl. Phys. Lett. 1993, 62, 573–575. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Echendu, O.K.; Fauzi, F.; Abdul-Manaf, N.A.; Olusola, O.I.; Salim, H.I.; Madugu, M.L.; Ojo, A.A. Improvement of composition of CdTe thin films during heat treatment in the presence of CdCl2. J. Mater. Sci. Mater. Electron. 2017, 28, 2343–2352. [Google Scholar] [CrossRef]

- Moutinho, H.R.; Al-Jassim, M.M.; Abufoltuh, F.A.; Levi, D.H.; Dippo, P.C.; Dhere, R.G.; Kazmerski, L.L. Studies of recrystallization of CdTe thin films after CdCl2 treatment. In Proceedings of the 26th IEEE Photovoltaic Specialists Conference (PVSC), Anaheim, CA, USA, 29 September–3 October 1997; pp. 431–434. [Google Scholar]

- Rami, M.; Benamar, E.; Fahoume, M.; Chraibi, F.; Ennaoui, A.M.J. Effect of heat-treatment with CdCl2 on the electrodeposited CdTe/CdS heterojunction. Condens. Matter. 2000, 3, 66–70. [Google Scholar]

- Schaffner, J.; Motzko, M.; Tueschen, A.; Swirschuk, A.; Schimper, H.J.; Klein, A.; Modes, T.; Zywitzki, O.; Jaegermann, W. 12% efficient CdTe/CdS thin film solar cells deposited by low-temperature close space sublimation. J. Appl. Phys. 2011, 110, 064508. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Thornton, J.M.; Williams, R.H. Effects of surface treatments on Schottky barrier formation at metal/n-type CdTe contacts. Appl. Phys. Lett. 1989, 54, 137–139. [Google Scholar] [CrossRef]

- Sobiesierski, Z.; Dharmadasa, I.M.; Williams, R.H. Correlation of photoluminescence measurements with the composition and electronic properties of chemically etched CdTe surfaces. Appl. Phys. Lett. 1988, 53, 2623–2625. [Google Scholar] [CrossRef]

- Diso, D.G.; Fauzi, F.; Echendu, O.K.; Dharmadasa, I.M. Optimisation of CdTe Electrodeposition Voltage for Development of CdS/CdTe Solar Cells. J. Mater. Sci. Mater. Electron. 2016, 27, 12464–12472. [Google Scholar] [CrossRef]

- Salim, H.I.; Patel, V.; Abbas, A.; Walls, M.; Dharmadasa, I.M. Electrodeposition of CdTe thin films solar cells using nitrate precursor. J. Mater. Sci. Mater. Electron. 2015, 26, 3119–3128. [Google Scholar] [CrossRef]

- Abdul-Manaf, N.A.; Salim, H.I.; Madugu, M.L.; Olusola, O.I.; Dharmadasa, I.M. Electroplating and characterisation of Cadmium Telluride thin films using CdCl2 as the cadmium source. Energies 2015, 8, 10883–10903. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Echendu, O.K.; Fauzi, F.; Abdul-Manaf, N.A.; Salim, H.I.; Druffel, T.; Dharmadasa, R.; Lavery, B. Effects of CdCl2 treatment on deep levels in CdTe and their implications on thin film solar cells; A comprehensive photoluminescence study. J. Mater. Sci. Mater. Electron. 2015, 26, 4571–4583. [Google Scholar] [CrossRef]

- Dharmadasa, I.M. Recent developments and progress on electrical contacts to CdTe, CdS and ZnSe with special reference to barrier contacts to CdTe. Prog. Cryst. Growth Charact. Mater. 1998, 36, 249–290. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Blomfield, C.J.; Scott, G.C.; Coratger, R.; Ajustron, F.; Beauvillain, J. Metal/n-CdTe interfaces: A study of electrical contacts by DLTS and BEEM. Solid State Electron. 1998, 42, 595–604. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Samantilleke, A.P.; Young, J.; Chaure, N.B. New ways of development of Glass/Conducting Glass/CdS/CdTe/metal thin film solar cells based on a new model. Semicond. Sci. Technol. 2002, 17, 1238–1248. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Alam, A.E.; Ojo, A.A.; Echendu, O.K. Scientific complications and controversies noted in the field of CdS/CdTe thin film solar cells and the way forward for further development. J. Mater. Sci. Mater. Electron. 2019, 30, 20330–20344. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Ojo, A.A. Unravelling complex nature of CdS/CdTe based thin film solar cells. J. Mater. Sci. Mater. Electron. 2017, 28, 16598–16617. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Ojo, A.A.; Salim, H.I.; Dharmadasa, R. Next Generation Solar Cells Based on Graded Bandgap Device Structures Utilising Rod-type Nano-Materials. Energies 2015, 8, 5440–5458. [Google Scholar] [CrossRef]

- Zanio, K. Semiconductors and Semimetals; Academic Press: New York, NY, USA, 1978; Volume 13. [Google Scholar]

- Zywitzki, O.; Modes, T. High resolution EBIC investigations on cross-sections of cadmium telluride thin film solar cells. In Proceedings of the 27th European Photovoltaic Solar Energy Conference and Exhibition, Frankfurt, Germany, 24–28 September 2012; pp. 2226–2231. [Google Scholar]

- Luria, J.; Kutes, Y.; Moore, A.; Zhang, L.; Stach, E.A.; Huey, B.D. Charge transport in CdTe solar cells revealed by conductive tomographic atomic force microscopy. Nat. Energy 2016, 1, 16150. [Google Scholar] [CrossRef]

- Dharmadasa, I.M. Third Generation Multi-layer Tandem Solar Cells for Achieving High Conversion Efficiencies. Sol. Energy Mater. Sol. Cells 2005, 85, 293–300. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Roberts, J.S.; Hill, G. Third Generation Multi-layer Graded Bandgap Solar Cells for Achieving High Conversion Efficiencies—II: Experimental results. Sol. Energy Mater. Sol. Cells 2005, 88, 413–422. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Kalyanaratne, N.D.P.S.R.; Dharmadasa, R. Effective harvesting of photons for improvement of solar energy conversion by graded bandgap multilayer solar cells. J. Natn. Sci. Found. Sri Lanka 2013, 41, 73–80. [Google Scholar] [CrossRef]

- Dharmadasa, I.M.; Elsherif, O.; Tolan, G.J. Solar cells active in complete darkness Solar Cells Active in Complete Darkness. J. Phys. Conf. Ser. 2011, 286, 012041. [Google Scholar] [CrossRef]

- Alam, A.E.; Ojo, A.A.; Jasinski, J.; Dharmadasa, I.M. Magnesium incorporation in n-CdTe to produce wide bandgap p-type CdTe:Mg window layers. Chem. Eng. 2018, 2, 59. [Google Scholar] [CrossRef]

- Alam, A.E.; Olusola, O.I.; Loch DA, L.; Shukla, K.; Cranton, W.M.; Dharmadasa, I.M. Electrodeposition of ternary compounds for novel PV application and optimisation of electrodeposited CdMnTe thin-films. Sci. Rep. 2020, 10, 21445. [Google Scholar] [CrossRef] [PubMed]

- Ojo, A.A.; Dharmadasa, I.M. 15.3% efficient graded bandgap solar cells fabricated using electroplated CdS and CdTe thin films. Sol. Energy 2016, 136, 10–14. [Google Scholar] [CrossRef]

- Paulson, P.D.; Dutta, V. Study of in situ CdCl2 treatment on CSS deposited CdTe films and CdS/CdTe solar cells. Thin Solid Film. 2000, 370, 299–306. [Google Scholar] [CrossRef]

- Davies, A.; Sites, J.R.; Enzenroth, R.A.; Sampath, W.S.; Barth, K.L. All-CSS processing of CdS/CdTe thin-film solar cells with thin CdS layers. MRS Online Proc. Libr. 2007, 1012, 323. [Google Scholar] [CrossRef]

- Amin, N.; Rahman, K.S. Close-Spaced Sublimation (CSS): A Low-Cost, High-Yield Deposition System for Cadmium Telluride (CdTe). Thin Film. Sol. Cells 2017, 361. [Google Scholar] [CrossRef]

- Romeo, A.; Khrypunov, G.; Alassini, S.G.; Zogg, H.; Tiwari, A.N.; Romeo, N.; Bosio, A.; Mazzamuto, S. Comparison of CSS-CdTe and PVD-CdTe with different activation processes. In Proceedings of the 22nd European Photovoltaic Solar Energy Conference, Milan, Italy, 3–7 September 2007. [Google Scholar]

- Vapor Pressures of the Elements (Data Page)—Wikipedia. Available online: https://en.wikipedia.org/wiki/Vapor_pressures_of_the_elements_(data_page) (accessed on 18 October 2022).

- Reese, M.O.; Perkins, C.L.; Burst, J.M.; Farrell, S.; Barnes, T.M.; Johnston, S.W.; Kuciauskas, D.; Gessert, T.A.; Metzger, W.K. Intrinsic surface passivation of CdTe. J. Appl. Phys. 2015, 118, 155305. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Dharmadasa, I.M.; Alam, A.E. How to Achieve Efficiencies beyond 22.1% for CdTe-Based Thin-Film Solar Cells. Energies 2022, 15, 9510. https://doi.org/10.3390/en15249510

Dharmadasa IM, Alam AE. How to Achieve Efficiencies beyond 22.1% for CdTe-Based Thin-Film Solar Cells. Energies. 2022; 15(24):9510. https://doi.org/10.3390/en15249510

Chicago/Turabian StyleDharmadasa, I. M., and A. E. Alam. 2022. "How to Achieve Efficiencies beyond 22.1% for CdTe-Based Thin-Film Solar Cells" Energies 15, no. 24: 9510. https://doi.org/10.3390/en15249510

APA StyleDharmadasa, I. M., & Alam, A. E. (2022). How to Achieve Efficiencies beyond 22.1% for CdTe-Based Thin-Film Solar Cells. Energies, 15(24), 9510. https://doi.org/10.3390/en15249510