Abstract

In converter-dominated direct-current microgrids, severe load transients can cause large voltage deviations on the common direct-current bus. To mitigate this, an energy storage system is typically employed, and an isolated bidirectional dual active bridge converter is commonly used as the power interface. Therefore, the controller must ensure robust transient performance under step-load conditions. This paper proposes an active disturbance rejection control framework that adaptively adjusts the bandwidth of an extended state observer using fuzzy logic. The proposed observer increases its bandwidth during transients—based on the estimation error—to accelerate disturbance compensation, while decreasing the bandwidth near steady state to suppress noise amplification. This adaptive tuning alleviates the fixed-bandwidth trade-off between transient speed and noise sensitivity in ESO-based regulation. Hardware experiments under load-step conditions validate the method: for a load increase, the peak voltage undershoot and settling time are reduced by 22% and 48.9% relative to a proportional–integral controller, and by 20% and 36.1% relative to a fixed-bandwidth observer. For a load decrease, the peak overshoot and settling time are reduced by 27.9% and 49.5% compared with the proportional–integral controller, and by 20.5% and 25% compared with the fixed-bandwidth observer.

1. Introduction

Recently, driven by carbon-neutrality targets and the efficiency requirements of power-electronics-dominated systems, DC microgrids (DCMGs) are gaining traction across applications such as data centers, transportation electrification, and industrial facilities [1]. Compared with ac distribution, DC architectures avoid frequency and phase synchronization requirements, reduce issues related to reactive-power flows and harmonics/unbalances, and interface naturally with renewable sources, power-electronic loads, and energy storage systems (ESS) [1,2]. In particular, in islanded or weakly grid-tied DCMGs, rapid variations in load and generation can induce deviations of the common DC-bus voltage; thus, tight regulation and fast restoration to the nominal reference become key control objectives for power quality and reliability [3,4,5]. To mitigate these power imbalances, an ESS is commonly integrated to buffer fast dynamics [6]. As a bidirectional power interface between the ESS and the DC bus, the dual active bridge (DAB), an isolated bidirectional DC/DC converter, is widely used [7,8]. The DAB offers high-frequency galvanic isolation, high power conversion efficiency over a wide operating range, and flexible power flow control through various modulation techniques such as single-phase-shift (SPS) and triple-phase-shift (TPS) [9,10,11,12,13,14]. Moreover, accurate average and discrete models have been established [11], along with frequency-domain zero-voltage switching (ZVS) boundary analysis [12] and phase-shift control methods for achieving fast dynamic response [13,14]. These modulation and control design guidelines have been systematically presented, and their reliability in high-power applications has been experimentally validated [11,12,13,14]. However, in real DCMG environments, superimposed uncertainties—including bus-impedance variations, model mismatch, sensor noise and delay, and abrupt step-like load changes—make an inherent trade-off between the robustness and dynamic performance of the DAB controller unavoidable [3,10].

Traditionally, single-voltage-loop PI controllers are designed for a specific operating point. Therefore, under rapid load transients, the operating point shifts away from the design point, making it difficult to maintain optimal performance [14,15]. Model predictive control (MPC) offers the advantage of fast transient response; however, it has inherent limitations, including a high computational burden in high-switching-frequency and high-speed sampling environments, as well as sensitivity to model mismatches [16,17,18,19,20]. Conventional sliding mode control (SMC) offers high robustness and fast responsiveness; however, due to its discontinuous switching control, chattering can occur, which may degrade system performance and cause potential damage to mechanical components [21,22]. Therefore, active disturbance rejection control (ADRC), which reduces dependence on detailed models while maintaining fast transient response and robustness, has attracted attention as an alternative [23]. The core of ADRC, the extended state observer (ESO), can compensate for model uncertainties and disturbances by treating them as a single total disturbance, thereby simplifying the control structure [24,25]. However, ESO inherently presents a trade-off between dynamic performance and noise based on the observer bandwidth; increasing the bandwidth improves dynamic performance but simultaneously amplifies noise [8,26,27,28].

To address these limitations, this paper proposes a fuzzy logic-based ESO bandwidth adjustment method for the DAB converter. In this approach, fuzzy logic operates based on the estimation error to adaptively adjust the observer bandwidth of the ESO in real time. This method mitigates the drawbacks of the strong dependence of MPC on models and parameters, the fixed-gain trade-off of ADRC, and chattering in SMC, while enhancing both power quality and reliability under severe step-load transients in converter-dominated DC microgrids.

The main contributions of this paper are summarized as follows:

- A unified frequency-domain analysis of the fixed-bandwidth ESO for DAB voltage regulation is presented, clarifying the trade-off between low-frequency disturbance rejection (under operating-point/model mismatch) and high-frequency noise amplification.

- A fuzzy logic-based adaptive ESO (FESO) is proposed to tune the observer bandwidth online using the ESO estimation error, increasing it only during transients for faster disturbance compensation while reducing it near steady state to mitigate noise sensitivity.

- The proposed method is validated via sensitivity-based robustness analysis under operating-point variations and hardware step-load experiments, demonstrating reduced voltage deviation and shorter settling time compared with a PI controller and a conventional fixed-bandwidth ESO.

The structure of this paper is as follows: Section 2 discusses the principles of ADRC. Section 3 presents the DAB converter controller design methodology and explains the ESO bandwidth trade-off. Section 4 describes the proposed fuzzy logic-based bandwidth adjustment method. Section 5 verifies the performance of the proposed method through hardware experiments. Section 6 discusses the scope of the proposed local controller and future research directions that consider communication constraints in distributed extensions. Finally, Section 7 concludes this paper.

2. Review of the ADRC Framework

Active disturbance rejection control (ADRC) models an n-th order system as an ideal n-th order integrator between the input and output, and separates it into a total disturbance that includes internal parameter uncertainties and external disturbances as shown in (1):

(1) can be expressed in a state-space form with an extended structure that includes the disturbance term. To estimate the total disturbance , the extended model can be reconstructed in the form of a Luenberger observer as shown in (2):

Here, denotes the actual output, and represents the estimated output. The observer gain reacts to the difference between the measured output and the estimated value. Using this structure, an ESO (extended state observer) is constructed to estimate the lumped disturbance term.

The input for compensating the estimated disturbance can be expressed as

If the disturbance is perfectly estimated such that , substituting (3) into (1) yields the following simple n-th order integrator form:

The observer gains are commonly designed via pole placement using a single observer bandwidth parameter as follows:

As shown in (6), all observer poles are determined by the observer bandwidth :

As a result, the roots of the characteristic equation are located at , which defines the dynamic performance of the observer:

As the poles move farther left in the left-half plane (LHP), the observer bandwidth increases, leading to faster convergence of the estimation error to zero. However, if becomes excessively large, the system becomes sensitive to noise and may suffer from limitations due to the sampling frequency. The detailed derivation of the ESO structure and pole-placement gain design is provided in Appendix A.

3. ADRC for the DAB Converter and Its Limitations

3.1. Controller Design for the DAB Converter

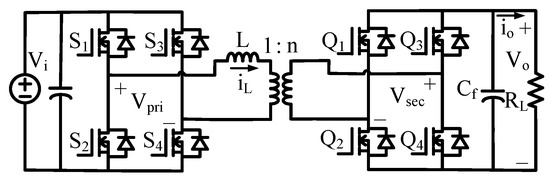

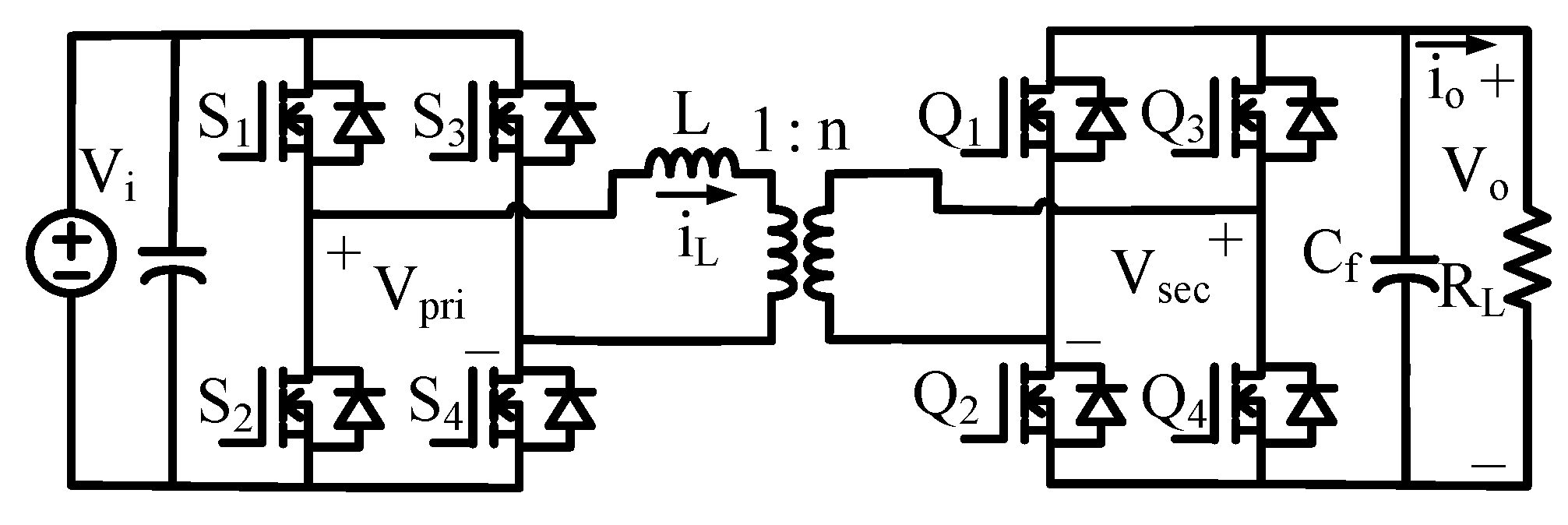

The DAB (Dual Active Bridge) converter consists of full-bridge circuits on both the input and output sides as shown in Figure 1, and these are connected through a transformer. According to [10], the reduced-order model is employed in this paper since it lowers the model complexity while still ensuring high large-signal and small-signal accuracy. In the reduced-order model, the system is approximated as a first-order transfer function with a single dominant pole. The resulting transfer function can be expressed as follows:

Here, N is the turns ratio of the transformer, is the input voltage, and D is the phase shift ratio, which typically ranges from 0 to 0.5. denotes the load resistance, is the switching frequency, is the output capacitance, and L is the series inductance.

Figure 1.

Schematic of the DAB converter.

Figure 1.

Schematic of the DAB converter.

To design the ESO, the transfer function in (8) is transformed into the time domain as

Considering both internal and external uncertainties as a total disturbance, the system can be extended as

If we define the total disturbance as

Then the structure becomes identical to that of (1).

Here, b represents the actual DAB converter parameter, and is the nominal parameter used in the design, which can be expressed as

The input is defined by (3). If the estimated disturbance is denoted as , then can be expressed accordingly as

Therefore, the ESO for the DAB converter can be derived from (A6) and is formulated as follows:

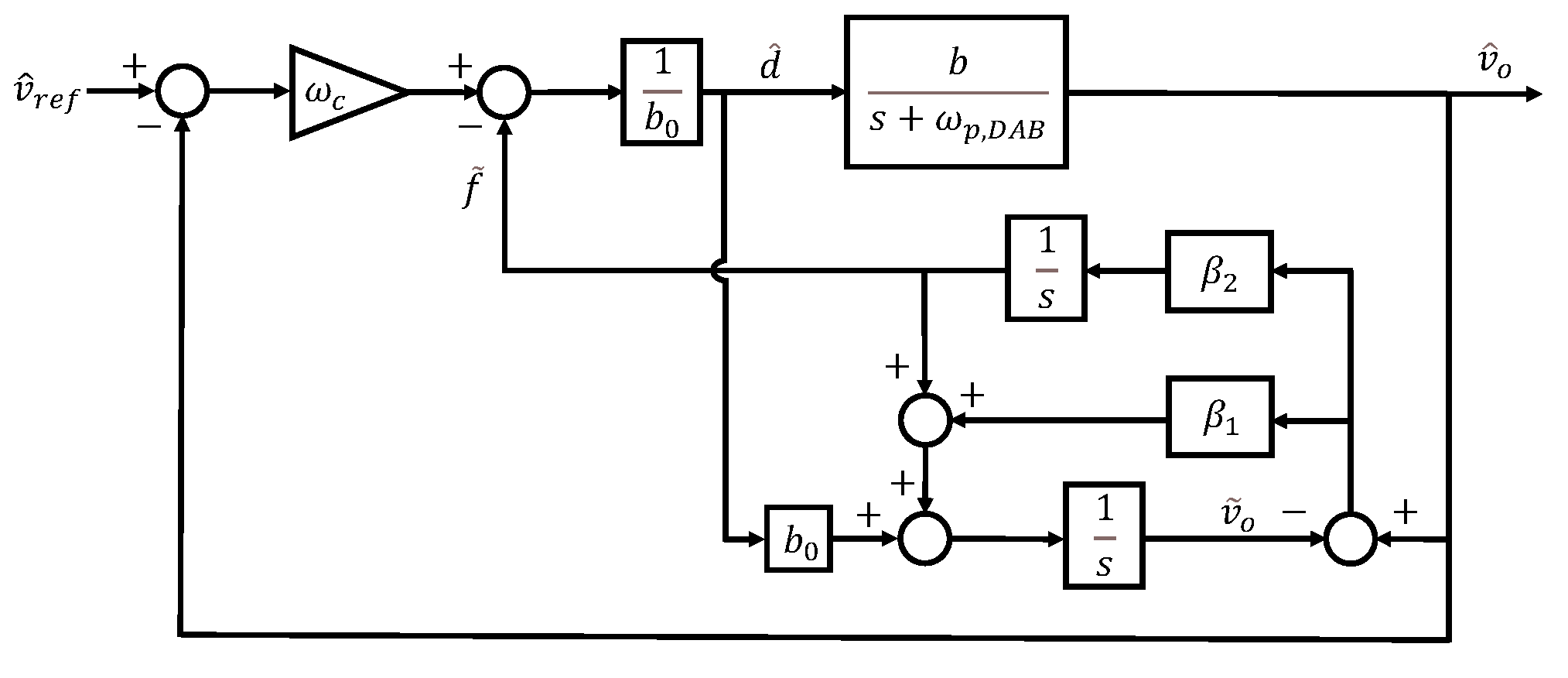

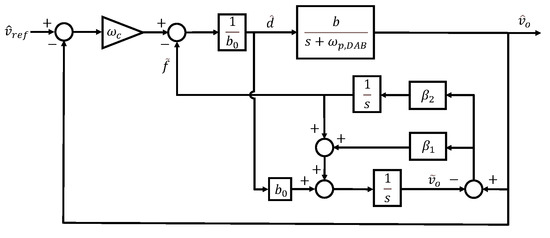

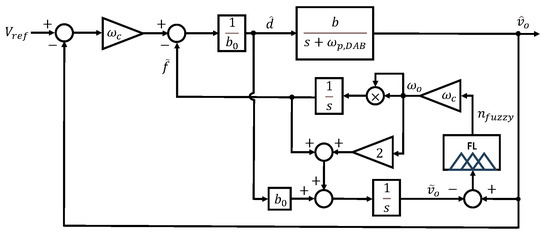

Here, represents the estimated output voltage. If the disturbance is effectively estimated through the observer, the system can be simplified to a first-order integrator form as described in (4). Accordingly, control can be achieved using a simple proportional controller with gain . The structure of this observer can be illustrated using a block diagram as shown in Figure 2.

Figure 2.

Block diagram of ESO system.

3.2. Limitation of the Conventional Method

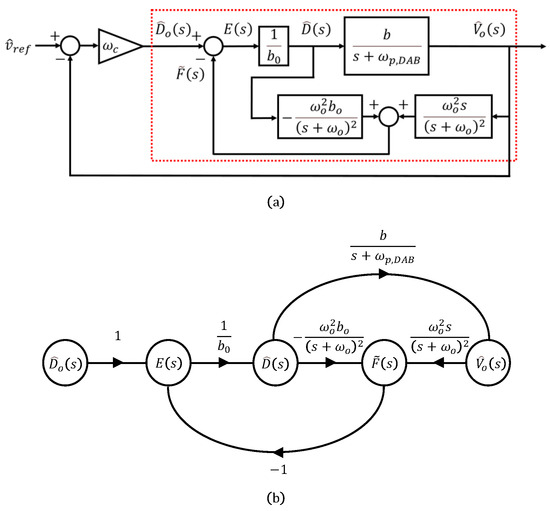

If we choose and , the observer gains can be defined in terms of the observer bandwidth , as shown in (5). This relationship can also be represented using a block diagram, as illustrated in Figure 3a.

Figure 3.

ADRC for DAB: (a) simplified diagram, (b) signal-flow graph for limitation analysis. The red dotted box indicates the ESO-based disturbance estimation and compensation subsystem.

By converting the red boxed region in the block diagram into a signal-flow graph as shown in Figure 3b and applying Mason’s gain rule, the output with respect to the input can be expressed as follows:

where,

The transfer function consists of an overall gain, an integrator, and second-order systems in both the numerator and the denominator. Here, we introduce two design parameters: represents the ratio of the designed parameter to the actual parameter, indicating how much the designed value differs from the actual value, and denotes the ratio of the observer bandwidth to the pole frequency of the DAB, indicating how many times greater the observer’s bandwidth is than the converter’s pole frequency. The natural frequency of the denominator is given by

while the quality factors are usually defined as for the numerator and (20) for the denominator.

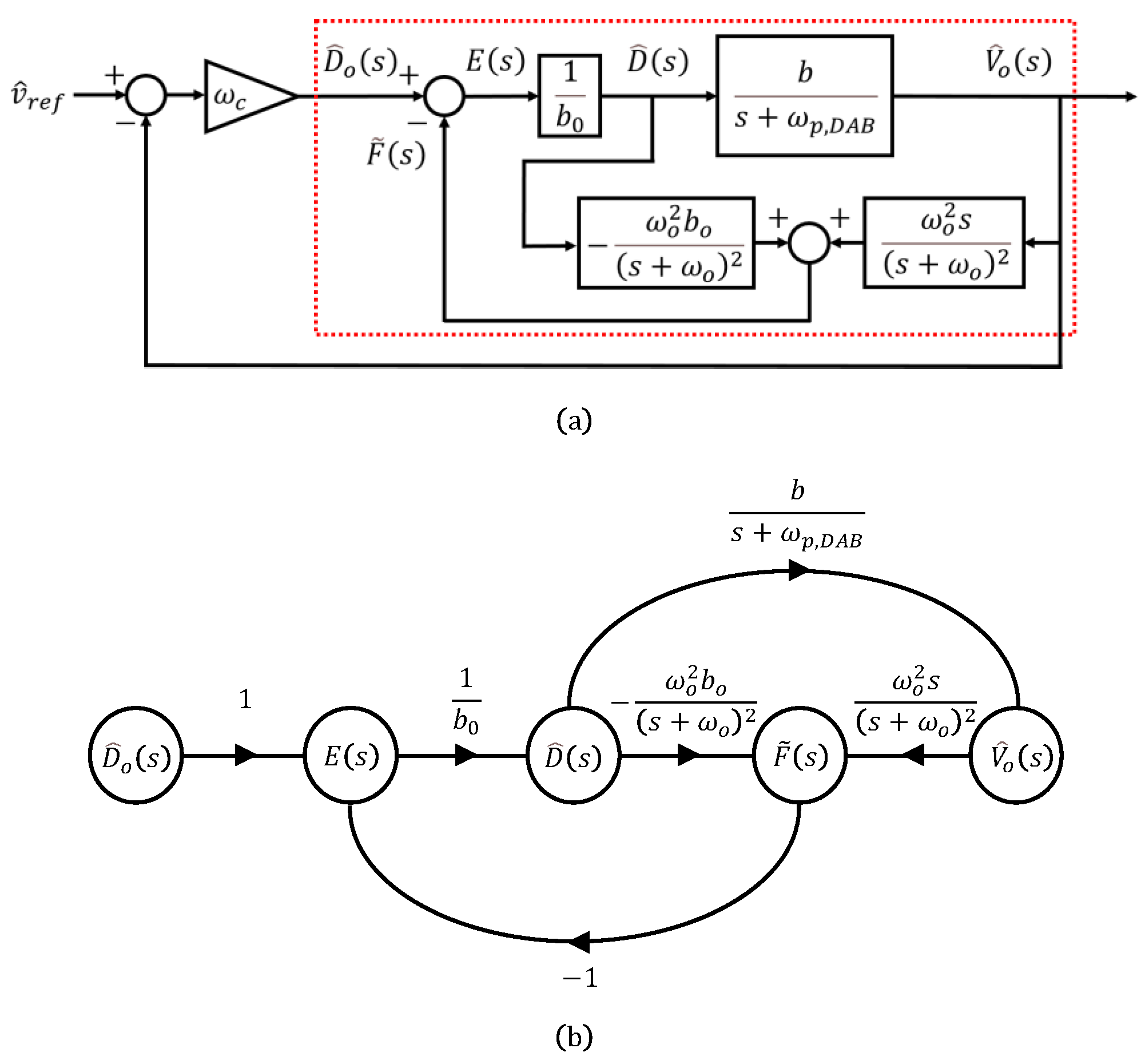

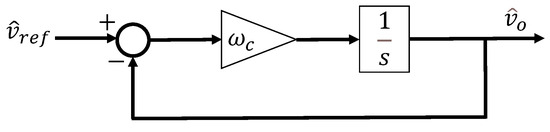

In the ideal case, the nominal and actual parameters of the DAB converter are perfectly matched, resulting in , and the observer bandwidth becomes infinitely large, leading to . Consequently, the natural frequency of the denominator becomes equal to the natural frequency of the numerator , and the quality factor of the denominator also becomes equal to that of the numerator. As a result, the second-order terms result in cancellation, and the overall gain term converges to 1. Therefore, (16) takes the form of a simple integrator, and with the proportional gain , it can be represented as shown in Figure 4, indicating that the larger the observer bandwidth, the better the disturbance estimation performance.

Figure 4.

ADRC for DAB in the ideal case.

Conversely, when the observer bandwidth approaches zero, the quality factor associated with the denominator (20) becomes less than . Since in this case, the characteristic denominator (18) has two distinct real roots, which are given by

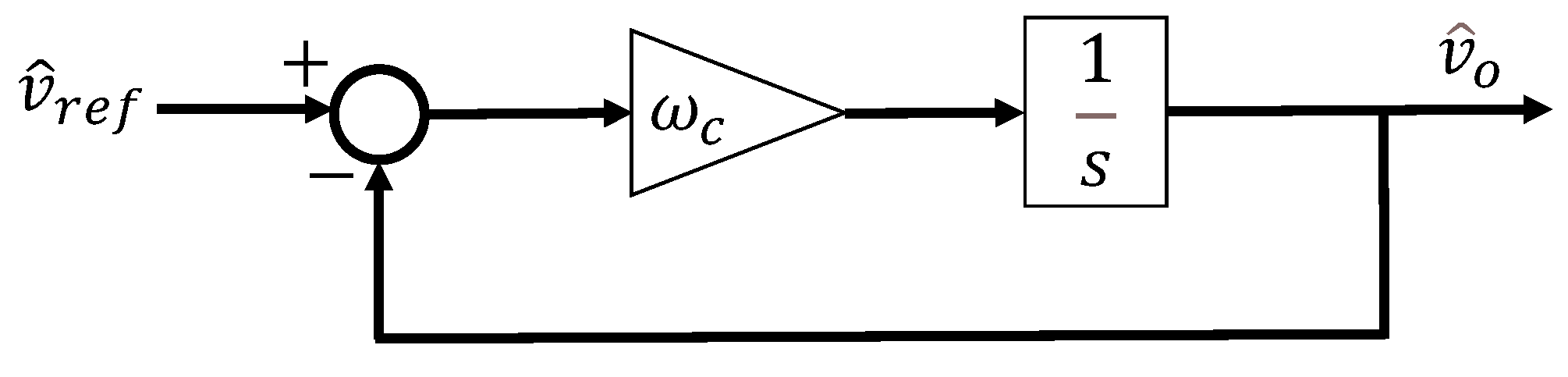

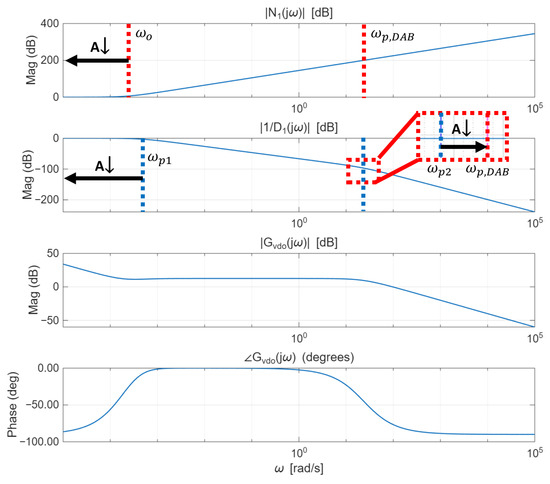

As A decreases, substituting (19) and (20) into (21) and simplifying shows that approaches 0 and approaches . Therefore, the first pole frequency decreases toward zero, and the second pole settles at . This behavior can be analyzed through the Bode plot shown in Figure 5.

Figure 5.

Bode plot of with respect to under a small observer bandwidth, where denotes the observer-bandwidth ratio. The red dotted line indicates the pole frequency of , and the blue dotted line indicates the pole frequency of .

In Figure 5, represents the magnitude of the numerator term of the second-order system in (16), whereas denotes the magnitude of the second-order pole factor (i.e., the inverse of the normalized denominator). In addition, and denote the overall magnitude and phase of (16), respectively.

The second-order numerator increases at a rate of 40 dB/dec around , while the first pole in the denominator causes a decrease of 20 dB/dec. Subsequently, the second pole , located near the DAB converter’s pole frequency , contributes an additional 40 dB/dec attenuation. When an integrator and an overall gain are added as seen in the magnitude of , a flat region appears in the low-frequency range up to the second pole of the denominator. During this region, the overall gain converges to zero. Afterward, the response begins to decrease at a rate of 20 dB/dec. This indicates the formation of a mid-band gain at the crossover frequency, during which the phase margin becomes almost 180 degrees. Consequently, the low-frequency loop gain decreases, degrading disturbance rejection at low frequencies.

From Figure 3b, using Mason’s rule, the relationship between the observer bandwidth and noise can be described by the output-to-disturbance transfer function (22):

where

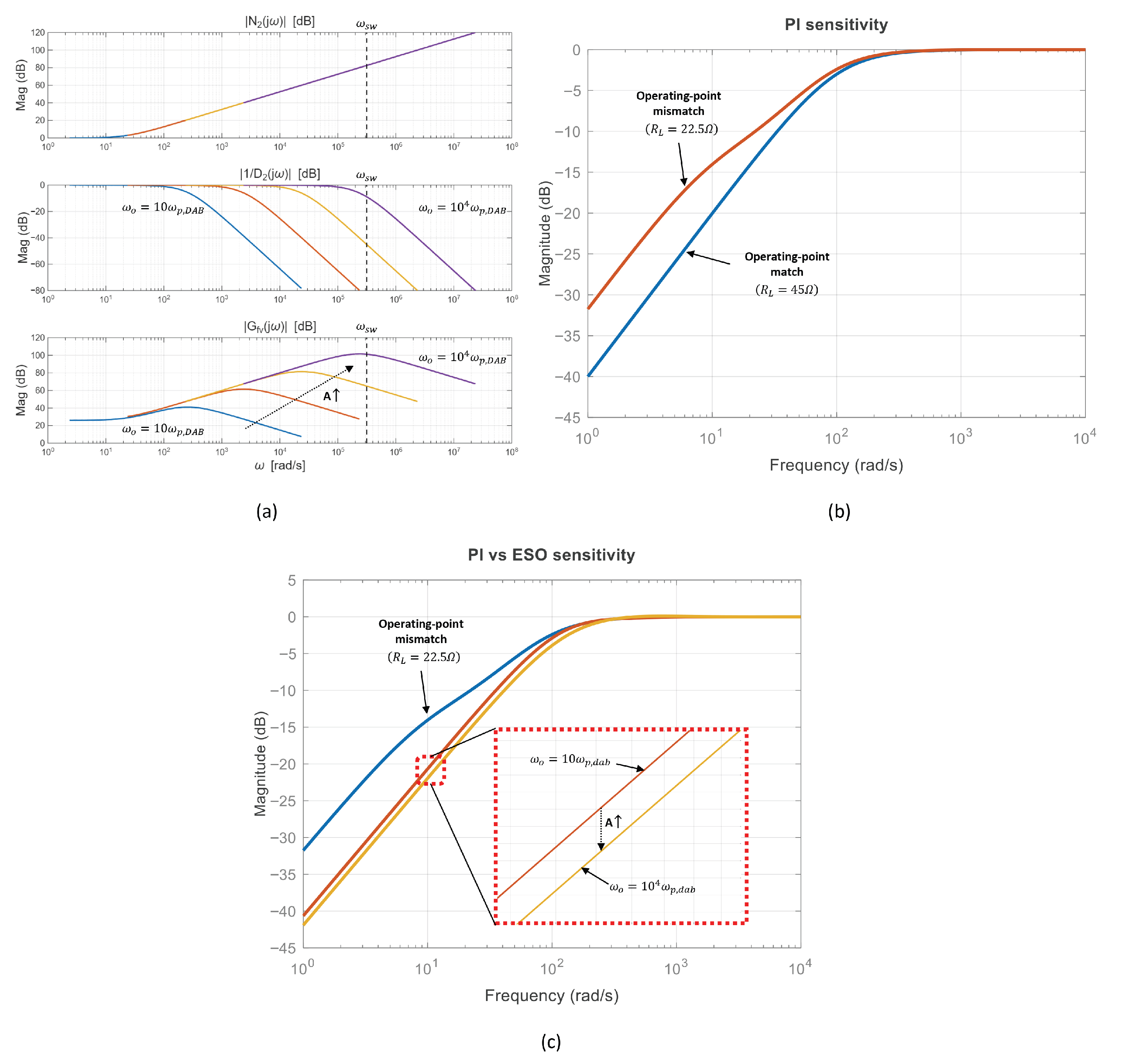

The output voltage consists of various frequency components, including ripple, load variations, and noise. The observer estimates the disturbance based on this signal. Therefore, (22) allows the analysis of the observer’s disturbance estimation characteristics in the frequency domain. Assuming the perfectly matched case (), the resulting Bode plot is shown in Figure 6a. The Bode plot illustrates the cases where A is 10, 100, 1000, and 10,000, and denotes the switching frequency. Here, denotes the magnitude of the numerator term, and represents the magnitude contribution of the second-order denominator term. In addition, indicates the overall magnitude of (22).

Figure 6.

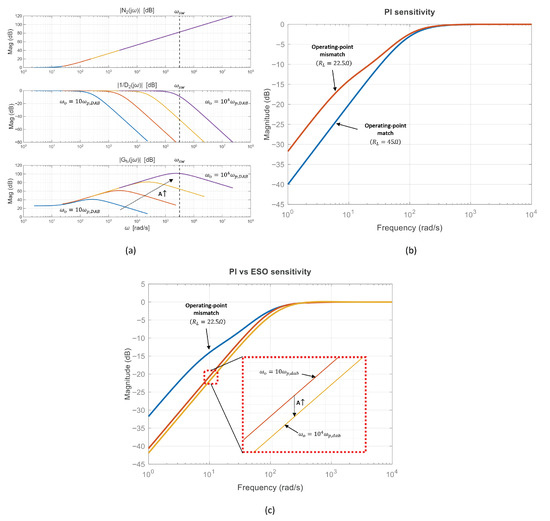

Unified theoretical comparison illustrating the fixed-bandwidth ESO trade-off and the expected benefit of the proposed FESO. (a) Bode plot of the disturbance–estimation dynamics versus (). Solid curves compare , 100, 1000, and 10,000; the dotted arrow indicates increasing A, and the vertical dashed line denotes . (b) Sensitivity–magnitude comparison for a PI controller under operating-point variation: matched case (; design point) vs. mismatched case (). (c) Controller comparison under the same mismatched condition (): PI vs. fixed-bandwidth ESO with different observer bandwidths (, ).

The magnitude of increases at for frequencies above . The contribution of the second-order denominator, , corresponds to two real poles; after the first pole the slope decreases at , and after the second pole it decreases at . As A increases, the quality factor approaches , and the two real poles migrate toward according to (17) and (19), becoming nearly a repeated root. Consequently, the ESO disturbance–estimation magnitude increases at beyond , exhibits a peak near , and then decreases at . As shown in Figure 6a, when , the natural frequency lies near the switching frequency, causing the observer to treat high-frequency noise as a disturbance. As a result, the system becomes highly susceptible to noise.

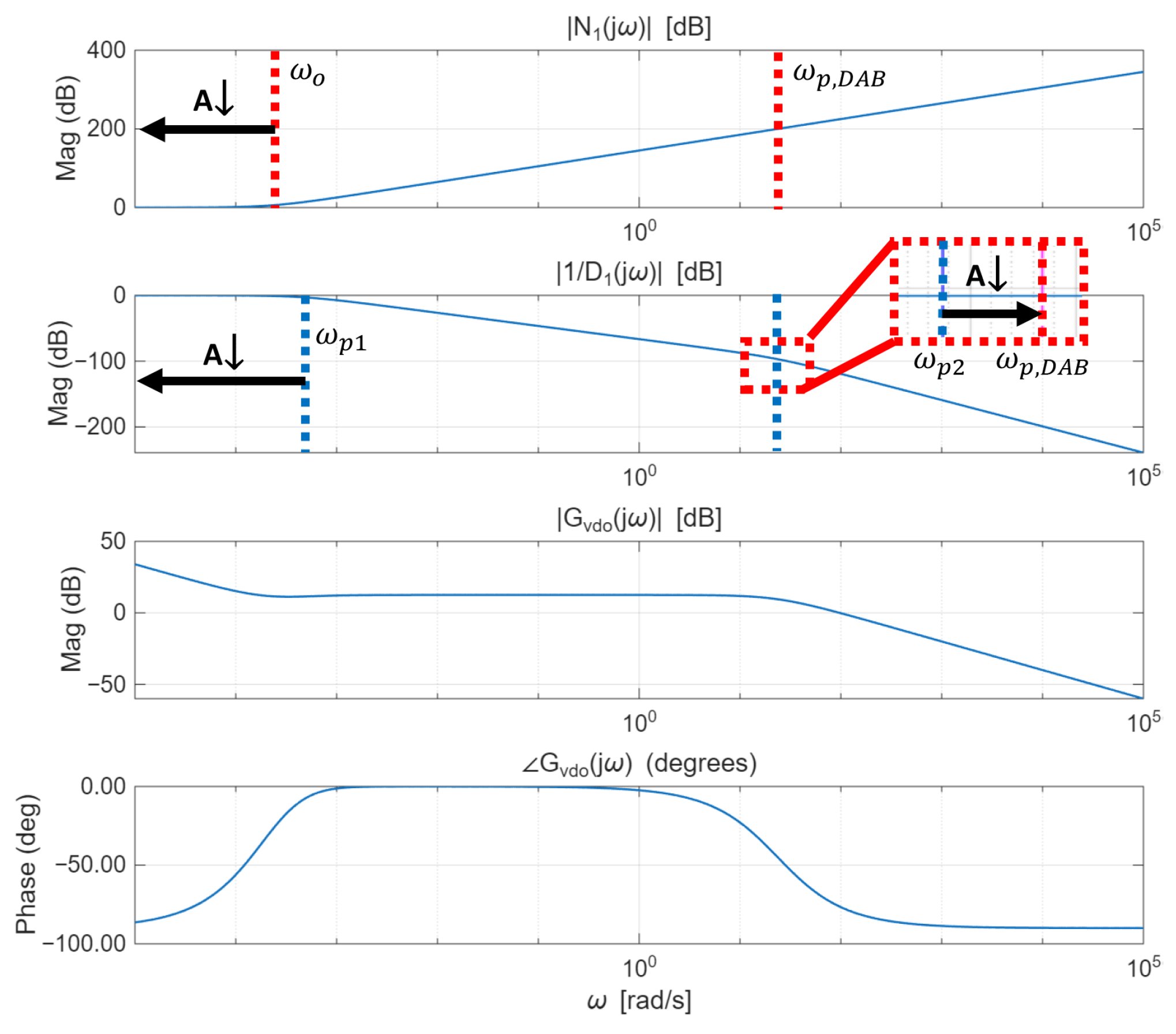

Therefore, if the bandwidth is too low, disturbances cannot be accurately estimated. On the other hand, if the bandwidth is too high, the observer becomes more vulnerable to noise. This indicates a trade-off relationship between estimation accuracy and noise robustness. Therefore, ref. [29] recommends setting the observer bandwidth to be 3 to 10 times the control bandwidth . The closed-loop transfer function in Figure 4 can be expressed as

Considering the 2% settling time criterion, the gain can be determined using

3.3. Sensitivity-Based Robustness Analysis Under Operating-Point Variations

As shown in the reduced-order model of (8), the DAB voltage plant exhibits a dominant pole at , which varies significantly with the load resistance. As the load becomes lighter ( increases), decreases and the plant approaches an integrator. In particular, for a resistive load, the no-load operation is reported to depict a conservative (worst-case) condition for voltage-controller design [30]. Therefore, a fixed-gain controller designed at a nominal operating point may experience performance degradation when the plant deviates from the design point.

To quantify such robustness characteristics in a unified frequency-domain manner, we employ the sensitivity function

where and denote the plant and controller transfer functions, respectively. Since load variations and reference changes are primarily low-frequency phenomena, the low-frequency magnitude of directly indicates disturbance-rejection capability: a smaller at low frequencies corresponds to the improved attenuation of load-induced output-voltage deviations.

Figure 6b compares the sensitivity of a fixed PI controller designed at a light-load operating point () when the plant is evaluated at the design point () and at a heavier-load condition (). Although the PI controller achieves the intended bandwidth at the nominal condition, the operating-point shift changes the dominant pole location () and the effective loop gain, which can increase the low-frequency sensitivity magnitude. This implies degraded rejection of load disturbances when the plant departs from the nominal design point.

Figure 6c compares the PI controller and the ESO-based controllers under the same mismatch condition (controllers designed at while the plant is evaluated at ). Two bandwidth settings, and , are considered to illustrate the effect of on low-frequency disturbance rejection. As increases, the low-frequency sensitivity magnitude can be reduced, indicating improved attenuation of load-induced output-voltage deviations. On the other hand, the noise-related drawback of an excessively large is more directly captured by the disturbance–estimation characteristics in Figure 6a, where approaching causes high-frequency ripple and noise to be treated as disturbances. These observations motivate the proposed fuzzy-bandwidth ESO, which increases only during transient load steps and decreases near steady state to avoid unnecessary noise sensitivity.

4. Proposed Fuzzy-Bandwidth ESO

As discussed in Section 3, a limitation of the conventional ESO is that its bandwidth is fixed. If the bandwidth is designed to be large in pursuit of fast response, the observer becomes more sensitive to noise. Conversely, if the bandwidth is reduced to enhance noise immunity, the disturbance estimation performance deteriorates. This reveals an inherent trade-off between the accuracy of the estimate and the robustness to noise. To overcome this limitation, this paper proposes a fuzzy logic-based ESO that adjusts the observer bandwidth in real time according to the magnitude of the estimation error.

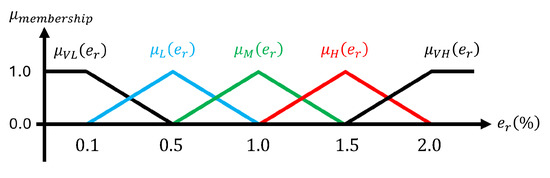

Membership Function

The membership function in fuzzy logic is designed based on the voltage error between the actual output voltage and the voltage estimated by the ESO, and it satisfies the following rules:

- Rule 1: If is VL (Very Low), then is

- Rule 2: If is L (Low), then is

- Rule 3: If is M (Medium), then is

- Rule 4: If is H (High), then is

- Rule 5: If is VH (Very High), then is

Here, represents the relative error between the estimated voltage from the observer and the actual output voltage , which is quantitatively defined as

In (28), the numerator represents the absolute error between the actual output voltage and the estimated voltage from the observer. The denominator corresponds to the reference output voltage that the system aims to achieve. This allows the absolute error to be expressed as a percentage of the system reference target, allowing the design criteria to be set more intuitively and clearly.

In this paper, the error range is divided into five regions for bandwidth design, as shown in Figure 7. The error magnitude is classified into VL (Very Low), L (Low), M (Medium), H (High), and VH (Very High), depending on the output response of the system and the allowable noise range. First, when the error is within , it is regarded as noise, where the signal mainly reflects sensor noise rather than actual disturbance, and the bandwidth is minimized to suppress noise amplification. If the error is between and , it is defined as the steady-state error region, representing small residual errors in which noise suppression remains a priority. An error between and is classified as the internal disturbance region, typically caused by parameter variations, and the bandwidth is moderately increased to compensate for model mismatch. An error between and is regarded as the external disturbance region, associated with load variations or bus impedance changes, requiring faster response through larger bandwidth. Finally, when the error exceeds , it is defined as the transient region, and the bandwidth is maximized to achieve rapid disturbance rejection.

Figure 7.

Membership function.

To ensure minimal computational load and latency in real-time applications, the weighted average defuzzification method is used to determine as defined in (29):

The value of calculated from (29) is confined to the range and is employed as a gain to determine the observer bandwidth , which is defined by

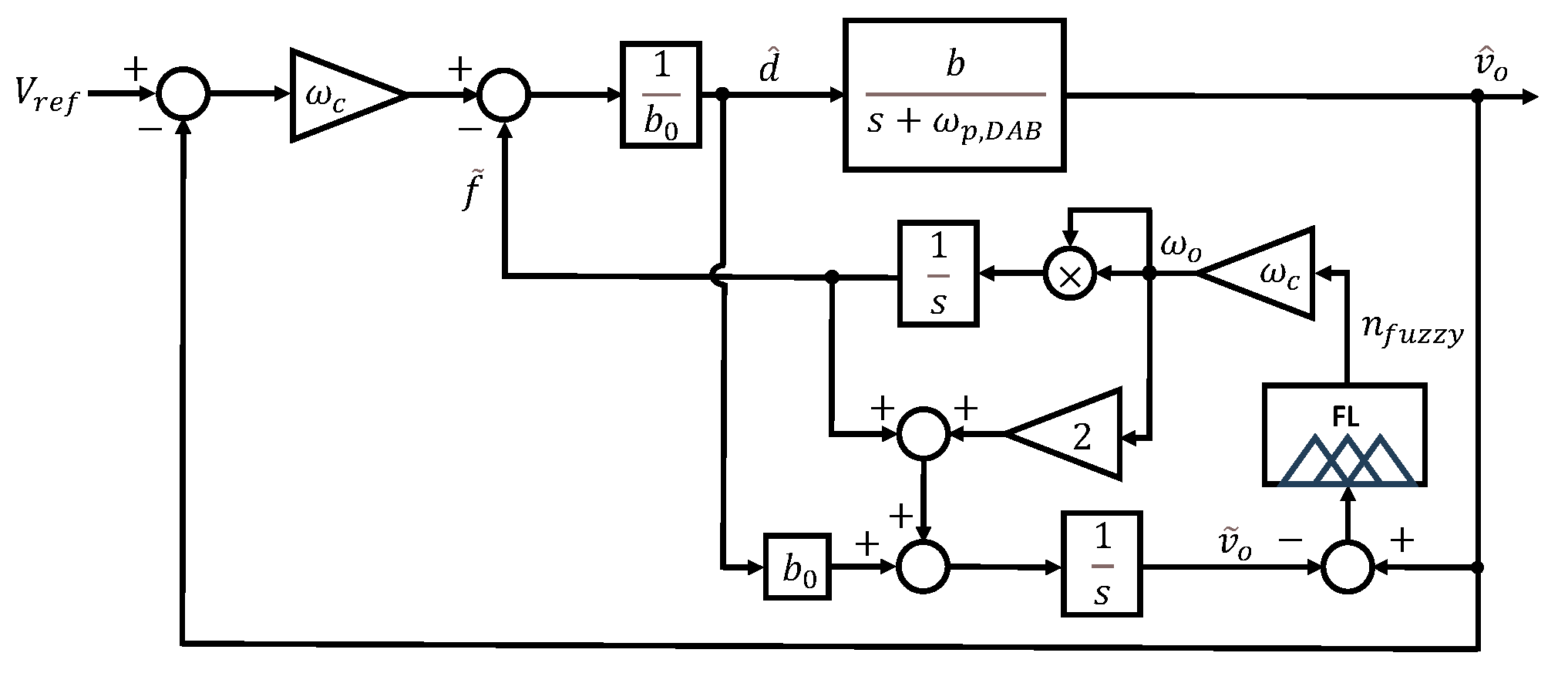

The proposed FESO block diagram is illustrated in Figure 8. As shown in the figures, FESO can dynamically adjust the observer bandwidth in real time. This allows the bandwidth to increase as needed without being significantly affected by noise. Using the error between the actual output and the estimated output of the observer as input to the fuzzy logic, the observer bandwidth can be adaptively adjusted. This dynamic adjustment mechanism enables the proposed FESO to effectively overcome the limitations of conventional fixed-bandwidth ESOs.

Figure 8.

Block diagram of the proposed FESO.

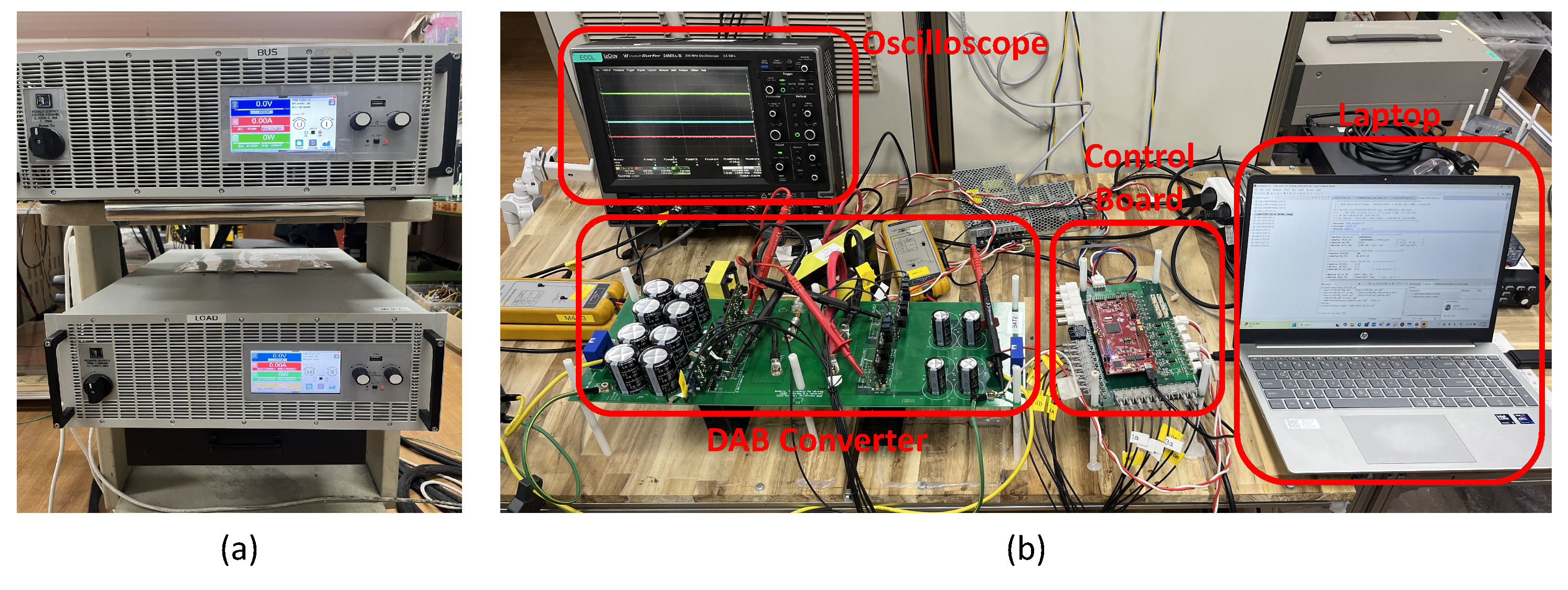

5. Hardware Results

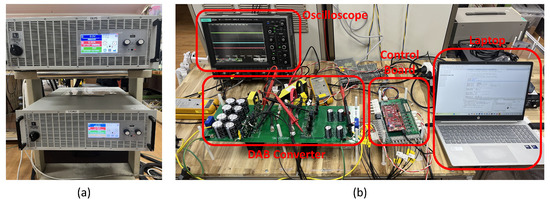

The hardware configuration is shown in Figure 9b. The main parameters of the DAB converter are listed in Table 1, and the control algorithm is implemented on a DSP control platform (TMS320F28379D, Texas Instruments, Dallas, TX, United States). As shown in Figure 9a, two bidirectional power supplies are used at the input and output sides: one is configured as a source, and the other as an electric load to implement the step-load condition.

Figure 9.

Hardware configuration: (a) bidirectional power supplies, (b) overall view of the DAB converter hardware setup.

Table 1.

System parameters.

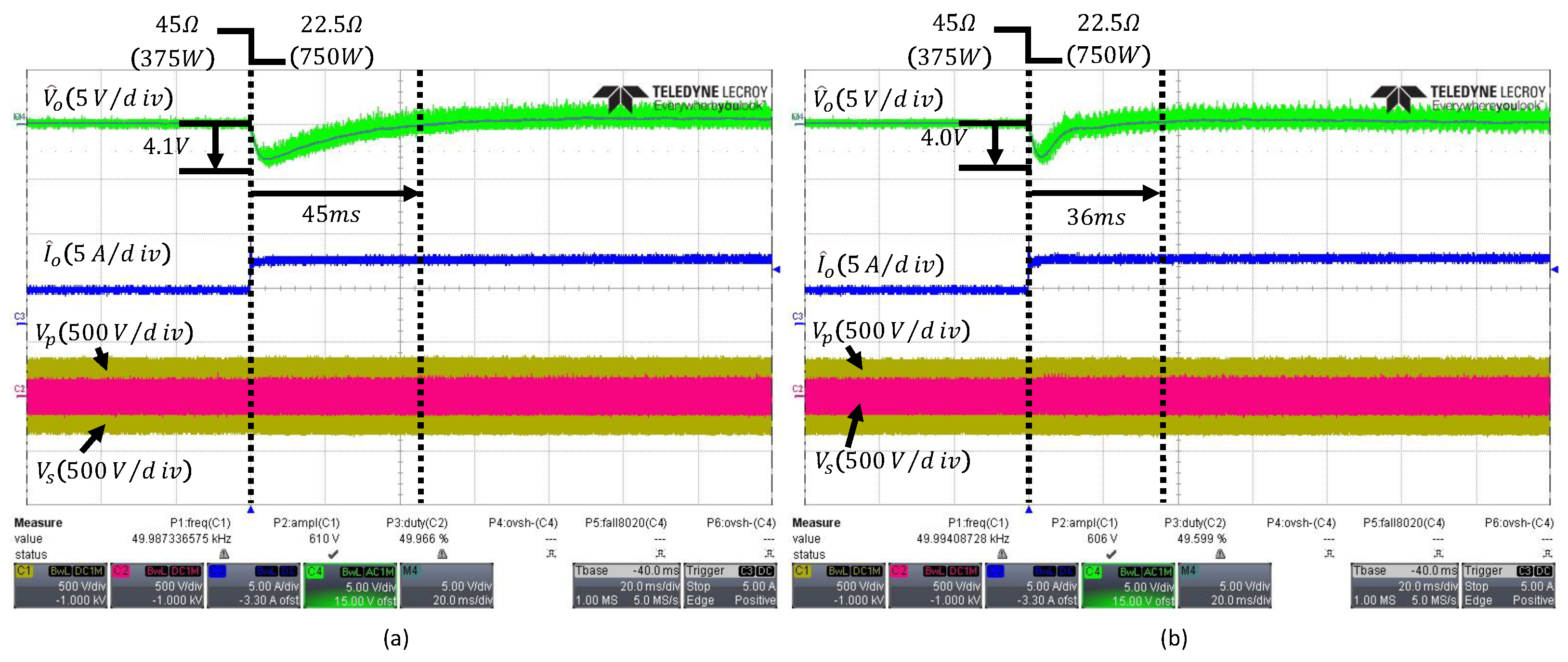

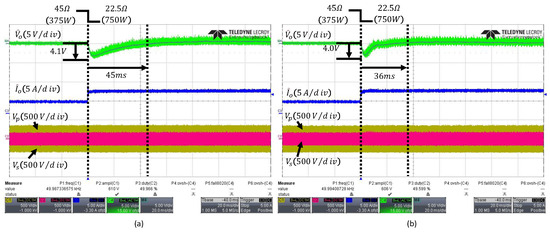

The hardware test was conducted under an output-voltage-controlled condition of 130 V with two step-load change scenarios. In the first scenario, the load was changed from to , causing the output power to increase from 375 W to 750 W. In the second scenario, the load was changed from to , causing the output power to decrease from 750 W to 375 W. For performance comparison with the proposed FESO, a conventional ESO and a PI controller were implemented. In the case of the conventional ESO, to achieve a settling time of 40 ms, the control bandwidth was set to using (26), and the ESO bandwidth was set to , three times the control bandwidth, which is typically accepted. The PI controller was designed using (8) with the pole–zero cancellation method to achieve the same settling time and a phase margin of .

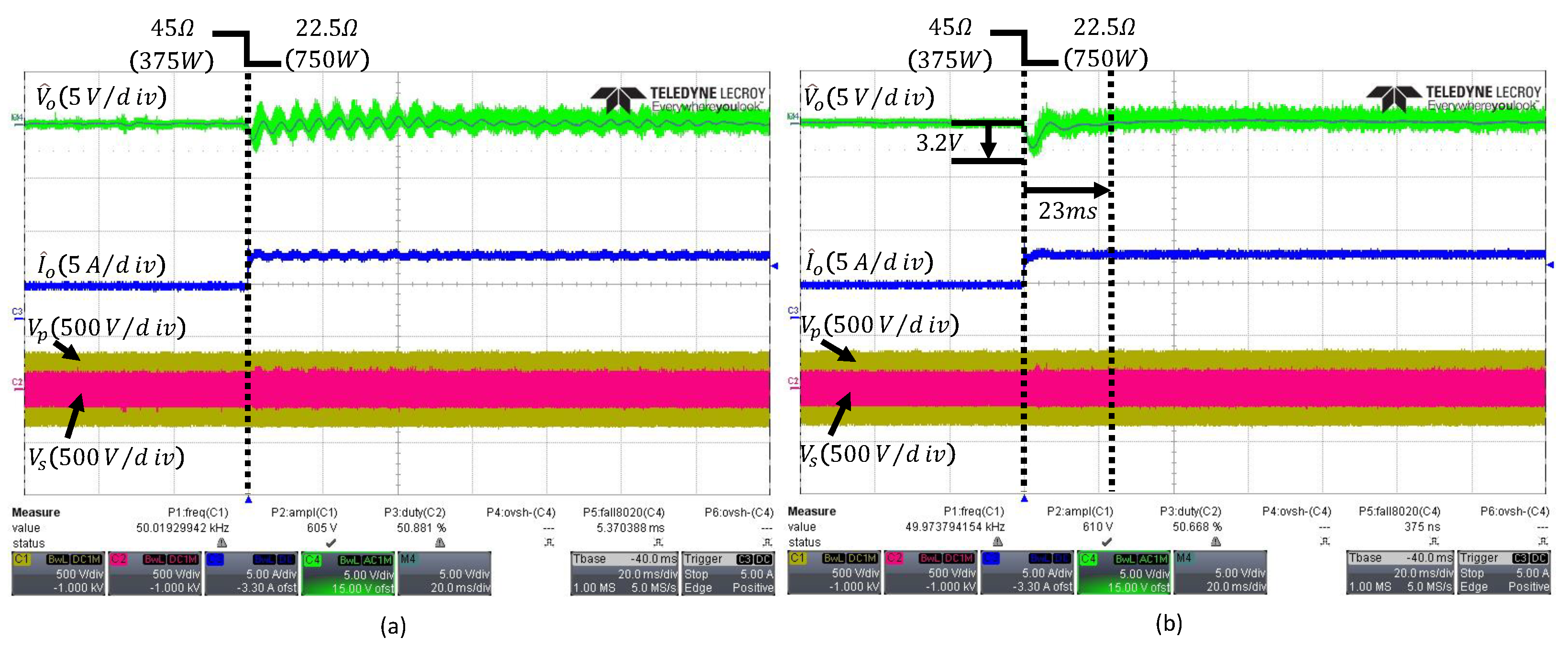

Figure 10 shows the waveforms of the output voltage, output current, and the primary- and secondary-side voltages of the PI controller and the conventional ESO when the load changes from to . Figure 10a presents the waveforms of the PI controller under a load change, showing a voltage undershoot of and a settling time of . Figure 10b presents the waveforms of the conventional ESO, which exhibits a comparable voltage undershoot of but achieves a shorter settling time of , approximately faster than the PI controller. In addition, since the PI controller uses fixed gains, it cannot account for discrepancies between the parameters used in the design and the actual model, leading to degraded transient performance compared with the conventional ESO.

Figure 10.

Transient responses to a load step from to : (a) PI controller, (b) conventional fixed-bandwidth ESO with . The arrows indicate the peak undershoot and the settling time.

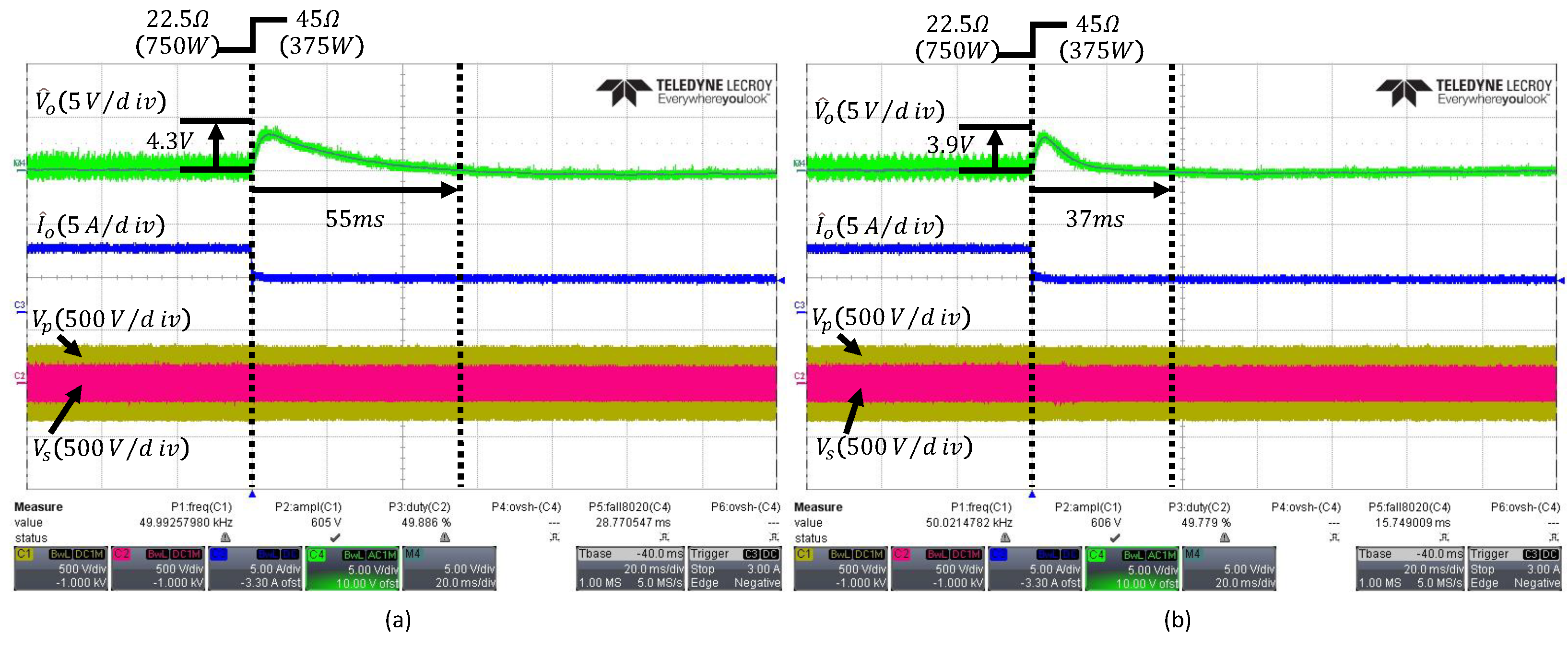

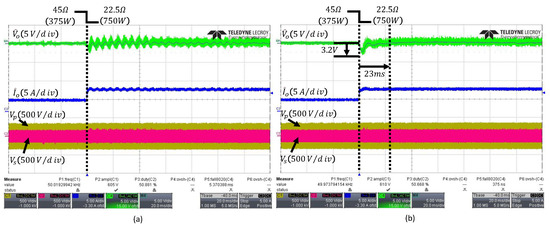

Figure 11a shows the output waveform when the observer bandwidth is set to . This corresponds to 15 times the conventional control bandwidth , which exceeds the typical range of 3 to 10 times. As the bandwidth expands, the high-frequency noise of the output voltage is amplified and reflected in the control signal, as illustrated in Figure 6a. Consequently, it can be observed that the output waveform is affected by the noise. The waveform of the proposed FESO in Figure 11b corresponds to and , which define the lower and upper limits of the observer bandwidth as and . The FESO operates with a low bandwidth under normal conditions to minimize noise influence and increases the bandwidth when internal or external disturbances occur, or during transient periods, according to fuzzy logic. The FESO achieves a settling time of and an undershoot of , and compared to the ESO with a fixed bandwidth of , the output waveform demonstrates that it is more robust to noise.

Figure 11.

Transient responses under load change from to : (a) conventional fixed-bandwidth ESO with , (b) proposed FESO. The arrows indicate the peak undershoot and the settling time.

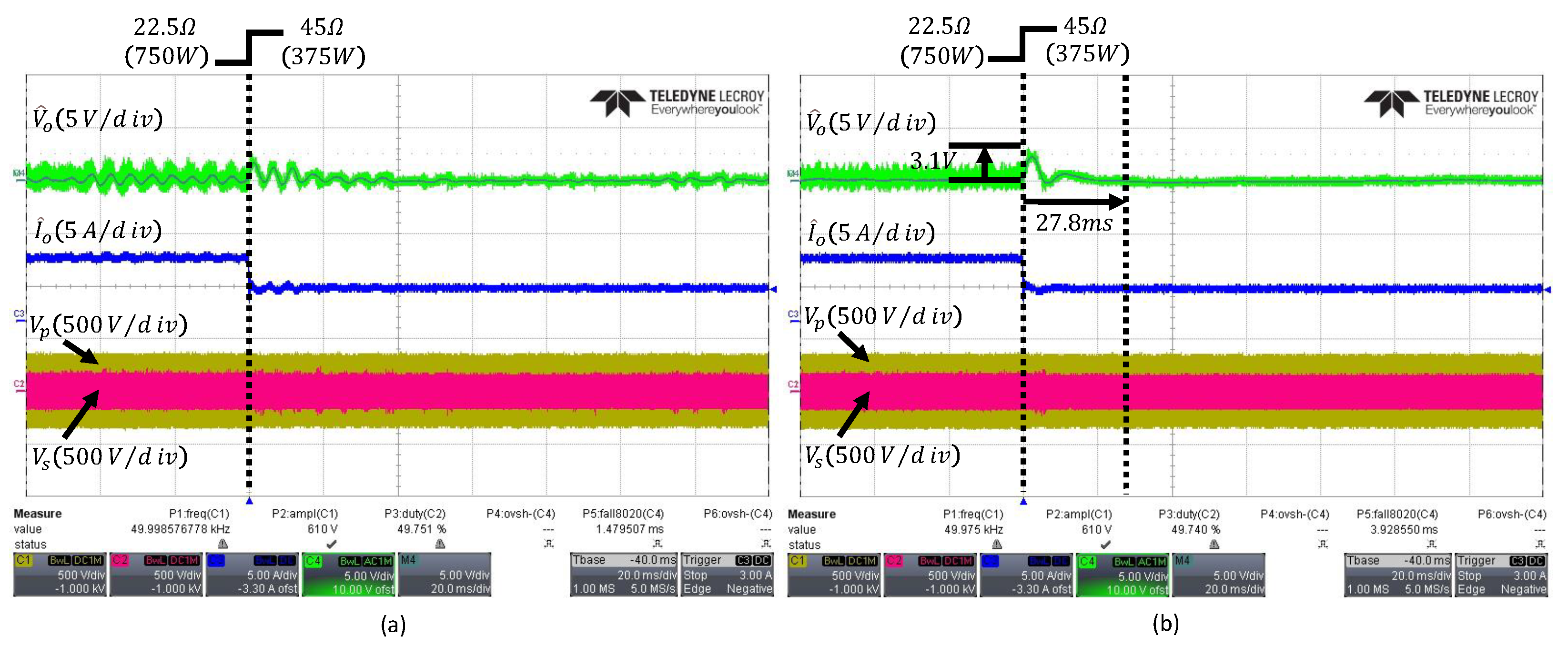

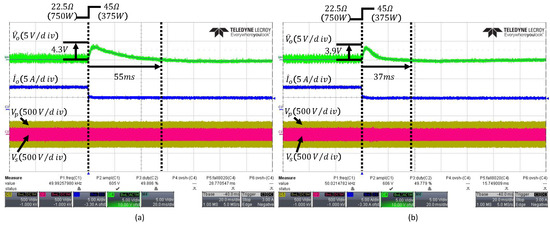

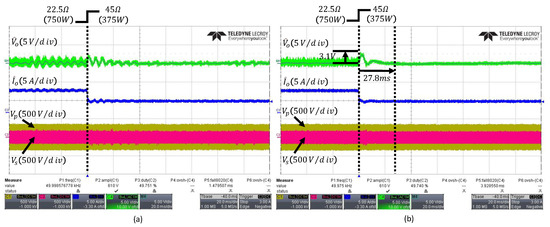

When the load changes from to , the output waveforms of the PI and ESO controller are shown in Figure 12a,b, respectively. The conventional ESO exhibits a voltage overshoot of and a settling time of , whereas the PI controller shows a voltage overshoot of and a settling time of , indicating that the PI controller’s transient performance is inferior to that of the ESO.

Figure 12.

Transient responses under load change from to : (a) PI controller, (b) conventional fixed-bandwidth ESO with . The arrows indicate the peak overshoot and the settling time.

Figure 13 shows the output waveform of the proposed FESO, which achieves an overshoot of and a settling time of , demonstrating improved transient performance over the conventional controllers while minimizing the influence of noise.

Figure 13.

Transient responses under load change from to : (a) conventional fixed-bandwidth ESO with , (b) proposed FESO. The arrows indicate the peak overshoot and the settling time.

Table 2 summarizes the output-voltage deviation and settling time of each controller under both load-decrease and load-increase conditions. From this table, it can be observed that the proposed FESO reduces both the voltage deviation and the settling time, thereby improving the transient performance.

Table 2.

Performance comparison for load-change tests.

6. Discussion

In this work, the proposed ESO-based disturbance compensation is implemented within the local (converter-level) digital controller of a single DAB-based ESS interface; therefore, it does not require inter-agent communication and introduces no additional communication overhead in our experimental setup. Nevertheless, if the framework is extended to networked/distributed cooperative control (e.g., higher-layer voltage restoration and power sharing), communication constraints may become an important design factor. In such cases, event-triggered strategies have been reported as an effective approach to reduce communication while maintaining closed-loop performance, e.g., the adaptive event-triggered output-feedback scheme in [31]. Exploring an event-triggered communication design for distributed extensions of the proposed local controller is an interesting direction for future work.

7. Conclusions

Based on the in-depth analysis of the trade-off associated with the bandwidth of the extended state observer (ESO), this paper proposes a Fuzzy-based ESO (FESO) with variable bandwidth to overcome the limitation of the conventional fixed-bandwidth approach. The proposed FESO adjusts the bandwidth using fuzzy logic, thereby minimizing the influence of noise while improving transient response performance. Experimental results show that, under load increase conditions, the proposed FESO reduces the output voltage undershoot by and compared to the conventional PI controller and ESO, respectively, and shortens the settling time by and . Under load decrease conditions, the output voltage overshoot is reduced by and compared to the PI controller and ESO, respectively, with the settling time reduced by and . These results demonstrate that the proposed FESO provides superior transient response performance compared to conventional controllers under severe step-load conditions, thus providing ADRC for the DAB as the bidirectional power flow for the DC microgrid.

Author Contributions

Conceptualization, J.-H.S. and S.-J.C.; methodology, J.-H.S.; software, J.-H.S.; validation, J.-H.S. and S.-J.C.; formal analysis, J.-H.S.; investigation, J.-H.S.; resources, S.-J.C.; data curation, J.-H.S.; writing—original draft preparation, J.-H.S.; writing—review and editing, J.-H.S. and S.-J.C.; visualization, J.-H.S.; supervision, S.-J.C.; project administration, S.-J.C.; funding acquisition, S.-J.C. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by the Regional Innovation System & Education (RISE) Program through the Ulsan RISE Center, funded by the Ministry of Education (MOE) and the Ulsan Metropolitan City, Republic of Korea, grant number 2025-RISE-07-001. The APC was funded by the same source.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

The original contributions presented in this study are included in the article. Further inquiries can be directed to the corresponding author.

Conflicts of Interest

The authors declare no conflicts of interest. The funders had no role in the design of the study; in the collection, analyses, or interpretation of data; in the writing of the manuscript; or in the decision to publish the results.

Appendix A. Derivation of the ESO Structure and Pole-Placement Gains

This appendix provides the detailed derivation of the extended state observer (ESO) used in the ADRC framework, including the error dynamics and the pole-placement gain expressions. These derivations are omitted from the main text to improve readability.

Appendix A.1. Extended-State Representation

Starting from the ADRC lumped model,

The disturbance is augmented as an additional state to obtain the extended state representation:

Appendix A.2. Luenberger-Observer Formulation

The ESO can be written in the Luenberger-observer form:

where the companion-form matrices are given by

And the observer gain is

Appendix A.3. Component-Wise ESO Form

Using (A3), the ESO dynamics can be expanded as

Appendix A.4. Estimation Error Dynamics and Characteristic Polynomial

Define the estimation error as . Neglecting for the pole-placement analysis, the error dynamics become

The characteristic equation is therefore

which yields the polynomial form

Appendix A.5. Pole-Placement Gain Design

A standard ADRC/ESO pole-placement choice is to place all observer poles at , leading to

Accordingly, the observer gains are obtained as

where

As increases, the observer bandwidth increases and the estimation error converges faster; however, excessively large amplifies measurement noise and may be limited by sampling and switching-frequency constraints.

References

- Dragičević, T.; Lu, X.; Vasquez, J.C.; Guerrero, J.M. DC Microgrids—Part II: A Review of Power Architectures, Applications, and Standardization Issues. IEEE Trans. Power Electron. 2016, 31, 3528–3549. [Google Scholar] [CrossRef]

- Heo, K.-W.; Yun, C.-W.; Jung, G.-G.; Lee, J.-S.; Kim, H.-S.; Jung, J.-H. Enhanced Four-Port Dual-Active-Bridge Converter Employing Power Decoupling Capability for DC Microgrid Islanding Mode Operation. J. Power Electron. 2024, 24, 171–180. [Google Scholar] [CrossRef]

- Dragičević, T.; Lu, X.; Vasquez, J.C.; Guerrero, J.M. DC Microgrids—Part I: A Review of Control Strategies and Stabilization Techniques. IEEE Trans. Power Electron. 2016, 31, 4876–4891. [Google Scholar] [CrossRef]

- Lu, X.; Guerrero, J.M.; Sun, K.; Vasquez, J.C. An Improved Droop Control Method for DC Microgrids Based on Low Bandwidth Communication with DC Bus Voltage Restoration and Enhanced Current Sharing Accuracy. IEEE Trans. Power Electron. 2014, 29, 1800–1812. [Google Scholar] [CrossRef]

- Hao, S.; Li, Z.; Tan, Y.; Qu, R.; Kong, W. Fast Dynamic DC-Link Voltage Control Strategy for Dual Three-Phase PM-Assisted Synchronous Reluctance Starter/Generator System. J. Power Electron. 2024, 24, 1899–1911. [Google Scholar] [CrossRef]

- Faisal, M.; Hannan, M.A.; Ker, P.J.; Hussain, A.; Mansor, M.B.; Blaabjerg, F. Review of Energy Storage System Technologies in Microgrid Applications: Issues and Challenges. IEEE Access 2018, 6, 35143–35164. [Google Scholar] [CrossRef]

- Jung, G.-G.; Lee, J.-S.; Kim, H.-S.; Jung, J.-H. Design Methodology of a Voltage Controller for a Dual-Active-Bridge Converter Utilizing Spread-Spectrum Modulation. J. Power Electron. 2025, 25, 393–404. [Google Scholar] [CrossRef]

- Duong, T.-Q.; Trinh, H.-A.; Ahn, K.-K.; Choi, S.-J. Adaptive Extended State Observer for the Dual Active Bridge Converters. Sensors 2024, 24, 2397. [Google Scholar] [CrossRef]

- Yong, S.-U.; Seo, D.; Kim, S.; Shin, J.-W.; Kim, W. Optimizing Inductance for Minimizing Reactive Power in Single-Phase-Shift Modulated Dual Active Bridge Converters under Variable Input Voltage. J. Power Electron. 2025, 25, 205–215. [Google Scholar] [CrossRef]

- Shao, S.; Chen, L.; Shan, Z.; Gao, F.; Chen, H.; Sha, D.; Dragičević, T. Modeling and Advanced Control of Dual-Active-Bridge DC–DC Converters: A Review. IEEE Trans. Power Electron. 2022, 37, 1524–1547. [Google Scholar] [CrossRef]

- Qin, H.; Kimball, J.W. Generalized Average Modeling of Dual Active Bridge DC–DC Converter. IEEE Trans. Power Electron. 2012, 27, 2078–2084. [Google Scholar] [CrossRef]

- Riedel, J.; Holmes, D.G.; McGrath, B.P.; Teixeira, C. ZVS Soft Switching Boundaries for Dual Active Bridge DC–DC Converters Using Frequency Domain Analysis. IEEE Trans. Power Electron. 2017, 32, 3166–3179. [Google Scholar] [CrossRef]

- Song, W.; Hou, N.; Wu, M. Virtual Direct Power Control Scheme of Dual Active Bridge DC–DC Converters for Fast Dynamic Response. IEEE Trans. Power Electron. 2018, 33, 1750–1759. [Google Scholar] [CrossRef]

- Zhao, W.; Zhang, X.; Gao, S.; Ma, M. Improved Model-Based Phase-Shift Control for Fast Dynamic Response of Dual Active Bridge DC/DC Converters. IEEE J. Emerg. Sel. Top. Power Electron. 2020, 9, 223–231. [Google Scholar] [CrossRef]

- Hassan, M.A.; Su, C.-L.; Pou, J.; Sulligoi, G.; Almakhles, D.; Bosich, D.; Guerrero, J.M. DC Shipboard Microgrids with Constant Power Loads: A Review of Advanced Nonlinear Control Strategies and Stabilization Techniques. IEEE Trans. Smart Grid 2022, 13, 3422–3438. [Google Scholar] [CrossRef]

- Tarisciotti, L.; Chen, L.; Shao, S.; Dragičević, T.; Wheeler, P.; Zanchetta, P. Finite Control Set Model Predictive Control for Dual Active Bridge Converter. IEEE Trans. Ind. Appl. 2022, 58, 2155–2165. [Google Scholar] [CrossRef]

- Chen, L.; Shao, S.; Xiao, Q.; Tarisciotti, L.; Wheeler, P.W.; Dragičević, T. Model Predictive Control for Dual-Active-Bridge Converters Supplying Pulsed Power Loads in Naval DC Micro-Grids. IEEE Trans. Power Electron. 2020, 35, 1957–1966. [Google Scholar] [CrossRef]

- Chen, L.; Gao, F.; Shen, K.; Wang, Z.; Tarisciotti, L.; Wheeler, P.; Dragičević, T. Predictive Control Based DC Microgrid Stabilization with the Dual Active Bridge Converter. IEEE Trans. Ind. Electron. 2020, 67, 8944–8956. [Google Scholar] [CrossRef]

- Yin, Z.; Deng, F.; Kaddah, S.S.; Ghanem, A.; Abulanwar, S.; Zhang, Y. Finite-Control-Set Model-Free Predictive Control Based on Voltage Noise Suppression for Dual Active Bridge Converters. J. Power Electron. 2025, 25, 1309–1319. [Google Scholar] [CrossRef]

- Kang, Z.; Li, Y. Active Disturbance Rejection Control of Full-Bridge DC–DC Converter for a Pulse Power Supply with Controllable Charging Time. Electronics 2023, 12, 5018. [Google Scholar] [CrossRef]

- Mosayebi, M.; Sadeghzadeh, S.M.; Gheisarnejad, M.; Khooban, M.H. Intelligent and Fast Model-Free Sliding Mode Control for Shipboard DC Microgrids. IEEE Trans. Transp. Electr. 2021, 7, 1662–1671. [Google Scholar] [CrossRef]

- Sami, I.; Alhosaini, W.; Khan, D.; Ahmed, E.M. Advancing Dual-Active-Bridge DC–DC Converters with a New Control Strategy Based on a Double Integral Super Twisting Sliding Mode Control. World Electr. Veh. J. 2024, 15, 348. [Google Scholar] [CrossRef]

- Guo, H.; Xiang, T.; Liu, Y.; Zhang, Q.; Liu, S.; Guan, B. Active Disturbance Rejection Control Method for Marine Permanent-Magnet Propulsion Motor Based on Improved ESO and Nonlinear Switching Function. J. Mar. Sci. Eng. 2023, 11, 1751. [Google Scholar] [CrossRef]

- Gao, Z. Active Disturbance Rejection Control: A Paradigm Shift in Feedback Control System Design. In Proceedings of the 2006 American Control Conference, Minneapolis, MN, USA, 14–16 June 2006. [Google Scholar] [CrossRef]

- Chen, W.; Yang, J.; Guo, L.; Li, S. Disturbance-Observer-Based Control and Related Methods—An Overview. IEEE Trans. Ind. Electron. 2016, 63, 1083–1095. [Google Scholar] [CrossRef]

- Łakomy, K.; Madonski, R.; Dai, B.; Yang, J.; Kicki, P.; Li, S. Active Disturbance Rejection Control Design with Suppression of Sensor Noise Effects in Application to DC–DC Buck Power Converter. IEEE Trans. Ind. Electron. 2021, 69, 816–824. [Google Scholar] [CrossRef]

- Guo, B.; Bacha, S.; Alamir, M.; Hably, A.; Boudinet, C. Generalized Integrator–Extended State Observer with Applications to Grid-Connected Converters in the Presence of Disturbances. IEEE Trans. Control Syst. Technol. 2021, 29, 744–755. [Google Scholar] [CrossRef]

- Wang, S.; Gan, H.; Luo, Y.; Luo, X.; Chen, Y. A Fractional-Order ADRC Architecture for a PMSM Position Servo System with Improved Disturbance Rejection. Fractal Fract. 2024, 8, 54. [Google Scholar] [CrossRef]

- Benrabah, A.; Xu, D.; Gao, Z. Active Disturbance Rejection Control of LCL-Filtered Grid-Connected Inverter Using Padé Approximation. IEEE Trans. Ind. Appl. 2018, 54, 6179–6189. [Google Scholar] [CrossRef]

- Krismer, F.; Kolar, J.W. Accurate Small-Signal Model for the Digital Control of an Automotive Bidirectional Dual Active Bridge. IEEE Trans. Power Electron. 2009, 24, 2756–2768. [Google Scholar] [CrossRef]

- Liu, G.; Liang, H.; Wang, R.; Sui, Z.; Sun, Q. Adaptive Event-Triggered Output Feedback Control for Nonlinear Multiagent Systems Using Output Information Only. IEEE Trans. Syst. Man Cybern. Syst. 2025, 55, 7639–7650. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license.