Non-Identical Inverter Rings as an Entropy Source: NIST-90B-Verified TRNG Architecture on FPGAs for IoT Device Integrity

Abstract

1. Introduction

- A non-identical entropy source was designed with ROs;

- Lightweight post-processing of the XOR corrector was used for the extraction of the randomness;

- The design consumed only 80 inverters to accomplish random number generation;

- The device’s independence from the proposed TRNG design was verified by implementing it on two different vendors of FPGAs, namely Intel and Xilinx-AMD.

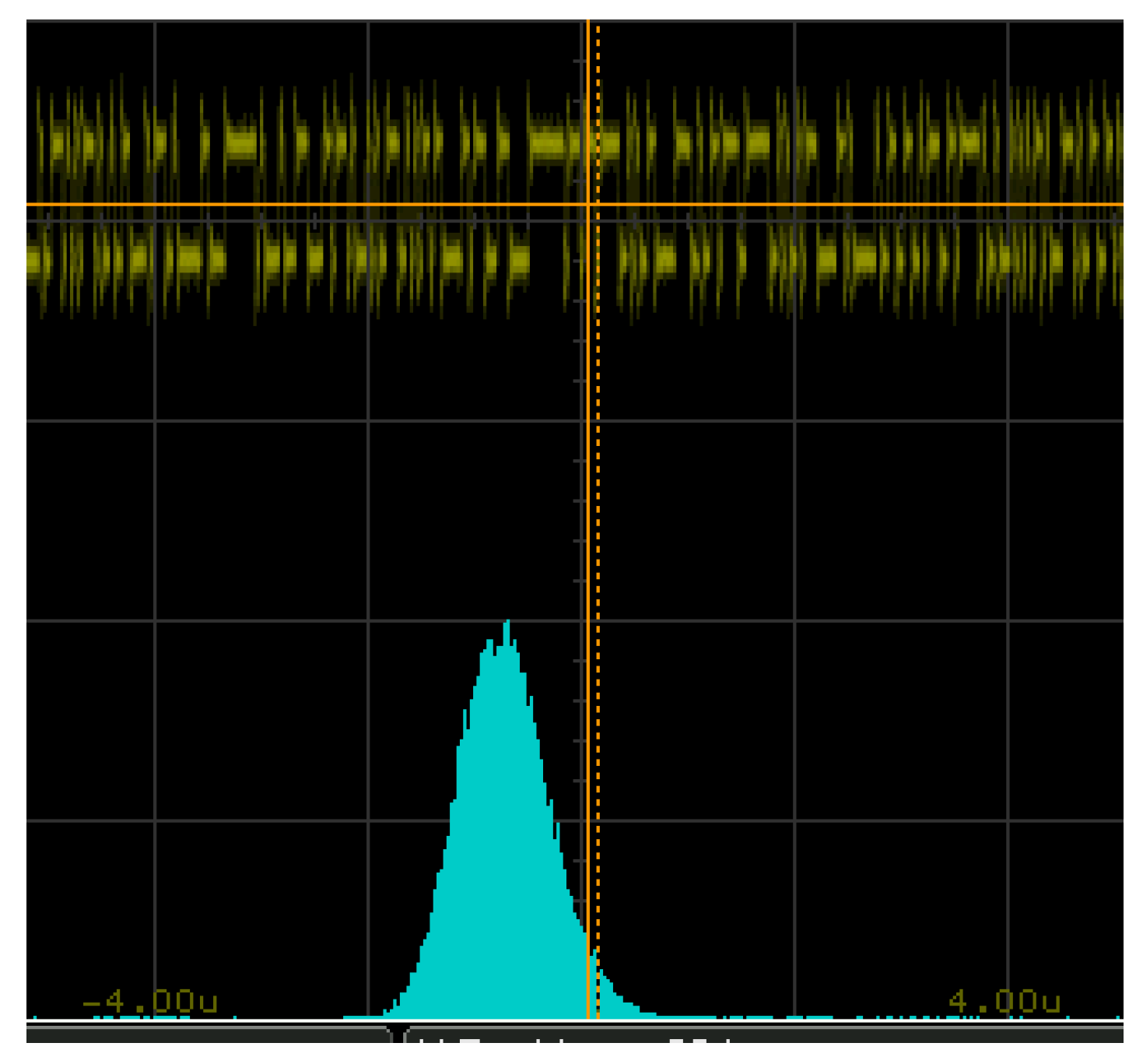

- Evidence of Gaussian jitter has been found through Keysight Logic Analyzer, and the standard deviation of the jitter is calculated as 24.010 ns;

- An equidistribution of 0.99999 is achieved without any post-processing;

- The TRNG design consumed only 15 LUTs and 13 registers to accommodate the TRNG on Intel FPGAs, which is <1% of its total hardware footprint;

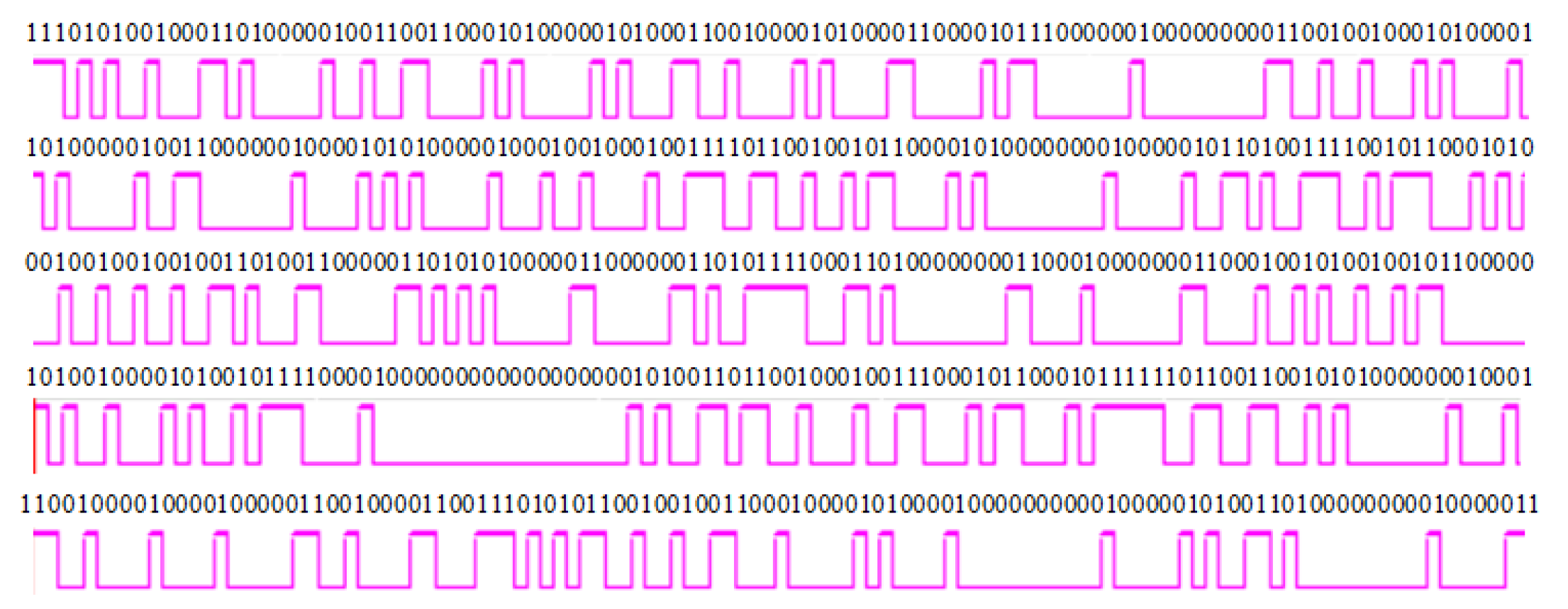

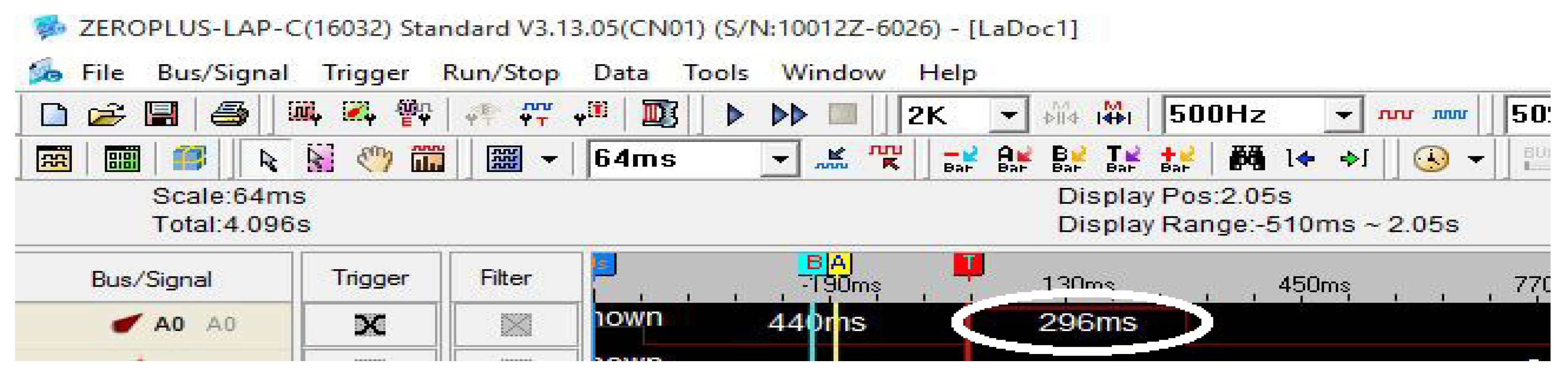

- 296 ms was taken for the TRNG to generate 10,48,576 bits with the 25 MHz of the sampling clock;

- Validation of the true randomness was carried out through batteries of NIST SP 800-90B and -22 tests;

- The proposed TRNG design does not require any post-processing mechanism to enhance the randomness.

2. Related Work

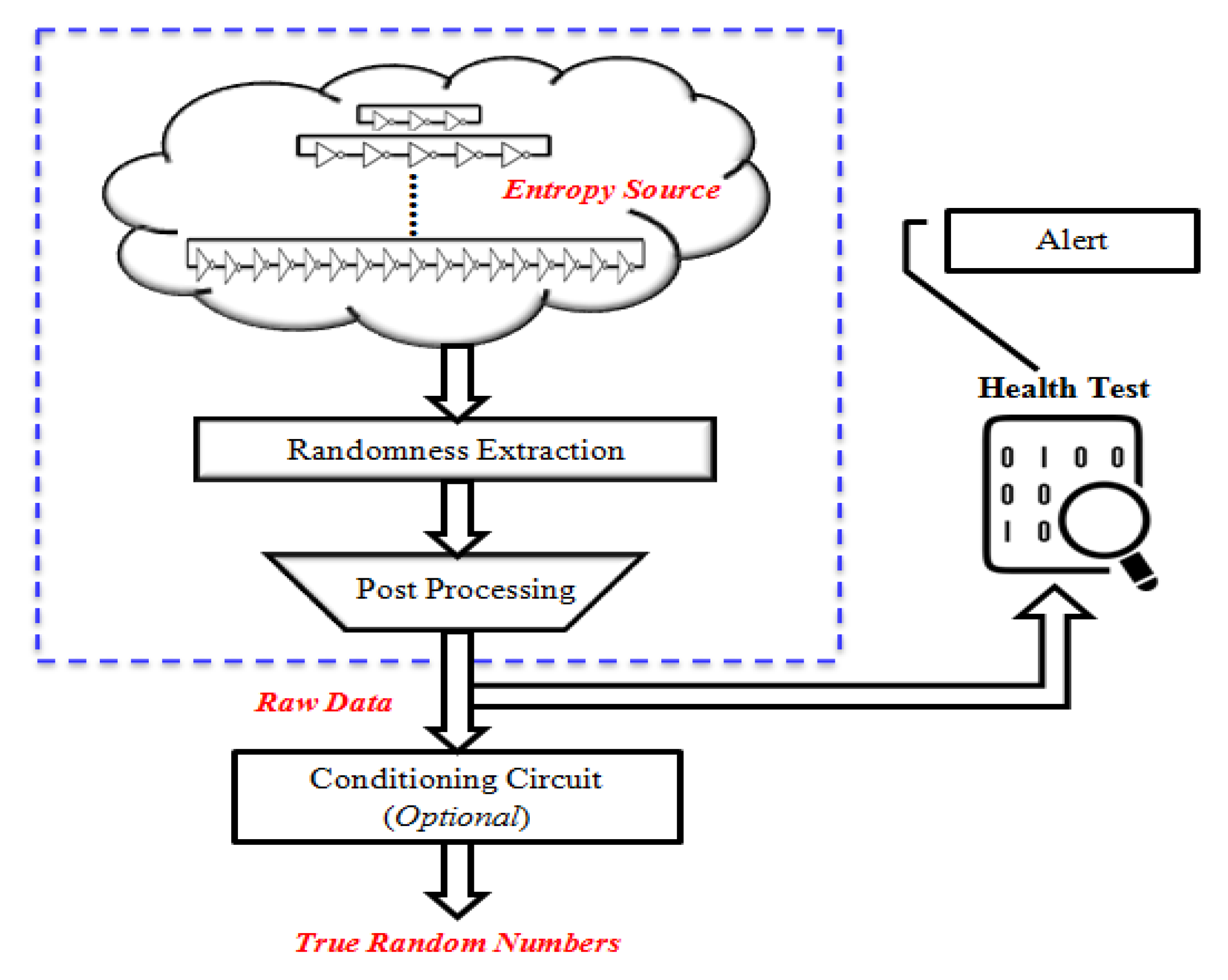

3. Proposed Architecture

3.1. Source of Entropy

= Dp + ΔdLpq + ΔdGpq

3.2. Extraction of Randomness

3.3. Post-Processing

4. Characterisation and Results

4.1. Evaluation of True Randomness

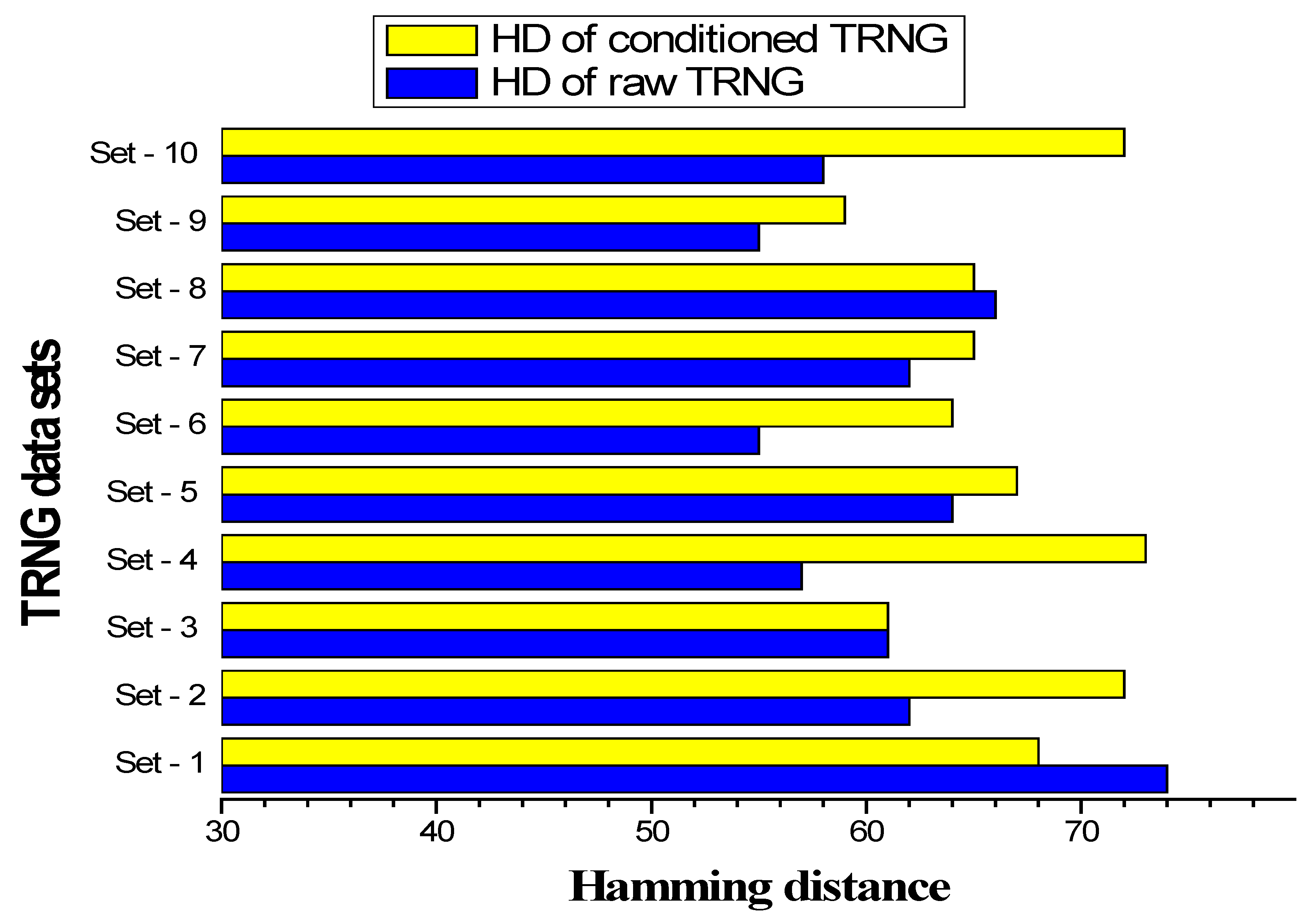

- (i)

- Restart experiment

- (ii)

- Calculation of the Hamming Distance (HD)

4.2. Evaluation of the Statistical Properties

- (i)

- It must have an equal distribution of 0 s and 1 s;

- (ii)

- It must be unpredictable;

- (iii)

- It should not produce any pattern.

- (i)

- Equidistribution analysis

- (ii)

- NIST 800-90B: min-entropy estimation

- (iii)

- NIST 800-22 batteries of tests

4.3. Evaluation of the Hardware Resources

- (a)

- Static probability: the expected state of the signal.

- (b)

- Transition rate: the number of transitions per unit of time. The transition rate is also referred to as the toggle rate.

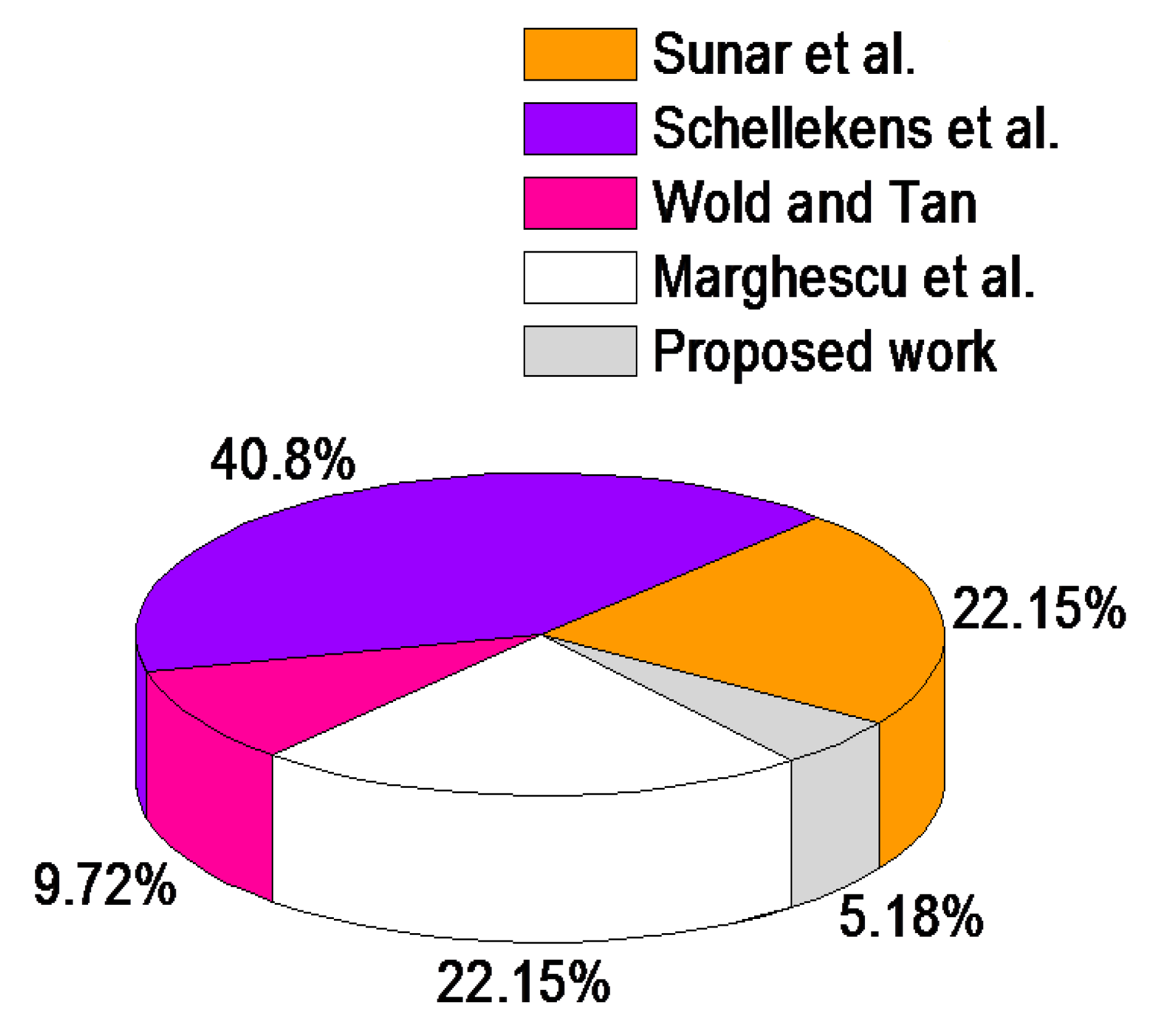

4.4. Performance Comparison

5. Conclusions

- Used as a session key generator in online transactions;

- Adopted as initialization vectors for rounds-based crypto-systems;

- Used as NONCE (Number Only Used Once) for mission-critical applications;

- Used as an integral part of the embedded devices for symmetric key generation;

- Used as a padding vector generator in encoding schemes;

- Used as a Physically Unclonable Function (PUF) with a slight hardware modification to verify the trustworthiness of the device in a network environment.

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Thangamani, N.; Murugappan, M. A Lightweight Cryptography Technique with Random Pattern Generation. Wirel. Pers. Commun. 2019, 104, 1409–1432. [Google Scholar] [CrossRef]

- Goswami, R.S.; Chakraborty, S.K.; Bhunia, A.; Bhunia, C.T. Generation of Automatic Variable Key under Various Approaches in Cryptography System. J. Inst. Eng. Ser. B 2013, 94, 215–220. [Google Scholar] [CrossRef]

- Perach, B.; Shahar, K. An Asynchronous and Low-Power True Random Number Generator Using STT-MTJ. IEEE Trans. Very Large Scale Integr. Syst. 2019, 27, 2473–2484. [Google Scholar] [CrossRef]

- Yao, Y.; Chen, X.; Kang, W.; Zhang, Y.; Zhao, W. Thermal Brownian Motion of Skyrmion for True Random Number Generation. IEEE Trans. Electron. Devices 2020, 67, 2553–2558. [Google Scholar] [CrossRef]

- Hsueh, J.-C.; Chen, V.H.-C. An ultra-low voltage chaos-based true random number generator for IoT applications. Microelectron. J. 2019, 87, 55–64. [Google Scholar] [CrossRef]

- Denis, T.S.; Johnson, S. Chapter 3—Random Number Generation, in Cryptography for Developers; Denis, T.S., Johnson, S., Eds.; Syngress: Burlington, VT, USA, 2007; pp. 91–137. [Google Scholar]

- Al-haija, Q.A.; Marouf, I.; Asad, M.M. A Double Stage Implementation for 1-K Pseudo RNG using LFSR and TRIVIUM. J. Comput. Sci. Control Syst. 2018, 11, 13–17. [Google Scholar]

- Al-Haija, Q.A.; Jebril, N.A. Implementing variable length Pseudo Random Number Generator (PRNG) with fixed high frequency (1.44 GHZ) via Vertix-7 FPGA family. In Proceedings of the 2014 International Conference on Network Security and Communication Engineering (NSCE 2014), Hong Kong, China, 25–26 December 2014. [Google Scholar]

- Garipcan, A.M.; Erdem, E. DESSB-TRNG: A novel true random number generator using data encryption standard substitution box as post-processing. Digit. Signal Process. 2022, 123, 103455. [Google Scholar] [CrossRef]

- Bakiri, M.; Guyeux, C.; Couchot, J.-F.; Oudjida, A.K. Survey on hardware implementation of random number generators on FPGA: Theory and experimental analyses. Comput. Sci. Rev. 2018, 27, 135–153. [Google Scholar] [CrossRef]

- Sönmez Turan, M.; Barker, E.; Kelsey, J.; Boyle, M.; Kerry, M.; Baish, M.L. Recommendation for the Entropy Sources Used for Random Bit Generation (Second DRAFT); NIST Special Publication 800-90B; NIST: Gaithersburg, MD, USA, 2016. [Google Scholar]

- Elbirt, A.J.; Yip, W.; Chetwynd, B.; Paar, C. An FPGA-based performance evaluation of the AES block cipher candidate algorithm finalists. IEEE Trans. Very Large Scale Integr. Syst. 2001, 9, 545–557. [Google Scholar] [CrossRef]

- Fischer, V.; Bernard, F. True Random Number Generators in FPGAs. In Security Trends for FPGAS: From Secured to Secure Reconfigurable Systems; Badrignans, B., Danger, J.L., Fischer, V., Gogniat, G., Torres, L., Eds.; Springer: Dordrecht, The Netherlands, 2011; pp. 101–135. [Google Scholar]

- Fischer, V.; Drutarovsky, M. True random number generator embedded in reconfigurable hardware. In Proceedings of the 4th International Workshop, Redwood Shores, CA, USA, 13–15 August 2003; pp. 415–430. [Google Scholar]

- Dejun, L.; Zhen, P. Research of True Random Number Generator Based on PLL at FPGA. Procedia Eng. 2012, 29, 2432–2437. [Google Scholar] [CrossRef]

- Johnson, A.P.; Chakraborty, R.S.; Mukhopadhyay, D. An Improved DCM-based Tunable True Random Number Generator for Xilinx FPGA. IEEE Trans. Circuits Syst. II Express Briefs 2016, 99, 1. [Google Scholar] [CrossRef]

- Kohlbrenner, P.; Gaj, K. An Embedded True Random Number Generator for FPGAs. In Proceedings of the 2004 ACM/SIGDA 12th International Symposium on Field Programmable Gate Arrays, Monterey, CA, USA, 22–24 February 2004; pp. 71–78. [Google Scholar]

- Sunar, B.; Martin, W.J.; Stinson, D.R. A Provably Secure True Random Number Generator with Built-In Tolerance to Active Attacks. IEEE Trans. Comput. 2007, 56, 109–119. [Google Scholar] [CrossRef]

- Schellekens, D.; Preneel, B.; Verbauwhede, I. FPGA vendor agnostic true random number generator. In Proceedings of the 2006 International Conference on Field Programmable Logic and Applications, Madrid, Spain, 28–30 August 2006; pp. 139–144. [Google Scholar]

- Jessa, M.; Matuszewski, L. Enhancing the randomness of a combined true random number generator based on the ring oscillator sampling method. In Proceedings of the 2011 International Conference on Reconfigurable Computing and FPGAs, Cancun, Mexico, 30 November–2 December 2011; pp. 274–279. [Google Scholar]

- Jessa, M.; Matuszewski, L. The use of delay lines in a ring-oscillator-based combined true random number generator. In Proceedings of the 2012 International Conference on Signals and Electronic Systems, Wroclaw, Poland, 18–21 September 2012. [Google Scholar]

- Loza, S.; Matuszewski, L. A true random number generator using ring oscillators and SHA-256 as post-processing. In Proceedings of the 2014 International Conference on Signals and Electronic Systems, Poznan, Poland, 11–13 September 2014; pp. 1–4. [Google Scholar]

- Wold, K.; Tan, C.H. Analysis and enhancement of random number generator in FPGA based on oscillator rings. In Proceedings of the 2008 International Conference on Reconfigurable Computing and FPGAs, Cancun, Mexico, 3–5 December 2008; Volume 2009, pp. 385–390. [Google Scholar]

- Fazili, M.M.; Shah, M.F.; Naz, S.F.; Shah, A.P. Next generation QCA technology based true random number generator for cryptographic applications. Microelectron. J. 2022, 126, 105502. [Google Scholar] [CrossRef]

- Morsali, M.; Moaiyeri, M.H.; Rajaei, R. A process variation resilient spintronic true random number generator for highly reliable hardware security applications. Microelectron. J. 2022, 129, 105606. [Google Scholar] [CrossRef]

- Saranya, M.; Revathy, M.; Kaleel Rahuman, A. Harvard architecture based post processed True random number generator. Mater. Today Proc. 2021, 47, 135–138. [Google Scholar] [CrossRef]

- Dong, S.; Wang, Y.; Xin, X.; Tong, X. A chaos-based true random number generator based on OTA sharing and non-flipped folded Bernoulli mapping for high-precision ADC calibration. Microelectron. J. 2021, 116, 105259. [Google Scholar] [CrossRef]

- Sen Teh, J.; Teng, W.; Samsudin, A.; Chen, J. A post-processing method for true random number generators based on hyperchaos with applications in audio-based generators. Front. Comput. Sci. 2020, 14, 146405. [Google Scholar] [CrossRef]

- Serrano, R.; Duran, C.; Hoang, T.; Sarmiento, M.; Nguyen, K.; Tsukamoto, A.; Suzaki, K.; Pham, C. A Fully Digital True Random Number Generator with Entropy Source Based in Frequency Collapse. IEEE Access 2021, 9, 105748–105755. [Google Scholar] [CrossRef]

- Valtchanov, B.; Fischer, V.; Aubert, A. Enhanced TRNG based on the coherent sampling. In Proceedings of the 2009 3rd International Conference on Signals, Circuits and Systems (SCS), Medenine, Tunisia, 6–8 November 2009. [Google Scholar]

- Marghescu, A.; Teseleanu, G.; Maimut, D.S.; Neacsa, T.; Svasta, P. Adapting a ring oscillator-based true random number generator for Zynq system on chip embedded platform. In Proceedings of the 2014 IEEE 20th International Symposium for Design and Technology in Electronic Packaging (SIITME), Bucharest, Romania, 23–26 October 2014; pp. 197–202. [Google Scholar]

- Wieczorek, P.Z. Dual-metastability FPGA-based true random number generator. Electron. Lett. 2013, 49, 744–745. [Google Scholar] [CrossRef]

- Tsai, K.; Huang, Y. AES-128 Based Secure Low Power Communication for LoRaWAN IoT Environments. IEEE Access 2018, 6, 45325–45334. [Google Scholar] [CrossRef]

- Dichtl, M.; Golić, J.D. High-Speed True Random Number Generation with Logic Gates Only. In Cryptographic Hardware and Embedded Systems CHES 2007; Springer: Berlin/Heidelberg, Germany, 2007; pp. 45–62. [Google Scholar]

- Pieterse, V.; Black, P. Hamming distance. In MATH32031: Coding Theory; 2001; p. 706. Available online: https://www.scribd.com/document/83172745/Parity-Check-Matrix# (accessed on 5 February 2023).

- Bassham, L.E.; Rukhin, A.; Soto, J.; Nechvatal, J.; Smid, M.; Leigh, S.; Levenson, M.; Heckert, N.; Banks, D. A Statistical Test Suite for Random and Pseudo-Random Number Generators for Cryptographic Applications; NIST: Gaithersburg, MD, USA, 2001. [Google Scholar]

- Bhatia, H.; Tretschk, E.; Theobalt, C.; Golyanik, V. Generation of Truly Random Numbers on a Quantum Annealer. IEEE Access 2022, 10, 3215500. [Google Scholar] [CrossRef]

- Sivaraman, R.; Rajagopalan, S.; Sridevi, A.; Rayappan, J.; Annamalai, M.; Rengarajan, A. Metastability-Induced TRNG Architecture on FPGA. Iran J. Sci. Technol. Trans. Electr. Eng. 2020, 44, 47–57. [Google Scholar] [CrossRef]

- Sivaraman, R.; Rajagopalan, S.; Rayappan, J.B.B.; Amirtharajan, R. Ring oscillator as confusion–diffusion agent: A complete TRNG drove image security. IET Image Process. 2020, 14, 2987–2997. [Google Scholar] [CrossRef]

- Sivaraman, R.; Rajagopalan, S.; Amirtharajan, R. FPGA based generic RO TRNG architecture for image confusion. Multimed Tools Appl. 2020, 79, 13841–13868. [Google Scholar] [CrossRef]

- Liu, H.; Kadir, A.; Xu, C. Cryptanalysis and constructing S-Box based on chaotic map and backtracking. Appl. Math. Comput. 2020, 376, 125153. [Google Scholar] [CrossRef]

- Altera, PowerPlay Early Power Estimator User Guide, May, 2015. Available online: https://www.manualsdir.com/models/altera/powerplay-early-power-estimator.html (accessed on 5 February 2023).

- Hassan, H.; Anis, M. Chapter 3—Power Estimation in FPGAs. In Low-Power Design of Nanometer FPGAs; Hassan, H., Anis, M., Eds.; Morgan Kaufmann: Boston, MA, USA, 2010; pp. 41–83. [Google Scholar]

- Hajji, B.; Mellit, A.; Bouselham, L. A Practical Guide for Simulation and FPGA Implementation of Digital Design; Springer: Berlin/Heidelberg, Germany, 2020. [Google Scholar]

| References | TRNG Source | Limitations |

|---|---|---|

| Refs. [14,15] | Phase Locked Loop | Device-dependent; synchronization of jitter clocks is difficult; low throughput |

| Ref. [17] | Identical Ring Oscillator | Frequencies were relatively the same; the placement of ROs plays an essential role in exploiting jitters; low throughput |

| Ref. [19] | Identical Ring Oscillator | Suffers from coupon collector problem; frequencies were relatively the same; low throughput |

| Ref. [21] | Identical Ring Oscillator + Carry4 Chain Logic | Device dependent; more rings of ring oscillators were used |

| Ref. [22] | Identical Ring Oscillator + SHA 256 | Consumes high volume hardware footprint |

| TRNG Datasets | Probability of Raw True Random Bits | Probability of Conditioned True Random Bits | ||||

|---|---|---|---|---|---|---|

| Ones | Zeros | Total | Ones | Zeros | Total | |

| Set 1 | 0.500702 | 0.4999298 | 0.999999 | 0.499504 | 0.500496 | 0.999999 |

| Set 2 | 0.499245 | 0.500755 | 0.999998 | 0.498688 | 0.501312 | 0.999995 |

| Set 3 | 0.501144 | 0.498856 | 0.999996 | 0.500626 | 0.499374 | 0.999999 |

| Set 4 | 0.498268 | 0.501732 | 0.999991 | 0.496803 | 0.503197 | 0.999971 |

| Set 5 | 0.500793 | 0.499207 | 0.999998 | 0.497917 | 0.502083 | 0.999987 |

| Set 6 | 0.500122 | 0.499878 | 1 | 0.499634 | 0.500366 | 1 |

| Set 7 | 0.504341 | 0.495659 | 0.999946 | 0.499069 | 0.500931 | 0.999998 |

| Set 8 | 0.499725 | 0.500275 | 1 | 0.500534 | 0.499466 | 0.999999 |

| Set 9 | 0.501877 | 0.498123 | 0.999999 | 0.499321 | 0.500679 | 0.999999 |

| Set 10 | 0.501282 | 0.498718 | 0.999995 | 0.499603 | 0.500397 | 1 |

| Estimation Methods | Theme of Estimation | Test Definition | |

|---|---|---|---|

| Entropic statistic estimates | Most common value | Number of occurrences | Works based on the frequency of the most common values in the dataset |

| Collision | Repeatability checking | Counts the number of successive samples until a duplicate is found | |

| Markov | Dependency checking | Finds the probability of samples in which the next sample depends on the latest observed sample’s value (first-order Markov model) | |

| Compression | Redundancy checking | Computes the redundancy rate of a dataset based on how much the dataset can be compressed | |

| Tuple estimates | T-Tuple | Pattern recognition | An extension of the most common value test. Examines the frequency of t–tuples (pairs, triples, etc.) in the input dataset |

| LRS | Longest run checking | T-tuples with a large size. It should not be ≥35 | |

| Predictor estimates | MultiMCW Prediction | Prediction of the next values from the observed values. It has sub-predictors | Includes a sliding window to record the t most recently observed samples. It predicts the subsequent output based on the most common value in the window. The window size should be 63, 255, 1023 or 4095 |

| Lag prediction | Detect the correlation and prediction value. | ||

| MultiMMC Prediction | Records the occurrences of transitions from a pattern with a fixed length to the subsequent output and predicts the most frequently observed transition from the current outputs | ||

| LZ78Y Prediction | Keeps a dictionary to record the tuples that have appeared in the previous outputs. It is based on the LZ78Y algorithm, and the dictionary has a fixed size of 65,536 | ||

| Estimation Methods | Sample 1 | Sample 2 | Sample 3 | Sample 4 | Sample 5 | |

|---|---|---|---|---|---|---|

| Entropic statistic estimates | Most common value | 0.776303 | 0.772829 | 0.774081 | 0.774165 | 0.773862 |

| Collision | 0.582513 | 0.576817 | 0.573787 | 0.575271 | 0.576649 | |

| Markov | 0.680329 | 0.677495 | 0.677831 | 0.678172 | 0.680321 | |

| Compression | 0.43252 | 0.428203 | 0.428726 | 0.429465 | 0.428224 | |

| Tuple estimates | T-tuple | 0.518165 | 0.503875 | 0.505944 | 0.507008 | 0.503875 |

| LRS | 0.60223 | 0.618924 | 0.610076 | 0.612304 | 0.609408 | |

| Predictor estimates | MultiMCW prediction | 0.776393 | 0.773231 | 0.774735 | 0.774728 | 0.77422 |

| Lag prediction | 0.646158 | 0.74279 | 0.74279 | 0.580808 | 0.72061 | |

| MultiMMC prediction | 0.599104 | 0.611752 | 0.610858 | 0.614122 | 0.611521 | |

| LZ78Y prediction | 0.776305 | 0.772844 | 0.774106 | 0.774192 | 0.773948 | |

| Estimation Methods | Sample 6 | Sample 7 | Sample 8 | Sample 9 | Sample 10 | |

| Entropic statistic estimates | Most common value | 0.773692 | 0.774377 | 0.77433 | 0.773578 | 0.773112 |

| Collision | 0.576271 | 0.578065 | 0.577006 | 0.572076 | 0.577741 | |

| Markov | 0.678259 | 0.678628 | 0.679594 | 0.676664 | 0.678986 | |

| Compression | 0.431527 | 0.430099 | 0.429395 | 0.427392 | 0.429304 | |

| Tuple estimates | T-tuple | 0.506473 | 0.499956 | 0.502869 | 0.503875 | 0.502373 |

| LRS | 0.617982 | 0.618924 | 0.595495 | 0.623257 | 0.598258 | |

| Predictor estimates | MultiMCW prediction | 0.774124 | 0.774787 | 0.774876 | 0.774023 | 0.773554 |

| Lag prediction | 0.74279 | 0.72061 | 0.699677 | 0.766341 | 0.766341 | |

| MultiMMC prediction | 0.612737 | 0.611371 | 0.614493 | 0.611618 | 0.611666 | |

| LZ78Y prediction | 0.773766 | 0.774414 | 0.77434 | 0.773596 | 0.773135 | |

| Estimation Methods | Sample 1 | Sample 2 | Sample 3 | Sample 4 | Sample 5 | |

|---|---|---|---|---|---|---|

| Entropic statistic estimates | Most common value | 0.774076 | 0.774325 | 0.774639 | 0.772213 | 0.77258 |

| Collision | 0.578074 | 0.574828 | 0.576665 | 0.574045 | 0.575295 | |

| Markov | 0.679357 | 0.678501 | 0.680025 | 0.677518 | 0.677673 | |

| Compression | 0.430194 | 0.427339 | 0.42911 | 0.430075 | 0.429719 | |

| Tuple estimates | T-tuple | 0.505419 | 0.507008 | 0.5049 | 0.505419 | 0.505419 |

| LRS | 0.625161 | 0.588358 | 0.607403 | 0.623526 | 0.585284 | |

| Predictor estimates | Multi MCW prediction | 0.774649 | 0.774807 | 0.775148 | 0.77265 | 0.773064 |

| Lag prediction | 0.766341 | 0.766341 | 0.580808 | 0.72061 | 0.72061 | |

| Multi MMC prediction | 0.613211 | 0.611999 | 0.612475 | 0.595327 | 0.612614 | |

| LZ78Y prediction | 0.774091 | 0.774363 | 0.774651 | 0.77224 | 0.772602 | |

| Estimation Methods | Sample 6 | Sample 7 | Sample 8 | Sample 9 | Sample 10 | |

| Entropic statistic estimates | Most common value | 0.774787 | 0.774039 | 0.773443 | 0.773995 | 0.77494 |

| Collision | 0.574717 | 0.575746 | 0.576025 | 0.576875 | 0.577158 | |

| Markov | 0.679194 | 0.679647 | 0.678308 | 0.678776 | 0.680344 | |

| Compression | 0.427999 | 0.428678 | 0.428281 | 0.428645 | 0.430835 | |

| Tuple estimates | T-tuple | 0.50337 | 0.501881 | 0.505419 | 0.504385 | 0.504385 |

| LRS | 0.622209 | 0.601729 | 0.589705 | 0.600017 | 0.622063 | |

| Predictor estimates | Multi MCW prediction | 0.775268 | 0.774444 | 0.773912 | 0.774496 | 0.775303 |

| Lag prediction | 0.813036 | 0.626573 | 0.679894 | 0.595327 | 0.766341 | |

| Multi MMC prediction | 0.61363 | 0.612777 | 0.614747 | 0.613002 | 0.614718 | |

| LZ78Y prediction | 0.774829 | 0.774054 | 0.773463 | 0.774002 | 0.77496 | |

| TRNG | Sample 1 | Sample 2 | Sample 3 | Sample 4 | Sample 5 |

|---|---|---|---|---|---|

| Raw bits | 0.43252 | 0.428203 | 0.428726 | 0.429465 | 0.428224 |

| Conditioned bits | 0.430194 | 0.427339 | 0.42911 | 0.430075 | 0.429719 |

| TRNG | Sample 6 | Sample 7 | Sample 8 | Sample 9 | Sample 10 |

| Raw bits | 0.431527 | 0.430099 | 0.429395 | 0.427392 | 0.429304 |

| Conditioned bits | 0.427999 | 0.428678 | 0.428281 | 0.428645 | 0.430835 |

| Test with Parameters | p-Value | Result | |

|---|---|---|---|

| Linear Complexity (N =1, n = 2, 56, 00, 000 bits, r = 0, s = 1) | Normal statistic | 0.89 | Pass |

| Chi2 statistics | 0.72 | ||

| Linear Complexity (N =1, n = 2, 56, 00, 000 bits, r = 29, s = 1) | Normal statistic | 0.9905 | Pass |

| Chi2 statistics | 0.18 | ||

| FPGA Vendor | Target FPGA | Consumption of Logic Elements |

|---|---|---|

| Intel (Altera) | Cyclone IV E (EP4CE115F29CN) | 15 LUTs and 13 registers |

| Cyclone II (EP2C35F672C6) | 15 LUTs and 13 registers | |

| Stratix III (EP3SL340H1152C3) | 14 LUTs and 13 registers | |

| Xilinx | Artix-7 (7a100tcsg324-3) | 10 LUTs and 13 registers |

| ZYNQ 7000 (7z020clg484-1) | 10 LUTs and 13 registers |

| Static Power (mW) | 98.49 |

|---|---|

| Dynamic Power (mW) | 1.28 |

| IO Power (mW) | 41.09 |

| Total Power (mW) | 140.86 |

| Reference | TRNG Design Technique | FPGA for Implementation | Hardware Resources | Frequency | Throughput |

|---|---|---|---|---|---|

| Fischer et al. [14] | PLL/DLL | Altera APEX EP20K200EFC484-2X | 121 LCs, 4 ESB and 1 PLL | 33.3 MHz | 69 Kbps |

| Kohlbrenner and Gaj [17] | Free-running oscillator | Xilinx XC2VP30 | 12LUTs and 24 registers | 150 MHz | 300 Kbps |

| Valchanov et al. [30] | RO–RO | Xilinx XC3S500E | 15 LUTs, 4 registers | 2 Mbps | |

| RO–PLL | 12 LUTs, 4 registers and 1 PLL | 65 MHz | 2 Mbps | ||

| RO–DFS | 11 LUTs, 6 registers and 2 DFS | 2 Mbps | |||

| Schellekens et al. [19] | Free-running oscillator | Xilinx XC2VP30 | 973 Slices | 40 MHz | 2.5 Mbps |

| Proposed | Non-identical ROs | Cyclone IV E EP4CE115F29CN | 15 LUTs and 13 registers | 25 MHz | 3.5 Mbps |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Mahalingam, H.; Rethinam, S.; Janakiraman, S.; Rengarajan, A. Non-Identical Inverter Rings as an Entropy Source: NIST-90B-Verified TRNG Architecture on FPGAs for IoT Device Integrity. Mathematics 2023, 11, 1049. https://doi.org/10.3390/math11041049

Mahalingam H, Rethinam S, Janakiraman S, Rengarajan A. Non-Identical Inverter Rings as an Entropy Source: NIST-90B-Verified TRNG Architecture on FPGAs for IoT Device Integrity. Mathematics. 2023; 11(4):1049. https://doi.org/10.3390/math11041049

Chicago/Turabian StyleMahalingam, Hemalatha, Sivaraman Rethinam, Siva Janakiraman, and Amirtharajan Rengarajan. 2023. "Non-Identical Inverter Rings as an Entropy Source: NIST-90B-Verified TRNG Architecture on FPGAs for IoT Device Integrity" Mathematics 11, no. 4: 1049. https://doi.org/10.3390/math11041049

APA StyleMahalingam, H., Rethinam, S., Janakiraman, S., & Rengarajan, A. (2023). Non-Identical Inverter Rings as an Entropy Source: NIST-90B-Verified TRNG Architecture on FPGAs for IoT Device Integrity. Mathematics, 11(4), 1049. https://doi.org/10.3390/math11041049