Abstract

Discrete orthogonal transforms such as the discrete Fourier transform, discrete cosine transform, discrete Hartley transform, etc., are important tools in numerical analysis, signal processing, and statistical methods. The successful application of transform techniques relies on the existence of efficient fast algorithms for their implementation. A special place in the list of transformations is occupied by the discrete fractional Fourier transform (DFrFT). In this paper, some parallel algorithms and processing unit structures for fast DFrFT implementation are proposed. The approach is based on the resourceful factorization of DFrFT matrices. Some parallel algorithms and processing unit structures for small size DFrFTs such as N = 2, 3, 4, 5, 6, and 7 are presented. In each case, we describe only the most important part of the structures of the processing units, neglecting the description of the auxiliary units and the control circuits.

1. Introduction

Traditional discrete orthogonal transforms such as the discrete Fourier transform (DFT), discrete cosine transform (DCT), the discrete Hartley transform (DHT), discrete Walsh–Hadamard transform (DWHT), discrete Haar transform (DHT), and the Slant transform (ST) are important tools in signal and image processing, numerical analysis, and statistical methods. Discrete fractional transforms are another important type of discrete orthogonal transformation. Discrete fractional transforms are the generalizations of the ordinary discrete transforms with one additional fractional parameter. Various discrete fractional transforms including the discrete Fourier transform [1,2,3], the discrete fractional Hartley transform [4], and the discrete fractional cosine and sine transforms [5] have been introduced and found wide applications in many scientific and technological areas including digital signal processing [4], image encryption [6,7,8], digital watermarking [9], and others. Different fast algorithms for their implementation have been separately developed to minimize computational complexity and implementation costs. A striking example is the discrete fractional Fourier transform (DFrFT), the discrete version of the integral fractional Fourier transform (FrFT). Besides its numerical side appropriateness, the DFrFT has proven over the years to be a powerful signal processing tool.

Today, there are many types of definitions of DFrFT. A first approach is represented by direct sampling of the FrFT [10]. It is the least complicated approach, and there are a few different algorithms that have been developed for computing this type of DFrFT. But these discrete realizations could lose many important properties of the FrFT like unitarity, reversibility, additivity; therefore, its applications are limited. A second approach relies on a linear combination of ordinary Fourier operators raised to different powers [11,12]. However, as emphasized in [3], these realizations often produce an output that does not match the output of the continuous FrFT. In other words, it is not the discrete version of the continuous transform. The third approach is based on the idea of an eigenvalue decomposition [1,2,3].

A decisive factor for applications of the various types of DFrFT has been the existence of fast algorithms for computing it. However, only DFrFT based on the eigenvalue decomposition [1,2,3] has all the properties which are required for DFrFT such as unitarity, additivity, reduction to discrete Fourier transform when the power is equal to 1, an approximation of the continuous FrFT [3]. We will call this type of DFrFT as “true” [13]. Fast algorithms for this type of transformation were described in papers [5,14]. The limited volume of these publications did not allow the presentation of all the details of the organization of the calculations for the specific lengths of the original data sequences. In particular, the fast algorithms and schemes for discrete orthogonal transformations for short lengths of input sequences are of practical interest. For example, in [15] the fast algorithms for small-size DFTs were presented. In [16], some schemes for small-size DHTs are given. In the case of DFrFT, such algorithms are not given anywhere. We want to eliminate this shortcoming. To this end, we present fast algorithms and processing unit structures to compute a true DFrFT for N = 2, 3, 4, 5, 6, and 7.

2. Preliminary Remarks

The definition of true DFrFT was first introduced by Pei and Yeh [1,2]. They defined the DFrFT in terms of a particular set of eigenvectors, which constitute the discrete counterpart of the set of Hermite–Gaussian functions (these functions are well-known eigenfunctions of DFT, and the fractional Fourier transform was defined through a spectral expansion in this base [3]):

where —is discrete fractional Fourier transform matrix, , and —are input and output data vectors, respectively, and is a fractional parameter (real number).

The fractional power of the matrix, including the DFT matrix, can be obtained from its eigenvalue decomposition and the power of eigenvalues:

where is the diagonal matrix of size N, whose diagonal entries are powers of eigenvalues of the DFT matrix with an exponent α, while is the matrix whose columns are normalized mutually orthogonal eigenvectors of the DFT matrix.

It is easy to check that the DFrFT matrix, calculated from (2), is symmetric [14]. Moreover the first row (and column) of the matrix is an even vector and a matrix which we obtain after removing the first row and the first column from the matrix is persymmetric [14]. Based on that general considerations, we can describe the entries of the DFrFT matrix in the following way:

The entries of this matrix are complex numbers, and their values depend on both the fractional parameter and the number N. However, it will be more convenient for us to denote the numerical values of the matrix entries by means of the letters of the ordinary Latin alphabet . In this case, the subscript N will indicate the size of the DFrFT matrix, while the superscript α will indicate the value of the fractional parameter. This will simplify the identification of the structural features of the matrix and the presence in it of compositions of the same values of the entries.

3. Algorithm and Processing Unit Structure for Small Size DFrFTs

3.1. Computing the Two-Point DFrFT

Let and be two-dimensional input and output data vectors, respectively.

The problem is to calculate a product

where

Direct computation of (4) takes four multiplications and two additions of complex numbers. From the symmetry of the DFrFT matrix follows that for any value of the parameter , the matrix contains the same elements on the secondary diagonal. Therefore [17], the number of multiplications in the calculation of the two-point DFrFT can be reduced.

With this in mind, the rationalized computational procedure for computing the two-point DFrFT has the following form:

where

and

As can be seen, the implementation of the two-point DFrFT requires only three multipliers and three two-input adders of complex numbers.

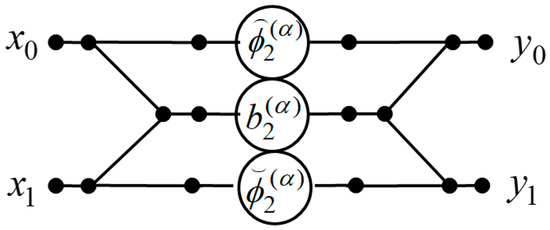

Figure 1 shows a data flow structure for the implementation of the two-point DFrFT. In this paper, data flow structures are oriented from left to right. Straight lines in the figures denote the operations of data transfer. The circles in these figures indicate complex-valued multipliers. These blocks multiply the input data by the numbers inscribed inside the circles. Points where lines converge denote summation and dotted lines indicate the sign-change operations. We use the usual lines without arrows on purpose, so as not to clutter the picture.

Figure 1.

The data flow structure of the proposed algorithm for the computation of the two-point DFrFT.

3.2. Computing the Three-Point DFrFT

Let and be three-dimensional input and output data vectors, respectively.

The three-point DFrFT can be represented in the following form:

where

Taking into account the specific structure of the matrix we can propose the following procedure for the efficient calculation of a three-point DFrFT:

where

and is an identity matrix, is the (2 × 2) Hadamard matrix, and the sign denotes the direct sum of two matrices [18].

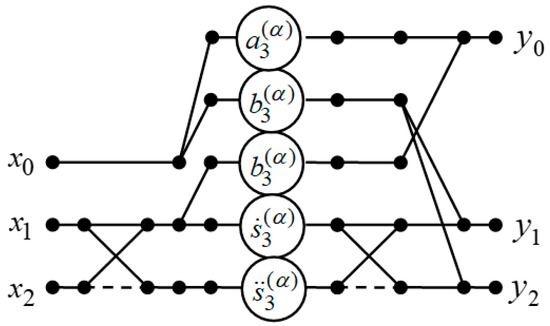

Figure 2 shows a data flow structure for the implementation of 3-point DFrFT. It is easy to see that the computation of requires only five multipliers and seven two-input adders of complex numbers.

Figure 2.

The data flow structure of the proposed algorithm for the computation of the three-point DFrFT.

3.3. Computing the Four-Point DFrFT

Let and be four-dimensional input and output data vectors, respectively.

The four-point DFrFT can be represented in the following form:

where

Taking into account the specific structure of the matrix , we can propose the following procedure for the efficient calculation of a four-point DFrFT:

where

where is an matrix of ones (a matrix in which every entry is equal to one).

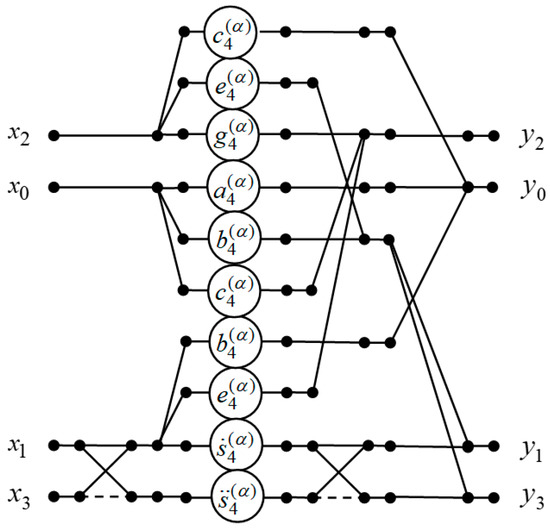

Figure 3 shows a data flow structure for the implementation of a four-point DFrFT. It is easy to see that the computation of requires only 10 multipliers, seven two-input adders, and two three-inputs adders of complex numbers.

Figure 3.

The data flow structure of the processing unit for the computation of the four-point DFrFT.

3.4. Computing the Five-Point DFrFT

Let and be five-dimensional input and output data vectors, respectively.

The five-point DFrFT can be represented in the following form:

where

Taking into account the specific structure of the matrix , we can propose the following procedure for the efficient calculation of a five-point DFrFT:

where

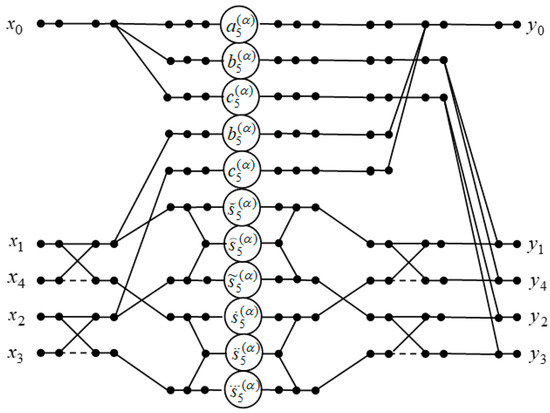

Figure 4 shows a data flow structure for the implementation of 5-point DFrFT. It is easy to see that the computation of requires only 11 multipliers, 18 two-input adders, and 1 three-input adder of complex numbers.

Figure 4.

The data flow structure of the processing unit for computation of 5-point DFrFT.

3.5. Computing the 6-Point DFrFT

Let and be six-dimensional input and output data vectors, respectively.

The 6-point DFrFT can be represented in the following form:

where

Taking into account the specific structure of the matrix , we can propose the following procedure for the efficient calculation of a 6-point DFrFT:

where

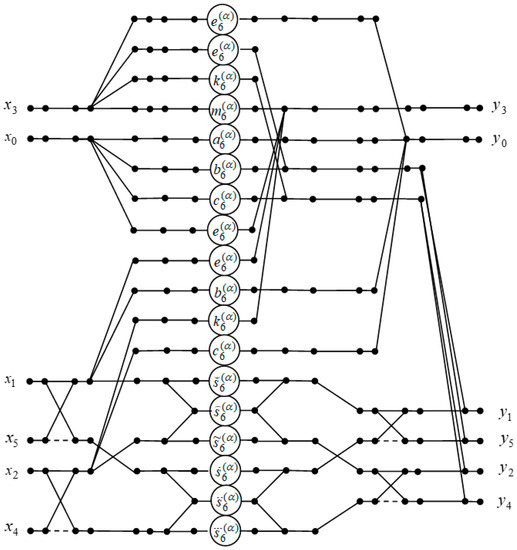

Figure 5 shows a data flow structure for the implementation of the six-point DFrFT. It is easy to see that the computation of requires only 18 multipliers, 20 two-input adders, and two four-input adders of complex numbers.

Figure 5.

The data flow structure of the processing unit for the computation of the six-point DFrFT.

3.6. Computing th eSeven-Point DFrFT

Let and be seven-dimensional input and output data vectors, respectively.

The seven-point DFrFT can be represented in the following form:

where

Taking into account the specific structure of the matrix , we can propose the following procedure for the efficient calculation of a seven-point DFrFT:

where

The sign denotes the Kronecker product of two matrices [18].

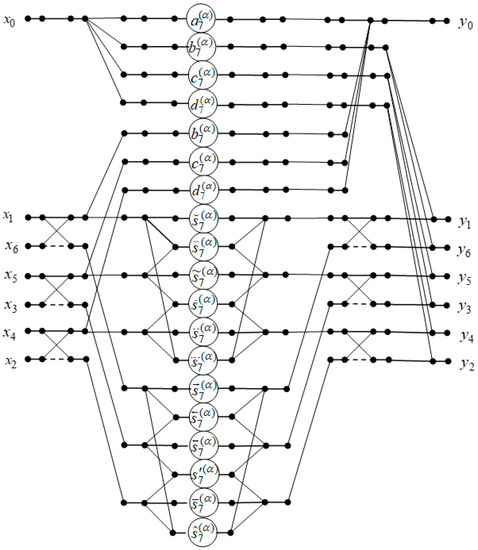

Figure 6 shows a data flow structure for the implementation of the seven-point DFrFT. It is easy to see that the computation of requires only 19 multipliers and 24 two-input adders, six three-input adders, and one four-input adder of complex numbers.

Figure 6.

The data flow structure of the processing unit for the computation of the seven-point DFrFT.

4. Implementation Complexity

Since the lengths of the input sequences are relatively small, and the data flow structures representing the organization of the computation process are fairly simple, it is easy to estimate the computational complexity of the implementation of the presented solutions. Table 1 shows evaluations of the number of arithmetic blocks for the small-size DFrFTs hardware implementations.

Table 1.

Implementation complexities of naive and proposed solutions.

5. Discussion

This paper presents some algorithms and parallel processing unit structures for small-size DFrFTs with a minimalized number of complex-valued multiplications (or complex multipliers in the case of a hardware implementation). Special attention is mainly focused on these operations because from the point of view of the hardware implementation complexity; these operations are the most expensive. This is because the complexity of implementing an adder depends linearly on the size of the operand, and the complexity of implementing a multiplier depends quadratically on the size of the operand. A binary multiplier occupies much more space and consumes much more power than a binary adder. Therefore, a processing unit structure containing as few multipliers as possible, even by the cost of a small increase in the number of adders, is preferable from the point of view of the application-specific integrated circuit (ASIC) design. The developed algorithms can be used as building blocks in more complex DSP algorithms. In the case of a hardware implementation of complex signal processing systems, the developed structures can be used as embedded hardware-implemented processing cores. Hopefully, these can be used as building blocks to reduce the hardware complexity of the DSP systems that use them, thus making more complicated structural solutions worthy of consideration in practice.

In our next articles, we plan to show how and for what purposes we use the solutions proposed here.

Author Contributions

Conceptualization—A.C. and J.P.; Methodology—A.C. and J.P.; validation, D.M.-M. and J.P.; Formal analysis—A.C. and D.M.-M.; Writing and original draft preparation—A.C.; Writing, review, and editing—D.M.-M.; Visualization—A.C. and J.P.; Supervision—D.M.-M. and A.C.

Funding

This research received no external funding.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Pei, S.-C.; Yeh, M.-H. Improved discrete fractional Fourier transform. Opt. Lett. 1997, 22, 1047–1049. [Google Scholar] [CrossRef] [PubMed]

- Pei, S.-C.; Yeh, M.-H.; Tseng, C.-C. Discrete fractional Fourier transform based on orthogonal projections. IEEE Trans. Signal Process. 1999, 47, 1335–1348. [Google Scholar] [CrossRef]

- Candan, Ç.C.; Kutay, M.A.; Ozaktas, H.M. The discrete fractional Fourier transform. IEEE Trans. Signal Process. 2000, 48, 1329–1337. [Google Scholar] [CrossRef]

- Pei, S.-C.; Tseng, C.-C.; Yeh, M.-H.; Shyu, J.-J. Discrete fractional Hartley and Fourier transforms. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 1998, 45, 665–675. [Google Scholar] [CrossRef]

- Pei, S.-C.; Yeh, M.H. The discrete fractional cosine and sine transforms. IEEE Trans. Signal Process. 2001, 49, 1198–1207. [Google Scholar] [CrossRef]

- Hennelly, B.; Sheridan, J.T. Fractional Fourier transform-based image encryption: Phase retrieval algorithm. Opt. Commun. 2003, 226, 61–80. [Google Scholar] [CrossRef]

- Liu, S.; Mi, Q.; Zhu, B. Optical image encryption with multistage and multichannel fractional Fourier-domain filtering. Opt. Lett. 2001, 26, 1242–1244. [Google Scholar] [CrossRef] [PubMed]

- Nishchal, N.K.; Joseph, J.; Singh, K. Fully phase encryption using fractional Fourier transform. Opt. Eng. 2003, 42, 1583–1588. [Google Scholar] [CrossRef]

- Djurović, I.; Stanković, S.; Pitas, I. Digital watermarking in the fractional Fourier transformation domain. J. Netw. Comput. Appl. 2001, 24, 167–173. [Google Scholar] [CrossRef]

- Ozaktas, H.M.; Ankan, O.; Kutay, M.A.; Bozdagi, G. Digital computation of the fractional Fourier transform. IEEE Trans. Signal Process. 1996, 44, 2141–2150. [Google Scholar] [CrossRef]

- Santhanam, B.; McClellan, J.H. Discrete rotational Fourier transform. IEEE Trans. Signal Process. 1996, 44, 994–998. [Google Scholar] [CrossRef]

- Dickinson, B.W.; Steiglitz, K. Eigenvectors and functions of the discrete Fourier transform. IEEE Trans. Acoust. Speech Signal Process. 1982, 30, 25–31. [Google Scholar] [CrossRef]

- Majorkowska–Mech, D.; Cariow, A. An Algorithm for Computing the True Discrete Fractional Fourier Transform. In Advances in Soft and Hard Computing; Pejaś, J., El Fray, I., Hyla, T., Kacprzyk, J., Eds.; Springer: Cham, Switzerland, 2019; Volume 889, pp. 420–432. [Google Scholar] [CrossRef]

- Majorkowska–Mech, D.; Cariow, A. A low-complexity approach to computation of the discrete fractional Fourier transform. Circuits Syst. Signal Process. 2017, 36, 4118–4144. [Google Scholar] [CrossRef][Green Version]

- Qureshi, F.; Garrido, M.; Gustafsson, O. Unified architecture for 2, 3, 4, 5, and 7-point DFTs based on Winograd Fourier transform algorithm. Electron. Lett. 2013, 49, 348–349. [Google Scholar] [CrossRef]

- De Oliveira, H.M.; Cintra, R.J.; Campello de Souza, R.M. A Factorization Scheme for Some Discrete Hartley Transform Matrices. arXiv 2015, arXiv:1502.01038, 1–10. [Google Scholar]

- Cariow, A. Strategies for the Synthesis of Fast Algorithms for the Computation of the Matrix-vector Products. J. Signal Process. Theory Appl. 2014, 3, 1–19. [Google Scholar] [CrossRef]

- Graham, A. Kronecker Products and Matrix Calculus: With Applications; Ellis Horwood Limited: Chichester, UK, 1981. [Google Scholar]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).