1. Introduction

Low-dropout regulators (LDOs), serving as critical power management units, are designed to provide a stable and clean output voltage despite variations in input voltage and load current. Their ability to operate with a very small input–output voltage differential makes them particularly suitable for battery-powered and noise-sensitive applications [

1,

2,

3,

4,

5,

6,

7,

8,

9]. In recent years, with the continuous scaling of CMOS technology and the increasing complexity of system-on-chip (SoC) designs, the performance requirements for LDOs, including transient response, quiescent current, and area efficiency, have become increasingly stringent.

The application of LDOs in aerospace electronic systems is of paramount importance. These systems demand extremely high reliability and robustness due to the harsh operating conditions of space. Spacecraft electronics are constantly exposed to intense radiation, which can induce various single-event effects (SEE) [

10,

11,

12,

13]. When high-energy particles, such as heavy ions or protons, strike a semiconductor device, they generate a dense track of electron–hole pairs through ionization. Under the influence of internal electric fields, these charge carriers are rapidly collected by circuit nodes, resulting in transient current pulses. These pulses can cause temporary upsets, known as single-event transients (SETs), or even permanent damage, such as latch-up or burnout, potentially leading to system-level functional interruptions or failures. For an LDO, a single-event strike on its sensitive nodes such as the pass gate, error amplifier, or feedback network, which can cause a temporary dropout or spike in the output voltage. If this disturbed voltage exceeds the tolerance range of the powered load circuits, it may trigger logic errors or operational faults in digital cores, analog-to-digital converters, or other critical subsystems. Consequently, investigating the single-event susceptibility and hardening techniques for LDOs is indispensable for ensuring the integrity and continuous operation of spacecraft power systems.

Currently, LDO architectures can be broadly categorized into three types: analog LDOs (A-LDOs), digital LDOs (D-LDOs), and hybrid analog-digital LDOs (H-LDOs), as illustrated in

Figure 1. Analog LDOs, the most traditional and widely used architecture, employ a high-gain error amplifier in a continuous-time feedback loop to compare the scaled output voltage with a precise reference voltage. The amplified error signal then drives the gate of the power transistor, thereby regulating the output voltage. This architecture offers several advantages, including high accuracy, excellent transient response, and superior power-supply rejection (PSR) [

14,

15,

16]. However, its primary drawback lies in its relatively low power conversion efficiency, especially at light loads, due to the necessity of maintaining a sufficiently large bias current for the error amplifier to ensure stability and speed. In contrast, digital LDOs represent a more recent development leveraging advanced CMOS nodes. They replace the continuous-time analog amplifier with a voltage comparator and a digital control loop, typically comprising a clocked sampler and a shift register or other digital logic that dynamically switches an array of power MOSFETs [

17]. This architecture eliminates the need for large on-chip compensation capacitors, reduces quiescent current, and achieves high power efficiency, particularly in deep sub-micron processes. Nevertheless, D-LDOs often suffer from inherent limit-cycle oscillations, resulting in larger output voltage ripple, slower transient response due to discrete-time operation, and degraded PSR. To harness the benefits of both paradigms while mitigating their respective limitations, hybrid LDOs have emerged. These designs typically incorporate a dual-loop or multi-loop control strategy, combining a fast analog auxiliary loop for rapid transient suppression with a digitally controlled main loop for high-efficiency regulation under steady-state conditions [

18,

19]. This synergistic approach aims to deliver robust performance across a wide range of operating conditions.

In this paper, a comprehensive investigation into the single-event response characteristics of analog, digital, and hybrid LDOs is conducted. Based on an advanced 28-nm CMOS process, a novel hybrid analog-digital LDO is proposed and designed. All three LDOs are implemented in the same 28-nm technology node, ensuring a fair and controlled comparison of their SET susceptibility under identical simulation conditions. Through detailed circuit simulations, the proposed H-LDO demonstrates a significant enhancement in tolerance to single-event effects compared to its analog and digital counterparts. The key innovation lies in its multi-loop architecture, which not only ensures high efficiency and fast transient response but also incorporates specific mechanisms to quickly recover from radiation-induced voltage disturbances. The remainder of this paper is structured as follows:

Section 2 provides a detailed introduction to the circuit architectures and operating principles of the three types of LDOs, with particular emphasis on the multi-loop design of the proposed hybrid LDO.

Section 3 presents and discusses the simulation results, including performance benchmarks under normal conditions and a detailed analysis of single-event transient responses under both light- and heavy-load scenarios. Finally,

Section 4 summarizes the key findings and concludes the paper.

2. Design of LDOs

This section elaborates on the detailed circuit implementations and design considerations for the three LDO topologies under study. All designs are performed in a 28-nm CMOS process. The designs are optimized to deliver a maximum output current () of 200 mA.

2.1. Design of the Analog LDO

The analog LDO in this work is based on the Flipped Voltage Follower (FVF) architecture, renowned for its inherent local feedback that enhances slew-rate and bandwidth. As shown in the analog section of

Figure 2, the core FVF loop is formed by the power transistor MPA and the common-gate transistor M1. This structure establishes a low-impedance node at the source of M1 (which is the gate of MPA), creating a very fast local feedback path that significantly boosts the circuit’s dynamic response to load current changes. A key advantage of the FVF is its low voltage headroom requirement—approximately

or

—enabling operation at low supply voltages, which is crucial for modern low-power systems.

To further improve performance, particularly in suppressing output voltage overshoot during load release events, an active compensation network consisting of capacitor C1 and transistor M10 is incorporated. Under steady-state conditions, M10 is biased in the subthreshold region, drawing negligible current and thus minimizing its impact on the overall quiescent current (). However, during a rapid reduction in load current that causes VOUT to rise, the high-frequency components of this voltage spike are coupled directly to the gate of M10 via C1. This momentarily pushes M10 into a stronger conduction region, allowing it to sink a significant instantaneous current from the output node, thereby effectively damping the overshoot.

A deeper analysis reveals that the implemented A-LDO operates through three distinct but interacting control loops, which will be analyzed in detail in the context of the hybrid LDO in

Section 2.3, as the core analog structure is shared. These loops work in concert to ensure stability, accuracy, and speed.

Identifying sensitive nodes is crucial for assessing Single-Event Transient (SET) susceptibility. For the A-LDO, the most sensitive node is the high-impedance output of the error amplifier (the gate of MPA). A charge deposition at this node directly modulates the gate voltage of the power transistor, causing a large output voltage glitch. The recovery is slow, governed by the bandwidth-limited analog feedback loop.

2.2. Design of the Digital LDO

The digital LDO, whose core digital control block is depicted in

Figure 2, adopts a segmented power transistor array architecture to achieve a balance between current drive resolution and dynamic range. The power switch array is divided into three groups with different bit weights: Low (L), Medium (M), and High (H). Specifically, the M and H groups each consist of 8 identical unit power transistors, while the L group comprises 64 much smaller unit transistors. This hierarchical segmentation allows the D-LDO to make large current adjustments swiftly when needed while maintaining fine control for low ripple under steady-state conditions.

The control mechanism operates in two primary modes: coarse adjustment and fine adjustment. The coarse adjustment loop is activated when the output voltage, VOUT, deviates beyond a predefined “dead zone” window. This is detected by two window comparators (CMP2 and CMP3 in the hybrid schematic,

Figure 2). When triggered, the M and H groups are enabled, injecting or sinking a substantial current (equivalent to 8 times the current of a single L-unit step) to bring VOUT back into the target range rapidly. Once VOUT is within the dead zone, the coarse loop is disabled, and the fine adjustment loop takes over. The fine loop is governed by a single comparator (CMP1) and a digital controller (a shift register, SR) that incrementally adjusts the number of enabled L-group units. This discrete-time, clocked operation minimizes the steady-state output voltage ripple, especially under light-load conditions, albeit at the cost of inherent limit-cycle oscillations.

In the D-LDO, sensitive nodes include the comparator output and the shift register control logic. An SET-induced glitch at these nodes can cause a temporary erroneous code, leading to a discrete output voltage step. However, the sampled-data nature of the digital control loop provides inherent resilience, as the error is typically corrected in subsequent clock cycles, leading to a relatively fast recovery.

2.3. Design of the Hybrid LDO

The proposed hybrid LDO synergistically integrates the strengths of both analog and digital architectures, as illustrated in

Figure 2. For a fair comparison, the total width of the power transistors (MPA in the analog path and the combined digital array) is carefully sized to ensure that all three LDOs possess equivalent current-driving capability. However, because the hybrid design leverages its analog auxiliary loop to naturally suppress ripple, the bit-weighting strategy for its digital segment differs from the standalone D-LDO. In the H-LDO, the M, H, and L groups are all configured as 8-bit arrays. This simplifies the digital control logic and is sufficient for cooperation with the analog loop to achieve excellent performance. The working principle of the hybrid LDO is shown in

Figure 3.

A key feature enhancing the transient performance is the incorporation of an asynchronous falling-edge detection module. This module, implemented with minimal hardware (an inverter, a NAND gate, and a small capacitor), continuously monitors VOUT. Under steady state, the internal node DDIN is held at a logic level that keeps the detection pulse signal (DDP) low. However, when a sharp falling edge is detected on VOUT (indicating a sudden increase in load current), the capacitive coupling through C1 causes a momentary change in DDIN’s voltage, which the logic interprets to generate a high pulse on DDP. This pulse asynchronously triggers the shift register (SR), bypassing the normal clock cycle to immediately turn on additional power switches, thereby accelerating the response to the load transient.

The robust operation of the hybrid LDO is governed by five intricately coupled control loops:

Loop-1 (Fast Analog Auxiliary Loop): This is the fastest loop, formed by the analog power transistor MPA and the common-gate amplifier M1. It provides an immediate, continuous-time response to counteract rapid output voltage fluctuations, effectively handling high-frequency transients.

Loop-2 (Main Analog Regulation Loop): This loop comprises a two-stage error amplifier (EA). The first stage is a differential pair (M3, M4) with a current mirror load (M7, M8), and the second stage is a common-source amplifier (M9). A Miller compensation capacitor () is connected across the second stage, establishing its output node as the dominant pole to ensure stability. This loop provides the primary DC gain for high-precision voltage regulation.

Loop-3 (Bias Current Stabilization Loop): A critical challenge in hybrid designs is maintaining a stable operating point for the analog circuitry when the digital section is active. Loop-3 addresses this by employing a replica path (MPr and M2r) that mirrors the current in the main analog branch. A dedicated error amplifier within the EA block (utilizing inputs M5, M6) compares the replica current () with a reference and adjusts the bias, thereby stabilizing the analog bias current () against variations.

Loop-4 (Digital Coarse Adjustment Loop): This loop is formed by the M and H subsections of the digital array (totaling 16 equivalent units) and is triggered by the window comparators (CMP2, CMP3). It performs coarse adjustments when VOUT deviates significantly from the target, providing a large current step for fast recovery.

Loop-5 (Digital Fine Adjustment Loop): This loop consists of the L subsection (8 bits) and a comparator (CMP1). It operates when VOUT is within the dead zone, performing fine-grained adjustments to minimize steady-state error and ripple, ensuring high DC accuracy.

This multi-loop architecture allows the H-LDO to dynamically allocate control effort, leveraging the speed of the analog loops and the efficiency of the digital loops to achieve superior overall performance.

The H-LDO’s SET mitigation strategy is inherent in its multi-loop architecture. Sensitive nodes exist in both the analog (e.g., EA output) and digital (e.g., comparator outputs) domains. However, the architecture provides cross-domain recovery mechanisms. An SET on an analog node, while causing an initial disturbance, can be corrected by the subsequent activation of the digital loops (Loop-4/5) if the deviation is large. Conversely, the fast analog Loop-1 can help dampen digital perturbations. This redundancy and collaboration between loops enhance the overall SET tolerance.

3. Simulation Results and Discussion

To thoroughly evaluate and compare the performance of the three LDO architectures, comprehensive simulations were conducted under both normal operating conditions and single-event strike scenarios. All designs were configured with a load capacitor () of 1 nF and tested for a maximum output current of 200 mA. Load transient simulations involved a current step from 0 to 200 mA (and vice versa) with a rise/fall time of 10 ns.

3.1. Performance Under Normal Operating Conditions

Figure 4 illustrates the transient response of the three LDOs to a 0-to-200 mA load current step. The analog LDO (A-LDO) exhibits a significant undershoot of 950 mV. This substantial deviation can be attributed to the limited slew rate of its error amplifier; when a large load current is suddenly demanded, the amplifier cannot instantaneously provide the necessary gate charging current for the large power transistor (MPA), leading to a temporary voltage droop until the feedback loop can compensate.

The digital LDO (D-LDO), benefiting from its fast, large-step coarse adjustment, shows a markedly improved undershoot of 470 mV. Its response is characterized by a two-stage recovery: an initial, rapid correction phase driven by the activation of the high-weight (H, M) bit groups, followed by a finer, oscillatory settling phase as the low-weight (L) group hunts for the new steady-state code. This discrete-time operation, while efficient, inherently results in the visible limit-cycle oscillations around the target voltage.

The proposed hybrid LDO (H-LDO) demonstrates the most superior performance, with a significantly smaller undershoot of only 230 mV. This enhancement is directly attributable to its synergistic multi-loop control strategy. The moment the load transient occurs, the ultra-fast analog auxiliary loop (Loop-1) provides an immediate burst of current through MPA, effectively “clamping” the initial voltage drop. Almost simultaneously, the asynchronous falling-edge detection circuit is triggered, pre-emptively enabling additional digital bits to provide sustained current support. This collaborative action between the analog and digital domains ensures a swift and smooth recovery with minimal overshoot and settling time.

Furthermore, the H-LDO achieves a remarkable peak current efficiency of 99.975%, rivaling that of pure D-LDOs, while its output voltage ripple remains comparable to that of A-LDOs thanks to the continuous regulation provided by the analog assist loop under steady-state conditions. A common figure-of-merit (FOM) is defined as:

which considers both transient response (

) and quiescent power consumption (

). This yields a value of 0.288 ps for the H-LDO using Equation (

1). A lower FOM value indicates a better trade-off between dynamic performance and power efficiency. This superior FOM indicates an excellent balance between dynamic performance and power efficiency, outperforming both the A-LDO and D-LDO in this holistic metric.

3.2. Single-Event Effect Analysis

The single-event susceptibility of the LDOs was evaluated by injecting a double-exponential current pulse,

, with

mA,

ps, and

ps at various sensitive circuit nodes, as illustrated in

Figure 5. This pulse shape is consistent with established models for charge deposition from heavy-ion strikes in advanced CMOS nodes. This current pulse model effectively replicates the charge deposition and collection process during an ion strike. Simulations were performed under both light-load (1 mA) and heavy-load (200 mA) conditions to assess performance across the operating range.

3.2.1. Digital LDO Robustness

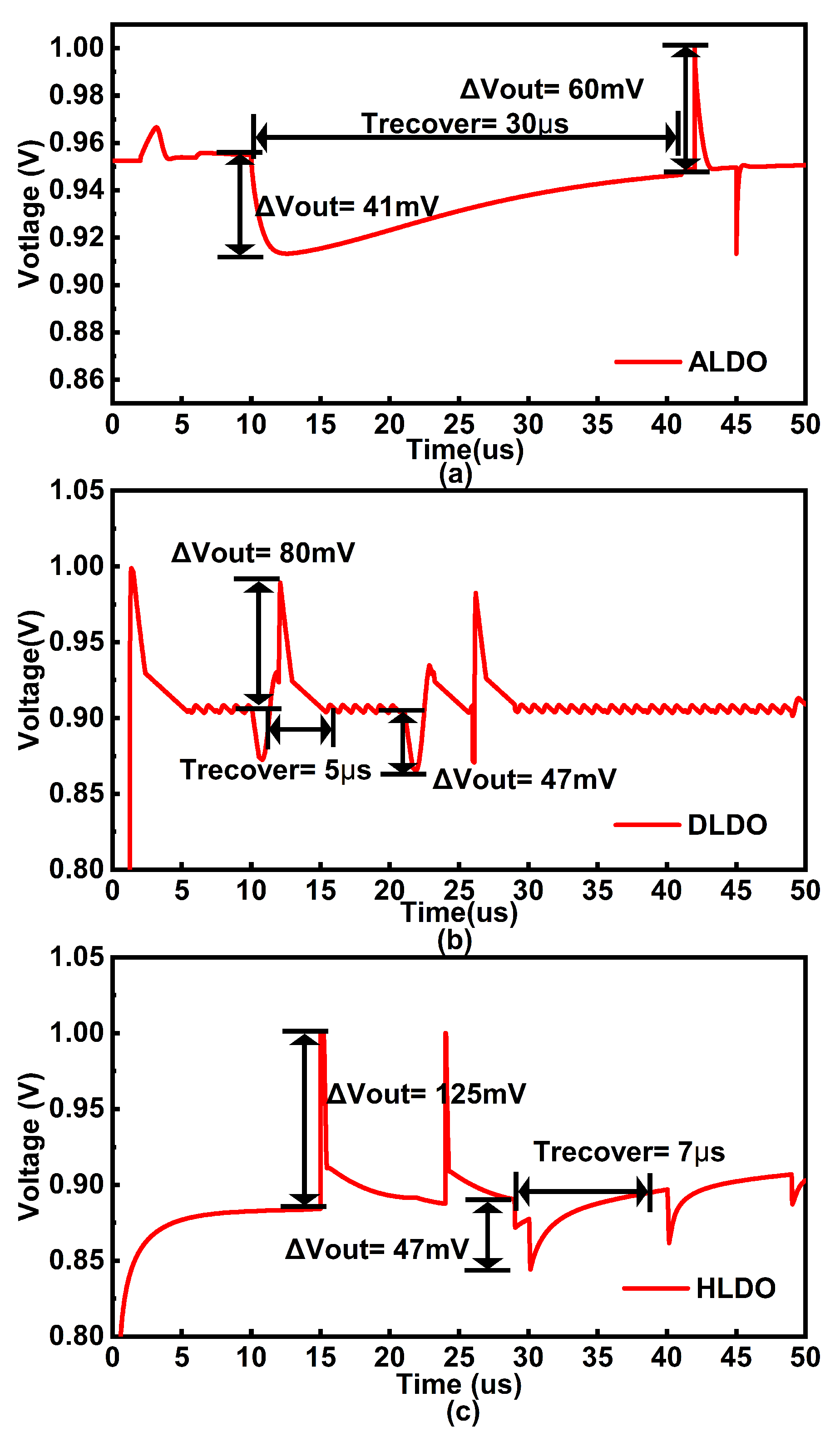

The digital LDO exhibits the highest inherent robustness to single-event transients. As shown in

Figure 6, at its most sensitive node—likely the output of the comparator or a critical node in the shift register control logic—the maximum observed output voltage perturbation is only 80 mV, with a recovery time of approximately 5 μs. This resilience stems from its digital, sampled-data nature. The radiation-induced current glitch is largely treated as transient noise. Unless the glitch is sufficiently large and timed to cause a metastable event in the comparator or a bit-flip in the shift register (effectively a Single-Event Upset, SEU), the periodic sampling and digital feedback mechanism will correct the output deviation within a few clock cycles. The primary SET manifestation is thus a small, quickly corrected voltage spike.

3.2.2. Analog LDO Vulnerability

In stark contrast, the analog LDO is highly susceptible. Referring to the simulation results in

Figure 7, a strike on a sensitive node like the high-impedance output of the error amplifier (e.g., the gate of MPA) can induce a large voltage glitch that directly and analogously modulates the gate drive of the power transistor. This disruption propagates through the entire feedback loop, leading to a substantial output voltage deviation, recorded here as 475 mV. The recovery time is prolonged, up to 30 μs, as the high-gain, continuous-time analog feedback loop, with its carefully designed but relatively slow compensation network, takes a significant time to settle back to its quiescent equilibrium point. This slow recovery can be catastrophic for noise-sensitive loads.

3.2.3. Hybrid LDO Mitigation Mechanism and Performance

The hybrid LDO effectively mitigates the weaknesses of the analog design, demonstrating significantly improved SET performance. The results in

Figure 6 and

Figure 7 show that the maximum output voltage change observed at its most sensitive node is 125 mV, and the recovery time is reduced to 7 μs. The analysis of its operation under different load conditions provides deeper insights into its hardening mechanism:

- -

Under Light-Load Conditions: The LDO operates predominantly in analog mode to maximize efficiency. In this state, its SET response is inherently inferior to the purely digital LDO, as a strike on the analog core (e.g., EA output) will still cause a disturbance. However, it shows a marked improvement over the standalone A-LDO. This is because the digital control loop remains active in the background. Once the analog-induced perturbation drives the output voltage outside the dead-zone of the digital comparators, the coarse digital loop (Loop-4) is activated, providing a deterministic current step to aid recovery, thereby cutting short the prolonged settling tail of the pure analog loop.

- -

Under Heavy-Load Conditions: The LDO operates primarily in digital mode. Consequently, its inherent susceptibility to SETs decreases and approaches that of the D-LDO. The key advantage of the H-LDO in this scenario lies in its enhanced recovery capability. The integrated fast transient modules—specifically the asynchronous falling-edge detector and the analog discharge transistor M10—play a crucial role. Following a particle strike that causes a voltage overshoot, M10 can actively sink current, rapidly pulling the output down. Conversely, if the strike causes a voltage droop, the falling-edge detector can asynchronously trigger the digital controller to provide immediate current boost, bypassing the normal clock latency. This results in a recovery time (7 μs) that is not only drastically faster than the A-LDO but also competitive with the D-LDO, despite the H-LDO’s more complex architecture.

Figure 8 presents a comprehensive radar chart comparing the normalized performance of the three LDOs across key metrics, including SET Susceptibility, Recovery Time, Transient Response, Efficiency, and Quiescent Current. The plot visually confirms that the hybrid LDO achieves a more balanced and superior overall performance profile. It successfully bridges the gap between the analog and digital domains, offering the high efficiency and digital robustness of a D-LDO while retaining the fast transient and low-noise advantages of an A-LDO, all while introducing significantly enhanced radiation hardness crucial for space-grade applications.

Table 1 provides a summary of the key performance metrics for the proposed hybrid LDO and compares them with recent state-of-the-art designs [

20,

21,

22,

23,

24]. The comparison highlights the competitive advantages of the proposed design, particularly in terms of its combination of high efficiency, fast transient response, and enhanced radiation tolerance. While direct quantitative comparison of SET performance with other works is challenging due to differences in technology nodes and simulation conditions, this work provides unique insights through its controlled comparison of three LDO architectures under identical 28-nm process technology.