Analysis of Mueller–Muller Clock and Data Recovery Circuits with a Linearized Model

Abstract

1. Introduction

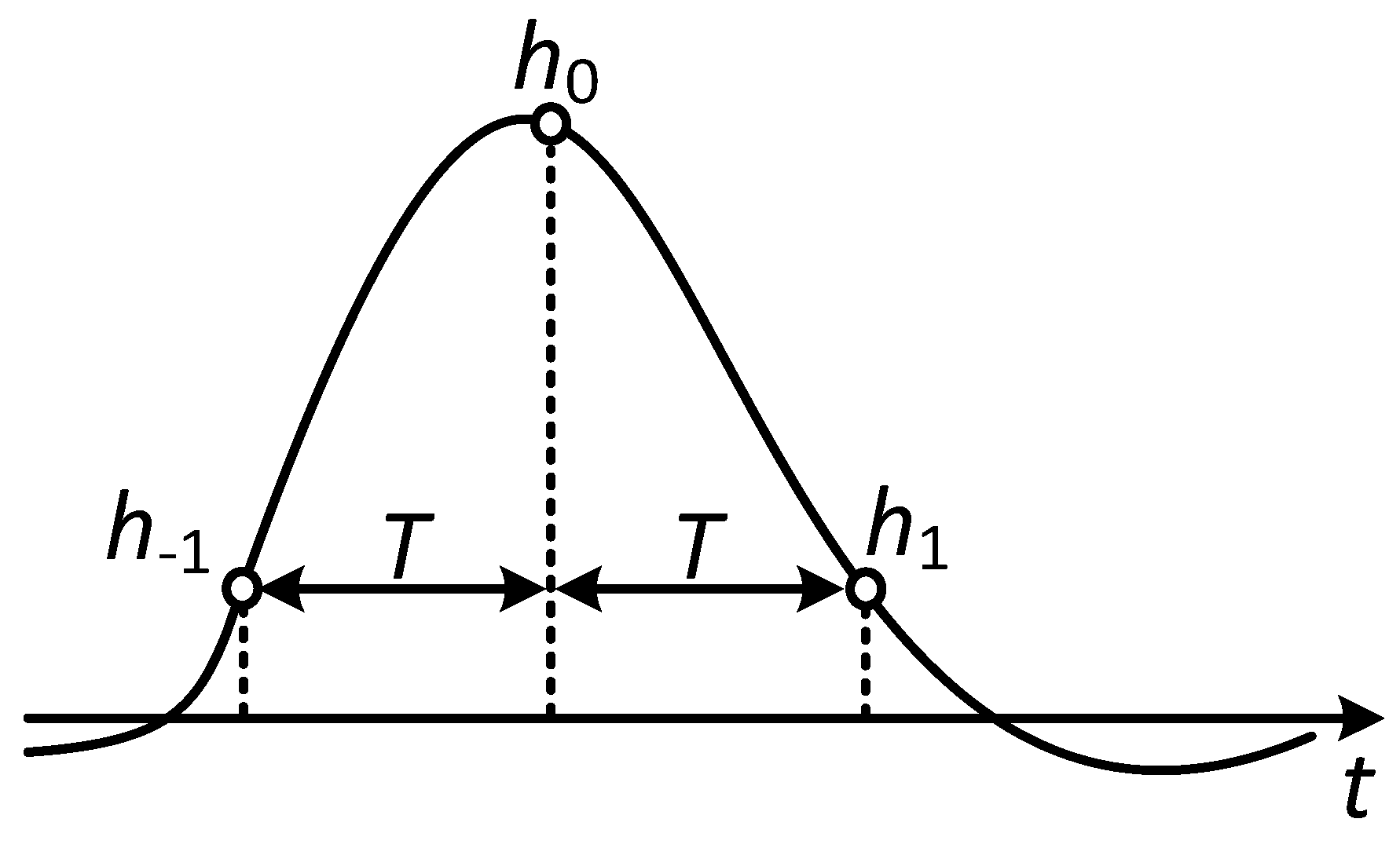

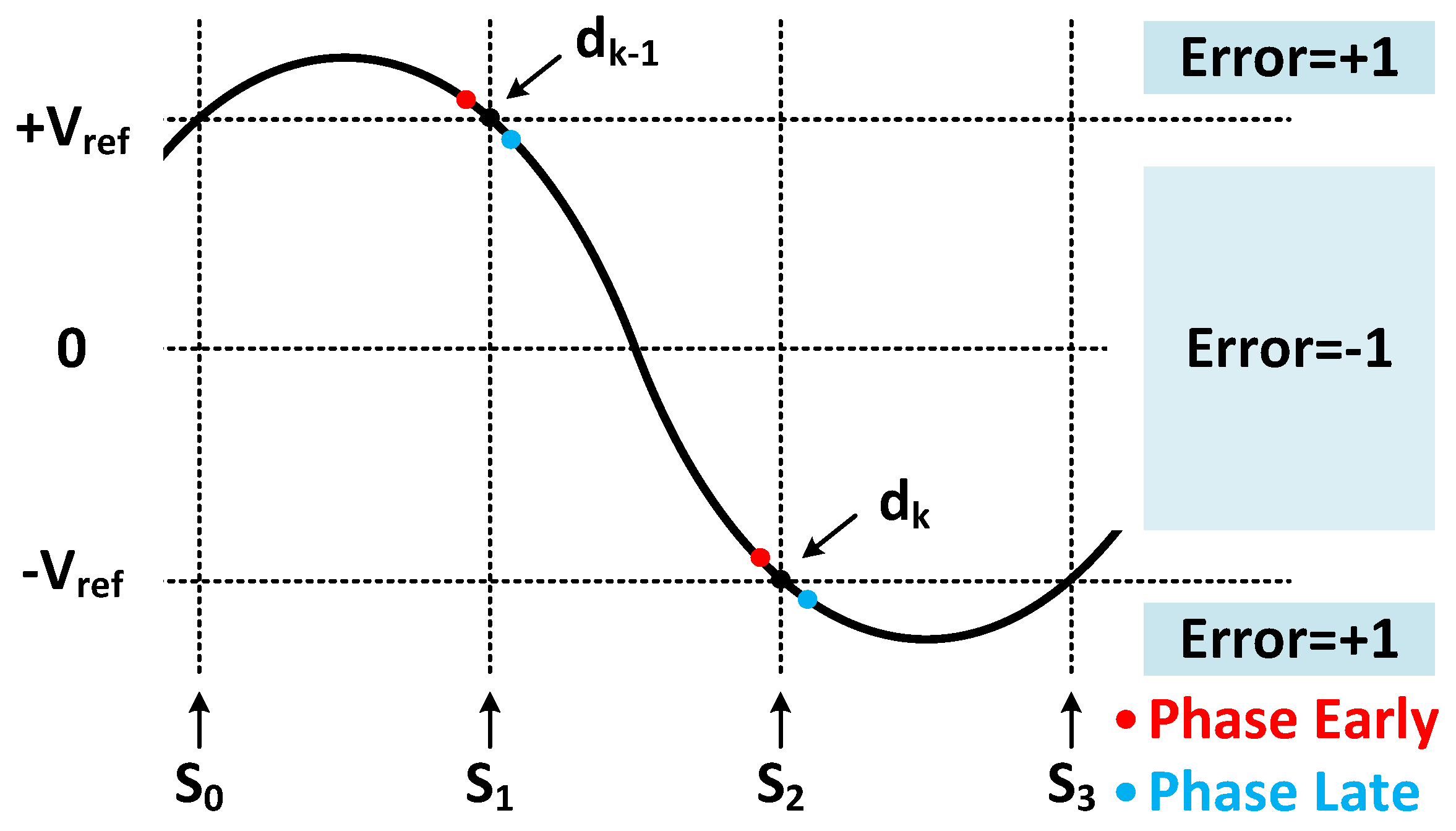

2. Mueller–Muller Phase Detector

2.1. The Principle of MMPD

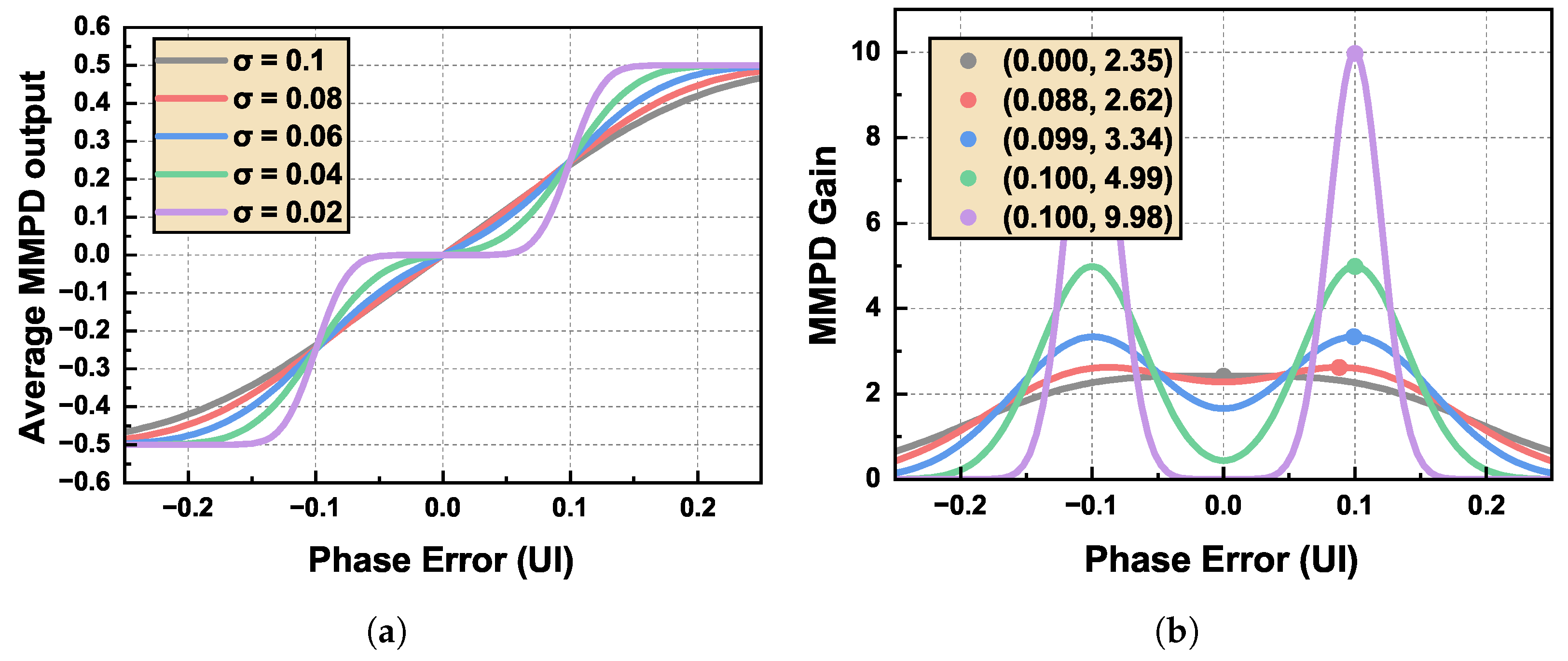

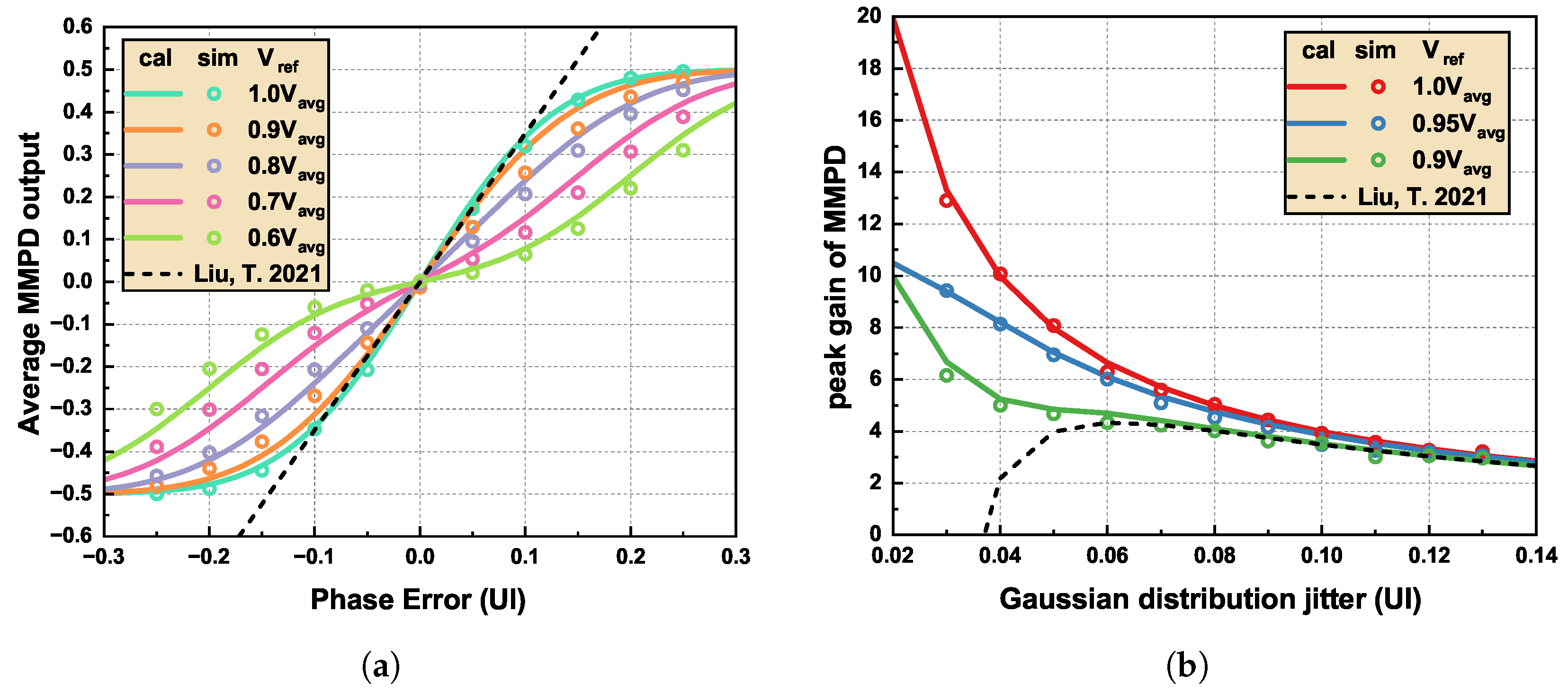

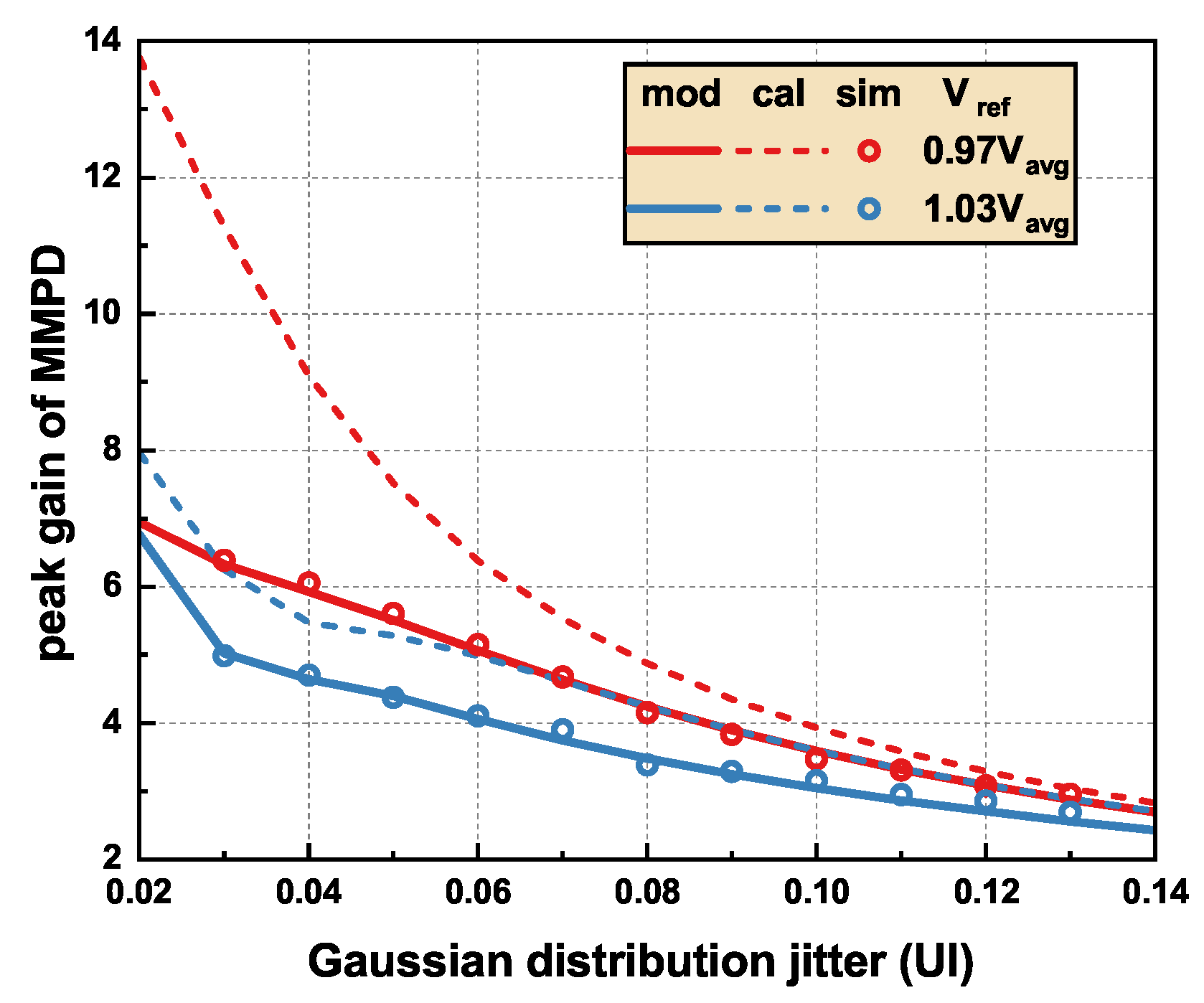

2.2. The Influence of the Reference Voltage

2.3. Linearization of MMPD

3. Small Signal Model of MM-CDR

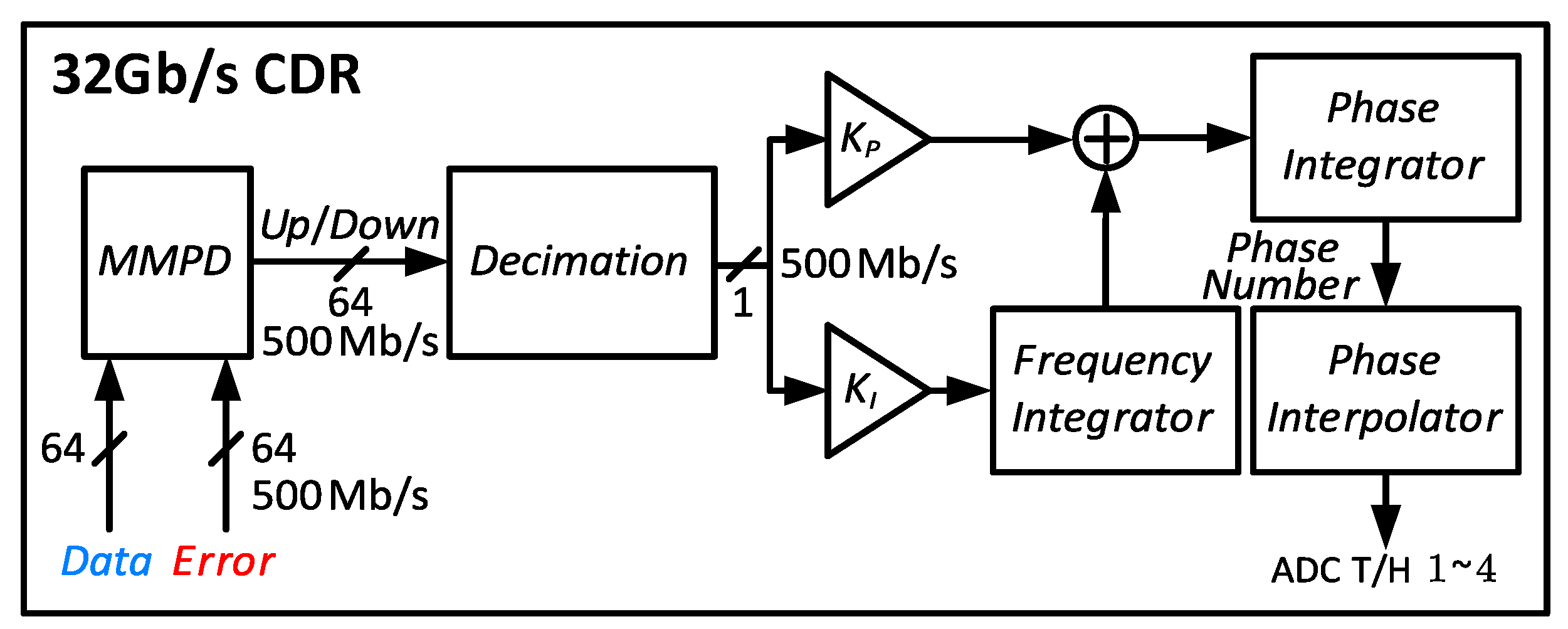

3.1. The Architecture of MMPD-Based Digital CDR

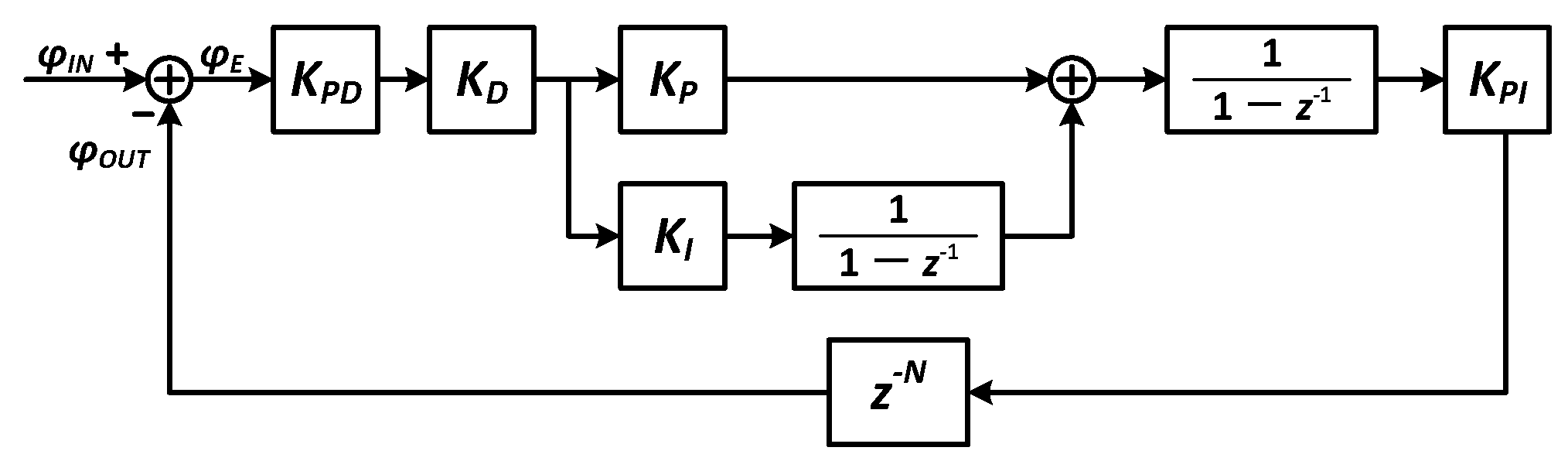

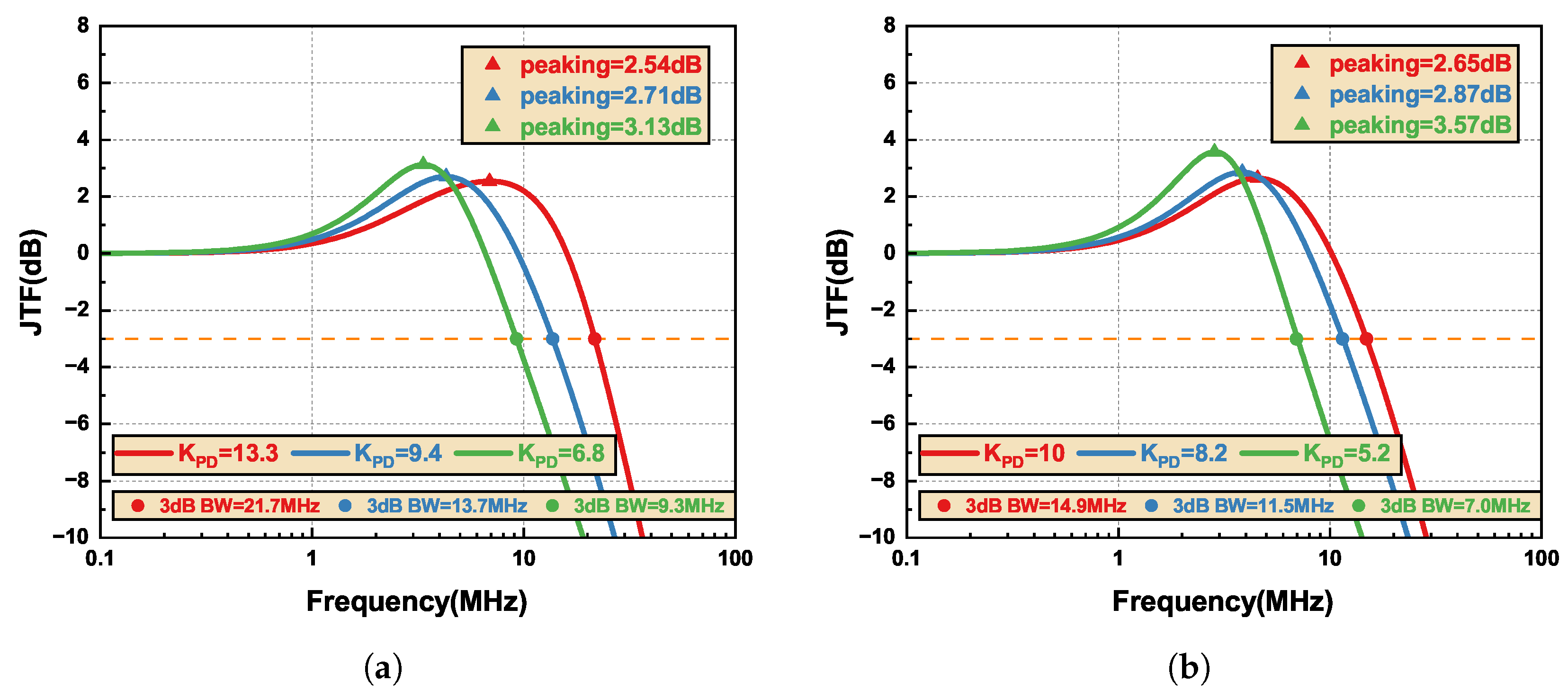

3.2. Linearized Analysis of CDR System

4. Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Mueller, K.; Muller, M. Timing Recovery in Digital Synchronous Data Receivers. IEEE Trans. Commun. 1976, 24, 516–531. [Google Scholar] [CrossRef]

- Spagna, F.; Chen, L.; Deshpande, M.; Fan, Y.; Gambetta, D.; Gowder, S.; Iyer, S.; Kumar, R.; Kwok, P.; Krishnamurthy, R.; et al. A 78 mW 11.8 Gb/s serial link transceiver with adaptive RX equalization and baud-rate CDR in 32 nm CMOS. In Proceedings of the 2010 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 7–11 February 2010; pp. 366–367. [Google Scholar] [CrossRef]

- Shi, L.; Gai, W.; Tang, L.; Xiang, X.; He, A. Hardware-efficient slope-error algorithm based PAM4 baud rate CDR scheme for 40 Gb/s receiver. Electron. Lett. 2018, 54, 1020–1022. [Google Scholar] [CrossRef]

- Sonntag, J.; Stonick, J. A Digital Clock and Data Recovery Architecture for Multi-Gigabit/s Binary Links. IEEE J. Solid-State Circuits 2006, 41, 1867–1875. [Google Scholar] [CrossRef]

- Park, M.J.; Kim, J. Pseudo-Linear Analysis of Bang-Bang Controlled Timing Circuits. IEEE Trans. Circuits Syst. I Regul. Pap. 2013, 60, 1381–1394. [Google Scholar] [CrossRef]

- Liang, J.; Sheikholeslami, A.; Tamura, H.; Ogata, Y.; Yamaguchi, H. Loop Gain Adaptation for Optimum Jitter Tolerance in Digital CDRs. IEEE J. Solid-State Circuits 2018, 53, 2696–2708. [Google Scholar] [CrossRef]

- Ge, X.; Chen, Y.; Zhao, X.; Mak, P.I.; Martins, R.P. Analysis and Verification of Jitter in Bang-Bang Clock and Data Recovery Circuit With a Second-Order Loop Filter. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2019, 27, 2223–2236. [Google Scholar] [CrossRef]

- Shu, Z.; Huang, S.; Li, Z.; Yin, P.; Zang, J.; Fu, D.; Tang, F.; Bermak, A. A 5–13.5 Gb/s Multistandard Receiver With High Jitter Tolerance Digital CDR in 40-nm CMOS Process. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 3378–3388. [Google Scholar] [CrossRef]

- Ting, C.; Liang, J.; Sheikholeslami, A.; Kibune, M.; Tamura, H. A Blind Baud-Rate ADC-Based CDR. IEEE J. Solid-State Circuits 2013, 48, 3285–3295. [Google Scholar] [CrossRef]

- Han, J.; Sutardja, N.; Lu, Y.; Alon, E. Design Techniques for a 60-Gb/s 288-mW NRZ Transceiver With Adaptive Equalization and Baud-Rate Clock and Data Recovery in 65-nm CMOS Technology. IEEE J. Solid-State Circuits 2017, 52, 3474–3485. [Google Scholar] [CrossRef]

- Lee, Y.S.; Ho, W.H.; Chen, W.Z. A 25-Gb/s, 2.1-pJ/bit, Fully Integrated Optical Receiver With a Baud-Rate Clock and Data Recovery. IEEE J. Solid-State Circuits 2019, 54, 2243–2254. [Google Scholar] [CrossRef]

- Park, S.; Choi, Y.; Sim, J.; Choi, J.; Park, H.; Kwon, Y.; Kim, C. A 0.83 pJ/b 52 Gb/s PAM-4 Baud-Rate CDR with Pattern-Based Phase Detector for Short-Reach Applications. In Proceedings of the 2023 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 19–23 February 2023; pp. 118–120. [Google Scholar] [CrossRef]

- Francese, P.A.; Toifl, T.; Buchmann, P.; Brändli, M.; Menolfi, C.; Kossel, M.; Morf, T.; Kull, L.; Andersen, T.M. A 16 Gb/s 3.7 mW/Gb/s 8-Tap DFE Receiver and Baud-Rate CDR With 31 kppm Tracking Bandwidth. IEEE J. Solid-State Circuits 2014, 49, 2490–2502. [Google Scholar] [CrossRef]

- Dokania, R.; Kern, A.; He, M.; Faust, A.; Tseng, R.; Weaver, S.; Yu, K.; Bil, C.; Liang, T.; O’Mahony, F. 10.5 A 5.9 pJ/b 10 Gb/s serial link with unequalized MM-CDR in 14 nm tri-gate CMOS. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar] [CrossRef]

- Mehrotra, P.; Maity, S.; Sen, S. An Improved Update Rate CDR for Interference Robust Broadband Human Body Communication Receiver. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 868–879. [Google Scholar] [CrossRef] [PubMed]

- Choi, M.C.; Ko, H.G.; Oh, J.; Joo, H.Y.; Lee, K.; Jeong, D.K. A 0.1-pJ/b/dB 28-Gb/s Maximum-Eye Tracking, Weight-Adjusting MM CDR and Adaptive DFE with Single Shared Error Sampler. In Proceedings of the 2020 IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar] [CrossRef]

- Yoo, B.J.; Lim, D.H.; Pang, H.; Lee, J.H.; Baek, S.Y.; Kim, N.; Choi, D.H.; Choi, Y.H.; Yang, H.; Yoon, T.; et al. 6.4 A 56 Gb/s 7.7 mW/Gb/s PAM-4 Wireline Transceiver in 10 nm FinFET Using MM-CDR-Based ADC Timing Skew Control and Low-Power DSP with Approximate Multiplier. In Proceedings of the 2020 IEEE International Solid-State Circuits Conference—(ISSCC), San Francisco, CA, USA, 16–20 February 2020; pp. 122–124. [Google Scholar] [CrossRef]

- Liu, T.; Li, T.; Lv, F.; Liang, B.; Zheng, X.; Wang, H.; Wu, M.; Lu, D.; Zhao, F. Analysis and Modeling of Mueller–Muller Clock and Data Recovery Circuits. Electronics 2021, 10, 1888. [Google Scholar] [CrossRef]

- JESD204C; Serial Interface for Data Converters. JEDEC Solid State Technology Association: Arlington, VA, USA, 2017.

| Phase Error | ||||

|---|---|---|---|---|

| 1 | −1 | 1 | −1 | Late |

| −1 | 1 | 1 | −1 | Late |

| 1 | −1 | −1 | 1 | Early |

| −1 | 1 | −1 | 1 | Early |

| All other cases | Hold | |||

| Parameter | Value |

|---|---|

| 13.3, 9.4, 6.8 per UI under = 0.03 UI | |

| 10, 8.2, 5.2 per UI under = 0.04 UI | |

| 0.54 × 64 = 34.56 | |

| 1 UI/25 bit | |

| N | 5 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, J.; Gu, Y.; Feng, X.; Chi, R.; Wu, J.; Chen, Y. Analysis of Mueller–Muller Clock and Data Recovery Circuits with a Linearized Model. Electronics 2024, 13, 4218. https://doi.org/10.3390/electronics13214218

Chen J, Gu Y, Feng X, Chi R, Wu J, Chen Y. Analysis of Mueller–Muller Clock and Data Recovery Circuits with a Linearized Model. Electronics. 2024; 13(21):4218. https://doi.org/10.3390/electronics13214218

Chicago/Turabian StyleChen, Junkun, Youzhi Gu, Xinjie Feng, Runze Chi, Jiangfeng Wu, and Yongzhen Chen. 2024. "Analysis of Mueller–Muller Clock and Data Recovery Circuits with a Linearized Model" Electronics 13, no. 21: 4218. https://doi.org/10.3390/electronics13214218

APA StyleChen, J., Gu, Y., Feng, X., Chi, R., Wu, J., & Chen, Y. (2024). Analysis of Mueller–Muller Clock and Data Recovery Circuits with a Linearized Model. Electronics, 13(21), 4218. https://doi.org/10.3390/electronics13214218