Abstract

Parametric fault diagnosis of analog very high-frequency circuits consisting of a distributed parameter transmission line (DPTL) terminated at both ends by lumped one-ports is considered in this paper. The one-ports may include linear passive and active components. The DPTL is a uniform two-conductor line immersed in a homogenous medium, specified by the per-unit-length (p-u-l) parameters. The proposed method encompasses all aspects of parametric fault diagnosis: detection of the faulty area, location of the fault inside this area, and estimation of its value. It is assumed that only one fault can occur in the circuit. The diagnostic method is based on a measurement test arranged in the AC state. Different approaches are proposed depending on whether the faulty is DPTL or one of the one-ports. An iterative method is modified to solve various systems of nonlinear equations that arise in the course of the diagnostic process. The diagnostic method can be extended to a broader class of circuits containing several transmission lines. Three numerical examples reveal that the proposed diagnostic method is fast and gives quite accurate findings.

1. Introduction

Accurate and fast fault diagnosis of analog circuits, including fault detection, location, and estimation of its value, is an important task in electrical engineering. A huge effort has been made by engineers and researches, over the last few decades, to develop various methods, algorithms, and techniques for testing and diagnosing analog electronic circuits. As a result, many accurate findings have been obtained and reported. Numerous fault diagnosis methods were described in [1,2,3,4]. Nevertheless, some issues in this field remain open, and there is a growing need for their solving.

The various types of faults that may occur in electronic circuits can be divided into local and global defects, as well as parametric (soft) and hard (catastrophic) faults. Local defects concern random regional disturbances within a circuit, whereas global defects concern disturbances that effect entire regions. A fault is said to be parametric if the circuit parameter deviates from the tolerance range, but does not produce any topological changes. Hard faults are shorts and opens. The real short is simulated by a low resistor, whereas the real open is simulated by a high resistor. In Integrated Circuits (ICs), they are classified as spot defects. Important questions of the fault diagnosis are testability analysis and test point selection [5,6,7,8,9]. The parametric fault diagnosis problem has attracted a great deal of attention both in linear circuits [10,11,12,13] and nonlinear circuits [14,15,16,17]. Catastrophic fault diagnosis of bipolar and Complementary Metal Oxide Semiconductor (CMOS) circuits was considered in [18]. Some research studies concentrate on self-testing methods [19]. Numerous works describe artificial intelligence method applications to fault diagnosis [20,21,22].

Traditionally, the research works dealing with fault diagnosis of analog electronic circuits are limited to lumped devices. However, the distribution systems that process high-speed signals play an important role in electronic engineering. Some very high-frequency circuits include distributed parameter transmission lines (DPTLs) [23] terminated by lumped passive or active devices. A method for diagnosing short and open faults in the circuits’ transmission lines was developed in [24]. However, the problem of parametric fault diagnosis of this class of circuits is a gap that should be filled.

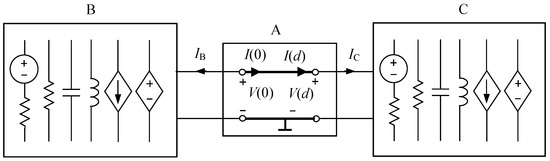

In this paper, we consider linear analog circuits of very high frequency consisting of cascade-connected Blocks A, B, and C, as shown in Figure 1. Block A includes a uniform two-conductor DPTL immersed in a homogenous medium. It has the length d and is specified by the per-unit-length (p-u-l) parameters [23]. Blocks B and C are lumped one-ports, which may contain linear resistors, inductors, capacitors, controlled sources, and independent AC sources. Our goal is to develop a method for parametric fault diagnosis of this class of circuits. The scope of the diagnosis and the main assumptions are as follows.

Figure 1.

Linear circuit including a distributed parameter transmission line (DPTL) terminated by lumped one-ports.

Assume that only one block, A, B, or C, can be faulty. A parametric fault of the DPTL in Block A, considered in this paper, can be caused by, e.g., the change of geometric dimensions (e.g., the distance between the conductors and their radii), a change of a relative dielectric constant, or a change of electrical resistivity. Thus, the defect occurs along the entire line and has a global nature. It influences the p-u-l parameters of the line. The deviations of these parameters from the nominal values evaluate the fault, and all of them should be determined in the course of the diagnostic process. In Block B or C, only one element may be faulty. Diagnosis of these blocks includes the location of the faulty element and the estimation of its value.

This paper is organized as follows. The basic methodology of the proposed approach is described in Section 2. Section 3 presents an iterative method utilized by the diagnostic method. Three examples and a discussion of the obtained results are demonstrated in Section 4. Section 5 concludes the paper.

2. Parametric Fault Diagnosis Method

To diagnose a circuit belonging to the class defined in Section 1, a measurement test is arranged in the AC state. The phasors and of the input and output voltages of the DPTL are measured at one frequency while running the test.

2.1. Detection of the Faulty Block

The preliminary step of fault diagnosis is to detect the faulty block or to state that the circuit is fault-free. For this purpose, each of the blocks with nominal parameters is considered separately. In the cases of Blocks B and C, the currents and are determined by the analysis of the blocks driven by the voltage sources and , respectively. The obtained phasors of these currents are denoted by and . Since and have been measured in the real circuit, which can be faulty, or is the actual current in the circuit if the corresponding Block B or C is fault-free. Next, we consider Block A including the DPTL driven at the left end by and at the right end by . The line is described by the system of equations:

where , with , , is the propagation constant, , with , is the characteristic impedance, and the p-u-l parameters, r, l, g, c have nominal values. We solve (1) for and and denote the solutions by and . They are the actual currents in the circuit if the DPTL is fault-free.

The fault detection and identification of the faulty block is based on Table 1, where , , , and denote the actual currents in the circuit. The table is created on the assumption, made in Section 1, that only one block, A, B, or C, can be faulty.

Table 1.

Results leading to a set of rules for detecting a faulty block.

The results presented in Table 1 can be summarized as follows.

If , , then the circuit is fault-free.

If , , then Block A is faulty.

If , , then Block B is faulty.

If , , then Block C is faulty.

2.2. Diagnosis of the Faulty Block A

If Block A has been detected as faulty (, ), we find its actual p-u-l parameters using the two-step procedure.

2.2.1. Step 1

Let us substitute , and the measurement voltages , in (1) and express and in the rectangular form: , . As a result, we obtain a system of two nonlinear complex equations in four real unknown variables: , , , . This system has the form , where , , and T denotes transposition. It is solved using the iterative method described in Section 3, where two iteration Formulas (8) and (9) are presented. In the discussed case, each of them consists of four individual real linear equations in four unknown real variables. If (8) generates the sequence that is not convergent, the modified iteration Formula (9) is applied.

2.2.2. Step 2

Having , , , and , the p-u-l parameters of the DPTL are determined as follows. On the basis of equations and , we write:

Hence, we arrive at two real equations with four real variables r, l, g, and c:

Similarly, using and gives the equality:

leading to two other real equations in four real variables r, l, g, and c:

In the systems of Equations (3) and (5), the unknown variables are the p-u-l parameters, r, l, g, and c. Since they have orders that differ significantly one from the other, we scale them using the factors , , , and . Combining (3) and (5) and substituting , , , and yield:

Let us denote (6) by , where , and solve it using the iterative method described in Section 3. Since is a real function, is a real matrix and . We apply the iteration formula (8), which in this case represents a system of four real linear equations in four unknown real variables. If the generated sequence does not converge, the modified iteration formula (9) is used.

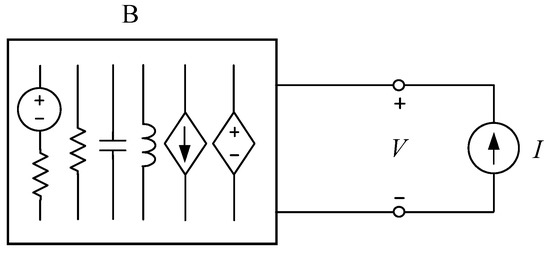

2.3. Diagnosis of the Faulty Block B

If the preliminary step of the diagnosis states that Block B is faulty (, ), then, according to the assumption made in Section 1, one of the elements of this block is faulty. We wish to locate this element and estimate its value. For this purpose, we consider Block B driven by the current source , as shown in Figure 2.

Figure 2.

Circuit used for fault diagnosis of Block B.

Since the input voltage V is equal to the measured voltage , both I and V are given. Let us describe the circuit depicted in Figure 2 using the node method, leading to a system of N complex equations. Because V is one of the node voltages, the number of unknown variables is . We present them in rectangular form obtaining real variables. Let us increase the number of variables to by adding one of the circuit parameters considered as potentially faulty. As a result, we obtain a system of N complex equations in real variables, which can be presented in the compact form . To solve them, we apply the method described in Section 3 where , and is a matrix. The iteration Formula (8) consists of real equations in real unknown variables. They include real and imaginary parts of the node voltage phasors and one unknown parameter, whereas the other parameters have nominal values. If the method based on the iteration Formula (8) does not converge, the modified Formula (9) is used. We repeat this approach for each of the parameters in Block B considered as potentially faulty. Every time, the solution includes one unknown parameter and redundant real variables. When the chosen parameter is faulty, we obtain the correct result. Otherwise, the method can give non-realistic solutions or not be convergent. Sometimes, the method may find a virtual solution.

Note 1. If Block B contains elements not acceptable by the node method, the modified node method is applied.

Note 2. Diagnosis of Block C is carried out analogously.

3. Solving a System of Nonlinear Algebraic Equations

3.1. Standard Method

Let us consider a system of n nonlinear complex equations in m unknown real variables presented in a compact form:

where , , . To solve this equation, the iterative method developed in [24] can be used. This iteration formula:

represents a system of m real individual linear equations in m real unknowns , …, at , where k is the index of iteration:

where:

Matrix has order ; matrix has order ; and is an vector. As a consequence, is a real square matrix of order . If the iteration process specified by (8) converges, it is terminated when and , where and are convergence tolerances, and is considered as an approximate solution. If the method does not meet the convergence tolerances in a preset maximum number of iterations , it fails.

3.2. Modified Method

The difficulty of solving (7) arises if the standard method does not converge. In such a case, we modify it as described in the sequel.

The matrix is symmetrical for each , because and positive semidefinite because for any real vector : . Thus, its determinant is greater than or equal to zero. When , the iterative method fails. Even if the determinant is close to zero, the method may not converge. To get rid of this drawback, we propose a new iteration formula as follows:

where and are positive constants selected based on numerical experiments. Since is a diagonal matrix with identical positive elements on the main diagonal, the matrix is positive definite for all , because for any real vector :

= .

4. Illustrative Examples

The diagnostic method proposed in Section 2 and Section 3 was implemented in the MATLAB environment, and the calculations were performed on a PC with an Intel Core i7-6700 processor. To show the efficiency of the method, three numerical examples are presented. Whenever the iterative method described in Section 3 is employed, the nominal values of the fault-free variables are chosen to form the initial guess.

4.1. Example 1

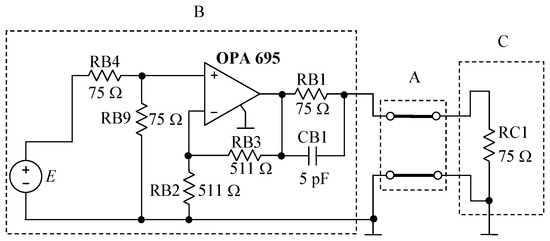

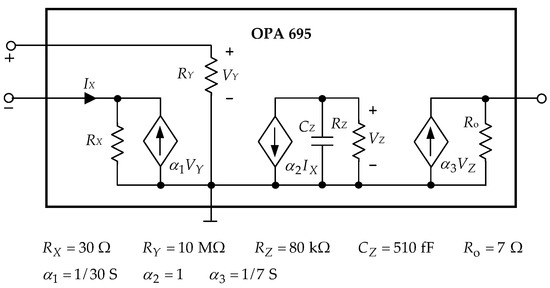

Figure 3 shows a basic wideband impedance-matched line driver, configured to drive a coaxial cable RG59 and 75 load. It includes the current-feedback operational amplifier, two-conductor DPTL, and lumped elements. The model OPA 695 used in the simulations is depicted in Figure 4. For this model, very good compatibility of the frequency responses in the frequency range 100 Hz–200 MHz and the time responses was achieved compared to the full model available in the IsSPICE software.

Figure 3.

Circuit containing a wideband impedance-matched line driver and a DPTL terminated by a resistor.

Figure 4.

Model OPA 695.

The nominal values of the lumped elements existing in the circuit and in the OPA 695 model are indicated in Figure 3 and Figure 4, whereas the nominal p-u-l parameters of the DPTL are as follows: , , , , and the length d of the line is 1 m. The amplitude of the voltage source E is 2 V, and the phase is , . The accuracy of the measurements of the voltage amplitudes is and of the phase . The convergence tolerances and constants are: , , , , .

In the circuit of Figure 3, we diagnosed 5 faults of Block A, 17 faults of Block B, and 3 faults of Block C. In all these cases, the procedure for detecting the faulty block, described in Section 2.1, gave the correct outcomes.

The findings of the diagnoses of five faults of Block A are placed in Table 2. Every time, all the p-u-l parameters of the line are calculated. The relative error:

of the 20 parameter values presented in this table is as follows. In 15 cases , ; in three cases , ; in two cases, (10%), . To obtain the results summarized in Table 2, the iterative method, based on the iteration Formula (8), was used. The number of iterations for finding , , , and (Step 1) ranges from six to 22 and for finding the p-u-l parameters (Step 2) is four in all the cases.

Table 2.

Results of the diagnosis of faulty Block A including the DPTL.

Table 3, Table 4, Table 5 and Table 6 present 17 cases of the faults of Block B caused by 5 faults of the resistor RB1 (Table 3), 4 faults of the resistor RB2 (Table 4), 4 faults of the resistor RB3 (Table 5), and 4 faults of the capacitor CB1 (Table 6).

Table 3.

Results of the diagnosis of faulty Block B for different values of the defective resistor RB1 whose nominal value is 75 .

Table 4.

Results of the diagnosis of faulty Block B for different values of the defective resistor RB2 whose nominal value is 511 .

Table 5.

Results of the diagnosis of faulty Block B for different values of the defective resistor RB3 whose nominal value is 511 .

Table 6.

Results of the diagnosis of faulty Block B for different values of the defective capacitor CB1 whose nominal value is 5 pF.

The outcomes summarized in Table 3 are quite accurate; does not exceed 0.7%. To diagnose Faults 1 and 2, the proposed iteration Formula (9) was used because the sequences generated by the iteration Formula (8) were not convergent. In the case of Fault 4, the method finds correctly the faulty resistor , inserted in the table, and a virtual fault . The number of iterations needed to determine each parameter value presented in the table varies from five to 13, and the CPU time does not exceed 0.33 s.

The findings inserted in Table 4 are very accurate; is smaller than 0.18%. The number of iterations ranges from five to eight, and the CPU time does not exceed 0.32 s.

The relative error of the resistor values posted in Table 5 is less than 0.7%; the number of iterations varies from five to six; and the CPU time does not exceed 0.36 s. In the cases of Faults 2 and 3 placed in this table, the method gives the correct faulty resistors and virtual ones. The virtual fault is in Case 2 and in Case 3. However, if the accuracy of the measurement in the diagnostic test course is increased ( for the amplitude and for the phase), the method provides only the correct findings. Unfortunately, it is difficult to ensure such high accuracy in real conditions.

The relative error of the outcomes placed in Table 6 is less than 2.8%; the number of iterations ranges from 4–6; and the CPU time does not exceed 0.063 s.

Table 7 contains the results of the diagnosis of the faulty Block C. They were obtained performing 4–5 iterations and are burdened with very small relative error, . The CPU time does not exceed 0.095 s.

Table 7.

Results of the diagnosis of faulty Block C for different values of the defective resistor RC1 whose nominal value is 75 .

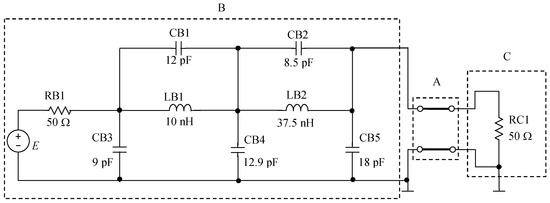

4.2. Example 2

Let us consider the circuit, including the 150 MHz elliptical low-pass filter and the DPTL terminated by a resistor, shown in Figure 5. The nominal values of the lumped elements are indicated in the figure, whereas the nominal p-u-l parameters of the DPTL are as follows: , , , , and the length d of the line is 0.7 m. The amplitude of the voltage source E is 5 V, and the phase is , . The accuracy of the measurements of the voltage amplitudes is and of the phase . The convergence tolerances and constants are: , , , , and .

Figure 5.

Circuit including the 150 MHz elliptical low-pass filter and the DPTL terminated by a resistor.

We performed 39 diagnoses including 4 faults of Block A, 30 faults of Block B, and 5 faults of Block C. In all cases, the procedure for detecting the faulty block, described in Section 2.1, gave the correct results.

The outcomes of the diagnoses of four faults of Block A are summarized in Table 8. In 11 cases , the relative error of the results provided by the method was less than 1%; in the remaining five cases it is greater than 1%, but smaller than 2.2%. The number of iterations for finding , , , and (Step 1) ranges from five to six and for finding the p-u-l parameters (Step 2) from four to five.

Table 8.

Results of the diagnosis of faulty Block A including the DPTL.

In Block B, all the elements can be diagnosed except CB1 and CB2, because the sensitivities of the voltage of this block with respect to these elements are very small. Consequently, for realistic measurement accuracy, variations of these elements have a very small influence on the voltage. All the other elements of this block, RB1, CB3, CB4, CB5, LB1, and LB2, were diagnosed. Table 9, Table 10, Table 11, Table 12, Table 13 and Table 14 present 30 cases of the faults including five faults of the resistor RB1 and five faults of each of the capacitors CB3, CB4, and CB5 and the inductors LB1 and LB2.

Table 9.

Results of the diagnosis of faulty Block B for different values of the defective resistor RB1 whose nominal value is 50 .

Table 10.

Results of the diagnosis of faulty Block B for different values of the defective capacitor CB3 whose nominal value is 9 pF.

Table 11.

Results of the diagnosis of faulty Block B for different values of the defective capacitor CB4 whose nominal value is 12.9 pF.

Table 12.

Results of the diagnosis of faulty Block B for different values of the defective capacitor CB5 whose nominal value is 18 pF.

Table 13.

Results of the diagnosis of faulty Block B for different values of the defective inductor LB1 whose nominal value is 10 nH.

Table 14.

Results of the diagnosis of faulty Block B for different values of the defective inductor LB2 whose nominal value is 37.5 nH.

The outcomes placed in Table 9 are very accurate, and . The number of iterations ranges from four to six, and the CPU time of each of the diagnoses does not exceed 0.1 s. To diagnose Fault 1, the proposed iteration Formula (9) was used because the sequence generated by the iteration Formula (8) was not convergent.

The findings presented in Table 10 and Table 11 are very accurate (); the number of iterations varies from four to five, and CPU time does not exceed 0.21 s.

The maximum relative error of the results included in Table 12 is , and the number of iterations in all the cases is two. The CPU time is 0.16 s.

The outcomes summarized in Table 13 and Table 14 are very accurate; . The number of iterations ranges from four to 14. The CPU time is 0.16 s.

The relative error of the resistor values inserted in Table 15 is less than 0.02%. The number of iterations varies from five to nine. The CPU time is 0.19 s. To diagnose Fault 1, the proposed iteration formula (9) was used because the sequence generated by the iteration formula (8) was not convergent.

Table 15.

Results of the diagnosis of faulty Block C for different values of the defective resistor RC1 whose nominal value is 50 .

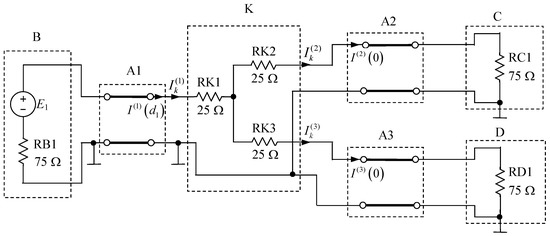

4.3. Example 3

Figure 6 shows the circuit including three DPTLs, A1, A2, and A3, having the p-u-l parameters: , , , . The lengths of the lines are , , and . The nominal values of the lumped elements are indicated in the figure; the amplitude of the voltage source equals 5 V; and the phase is . The other parameters are as in Example 2.

Figure 6.

Circuit including three distributed parameter transmission lines.

The circuit of Figure 6 has a more complex structure than that shown in Figure 1. It consists of three blocks, A1, A2, and A3, containing DPTLs and four blocks, B, C, D, and K, including lumped elements. Similarly, as in Section 1, we assume that only one block can be faulty and only one element of the lumped block can be defective. In the blocks containing DPTLs, all the p-u-l parameters may deviate from nominal values due to a fault, and all of them must be diagnosed. The diagnostic test of the circuit requires the input and output voltages of each DPTL. The fault detection rule presented in Section 2.1 for three-block circuits can be directly extended to the circuit of Figure 6. In particular, the three-port Block K is faulty if , ,and .

In the circuit of Figure 6, we diagnosed three faults of each of Blocks A1, A2, A3, B, C, and D and nine faults of Block K. In all these cases, the procedure for detecting a faulty block gave correct outcomes.

The findings of the diagnoses of six faults of Blocks A1, A2, and A3 (24 parameters) are placed in Table 16. In 18 cases (75%), , and in six cases (25%), . The number of iterations in Step 1 ranges from 4–7 and in Step 2 from 4–5.

Table 16.

Results of the diagnosis of faulty Blocks A1, A2, and A3 including DPTLs.

Table 17 and Table 18 present the results of the diagnoses of two faults in each of Blocks B, C, and D and six faults in Block K. To diagnose Block K, which is a three-port circuit, an obvious modification of the procedure described in Section 2.3 is needed. The results are very accurate; the number of iterations ranges from 5–15; and the CPU time does not exceed 0.4 s. In three cases, corresponding to , , and , the iteration formula (9) was used because the iteration sequences generated by formula (8) were not convergent.

Table 17.

Results of the diagnosis of faulty Blocks B, C, and D for different values of the defective resistors RB1, RC1, and RD1.

Table 18.

Results of the diagnosis of faulty Block K for different values of the defective resistors RK1, RK2, and RK3.

5. Conclusions

Parametric fault diagnosis of analog circuits of very high frequency consisting of a distributed parameter transmission line, as well as lumped linear passive and active elements has not been discussed in the literature till now. This paper deals with the problem and proposes a method that covers all aspects of the fault diagnosis. First, the faulty area is determined, and then, the faulty component inside this area is located and its value estimated. There are three areas in the circuit, called blocks, including the DPTL (Block A) and two lumped circuits terminating the line (Blocks B and C). It is assumed that only one block may be faulty and only one component of the faulty Block B or C can be defective. The blocks may include IC devices if they can be represented by realistic linear models. The example is the operational amplifier circuit designed so that the operational amplifiers operate in the linear regions. In the DPTL, all the p-u-l parameters can deviate from their nominal values, leading to the fault of the line. This concept can be directly extended to the circuits, including more than one DPTL and more than three blocks, as illustrated in Example 3.

The proposed diagnostic method employs voltage measurements from two terminals of the DPTL, and no current measurements are required. It takes full advantage of the measured amplitude and phase at one frequency only. Numerical examples reveal that the method successfully determines the faulty block and the faulty element inside this block. The obtained values of the faulty elements are quite accurate. The iterative method utilized by the diagnostic method is effective, fast, and does not require great computing power. The proposed iteration Formula (9) is useful when the standard Formula (8) fails. In the numerical examples where such a situation occurred, it helps to find the solution. The method is limited to single fault diagnosis, which occurs most frequently in analog circuits. The temperature changes of the parameters are neglected because the temperature coefficients of resistance and capacitance of the elements used in the circuits of very high frequency have low values.

A drawback of the proposed diagnostic method is that, sometimes, it gives the actual fault accompanied by a virtual one. In 2.2% of the diagnosed cases, the method failed.

Author Contributions

M.T. provided the idea, managed the paper, and wrote the manuscript; S.H. implemented the method, chose illustrative examples, and performed the numerical experiments. All authors read and agreed to the published version of the manuscript.

Funding

This research received no external funding.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Gizopoulos, D. Advances in Electronic Testing: Challenges and Methodologies; Springer: Dordrecht, The Netherlands, 2006. [Google Scholar]

- Kabisatpathy, P.; Barua, A.; Sinha, S. Fault Diagnosis of Analog Integrated Circuits; Springer: Dordrecht, The Netherlands, 2005. [Google Scholar]

- Sun, Y. (Ed.) Test and Diagnosis of Analogue, Mixed-Signal and RF Integrated Circuits: The System on Chip Approach; IET Digital Library: London, UK, 2008. [Google Scholar]

- Binu, D.; Kariyappa, B.S. A survey on fault diagnosis of analog circuits: Taxonomy and state of the art. Int. J. Electron. Commun. 2017, 73, 68–83. [Google Scholar] [CrossRef]

- Fontana, G.; Luchetta, A.; Manetti, S.; Piccirilli, M.C. An unconditionally sound algorithm for testability analysis in linear time-invariant electrical networks. Int. J. Circ. Theor. Appl. 2016, 44, 1308–1340. [Google Scholar] [CrossRef]

- Fontana, G.; Luchetta, A.; Manetti, S.; Piccirilli, M.C. A fast algorithm for testability analysis of large linear time-invariant networks. IEEE Trans. Circuits Syst. I Regul. Pap. 2017, 64, 1564–1575. [Google Scholar] [CrossRef]

- Tang, X.; Xu, A.; Li, R.; Zhu, M.; Dai, J. Simulation-based diagnostic model for automatic testability analysis of analog circuit. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 2018, 37, 1483–1493. [Google Scholar] [CrossRef]

- Grasso, F.; Luchetta, A.; Manetti, S.; Piccirilli, M.C. A method for the automatic selection of test frequencies in analog fault diagnosis. IEEE Trans. Instrum. Meas. 2007, 56, 2322–2329. [Google Scholar] [CrossRef]

- Saeedi, S.; Pishgar, S.H.; Eslami, M. Optimum test point selection method for analog fault dictionary techniques. Analog Integr. Circuits Signal Proc. 2019, 100, 167–179. [Google Scholar] [CrossRef]

- Djordjevic, S.; Pesic, M.T. A fault verification method based on the substitution theorem and voltage-current phase relationship. J. Electron. Test. 2020, 36, 617–629. [Google Scholar] [CrossRef]

- Gao, T.; Yang, J.; Jiang, S. A novel incipient fault diagnosis method for analog circuits based on GMKL-SVM and wavelet fusion features. IEEE Trans. Instrum. Meas. 2021, 70, 3502315. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S. A method for multiple soft fault diagnosis of linear analog circuits. Measurement 2019, 131, 714–722. [Google Scholar] [CrossRef]

- Yang, C. Multiple soft fault diagnosis of analog filter circuit based on genetic algorithm. IEEE Access 2020, 8, 8193–8201. [Google Scholar] [CrossRef]

- Deng, Y.; Liu, N. Soft fault diagnosis in analog circuits based on bispectral models. J. Electron. Test. 2017, 33, 543–557. [Google Scholar] [CrossRef]

- Li, Y.; Zhang, R.; Guo, Y.; Huan, P.; Zhang, M. Nonlinear soft fault diagnosis of analog circuits based on RCCA-SVM. IEEE Access 2020, 8, 60951–60963. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S. A new approach to multiple soft fault diagnosis of analog BJT and CMOS circuits. IEEE Trans. Instrum. Meas. 2015, 64, 2688–2695. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Hałgas, S. A method for local parametric fault diagnosis of a broad class of analog integrated circuits. IEEE Trans. Instrum. Meas. 2018, 67, 328–337. [Google Scholar] [CrossRef]

- Tadeusiewicz, M.; Kuczynski, A.; Hałgas, S. Catastrophic fault diagnosis of a certain class of nonlinear analog circuits. Circuits Syst. Signal Process. 2015, 34, 353–375. [Google Scholar] [CrossRef]

- Kladovscikov, L.; Jurgo, M.; Navickas, R. Desing of an oscillation-based BISTS system for active analog intergrated filters in 0.18 m CMOS. Electronics 2019, 8, 813. [Google Scholar] [CrossRef]

- Bindi, M.; Grasso, F.; Luchetta, A.; Manetti, S.; Piccirilli, M.C. Smart monitoring and fault diagnosis of joints in high voltage electrical transmission lines. In Proceedings of the 6th International Conference on Soft Computing & Machine Intelligence, Johannesburg, South Africa, 19–20 November 2019; pp. 40–44. [Google Scholar] [CrossRef]

- Binu, D.; Kariyappa, B.S.; Ride, N.N. A new rider optimization algorithm-based network for fault diagnosis in analog circuits. IEEE Trans. Instrum. Meas. 2019, 68, 2–26. [Google Scholar] [CrossRef]

- Yuan, L.; He, Y.; Huang, J.; Sun, Y. A new neural-network-based fault diagnosis approach for analog circuits by using kurtosis and entropy as a preprocessor. IEEE Trans. Instrum. Meas. 2010, 59, 586–595. [Google Scholar] [CrossRef]

- Paul, C.R. Analysis of Multiconductor Transmission Lines, 2nd ed.; John Wiley & Sons Inc.: New York, NY, USA, 2008. [Google Scholar]

- Tadeusiewicz, M.; Hałgas, S. A method for diagnosing soft short and open faults in distributed parameter multiconductor transmission lines. Electronics 2021, 10, 35. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).