Batch-Fabricated α-Si Assisted Nanogap Tunneling Junctions

Abstract

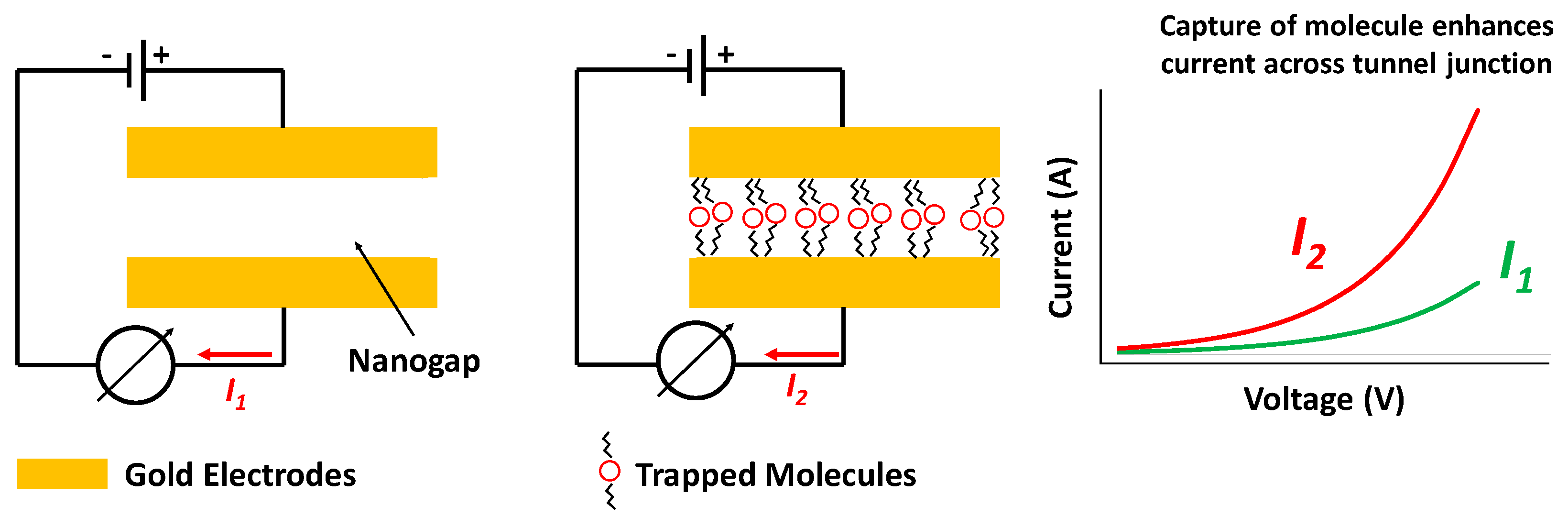

1. Introduction

2. Materials and Methods

2.1. Thin-Film Deposition and Characterization

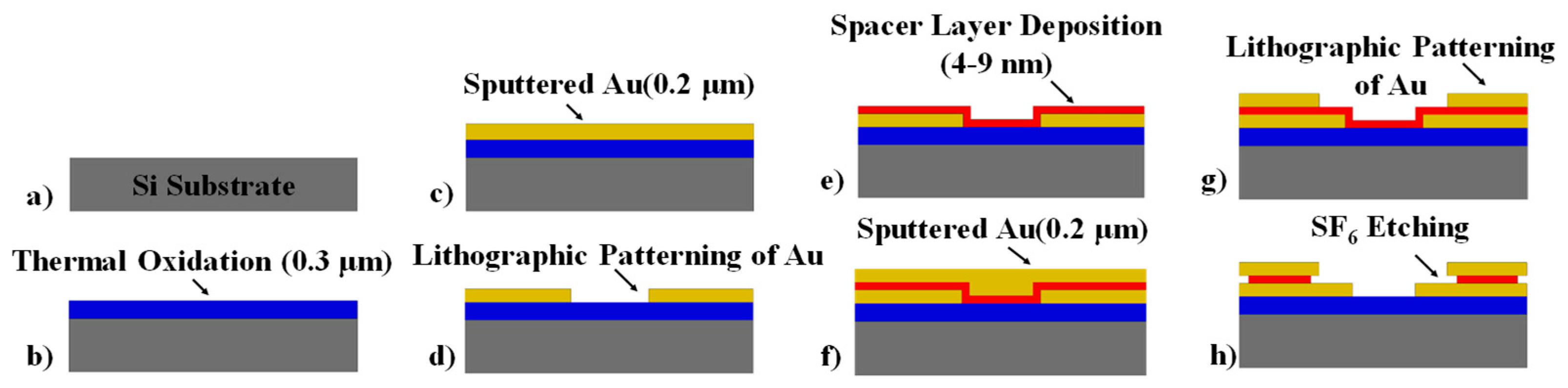

2.2. Device Structure, Design, and Fabrication

2.3. Choice of Spacer Stack: SiO2 As the Dielectric Material and Using α-Si As An Adhesive Layer

2.4. Imaging and Electrical Characterization of Nanogap Electrodes

3. Results and Discussion

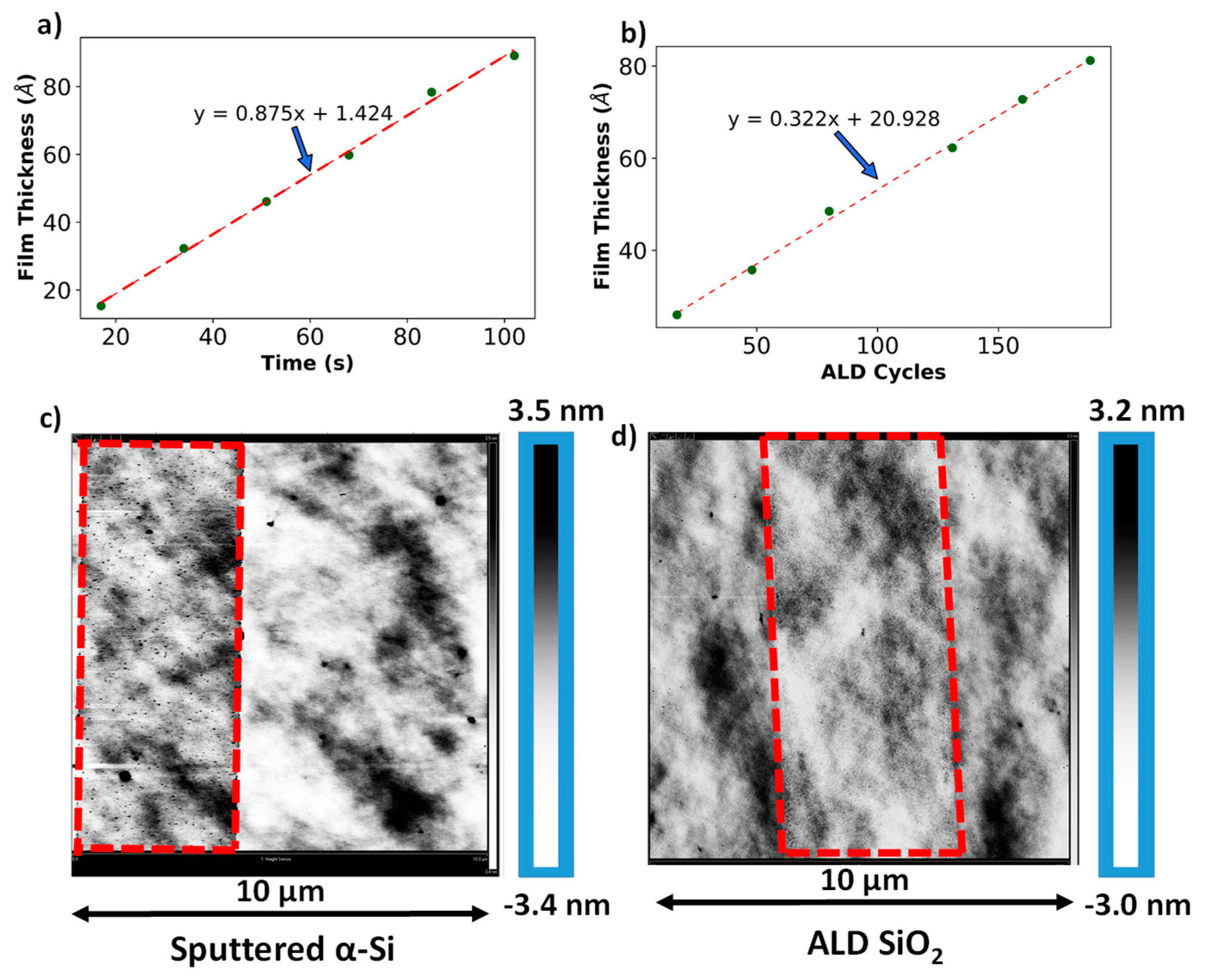

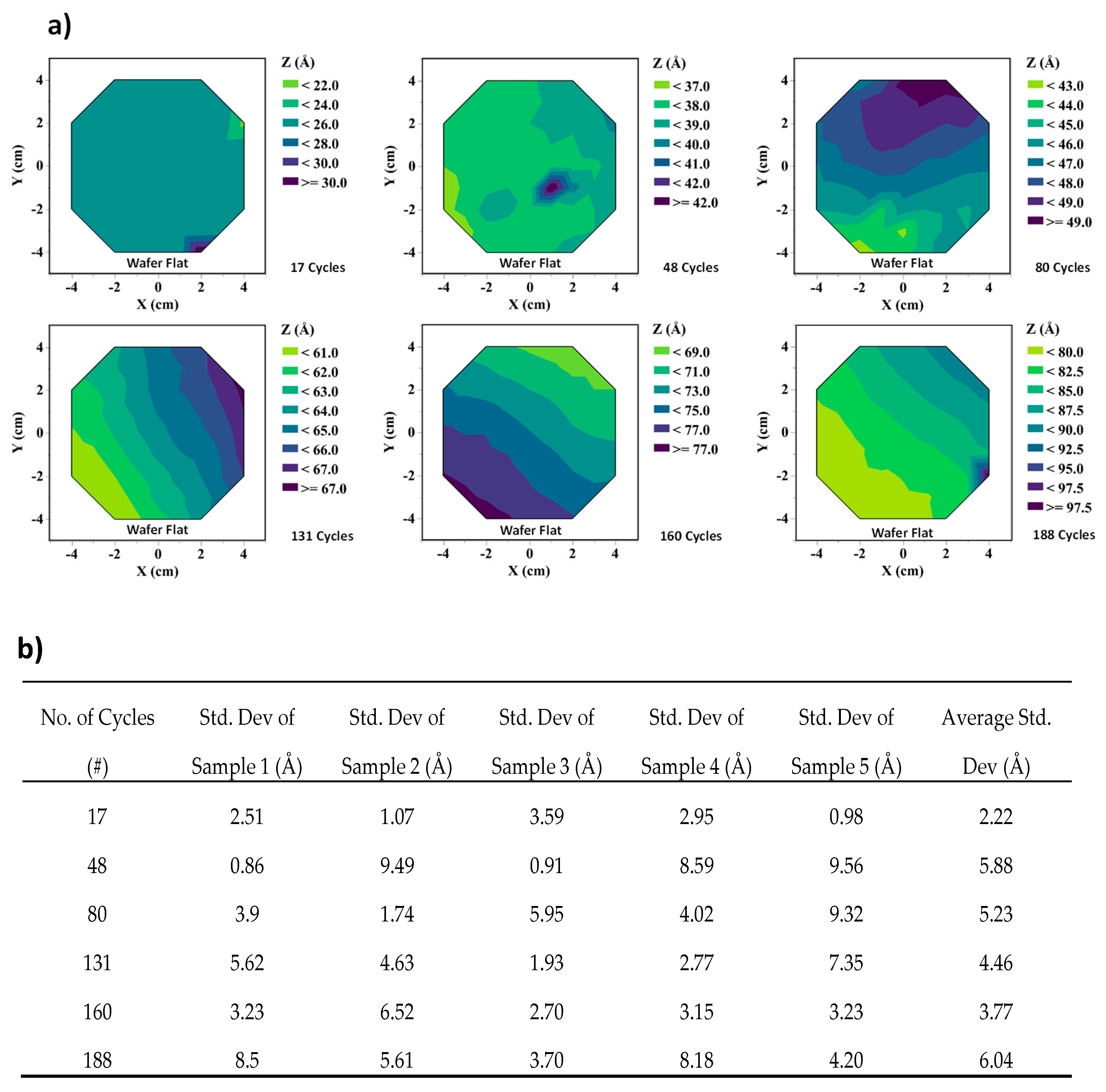

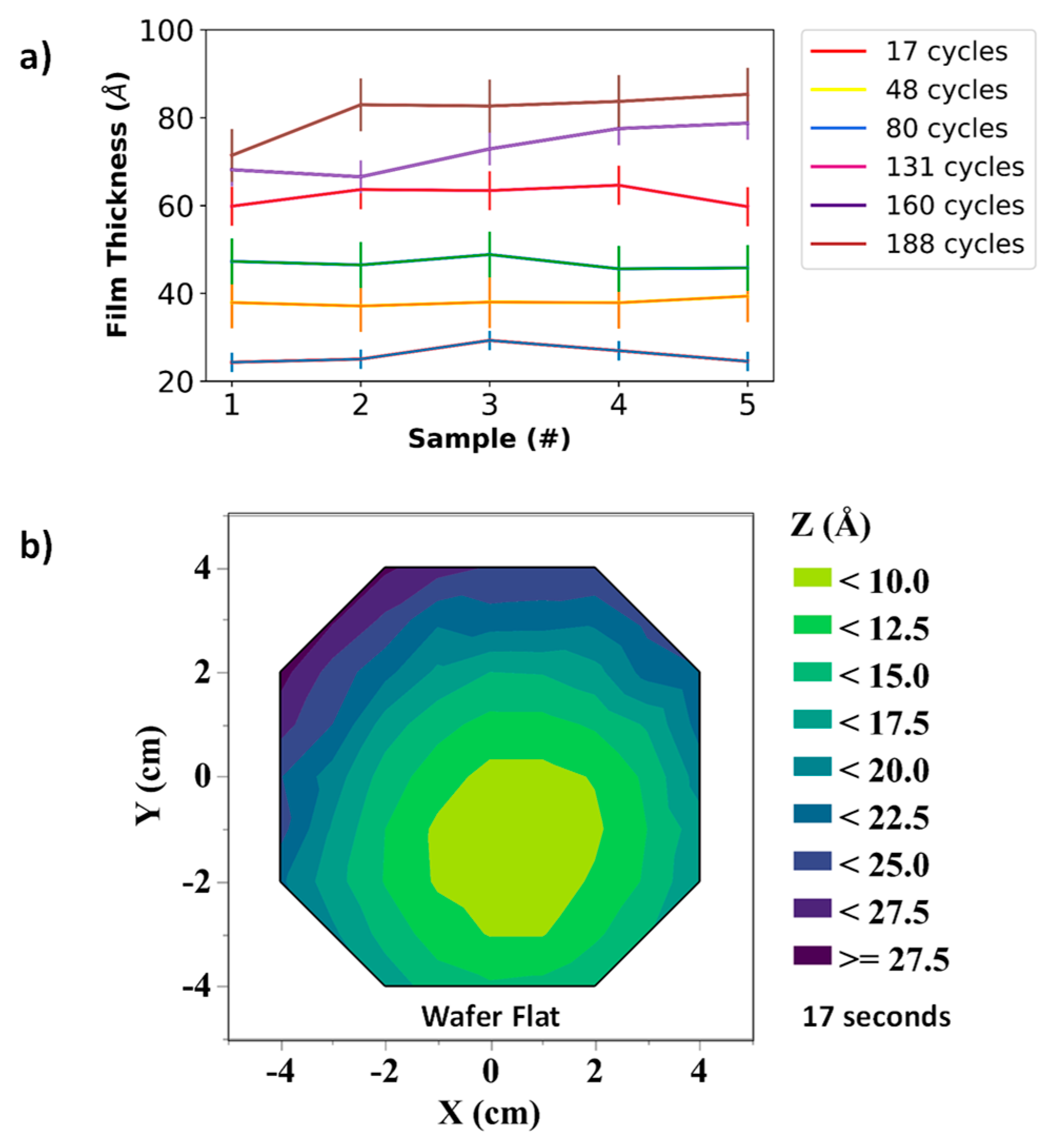

3.1. Sacrificial Film Characterization—Thickness Calibration Curves, Uniformity Measurements, and Surface Topology for SiO2 and α-Si Thin Films

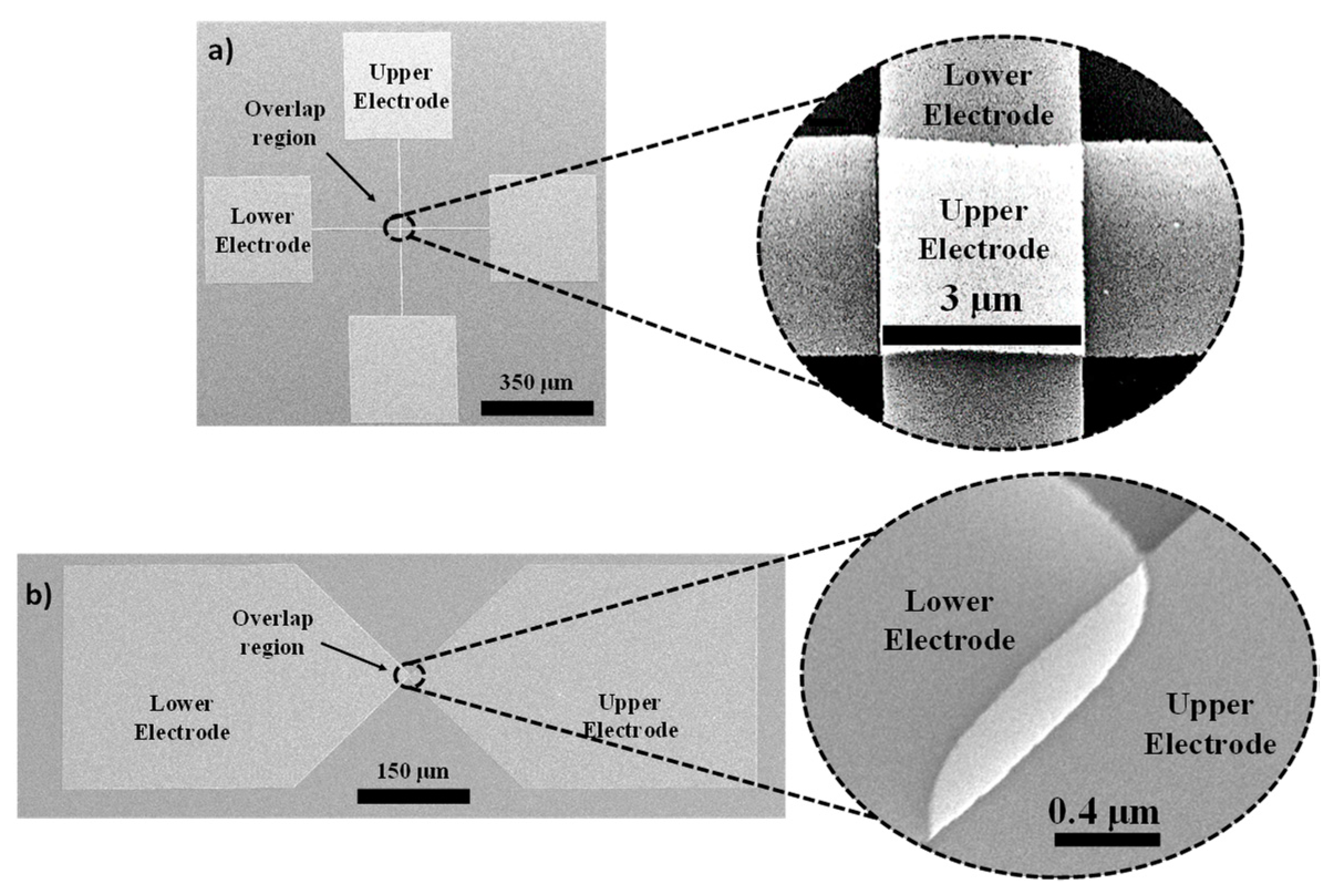

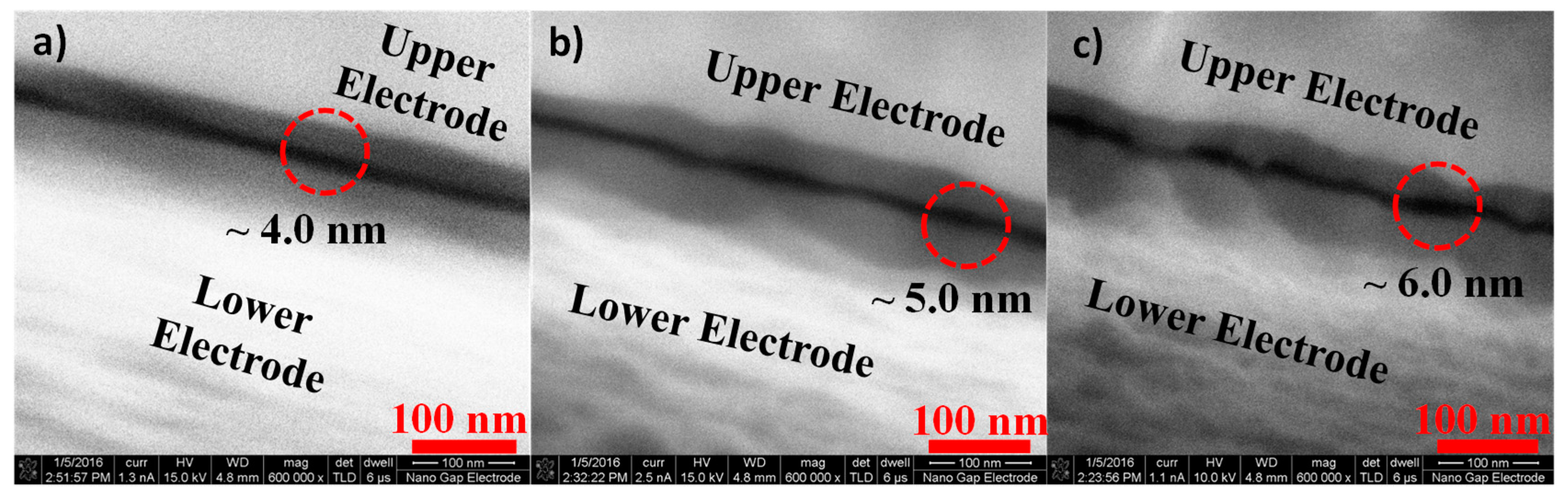

3.2. SEM Imaging

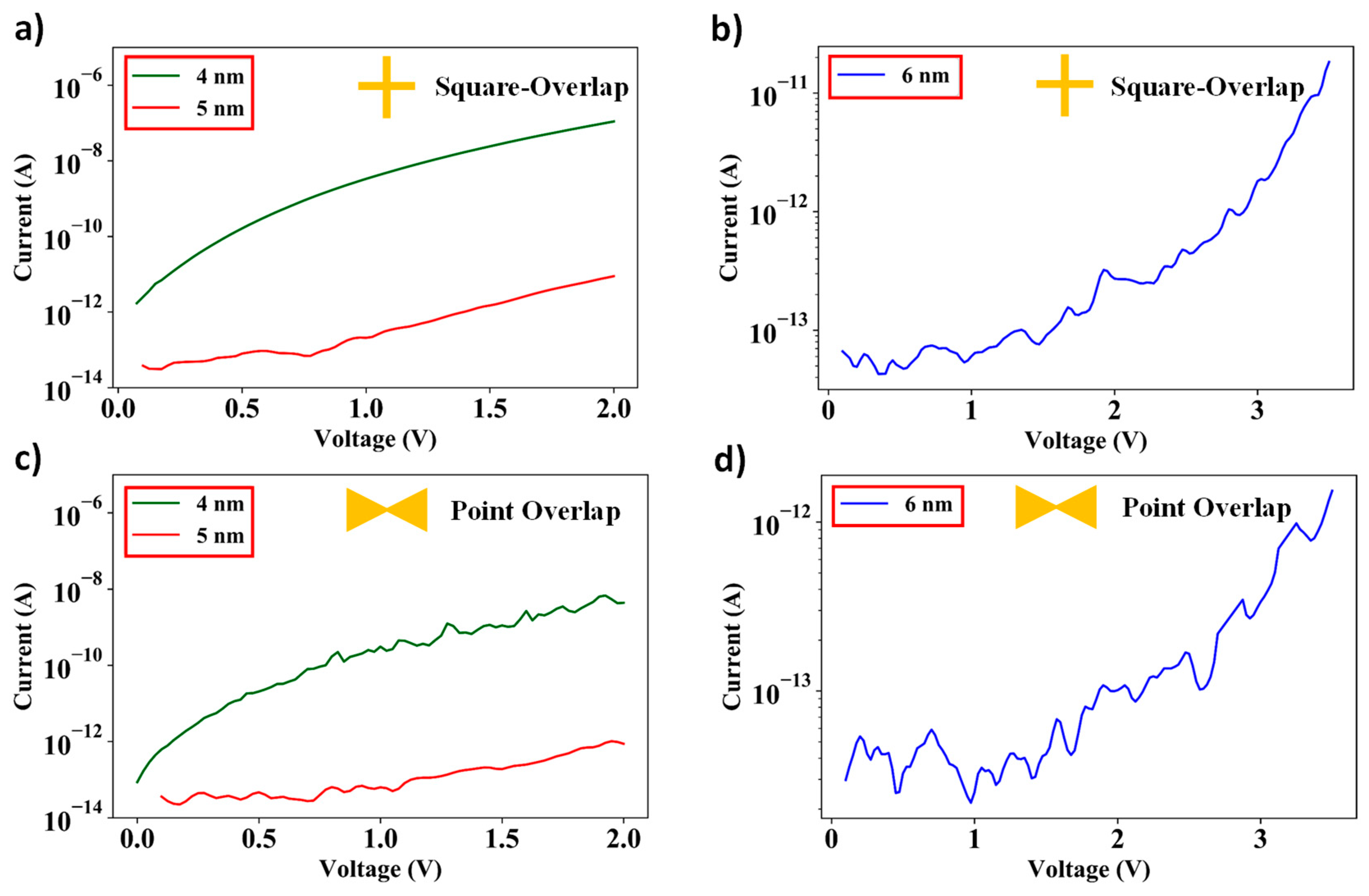

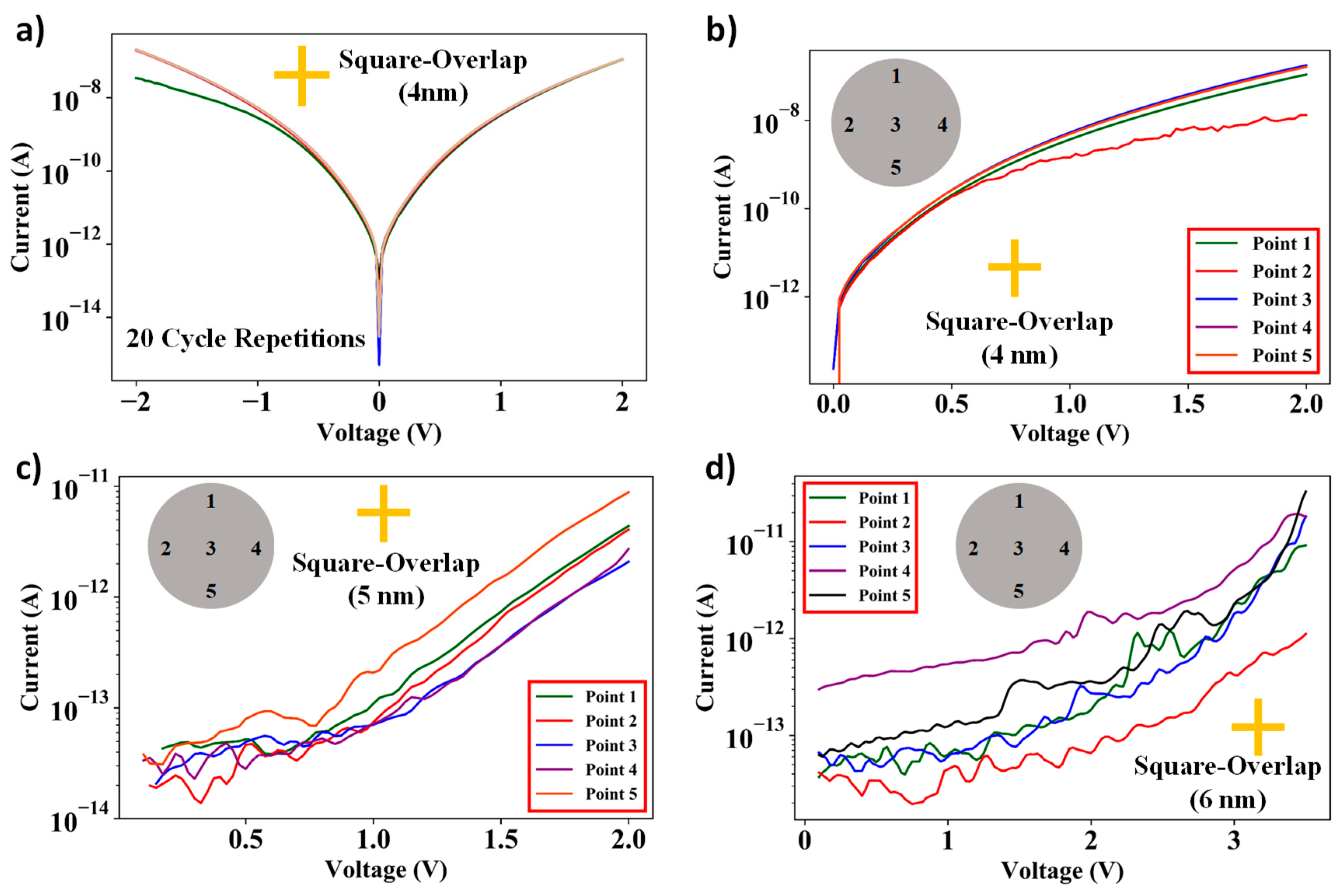

3.3. I–V Characteristics of Square-Overlap and Point-Overlap Layout Devices Across the Wafer

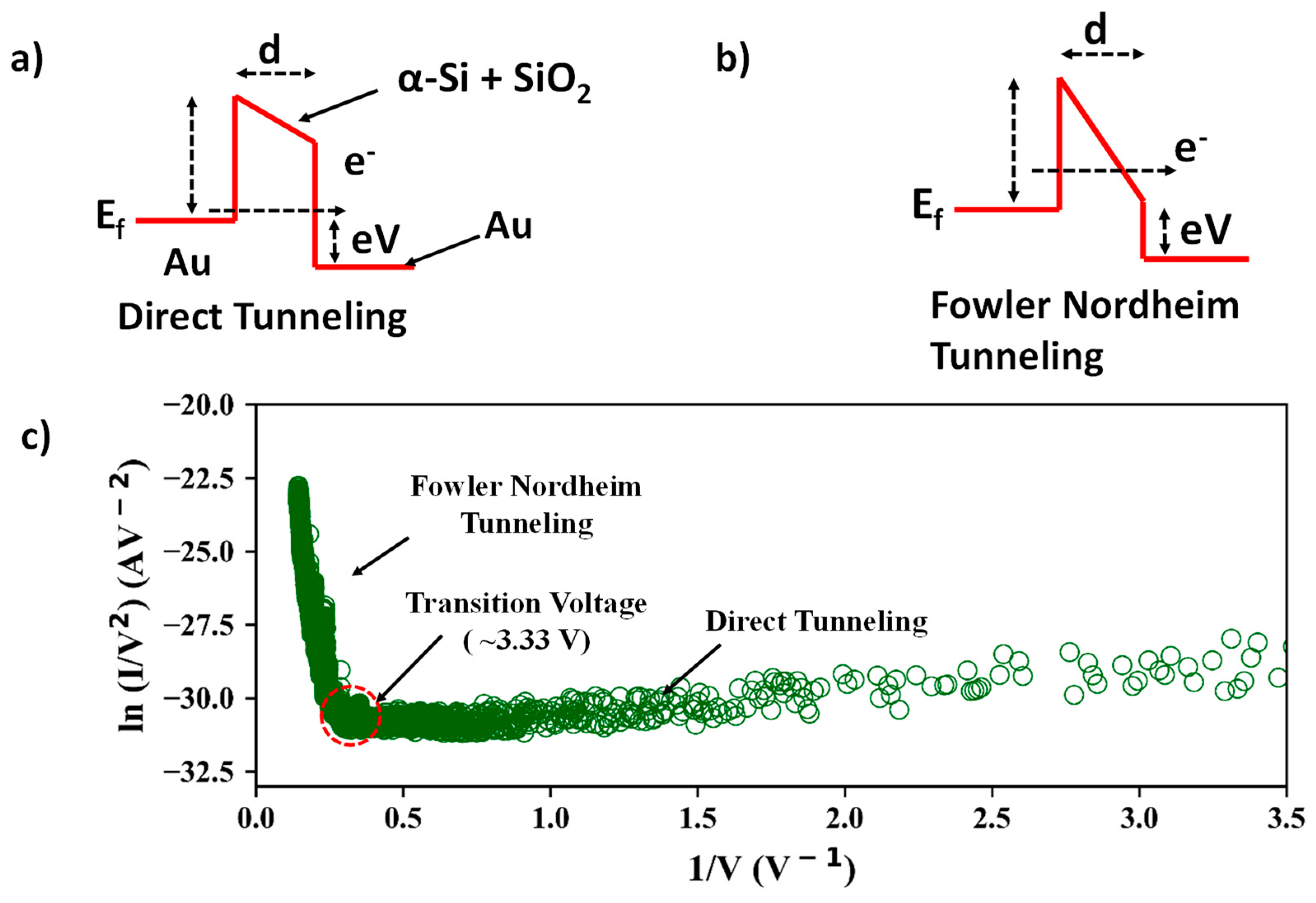

3.4. Tunneling Current Measurements and Transition from Direct Tunneling to Fowler–Nordheim Tunneling

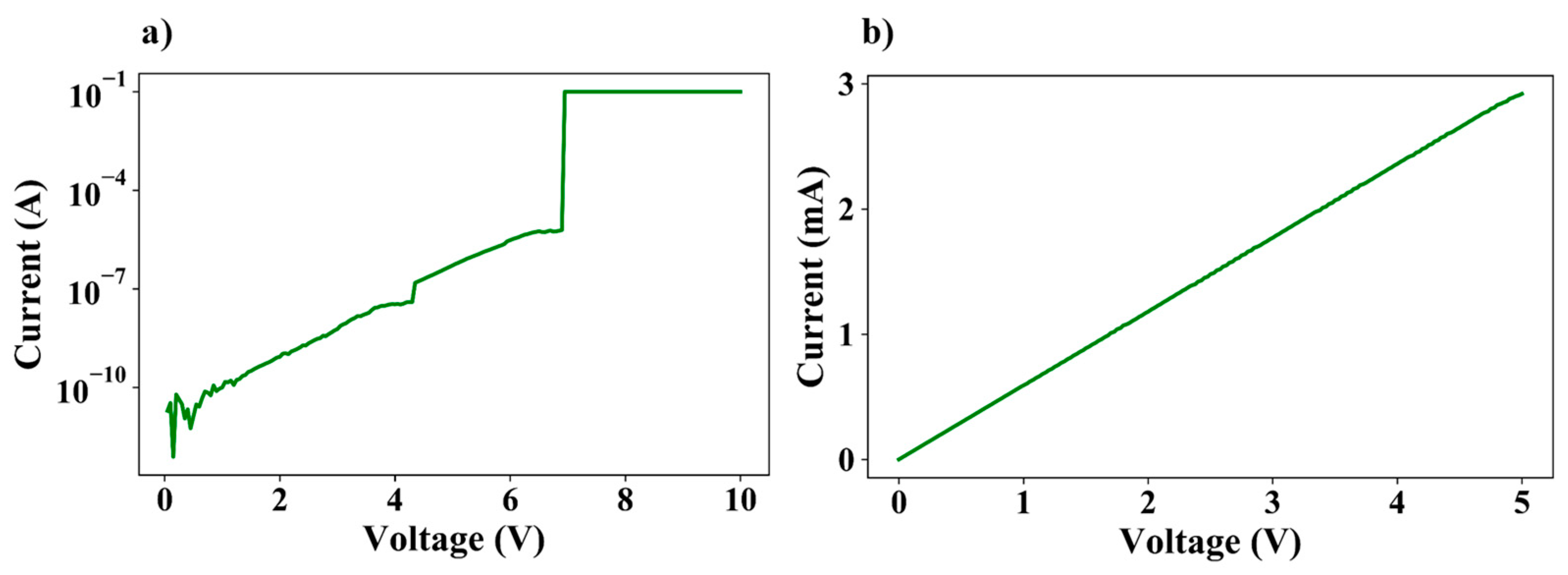

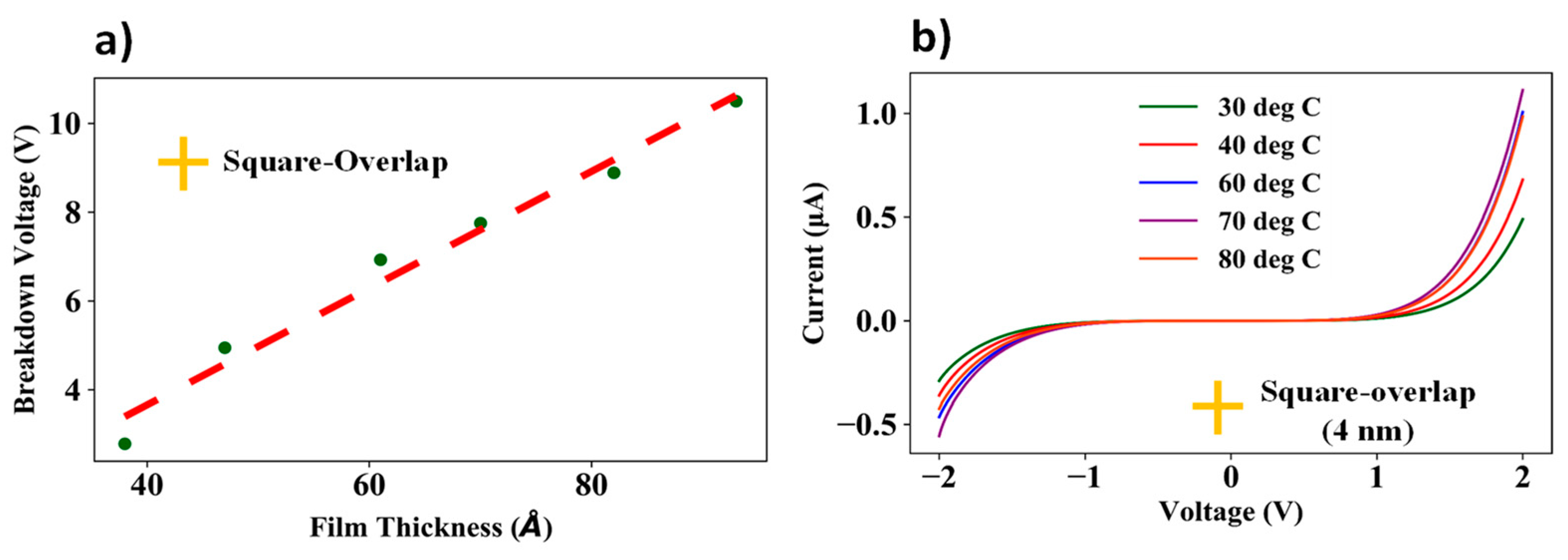

3.5. Dielectric Breakdown Measurements and I–V Measurements Across Various Temperatures

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Howell, S.W.; Dirk, S.M.; Childs, K.; Pang, H.; Blain, M.; Simonson, R.J.; Tour, M.J.; Wheeler, D.R. Mass-fabricated one-dimensional silicon nanogaps for hybrid organic/nanoparticle arrays. Nanotechnology 2005, 16, 754–758. [Google Scholar] [CrossRef]

- Tyagi, P.; Li, D.; Holmes, S.M.; Hinds, B.J. Molecular electrodes at the exposed edge of metal/insulator/metal trilayer structures. J. Am. Chem. Soc. 2007, 129, 4929–4938. [Google Scholar] [CrossRef] [PubMed]

- Ashwell, G.J.; Wierzchowiec, P.; Bartlett, C.J.; Buckle, P.D. Molecular electronics: Connection across nano-sized electrode gaps. Chem. Commun. 2007, 12, 1254–1256. [Google Scholar] [CrossRef]

- Chen, J.; Reed, M.A.; Rawlett, A.M.; Tour, J.M. Large on-off ratios and negative differential resistance in a molecular electronic device. Science 1999, 286, 1550–1552. [Google Scholar] [CrossRef] [PubMed]

- Akkerman, H.B.; Blom, P.W.M.; de Leeuw, D.M.; de Boer, B. Towards molecular electronics with large-area molecular junctions. Nature 2006, 441, 69. [Google Scholar] [CrossRef] [PubMed]

- Cui, X.D.; Zarate, X.; Tomfohr, J.; Sankey, O.F.; Primak, A.; Moore, A.L.; Gust, D.; Harris, G.; Lindsay, S.M. Making electrical contacts to molecular monolayers. Nanotechnology 2001, 13, 5–14. [Google Scholar] [CrossRef]

- Kim, J.-H.; Moon, H.; Yoo, S.; Choi, Y.-K. Nanogap electrode fabrication for a nanoscale device by volume-expanding electrochemical synthesis. Small 2011, 7, 2210–2216. [Google Scholar] [CrossRef]

- Dolan, G.J. Offset masks for lift-off photoprocessing. Appl. Phys. Lett. 1977, 31, 337–339. [Google Scholar] [CrossRef]

- Los Santos Valladares, L.D.; Felix, L.L.; Dominguez, A.B.; Mitrelias, T.; Sfigakis, F.; Khondaker, S.I.; Barnes, C.H.W.; Majima, Y. Controlled electroplating and electromigration in nickel electrodes for nanogap formation. Nanotechnology 2010, 21, 445304. [Google Scholar] [CrossRef] [PubMed]

- Hatzor, A.; Weiss, P.S. Molecular rulers for scaling down nanostructures. Science 2001, 291, 1019. [Google Scholar]

- Horiuchi, K.; Kato, T.; Hashii, S.; Hashimoto, A.; Sasaki, T.; Aoki, N.; Ochiai, Y. Fabrication of nanoscale C60 field-effect transistors with carbon nanotubes. Appl. Phys. Lett. 2005, 86, 153108. [Google Scholar] [CrossRef]

- Guo, X.; Small, J.P.; Klare, J.E.; Wang, Y.; Purewal, M.S.; Tam, I.W.; Hong, B.H.; Caldwell, R.; Huang, L.; O’Brien, S.; et al. Covalently bridging gaps in single-walled carbon nanotubes with conducting molecules. Science 2006, 311, 356. [Google Scholar] [CrossRef] [PubMed]

- Li, T.; Hu, W.; Zhu, D. Nanogap electrodes: Nanogap electrodes. Adv. Mater. 2010, 22, 286–300. [Google Scholar] [CrossRef]

- Tyagi, P. Multilayer edge molecular electronics devices: A review. J. Mater. Chem. 2011, 21, 4733–4742. [Google Scholar] [CrossRef]

- Banerjee, A.; Farhoudi, N.; Ghosh, C.; Mastrangelo, C.H.; Kim, H.; Broadbent, S.J.; Looper, R. Picowatt gas sensing and resistance switching in tunneling nano-gap electrodes. In Proceedings of the 2016 IEEE SENSORS, Orlando, FL, USA, 30 October–3 November 2016. [Google Scholar]

- Ghosh, C.; Khan, S.H.; Broadbent, S.J.; Hsieh, H.C.; Noh, S.; Banerjee, A.; Farhoudi, N.; Mastrangelo, C.H.; Looper, R.; Kim, H. Nano-gap vapor sensor. In Proceedings of the 2017 IEEE SENSORS, Glasgow, UK, 29 October–1 November 2017. [Google Scholar]

- Banerjee, A.; Ghosh, T.; Likhite, R.; Hasan, N.; Kim, H.; Mastrangelo, C.H. Electrical detection of proteins using batch-fabricated vertical metal nanogap break-junctions. In Proceedings of the 20th International Conference on Miniaturized Systems for Chemistry and Life Sciences, Dublin, Ireland, 9–13 October 2016. [Google Scholar]

- Khan, S.H.; Jung, Y.J.; Hsieh, H.C.; Wu, T.; Mastrangelo, C.H.; Kim, H.; Broadbent, S.J.; Looper, R. Ultra-low-power chemical sensor node. In Proceedings of the GOMAC Tech. 2018, Miami, FL, USA, 12–15 March 2018. [Google Scholar]

- Banerjee, A.; Pandey, S.S.; Banerjee, N.; Hasan, N.; Mastrangelo, C.H. A milli-volt triggered MEMS paddle switch. In Proceedings of the 2015 IEEE SENSORS, Busan, Korea, 1–4 November 2015. [Google Scholar]

- Likhite, R.; Banerjee, A.; Kim, H.; Mastrangelo, C.H. Self-leveling micromechanical gas sensors. In Proceedings of the 2018 IEEE SENSORS, New Delhi, India, 28–31 October 2018. [Google Scholar]

- Likhite, R.; Pandey, S.S.; Banerjee, A.; Kim, H.; Mastrangelo, C.H. Amplified chemomechanical comb gas sensor. In Proceedings of the 2016 IEEE SENSORS, Orlando, FL, USA, 30 October–3 November 2016. [Google Scholar]

- Pandey, S.S.; Banerjee, N.; Banerjee, A.; Hasan, N.; Kim, H.; Mastrangelo, C.H. High-sensitivity parametrically amplified chemo-mechanical vapor sensors. In Proceedings of the 2015 IEEE SENSORS, Busan, Korea, 1–4 November 2015. [Google Scholar]

- Han, B.; Lee, S.-W.; Park, K.; Park, C.-O.; Rha, S.-K.; Lee, W.-J. The electrical properties of dielectric stacks of SiO2 and Al2O3 prepared by atomic layer deposition method. Curr. Appl. Phys. 2012, 12, 434–436. [Google Scholar] [CrossRef]

- George, M.A.; Bao, Q.C.; Sorensen, W.I.; Glaunsinger, W.S. Thermally induced changes in the resistance, microstructure, and adhesion of thin gold films on Si/SiO2 substrates. J. Vac. Sci. Technol. A 1990, 8, 1491–1497. [Google Scholar] [CrossRef]

- Valitova, I.; Amato, M.; Mahvash, F.; Cantele, G.; Maffuci, A.; Santato, C.; Martel, R.; Cicoira, F. Carbon nanotube electrodes in organic transistors. Nanoscale 2013, 5, 4638–4646. [Google Scholar] [CrossRef]

- Ikuno, T.; Okamoto, H.; Sugiyama, Y.; Nakano, H.; Yamada, F.; Kamiya, I. Electron transport properties of Si nanosheets: Transition from direct tunneling to Fowler-Nordheim tunneling. Appl. Phys. Lett. 2011, 99, 023107. [Google Scholar] [CrossRef]

- O’Dwyer, J.J. Theory of Electrical Conduction and Breakdown in Solid Dielectrics (Monographs on the Physics & Chemistry of Materials); Oxford University Press: Oxford, UK, 1973. [Google Scholar]

- Simmons, J.G. Generalized formula for the electric tunnel effect between similar electrodes separated by a thin insulating film. J. Appl. Phys. 1963, 34, 1793–1803. [Google Scholar] [CrossRef]

- Joshi, P.C.; Voutsas, A.T.; Hartzell, J.W. High density plasma growth of thermal quality SiO2 thin films. In Electrochemical Society Proceedings; The Electrochemical Society, Inc.: Pennington, NJ, USA, 2005. [Google Scholar]

- Verweij, J.F.; Klootwijk, J.H. Dielectric breakdown I: A review of oxide breakdown. Microelectr. J. 1996, 27, 611–622. [Google Scholar] [CrossRef]

- Usui, T.; Donnelly, C.A.; Logar, M.; Sinclair, R.; Schoonman, J.; Prinz, F.B. Approaching the limits of dielectric breakdown for SiO2 films deposited by plasma-enhanced atomic layer deposition. Acta Mater. 2013, 61, 7660–7670. [Google Scholar] [CrossRef]

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Banerjee, A.; Khan, S.-U.H.; Broadbent, S.; Likhite, R.; Looper, R.; Kim, H.; Mastrangelo, C.H. Batch-Fabricated α-Si Assisted Nanogap Tunneling Junctions. Nanomaterials 2019, 9, 727. https://doi.org/10.3390/nano9050727

Banerjee A, Khan S-UH, Broadbent S, Likhite R, Looper R, Kim H, Mastrangelo CH. Batch-Fabricated α-Si Assisted Nanogap Tunneling Junctions. Nanomaterials. 2019; 9(5):727. https://doi.org/10.3390/nano9050727

Chicago/Turabian StyleBanerjee, Aishwaryadev, Shakir-Ul Haque Khan, Samuel Broadbent, Rugved Likhite, Ryan Looper, Hanseup Kim, and Carlos H. Mastrangelo. 2019. "Batch-Fabricated α-Si Assisted Nanogap Tunneling Junctions" Nanomaterials 9, no. 5: 727. https://doi.org/10.3390/nano9050727

APA StyleBanerjee, A., Khan, S.-U. H., Broadbent, S., Likhite, R., Looper, R., Kim, H., & Mastrangelo, C. H. (2019). Batch-Fabricated α-Si Assisted Nanogap Tunneling Junctions. Nanomaterials, 9(5), 727. https://doi.org/10.3390/nano9050727