Design of a Capacitorless DRAM Based on a Polycrystalline-Silicon Dual-Gate MOSFET with a Fin-Shaped Structure

Abstract

1. Introduction

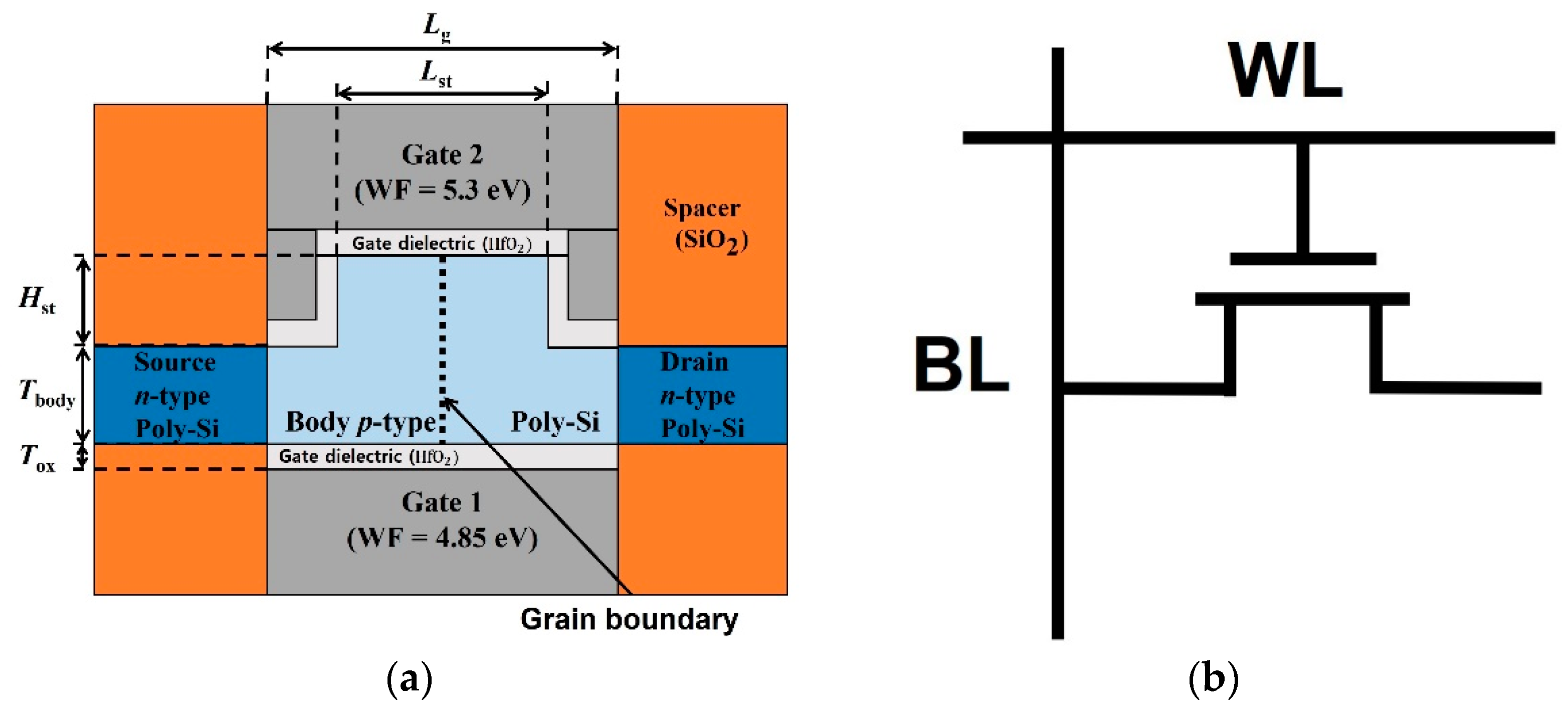

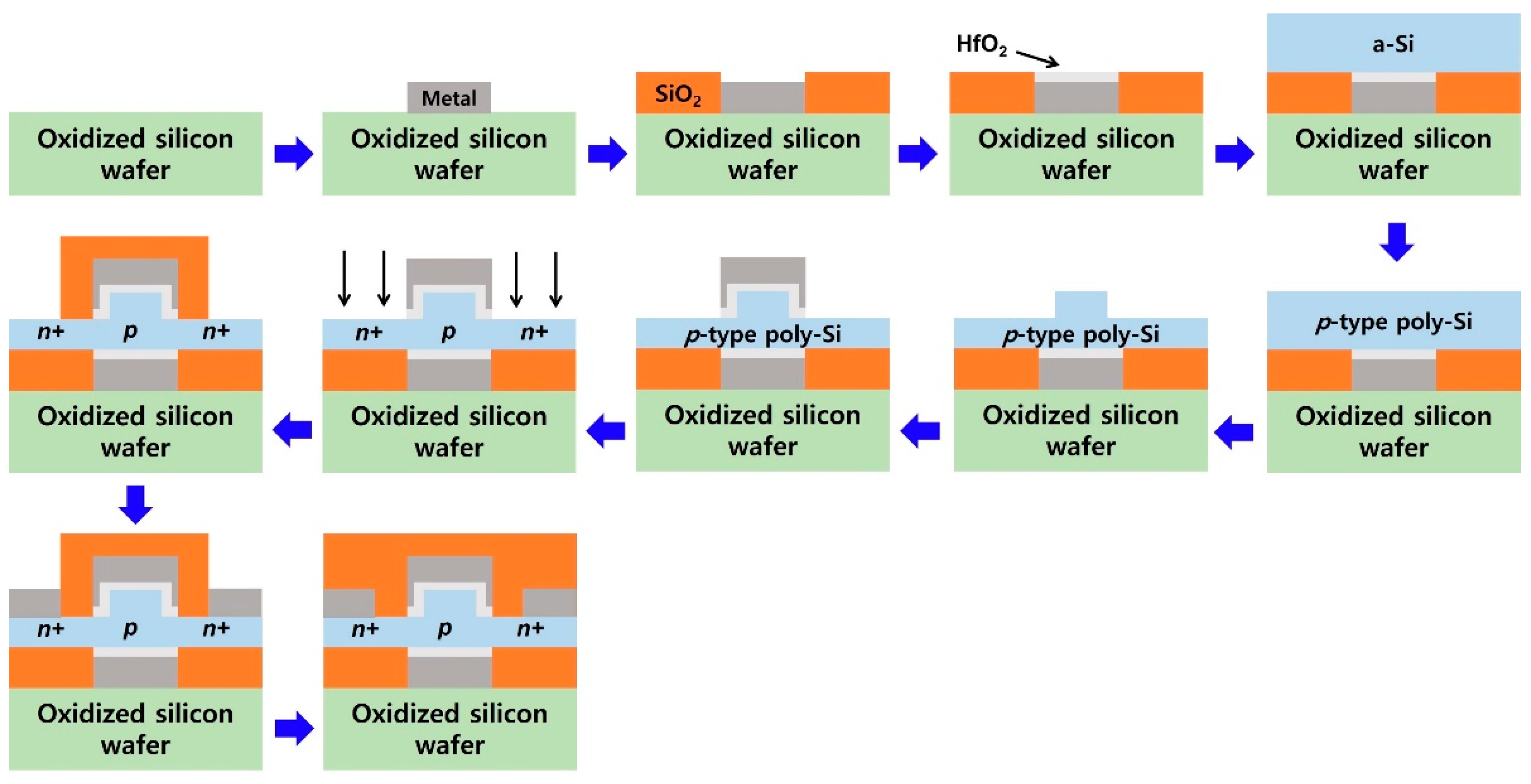

2. Device Structure and Simulation Method

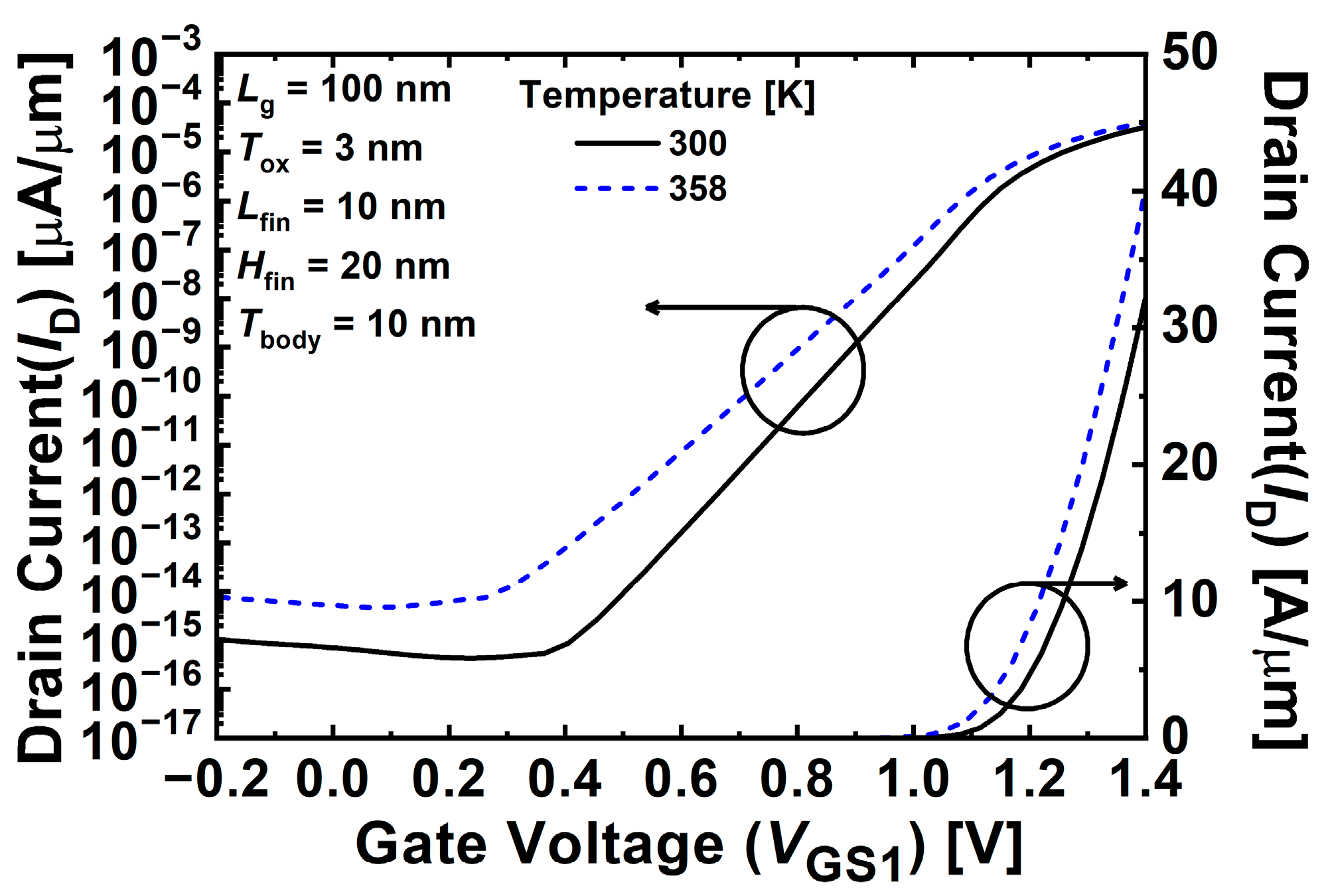

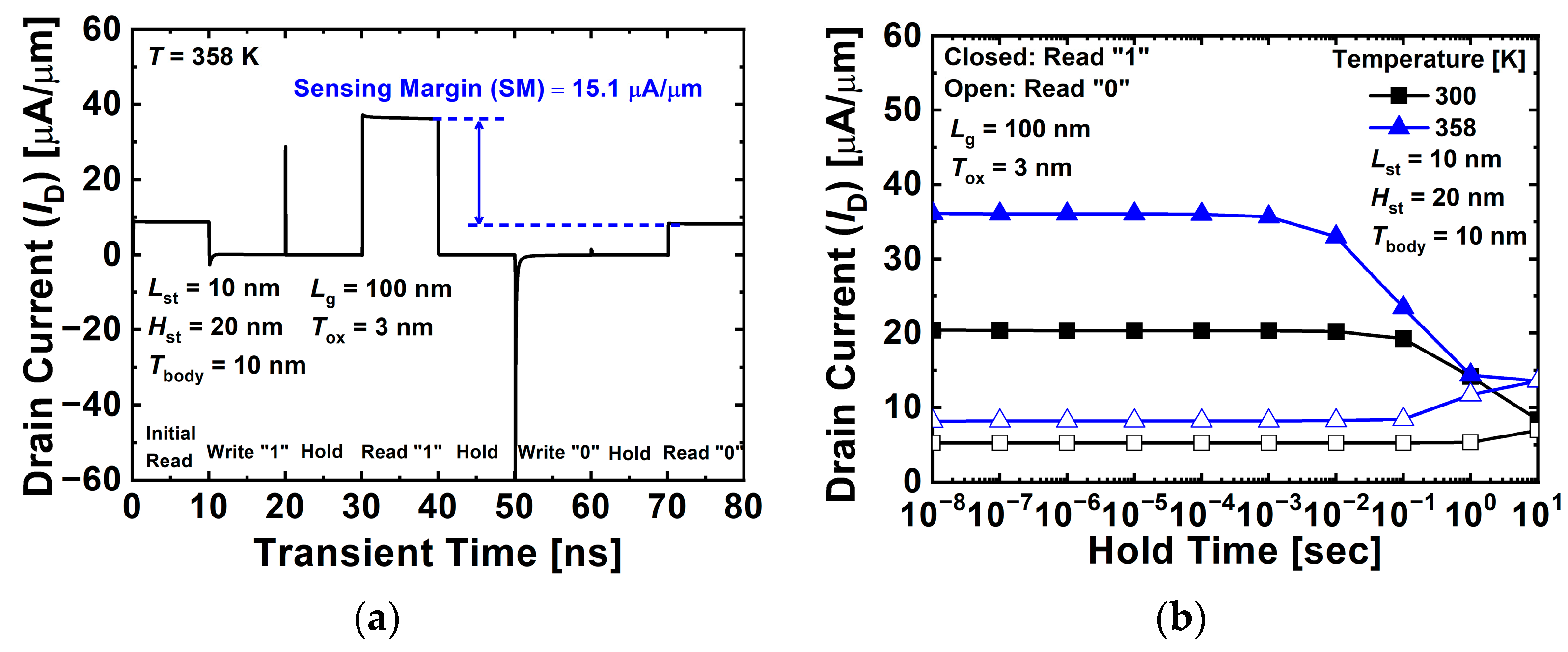

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Yang, H.Y.; Chang, C.M.; Chao MC, T.; Huang, R.F.; Lin, S.C. Testing methodology of embedded DRAMs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 2011, 20, 1715–1728. [Google Scholar] [CrossRef]

- Spessot, A.; Oh, H. 1T-1C Dynamic Random Access Memory Status, Challenges, and Prospects. IEEE Trans. Electron Devices 2020, 67, 1382–1393. [Google Scholar] [CrossRef]

- Koyanagi, M. The Stacked Capacitor DRAM Cell and Three-Dimensional Memory. IEEE Solid-State Circuits Soc. Newsl. 2008, 13, 37–41. [Google Scholar] [CrossRef]

- Mueller, W.; Aichmayr, G.; Bergner, W.; Erben, E.; Hecht, T.; Kapteyn, C.; Kersch, A.; Kudelka, S.; Lau, F.; Luetzen, J.; et al. Challenges for the DRAM cell scaling to 40 nm. In Proceedings of the IEEE International Electron Devices Meeting, 2005. IEDM Technical Digest, Washington, DC, USA, 5 December 2005; Volume 4, p. 339. [Google Scholar]

- Sunami, H. The Role of the Trench Capacitor in DRAM Innovation. IEEE Solid-State Circuits Soc. Newsl. 2008, 13, 42–44. [Google Scholar] [CrossRef]

- Ansari, M.H.R.; Singh, J. Capacitorless 2T-DRAM for higher retention time and sense margin. IEEE Trans. Electron Devices 2020, 67, 902–906. [Google Scholar] [CrossRef]

- Lin, J.-T.; Lin, H.-H.; Chen, Y.-J.; Yu, C.-Y.; Kranti, A.; Lin, C.-C.; Lee, W.-H. Vertical Transistor with n-Bridge and Body on Gate for Low-Power 1T-DRAM Application. IEEE Trans. Electron Devices 2017, 64, 4937–4945. [Google Scholar] [CrossRef]

- Ansari, M.H.R.; Cho, S. Performance improvement of 1T DRAM by raised source and drain engineering. IEEE Trans. Electron Devices 2021, 68, 1577–1584. [Google Scholar] [CrossRef]

- Han, J.-W.; Ryu, S.-W.; Kim, S.; Kim, C.-J.; Ahn, J.-H.; Choi, S.-J.; Kim, J.S.; Kim, K.H.; Lee, G.S.; Oh, J.S.; et al. A Bulk FinFET Unified-RAM (URAM) Cell for Multifunctioning NVM and Capacitorless 1T-DRAM. IEEE Electron Device Lett. 2008, 29, 632–634. [Google Scholar] [CrossRef]

- Bawedin, M.; Cristoloveanu, S.; Flandre, D. A Capacitorless 1T-DRAM on SOI Based on Dynamic Coupling and Double-Gate Operation. IEEE Electron Device Lett. 2008, 29, 795–798. [Google Scholar] [CrossRef]

- Cristoloveanu, S.; Lee, K.; Parihar, M.; El Dirani, H.; Lacord, J.; Martinie, S.; Le Royer, C.; Barbe, J.-C.; Mescot, X.; Fonteneau, P.; et al. A review of the Z 2 -FET 1T-DRAM memory: Operation mechanisms and key parameters. Solid-State Electron. 2017, 143, 10–19. [Google Scholar] [CrossRef]

- Navlakha, N.; Lin, J.-T.; Kranti, A. Improved Retention Time in Twin Gate 1T DRAM with Tunneling Based Read Mechanism. IEEE Electron Device Lett. 2016, 37, 1127–1130. [Google Scholar] [CrossRef]

- Kamal, N.; Kamal, A.K.; Singh, J. L-Shaped Tunnel Field-Effect Transistor-Based 1T DRAM with Improved Read Current Ratio, Retention Time, and Sense Margin. IEEE Trans. Electron Devices 2021, 68, 2705–2711. [Google Scholar] [CrossRef]

- Lin, J.-T.; Lin, P.-H.; Eng, Y.-C.; Chen, Y.-R. Novel Vertical SOI-Based 1T-DRAM with Trench Body Structure. IEEE Trans. Electron Devices 2013, 60, 1872–1877. [Google Scholar] [CrossRef]

- Lee, W.; Choi, W.Y. A Novel Capacitorless 1T DRAM Cell for Data Retention Time Improvement. IEEE Trans. Nanotechnol. 2010, 10, 462–466. [Google Scholar] [CrossRef]

- Ansari, H.R.; Navlakha, N.; Lin, J.-T.; Kranti, A. 1T-DRAM with Shell-Doped Architecture. IEEE Trans. Electron Devices 2018, 66, 428–435. [Google Scholar] [CrossRef]

- Ansari, H.R.; Navlakha, N.; Lee, J.Y.; Cho, S. Double-Gate Junctionless 1T DRAM with Physical Barriers for Retention Improvement. IEEE Trans. Electron Devices 2020, 67, 1471–1479. [Google Scholar] [CrossRef]

- Choi, K.R.; Lee, C.H.; Kim, S.J.; Enomoto, H.; Shim, T.H.; Cho, W.J.; Park, J.G. Dependence of memory margin of Cap-less memory cells on top Si thickness. Appl. Phys. Lett. 2009, 94, 023508. [Google Scholar] [CrossRef]

- Okhonin, S.; Nagoga, M.; Sallese, J.; Fazan, P. A capacitor-less 1T-DRAM cell. IEEE Electron Device Lett. 2002, 23, 85–87. [Google Scholar] [CrossRef]

- Blagojevic, M.; Kayal, M.; Pastre, M.; Harik, L.; Declercq, M.; Okhonin, S.; Fazan, P. Capacitorless 1T DRAM Sensing Scheme With Automatic Reference Generation. IEEE J. Solid-State Circuits 2006, 41, 1463–1470. [Google Scholar] [CrossRef]

- Michaelson, H.B. The work function of the elements and its periodicity. J. Appl. Phys. 1977, 48, 4729–4733. [Google Scholar] [CrossRef]

- Polishchuk, I.; Ranade, P.; King, T.-J.; Hu, C. Dual work function metal gate CMOS technology using metal interdiffusion. IEEE Electron Device Lett. 2001, 22, 444–446. [Google Scholar] [CrossRef]

- Lee, I.-C.; Tsai, T.-C.; Tsai, C.-C.; Yang, P.-Y.; Wang, C.-L.; Cheng, H.-C. High-performance vertically stacked bottom-gate and top-gate polycrystalline silicon thin-film transistors for three-dimensional integrated circuits. Solid-State Electron. 2012, 77, 26–30. [Google Scholar] [CrossRef]

- Seo, J.H.; Yoon, Y.J.; Yu, E.; Sun, W.; Shin, H.; Kang, I.M.; Lee, J.-H.; Cho, S. Fabrication and characterization of a thin-body poly-Si 1T DRAMwith charge-trap effect. IEEE Electron Device Lett. 2019, 40, 566–569. [Google Scholar] [CrossRef]

- Lin, J.-T.; Lee, W.-H.; Lin, P.-H.; Haga, S.W.; Chen, Y.-R.; Kranti, A. A New Electron Bridge Channel 1T-DRAM Employing Underlap Region Charge Storage. IEEE J. Electron Devices Soc. 2016, 5, 59–63. [Google Scholar] [CrossRef]

- Lin, J.-T.; Sun, W.-T.; Lin, H.-H.; Chen, Y.-J.; Navlakha, N.; Kranti, A. Raised Body Doping-Less 1T-DRAM With Source/Drain Schottky Contact. IEEE J. Electron Devices Soc. 2019, 7, 276–281. [Google Scholar] [CrossRef]

- Lahgere, A.; Kumar, M.J. 1-T Capacitorless DRAM Using Bandgap-Engineered Silicon-Germanium Bipolar I-MOS. IEEE Trans. Electron Devices 2017, 64, 1–8. [Google Scholar] [CrossRef]

- Lin, J.-T.; Lin, P.-H.; Haga, S.W.; Wang, Y.-C.; Lu, D.-R. Transient and Thermal Analysis on Disturbance Immunity for 4 F2 Surrounding Gate 1T-DRAM with Wide Trenched Body. IEEE Trans. Electron Devices 2014, 62, 61–68. [Google Scholar] [CrossRef]

- Cho, M.S.; Mun, H.J.; Lee, S.H.; Jang, J.; Bae, J.-H.; Kang, I.M. Simulation of capacitorless dynamic random access memory based on junctionless FinFETs using grain boundary of polycrystalline silicon. Appl. Phys. A 2020, 126, 1–10. [Google Scholar] [CrossRef]

- Yoon, Y.J.; Cho, M.S.; Kim, B.G.; Seo, J.H.; Kang, I.M. Capacitorless One-Transistor Dynamic Random-Access Memory Based on Double-Gate Metal-Oxide-Semiconductor Field-Effect Transistor with Si/SiGe Heterojunction and Underlap Structure for Improvement of Sensing Margin and Retention Time. J. Nanosci. Nanotechnol. 2019, 19, 6023–6030. [Google Scholar] [CrossRef]

- Lee, S.H.; Jang, W.D.; Yoon, Y.J.; Seo, J.H.; Mun, H.J.; Cho, M.S.; Jang, J.; Bae, J.-H.; Kang, I.M. Polycrystalline-Silicon-MOSFET-Based Capacitorless DRAM With Grain Boundaries and Its Performances. IEEE Access 2021, 9, 50281–50290. [Google Scholar] [CrossRef]

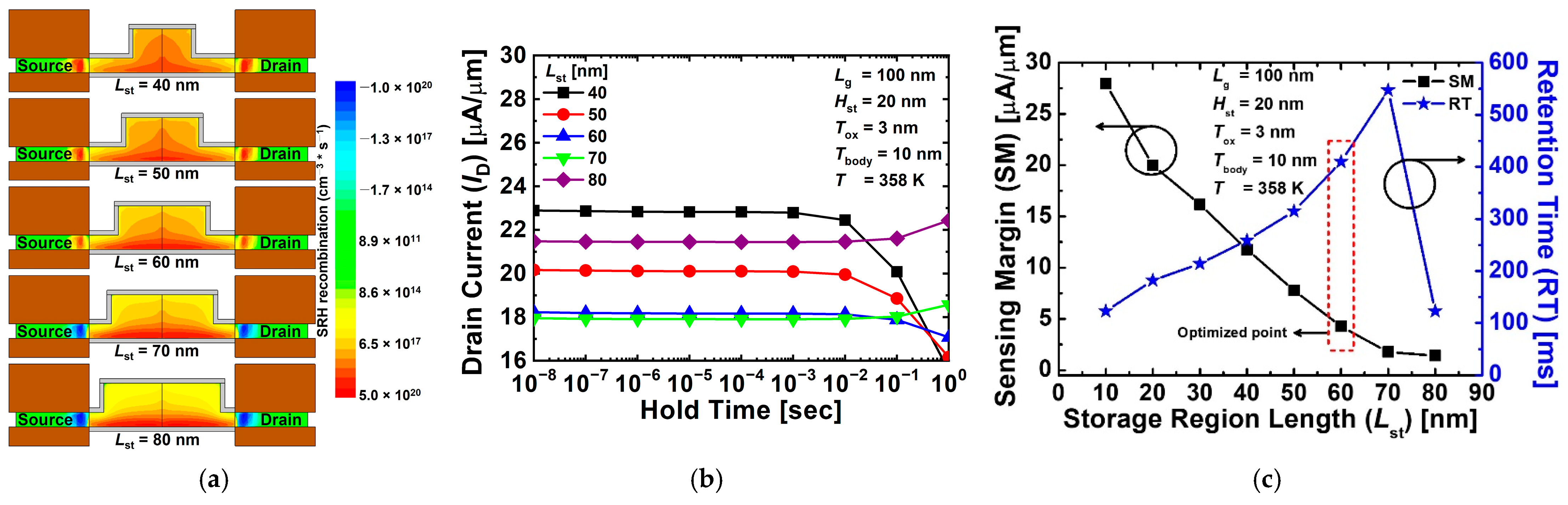

| Parameter | Values |

|---|---|

| Gate length (Lg) | 100 nm |

| Body thickness (Tbody) | 5–20 nm |

| Storage region length (Lst) | 10–80 nm |

| Storage region height (Hst) | 10–30 nm |

| Gate dielectric (HfO2) thickness (Tox) | 3 nm |

| Source and Drain doping concentration | n-type, 1 × 1020 cm−3 |

| Body doping concentration | p-type, 1 × 1018 cm−3 |

| Gate 1 work-function (WFG1) | 4.85 eV |

| Gate 2 work-function (WFG2) | 5.3 eV |

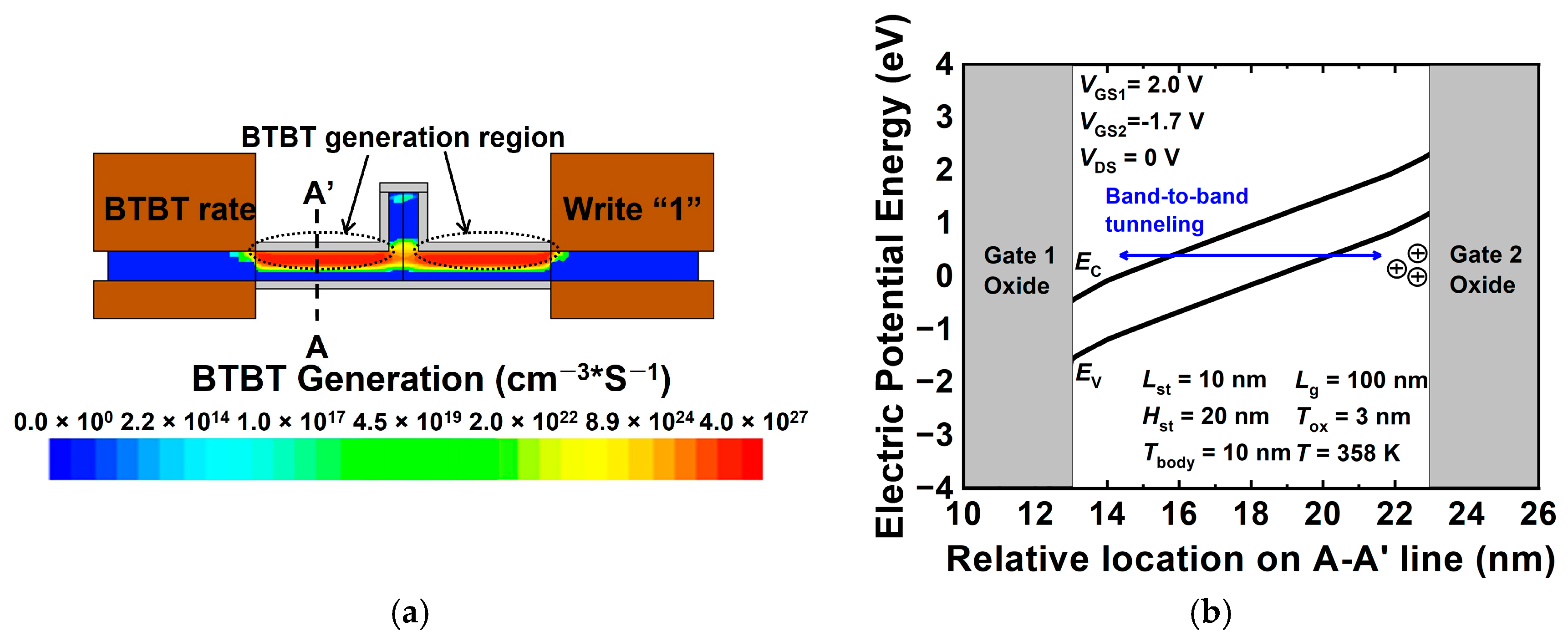

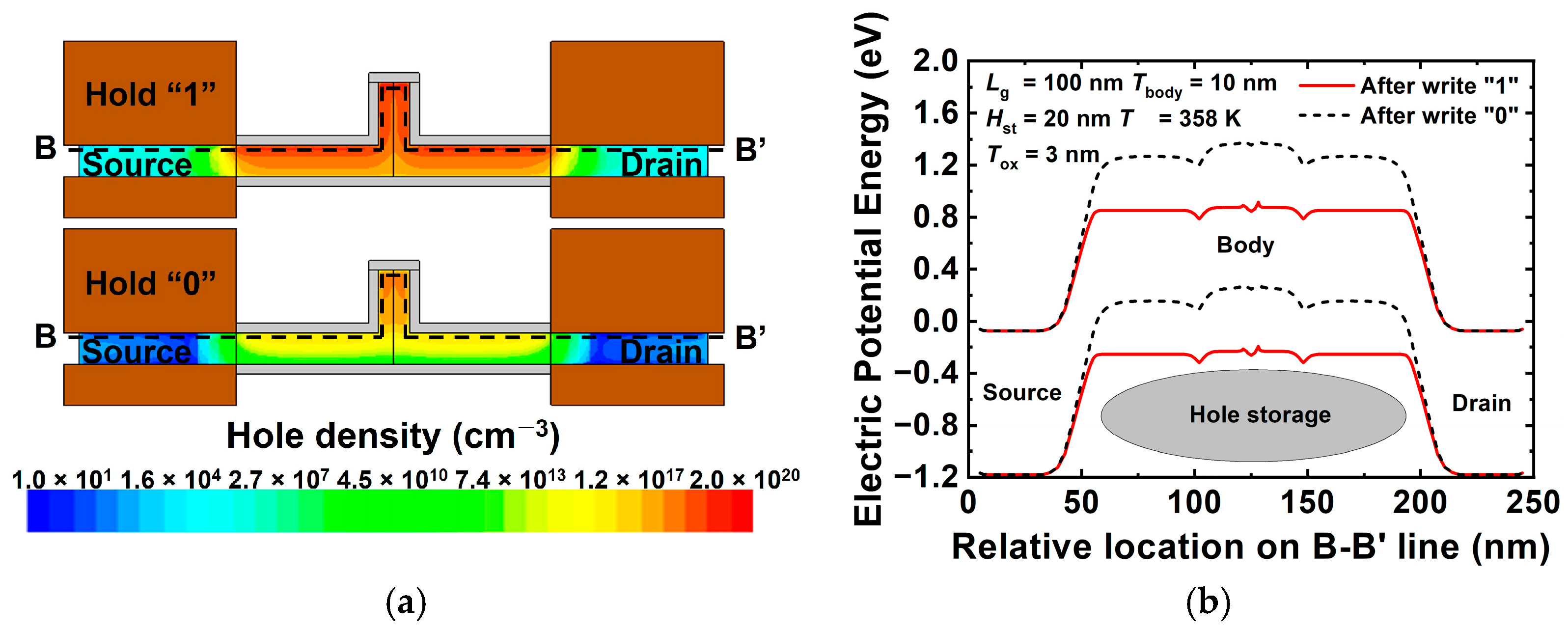

| Write “1” (Program) | Write “0” (Erase) | Read | Hold | |

|---|---|---|---|---|

| Gate 1 voltage (VGS1) | 2.0 V | 0.0 V | 1.2 V | 0.0 V |

| Gate 2 voltage (VGS2) | −1.7 V | 0.5 V | 0.0 V | −0.2 V |

| Drain voltage (VDS) | 0.0 V | −0.5 V | 0.5 V | 0.0 V |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

An, H.D.; Lee, S.H.; Park, J.; Min, S.R.; Kim, G.U.; Yoon, Y.J.; Seo, J.H.; Cho, M.S.; Jang, J.; Bae, J.-H.; et al. Design of a Capacitorless DRAM Based on a Polycrystalline-Silicon Dual-Gate MOSFET with a Fin-Shaped Structure. Nanomaterials 2022, 12, 3526. https://doi.org/10.3390/nano12193526

An HD, Lee SH, Park J, Min SR, Kim GU, Yoon YJ, Seo JH, Cho MS, Jang J, Bae J-H, et al. Design of a Capacitorless DRAM Based on a Polycrystalline-Silicon Dual-Gate MOSFET with a Fin-Shaped Structure. Nanomaterials. 2022; 12(19):3526. https://doi.org/10.3390/nano12193526

Chicago/Turabian StyleAn, Hee Dae, Sang Ho Lee, Jin Park, So Ra Min, Geon Uk Kim, Young Jun Yoon, Jae Hwa Seo, Min Su Cho, Jaewon Jang, Jin-Hyuk Bae, and et al. 2022. "Design of a Capacitorless DRAM Based on a Polycrystalline-Silicon Dual-Gate MOSFET with a Fin-Shaped Structure" Nanomaterials 12, no. 19: 3526. https://doi.org/10.3390/nano12193526

APA StyleAn, H. D., Lee, S. H., Park, J., Min, S. R., Kim, G. U., Yoon, Y. J., Seo, J. H., Cho, M. S., Jang, J., Bae, J.-H., Lee, S.-H., & Kang, I. M. (2022). Design of a Capacitorless DRAM Based on a Polycrystalline-Silicon Dual-Gate MOSFET with a Fin-Shaped Structure. Nanomaterials, 12(19), 3526. https://doi.org/10.3390/nano12193526