# Design of a Capacitorless DRAM Based on a Polycrystalline-Silicon Dual-Gate MOSFET with a Fin-Shaped Structure

Hee Dae An<sup>1</sup>, Sang Ho Lee<sup>1</sup>, Jin Park<sup>1</sup>, So Ra Min<sup>1</sup>, Geon Uk Kim<sup>1</sup>, Young Jun Yoon<sup>2</sup>, Jae Hwa Seo<sup>3</sup>, Min Su Cho<sup>4</sup>, Jaewon Jang<sup>1</sup>, Jin-Hyuk Bae<sup>1</sup>, Sin-Hyung Lee<sup>1</sup> and In Man Kang<sup>1,\*</sup>

- <sup>1</sup> School of Electronic and Electrical Engineering, Kyungpook National University, Daegu 41566, Korea

- <sup>2</sup> Korea Multi-Purpose Accelerator Complex, Korea Atomic Energy Research Institute, Gyeongju 38180, Korea

- <sup>3</sup> Power Semiconductor Research Center, Korea Electrotechnology Research Institute, Changwon 51543, Korea

- <sup>4</sup> DB HiTek, RF/Mixed Signal Development Team, Eumseong 27605, Korea

- \* Correspondence: imkang@ee.knu.ac.kr

**Abstract:** In this study, a capacitorless one-transistor dynamic random-access memory (1T-DRAM) cell based on a polycrystalline silicon dual-gate metal-oxide-semiconductor field-effect transistor with a fin-shaped structure was optimized and analyzed using technology computer-aided design simulation. The proposed 1T-DRAM demonstrated improved memory characteristics owing to the adoption of the fin-shaped structure on the side of gate 2. This was because the holes generated during the program operation were collected on the side of gate 2, allowing an expansion of the area where the holes were stored using the fin-shaped structure. Therefore, compared with other previously reported 1T-DRAM structures, the fin-shaped structure has a relatively high retention time due to the increased hole storage area. The proposed 1T-DRAM cell exhibited a sensing margin of 2.51  $\mu$ A/ $\mu$ m and retention time of 598 ms at *T* = 358 K. The proposed 1T-DRAM has high retention time and chip density, so there is a possibility that it will replace DRAM installed in various applications such as PCs, mobile phones, and servers in the future.

**Keywords:** dual-gate; grain boundary; polycrystalline silicon; 1T-DRAM; metal-oxide-semiconductor field-effect transistor; sensing margin; retention time

# 1. Introduction

Dynamic random access memory (DRAM) has been employed as a memory element for decades and is one of the key components of electronic devices [1,2]. This is because hat conventional DRAM has one transistor–one capacitance, simple configuration, high chip density, and low power consumption. In recent years, miniaturization of electronic devices has necessitated the use of small cells; however, it is extremely difficult to reduce the size of capacitors. To address this concern, various structures such as 3D storage capacitors, cylindrical vertical array transistors, and trench cell capacitors have been proposed [3–5]. However, such structures complicate manufacturing processes. Therefore, a one-transistor (1T)-DRAM that can achieve a high chip density by eliminating the need for a capacitor, which is the basic hurdle in reducing the size of a DRAM cell, has been proposed. However, planar 1T-DRAM still exhibits poor retention time. Therefore, various structures and methods for improving the memory characteristic have been investigated [6–17].

The primary concept of 1T-DRAM involves the implementation of memory characteristics using floating body effects with a silicon-on-insulator (SOI) structure [18–20]. However, the SOI technology is expensive, and its mass production is limited. Nevertheless, cost issues can be overcome by using a polycrystalline silicon (poly-Si)-based SOI-like structure. In addition, poly-Si-based 1T-DRAM can be combined with the technologies used in 3D NAND manufacturing to increase chip density.

Citation: An, H.D.; Lee, S.H.; Park, J.; Min, S.R.; Kim, G.U.; Yoon, Y.J.; Seo, J.H.; Cho, M.S.; Jang, J.; Bae, J.-H.; et al. Design of a Capacitorless DRAM Based on a Polycrystalline-Silicon Dual-Gate MOSFET with a Fin-Shaped Structure. *Nanomaterials* **2022**, *12*, 3526. https://doi.org/10.3390/ nano12193526

Academic Editor: Antonio Di Bartolomeo

Received: 21 August 2022 Accepted: 6 October 2022 Published: 9 October 2022

**Publisher's Note:** MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations.

**Copyright:** © 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https:// creativecommons.org/licenses/by/ 4.0/). In this paper, we proposed a novel 1T-DRAM based on a poly-Si dual-gate metal-oxidesemiconductor field-effect transistor (MOSFET) with a fin-shaped structure. The proposed device adopts a fin-shaped structure to improve the memory characteristics and can be 3D-stacked using poly-Si, which can increase the chip density. During program operation, holes are generated by band-to-band tunneling (BTBT) between gates 1 and 2 in the body region, and these holes are stored on the side of gate 2. Therefore, a fin-shaped structure is adopted on the side of gate 2 to expand the storage space and improve the retention time. In addition, the advantage of the fin-shaped structure is that the retention time can be improved without changing the size of the device. Furthermore, we optimize the storage region length, storage region height, and body thickness, which are important geometric parameters for memory characteristics, and achieve high retention times. Furthermore, to improve the accuracy of the simulation, a study is conducted assuming the existence of a single grain boundary (GB) at the center of the body region.

#### 2. Device Structure and Simulation Method

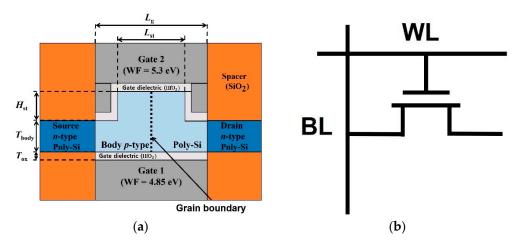

Figure 1a shows a cross-sectional view of the proposed poly-Si dual-gate MOSFETbased 1T-DRAM with a fin-shaped structure. Gate 1 was used for the conventional MOSFET and programming operations. Gate 2 was used to perform the program, erase, and hold operations. The work functions of gate 1 ( $WF_{G1}$ ) and gate 2 ( $WF_{G2}$ ) are 4.85 eV and 5.3 eV, respectively. Note that poly-Si and Ni were employed as electrode materials for gates 1 and 2, respectively [21,22]. The proposed device was designed with a fin-shaped structure to increase the storage area where holes accumulated and to improve the retention time. Figure 1b is a simple circuit diagram of 1T-DRAM, and the capacitor is removed from the DRAM circuit diagram.

**Figure 1.** (a) Cross-sectional view of the proposed poly-Si dual-gate MOSFET based 1T-DRAM with a fin-shaped structure. (b) Simplified circuit diagram of 1T-DRAM.

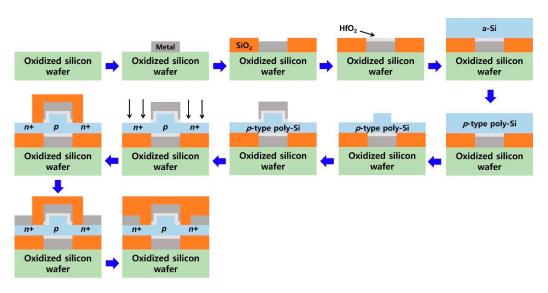

Figure 2 shows the key fabrication steps of the proposed 1T-DRAM based on a poly-Si dual-gate MOSFET with a fin-shaped structure crystallized via excimer laser crystallization consisting of a total of 11 steps [23]. First, metal is deposited on an oxidized silicon wafer, and then dry etching is performed to form a bottom gate electrode. Second, after depositing SiO<sub>2</sub> serving as a spacer, dry etching of the SiO<sub>2</sub> in the bottom gate electrode area is carried out. Third, HfO<sub>2</sub>, the gate dielectric, is deposited and etched. Fourth, a-Si is deposited using LPCVD. Fifth, excimer laser irradiation is performed to convert a-Si to poly-Si. Sixth, etching of poly-Si is performed to make a fin shape. Seventh, HfO<sub>2</sub> and metal are deposited and etched to form the top gate electrode. Eighth, ion implantation is performed to form the n-type source and drain. Ninth, SiO<sub>2</sub> is deposited for insulation between the gate electrode and the source and drain electrodes. Tenth, the source and drain metal is deposited. Finally, after removing SiO<sub>2</sub> from the top of the electrode, SiO<sub>2</sub> is deposited for passivation [23].

**Figure 2.** Key fabrication steps of proposed 1T-DRAM based on a poly-Si dual-gate MOSFET with a fin-shaped structure crystallized via excimer laser crystallization [23].

The gate length ( $L_g$ ) and gate dielectric (HfO<sub>2</sub>) thickness ( $T_{ox}$ ) were 100 and 3 nm, respectively. The doping concentrations in the source, body, and drain regions were  $1 \times 10^{20}$  (*n*-type),  $1 \times 10^{18}$  (*p*-type), and  $1 \times 10^{20}$  (*n*-type), respectively. The relevant parameters of the proposed device are presented in Table 1. Note that in the proposed device, geometric parameters, including the storage region length ( $L_{st}$ ), storage region height ( $H_{st}$ ), and body thickness ( $T_{body}$ ), significantly affect memory characteristics. Therefore, we used the aforementioned three variables for optimization. For high accuracy, simulations such as the Fermi–Dirac statistical model, Shockley–Read–Hall (SRH) recombination model, non-local BTBT model, Auger recombination model, trap-assisted tunneling model, quantum confinement effect, and the doping-dependent and field-dependent mobility models were considered. In addition, the GB present in poly-Si was also adopted. To apply the interface trap of GB, the reported experimental results of 1T-DRAM [24] were borrowed. The device design and analysis were performed using the Sentaurus technology computer-aided design (TCAD) tool.

Table 1. Device parameters of proposed 1T-DRAM used for simulation.

| Parameter                                                  | Values                                                 |  |

|------------------------------------------------------------|--------------------------------------------------------|--|

| Gate length $(L_g)$                                        | 100 nm                                                 |  |

| Body thickness $(T_{body})$                                | 5–20 nm                                                |  |

| Storage region length $(L_{st})$                           | 10–80 nm                                               |  |

| Storage region height $(H_{st})$                           | 10–30 nm                                               |  |

| Gate dielectric (HfO <sub>2</sub> ) thickness ( $T_{ox}$ ) | ectric (HfO <sub>2</sub> ) thickness ( $T_{ox}$ ) 3 nm |  |

| Source and Drain doping concentration                      | <i>n</i> -type, $1 \times 10^{20}$ cm <sup>-3</sup>    |  |

| Body doping concentration                                  | <i>p</i> -type, $1 	imes 10^{18}$ cm $^{-3}$           |  |

| Gate 1 work-function ( $WF_{G1}$ )                         | 4.85 eV                                                |  |

| Gate 2 work-function ( $WF_{G2}$ )                         | 5.3 eV                                                 |  |

# 3. Results and Discussion

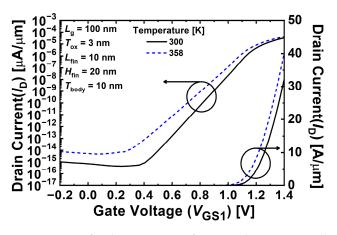

Figure 3 shows the transfer characteristics of the proposed 1T-DRAM cell at different temperatures of 300 K and 358 K. Note that the threshold voltage ( $V_{\text{th}}$ ) of the proposed device was 1.05 V and 0.99 V at temperatures of 300 K and 358 K, respectively.  $V_{\text{th}}$  was obtained at  $I_{\text{D}} = 10^{-7} \text{ A}/\mu\text{m}$ . When the temperature increased from 300 K to 358 K, the off-current increased because carrier generation was accelerated by the high temperature. In addition, because the carrier density increased the recombination rate, the retention time decreased.

**Figure 3.** Transfer characteristics of proposed 1T-DRAM cell at different temperatures of 300 K and 358 K.

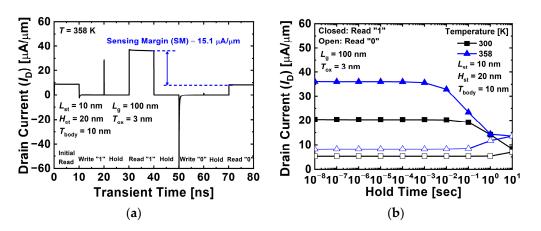

Figure 4a shows the transient characteristics of the proposed 1T-DRAM cell at 358 K. The sensing margin is defined as the difference between the read "1" current and read "0" current. The sensing margin of the proposed device was  $15.1 \,\mu\text{A}/\mu\text{m}$  at T = 358 K. The operation mechanism of the 1T-DRAM consists of program, erase, read, and hold operations. The program operation uses the BTBT mechanism to generate holes on the side of gate 2 in the body area. During the erase operation, a negative bias is applied to the drain and the potential barrier disappears; thus, the holes accumulated on the side of gate 2 in the body region move to the drain region. The bias conditions for the operation of the 1T-DRAM are summarized in Table 2. Figure 4b shows the variation in the read currents for the "1" and "0" states at different temperatures of 300 K and 358 K. Conventionally, the retention time is defined as the time elapsed until the initial sensing margin reaches 50%. The retention times of the proposed 1T-DRAM were 1.48 s and 123 ms at temperatures of 300 K and 358 K, respectively. As shown in Figure 3, increasing the temperature increased the carrier density and recombination rate and decreased the retention time.

Table 2. Operating bias scheme for memory performance.

|                                | Write "1"<br>(Program) | Write "0"<br>(Erase) | Read  | Hold              |

|--------------------------------|------------------------|----------------------|-------|-------------------|

| Gate 1 voltage ( $V_{GS1}$ )   | 2.0 V                  | 0.0 V                | 1.2 V | 0.0 V             |

| Gate 2 voltage ( $V_{GS2}$ )   | -1.7 V                 | 0.5 V                | 0.0 V | $-0.2 \mathrm{V}$ |

| Drain voltage ( $V_{\rm DS}$ ) | 0.0 V                  | -0.5 V               | 0.5 V | 0.0 V             |

**Figure 4.** (a) Transient characteristics of proposed 1T-DRAM cell. (b) Variation of read currents in "1" and "0" states at different temperatures of 300 K and 358 K.

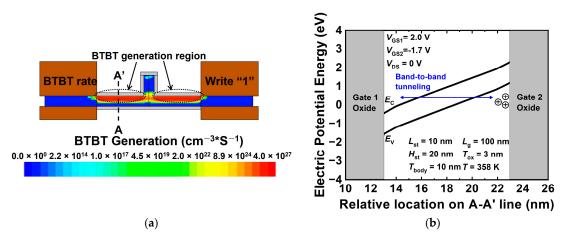

Figure 5a,b show that BTBT vertically occurs between gates 1 and 2 in the body region during the program operation. When the program operation is used as a BTBT mechanism, it demonstrates the advantage of a lower power consumption than the impact ionization mechanism. Figure 5b shows an energy band diagram when a positive voltage of 2.0 V is applied to gate 1 and a negative voltage of -1.7 is applied to gate 2. The voltages applied to gates 1 and 2 cause band bending and BTBT. Therefore, electrons in the valence band tunnel into the conduction band, and holes are created on the side of gate 2. Because the high work function of gate 2 forms a potential well, the generated holes accumulate on side of gate 2 in the body region.

**Figure 5.** (a) Contour map of BTBT rate and (b) energy band diagram of the proposed 1T-DRAM cell in program operation (energy band is extracted 10 nm away from source–channel junction).

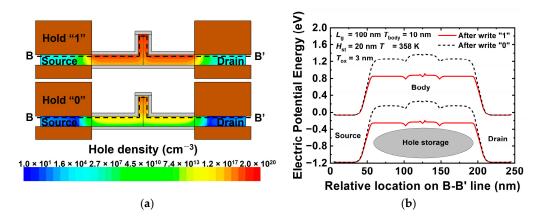

Figure 6a,b show the contour map of the hole density and energy band diagram of the proposed 1T-DRAM cell in states "1" and "0", respectively. Note that state "1" indicates that the holes generated by BTBT after the program operation accumulate in the body area. State "0" implies a state wherein the holes further generated after the erasing operation disappear. Figure 6a shows that the hole densities in the body region on the side of gate 2 corresponding to states "1" and "0" are significantly different. Figure 6b shows the difference in the hole density with an energy band diagram. Note that the additionally generated holes lower the energy barrier, similar to when a positive voltage is applied to the body region.

**Figure 6.** (a) Contour map of hole density and (b) energy band diagram of proposed 1T-DRAM cell in hold states "1" and "0" (energy band is extracted at 2 nm above gate 2 oxide).

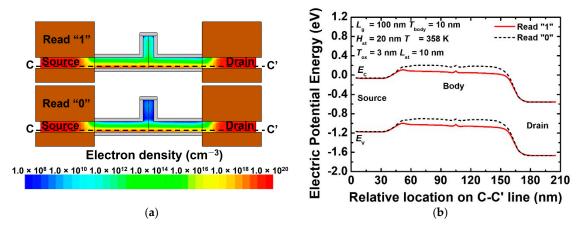

Figure 7a,b show the contour map of the electron density and energy band diagram of the proposed 1T-DRAM cell in the read "1" and read "0" operations. Note that a read operation is performed via the conventional MOSFET operation. Figure 7a shows that

the electron density corresponding to read "1" is higher than that corresponding to read "0", the inversion layer is formed on the side of gate 1 in the body region, and a current flows. Figure 7b shows the effect of the electron potential in the body region depending on the presence or absence of excess holes in the storage region. The generated hole acts as if a positive voltage is applied to the body region, and when read "1" is operated, the energy barrier in the body region is lowered and a high current flows. Because the current changes depending on the presence of excess holes, it is possible to distinguish between data "1" and "0". The difference between read "1" current and read "0" current is defined as a sensing margin in 1T-DRAM.

**Figure 7.** (a) Contour map of electron density and (b) energy band diagram of proposed 1T-DRAM cell in read states "1" and "0" (energy band is extracted at 3 nm above gate 1 oxide).

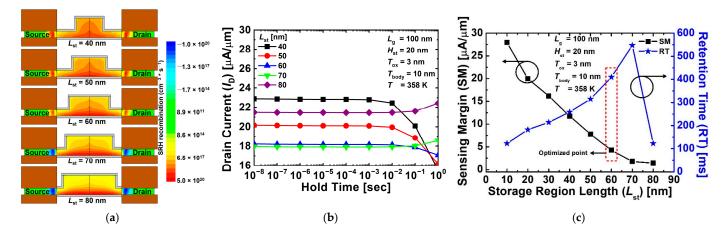

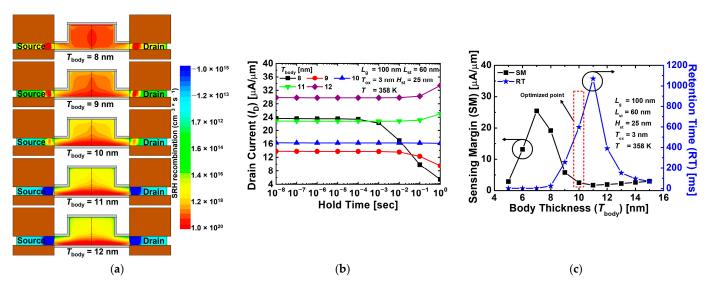

Figure 8a shows the contour maps of the SRH recombination rate for the proposed 1T-DRAM with different  $L_{st}$  in the hold state "1" operation. As shown in Figure 5a, BTBT vertically occurs between gates 1 and 2 in the body region during program operation. Moreover, in Figure 5a, the circular dotted line indicates the region where BTBT is generated, and as  $L_{\rm st}$  becomes longer, the area where BTBT occurs becomes smaller. Therefore, it can be seen from Figure 8a that as  $L_{st}$  increases, the BTBT rate decreases and the SRH recombination rate decreases because fewer holes are generated. Furthermore, when  $L_{\rm st}$ is 70 nm, SRH recombination transforms into SRH generation at the source-channel and channel-drain junctions, and in Figure 8b, the current corresponding to read "1" increases with the hold time and becomes unstable. Therefore, for all the optimization processes considered in this study, the point with the longest retention time under the condition that the current corresponding to read "1" does not increase is considered as the optimization point. In other words, SRH generation does not occur at the source-channel and channeldrain junctions. Moreover, because the read "1" and "0" current rapidly increases with time by SRH generation, the retention time is rapidly reduced at  $L_{st} = 80$  nm. In Figure 8c, as  $L_{st}$  becomes longer, the region where BTBT occurs becomes smaller, indicating that fewer holes are generated, and the sensing margin decreases. Furthermore, it is shown that the SRH recombination rate decreases, and the retention time increases as fewer holes are generated. When  $L_{st}$  is 60 nm, the current corresponding to read "1" does not increase with the hold time, and the retention time is the highest; therefore, this value was selected as the optimization point. The proposed device with an  $L_{st}$  of 60 nm obtained a sensing margin of 4.25  $\mu$ A/ $\mu$ m and a retention time of 410 ms at *T* = 358 K.

**Figure 8.** (a) Contour map of SRH recombination rate for proposed 1T-DRAM with different  $L_{st}$  in hold state "1" operation. (b) Read "1" current of proposed 1T-DRAM with different  $L_{st}$ . (c) Sensing margin and retention time of proposed 1T-DRAM cell as a function of  $L_{st}$ .

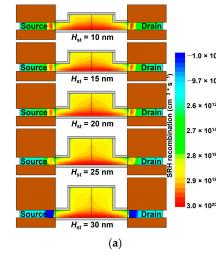

Figure 9a shows the contour maps of the SRH recombination rate for the proposed 1T-DRAM with different  $H_{st}$  values in the hold state "1" operation. As mentioned earlier, during program operation, BTBT occurs in the circular dotted line area in Figure 5a. However, a small amount of BTBT also occurs between the fin-shaped gates 1 and 2. As  $H_{\rm st}$  increases, less tunneling occurs because the distance between gates 1 and 2 increases in the fin-shaped region. Therefore, as shown in Figure 9a, as  $H_{st}$  increases, the BTBT rate decreases, and the number of generated holes decreases, so the SRH recombination rate decreases. Figure 9b shows the current corresponding to read "1", and the number of holes created depending on the increase of  $H_{\rm st}$  decreases and the current decreases. In the end, similar to the above-mentioned  $L_{\rm st}$  optimization process, when  $H_{\rm st}$  is 30 nm, the current corresponding to read "1" increases with time due to SRH generation and becomes unstable. Figure 9c shows the sensing margin and retention time of the proposed 1T-DRAM cell as a function of H<sub>st</sub>. As H<sub>st</sub> increases, fewer holes are generated, and sensing margin gradually decreases. Conversely, the retention time increases because the stored holes can be retained longer by the reduced SRH recombination rate. Notably, the proposed device with an  $H_{st}$  of 25 nm obtained a sensing margin of 2.51  $\mu$ A/ $\mu$ m and a retention time of 598 ms at T = 358 K.

**Figure 9.** (a) Contour map of SRH recombination rate for proposed 1T-DRAM with different  $H_{st}$  in hold state "1" operation. (b) Read "1" current of proposed 1T-DRAM with different  $H_{st}$ . (c) Sensing margin and retention time of proposed 1T-DRAM cell as a function of  $H_{st}$ .

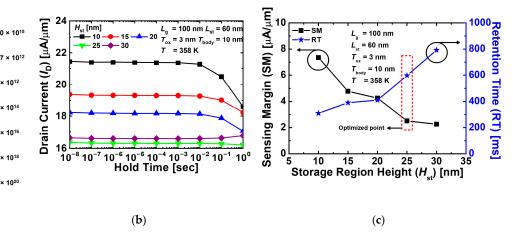

Figure 10a shows the contour maps of the SRH recombination rate for the proposed 1T-DRAM with different  $T_{\text{body}}$  values in the hold state "1" operation. Since BTBT vertically occurs between gates 1 and 2 in the body region, as the  $T_{body}$  becomes thicker, less BTBT occurs and fewer holes are created, so the SRH rate decreases. Conversely, as shown in Figure 10a, the thinner the  $T_{\text{body}}$ , the more BTBT is generated, and the more holes are created, so the SRH rate is high throughout the body region. Figure 10b shows read "1" current of the proposed 1T-DRAM with different  $T_{body}$ . Similar to the above-mentioned  $L_{\rm st}$  optimization process, when  $T_{\rm body}$  is 11 nm, the current corresponding to read "1" increases with time due to SRH generation and becomes unstable. Figure 10c shows the sensing margin and retention time for the proposed 1T-DRAM cell as functions of  $T_{\text{body}}$ . Since electrons are accumulated in the inversion channel on the side of gate 1 and holes are accumulated on the side of gate 2, when  $T_{body}$  becomes thinner than a certain thickness, electrons and holes meet and recombination occurs, reducing sensing margin. In addition, when  $T_{\text{body}}$  becomes thicker than a specific thickness, the sensing margin decreases because the BTBT rate decreases in the program operation. For our device, the final optimized parameters were  $L_{st}$  = 60 nm,  $H_{st}$  = 25 nm, and  $T_{body}$  = 10 nm. Table 3 summarizes previously reported sensing margin and retention times for various 1T-DRAM cells. As can be inferred, the 1T-DRAM cell proposed in this paper exhibits excellent memory characteristics at T = 358 K compared with other device.

Table 3. Memory performance of various 1T-DRAM-related papers.

| No | Reference | Sensing Margin [µA/µm] | Retention Time [ms] |

|----|-----------|------------------------|---------------------|

| 1  | [25]      | 5.4                    | 68                  |

| 2  | [26]      | 28.7                   | 79                  |

| 3  | [27]      | 0.15                   | 320                 |

| 4  | [28]      | 52.3                   | 11.2                |

| 5  | [29]      | 11.7                   | 64.2                |

| 6  | [30]      | 6.16                   | 131                 |

| 7  | [31]      | 6.58                   | 340.1               |

| 8  | This work | 2.51                   | 598                 |

**Figure 10.** (a) Contour map of SRH recombination rate for proposed 1T-DRAM with different  $T_{ch}$  in hold state "1" operation. (b) Read "1" current of proposed 1T-DRAM with different  $T_{ch}$ . (c) Sensing margin and retention time of the proposed 1T-DRAM cell as a function of  $T_{ch}$ .

### 4. Conclusions

In this study, a novel 1T-DRAM based on a poly-Si dual-gate MOSFET with a finshaped structure was optimized and analyzed using a TCAD simulation. In the proposed device, a negative bias is applied to gate 2 during the hold operation to prevent the holes generated in the program operation from escaping. In addition, by using a fin-type structure, the length of the gate 2 side is geographically increased to expand the area where the hole is stored. Therefore, the proposed 1T-DRAM has improved memory characteristics as a result of which the hole storage area is expanded compared with the planar dual-gate MOSFET-based 1T-DRAM of the same channel length. The storage region length, storage region height, and body thickness have a great influence on the memory characteristics because they affect the number of holes created by BTBT during the program operation. Therefore, the optimized parameters were  $L_{st} = 60 \text{ nm}$ ,  $H_{st} = 25 \text{ nm}$ , and  $T_{body} = 10 \text{ nm}$ , and a high retention time of 598 ms was obtained at T = 358 K. In conclusion, the proposed novel 1T-DRAM demonstrates potential to replace conventional 1T-1C DRAM because it possesses a high retention time and can increase the chip density.

**Author Contributions:** Conceptualization, H.D.A.; investigation, H.D.A.; data curation, H.D.A., M.S.C., S.H.L., J.P., S.R.M., G.U.K., Y.J.Y., and J.H.S.; validation, J.J., J.-H.B., S.-H.L., and I.M.K.; writing—original draft preparation, H.D.A.; writing—review and editing, I.M.K. All authors have read and agreed to the published version of the manuscript.

**Funding:** This work was supported by the National Research Foundation of Korea (NRF) grant funded by the Korea government (MSIT) (No. NRF-2020R1A2C1005087); the BK21 FOUR project funded by the Ministry of Education, Korea (4199990113966); the Basic Science Research Program through the National Research Foundation of Korea (NRF) funded by the Ministry of Education (NRF-2021R1A6A3A13039927); the National R&D Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT (2021M3F3A2A03017764); and the National R&D Program through the National Research Foundation of Korea (NRF) funded by Ministry of Science and ICT (2022M3I7A1078936). This investigation was financially supported by Semiconductor Industry Collaborative Project between Kyungpook National University and Samsung Electronics Co. Ltd. The EDA tool was supported by the IC Design Education Center (IDEC), Korea.

Institutional Review Board Statement: Not applicable.

Informed Consent Statement: Not applicable.

Data Availability Statement: Not applicable.

**Conflicts of Interest:** The authors declare no conflict of interest.

# References

- 1. Yang, H.Y.; Chang, C.M.; Chao MC, T.; Huang, R.F.; Lin, S.C. Testing methodology of embedded DRAMs. *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.* 2011, 20, 1715–1728. [CrossRef]

- Spessot, A.; Oh, H. 1T-1C Dynamic Random Access Memory Status, Challenges, and Prospects. IEEE Trans. Electron Devices 2020, 67, 1382–1393. [CrossRef]

- Koyanagi, M. The Stacked Capacitor DRAM Cell and Three-Dimensional Memory. IEEE Solid-State Circuits Soc. Newsl. 2008, 13, 37–41. [CrossRef]

- Mueller, W.; Aichmayr, G.; Bergner, W.; Erben, E.; Hecht, T.; Kapteyn, C.; Kersch, A.; Kudelka, S.; Lau, F.; Luetzen, J.; et al. Challenges for the DRAM cell scaling to 40 nm. In Proceedings of the IEEE International Electron Devices Meeting, 2005. IEDM Technical Digest, Washington, DC, USA, 5 December 2005; Volume 4, p. 339.

- 5. Sunami, H. The Role of the Trench Capacitor in DRAM Innovation. IEEE Solid-State Circuits Soc. Newsl. 2008, 13, 42–44. [CrossRef]

- 6. Ansari, M.H.R.; Singh, J. Capacitorless 2T-DRAM for higher retention time and sense margin. *IEEE Trans. Electron Devices* 2020, 67, 902–906. [CrossRef]

- Lin, J.-T.; Lin, H.-H.; Chen, Y.-J.; Yu, C.-Y.; Kranti, A.; Lin, C.-C.; Lee, W.-H. Vertical Transistor with n-Bridge and Body on Gate for Low-Power 1T-DRAM Application. *IEEE Trans. Electron Devices* 2017, 64, 4937–4945. [CrossRef]

- 8. Ansari, M.H.R.; Cho, S. Performance improvement of 1T DRAM by raised source and drain engineering. *IEEE Trans. Electron Devices* **2021**, *68*, 1577–1584. [CrossRef]

- Han, J.-W.; Ryu, S.-W.; Kim, S.; Kim, C.-J.; Ahn, J.-H.; Choi, S.-J.; Kim, J.S.; Kim, K.H.; Lee, G.S.; Oh, J.S.; et al. A Bulk FinFET Unified-RAM (URAM) Cell for Multifunctioning NVM and Capacitorless 1T-DRAM. *IEEE Electron Device Lett.* 2008, 29, 632–634. [CrossRef]

- 10. Bawedin, M.; Cristoloveanu, S.; Flandre, D. A Capacitorless 1T-DRAM on SOI Based on Dynamic Coupling and Double-Gate Operation. *IEEE Electron Device Lett.* 2008, 29, 795–798. [CrossRef]

- Cristoloveanu, S.; Lee, K.; Parihar, M.; El Dirani, H.; Lacord, J.; Martinie, S.; Le Royer, C.; Barbe, J.-C.; Mescot, X.; Fonteneau, P.; et al. A review of the Z 2 -FET 1T-DRAM memory: Operation mechanisms and key parameters. *Solid-State Electron*. 2017, 143, 10–19. [CrossRef]

- 12. Navlakha, N.; Lin, J.-T.; Kranti, A. Improved Retention Time in Twin Gate 1T DRAM with Tunneling Based Read Mechanism. *IEEE Electron Device Lett.* **2016**, *37*, 1127–1130. [CrossRef]

- Kamal, N.; Kamal, A.K.; Singh, J. L-Shaped Tunnel Field-Effect Transistor-Based 1T DRAM with Improved Read Current Ratio, Retention Time, and Sense Margin. IEEE Trans. Electron Devices 2021, 68, 2705–2711. [CrossRef]

- Lin, J.-T.; Lin, P.-H.; Eng, Y.-C.; Chen, Y.-R. Novel Vertical SOI-Based 1T-DRAM with Trench Body Structure. IEEE Trans. Electron Devices 2013, 60, 1872–1877. [CrossRef]

- 15. Lee, W.; Choi, W.Y. A Novel Capacitorless 1T DRAM Cell for Data Retention Time Improvement. *IEEE Trans. Nanotechnol.* **2010**, 10, 462–466. [CrossRef]

- 16. Ansari, H.R.; Navlakha, N.; Lin, J.-T.; Kranti, A. 1T-DRAM with Shell-Doped Architecture. *IEEE Trans. Electron Devices* 2018, 66, 428–435. [CrossRef]

- Ansari, H.R.; Navlakha, N.; Lee, J.Y.; Cho, S. Double-Gate Junctionless 1T DRAM with Physical Barriers for Retention Improvement. *IEEE Trans. Electron Devices* 2020, 67, 1471–1479. [CrossRef]

- Choi, K.R.; Lee, C.H.; Kim, S.J.; Enomoto, H.; Shim, T.H.; Cho, W.J.; Park, J.G. Dependence of memory margin of Cap-less memory cells on top Si thickness. *Appl. Phys. Lett.* 2009, *94*, 023508. [CrossRef]

- 19. Okhonin, S.; Nagoga, M.; Sallese, J.; Fazan, P. A capacitor-less 1T-DRAM cell. IEEE Electron Device Lett. 2002, 23, 85–87. [CrossRef]

- Blagojevic, M.; Kayal, M.; Pastre, M.; Harik, L.; Declercq, M.; Okhonin, S.; Fazan, P. Capacitorless 1T DRAM Sensing Scheme With Automatic Reference Generation. *IEEE J. Solid-State Circuits* 2006, 41, 1463–1470. [CrossRef]

- 21. Michaelson, H.B. The work function of the elements and its periodicity. J. Appl. Phys. 1977, 48, 4729–4733. [CrossRef]

- 22. Polishchuk, I.; Ranade, P.; King, T.-J.; Hu, C. Dual work function metal gate CMOS technology using metal interdiffusion. *IEEE Electron Device Lett.* 2001, 22, 444–446. [CrossRef]

- Lee, I.-C.; Tsai, T.-C.; Tsai, C.-C.; Yang, P.-Y.; Wang, C.-L.; Cheng, H.-C. High-performance vertically stacked bottom-gate and top-gate polycrystalline silicon thin-film transistors for three-dimensional integrated circuits. *Solid-State Electron.* 2012, 77, 26–30. [CrossRef]

- 24. Seo, J.H.; Yoon, Y.J.; Yu, E.; Sun, W.; Shin, H.; Kang, I.M.; Lee, J.-H.; Cho, S. Fabrication and characterization of a thin-body poly-Si 1T DRAMwith charge-trap effect. *IEEE Electron Device Lett.* **2019**, *40*, 566–569. [CrossRef]

- Lin, J.-T.; Lee, W.-H.; Lin, P.-H.; Haga, S.W.; Chen, Y.-R.; Kranti, A. A New Electron Bridge Channel 1T-DRAM Employing Underlap Region Charge Storage. *IEEE J. Electron Devices Soc.* 2016, *5*, 59–63. [CrossRef]

- Lin, J.-T.; Sun, W.-T.; Lin, H.-H.; Chen, Y.-J.; Navlakha, N.; Kranti, A. Raised Body Doping-Less 1T-DRAM With Source/Drain Schottky Contact. *IEEE J. Electron Devices Soc.* 2019, 7, 276–281. [CrossRef]

- Lahgere, A.; Kumar, M.J. 1-T Capacitorless DRAM Using Bandgap-Engineered Silicon-Germanium Bipolar I-MOS. *IEEE Trans. Electron Devices* 2017, 64, 1–8. [CrossRef]

- Lin, J.-T.; Lin, P.-H.; Haga, S.W.; Wang, Y.-C.; Lu, D.-R. Transient and Thermal Analysis on Disturbance Immunity for 4 F<sup>2</sup> Surrounding Gate 1T-DRAM with Wide Trenched Body. *IEEE Trans. Electron Devices* 2014, 62, 61–68. [CrossRef]

- Cho, M.S.; Mun, H.J.; Lee, S.H.; Jang, J.; Bae, J.-H.; Kang, I.M. Simulation of capacitorless dynamic random access memory based on junctionless FinFETs using grain boundary of polycrystalline silicon. *Appl. Phys. A* 2020, 126, 1–10. [CrossRef]

- Yoon, Y.J.; Cho, M.S.; Kim, B.G.; Seo, J.H.; Kang, I.M. Capacitorless One-Transistor Dynamic Random-Access Memory Based on Double-Gate Metal-Oxide-Semiconductor Field-Effect Transistor with Si/SiGe Heterojunction and Underlap Structure for Improvement of Sensing Margin and Retention Time. J. Nanosci. Nanotechnol. 2019, 19, 6023–6030. [CrossRef]

- Lee, S.H.; Jang, W.D.; Yoon, Y.J.; Seo, J.H.; Mun, H.J.; Cho, M.S.; Jang, J.; Bae, J.-H.; Kang, I.M. Polycrystalline-Silicon-MOSFET-Based Capacitorless DRAM With Grain Boundaries and Its Performances. *IEEE Access* 2021, 9, 50281–50290. [CrossRef]