High-Efficiency, Low-Power, Fully Integrated Neural Electrical Stimulation Circuit

Abstract

1. Introduction

2. Overall Neural Stimulator System

3. Circuit Design

3.1. High-Voltage-Generation Circuit Design

3.2. Constant-Current Source Design

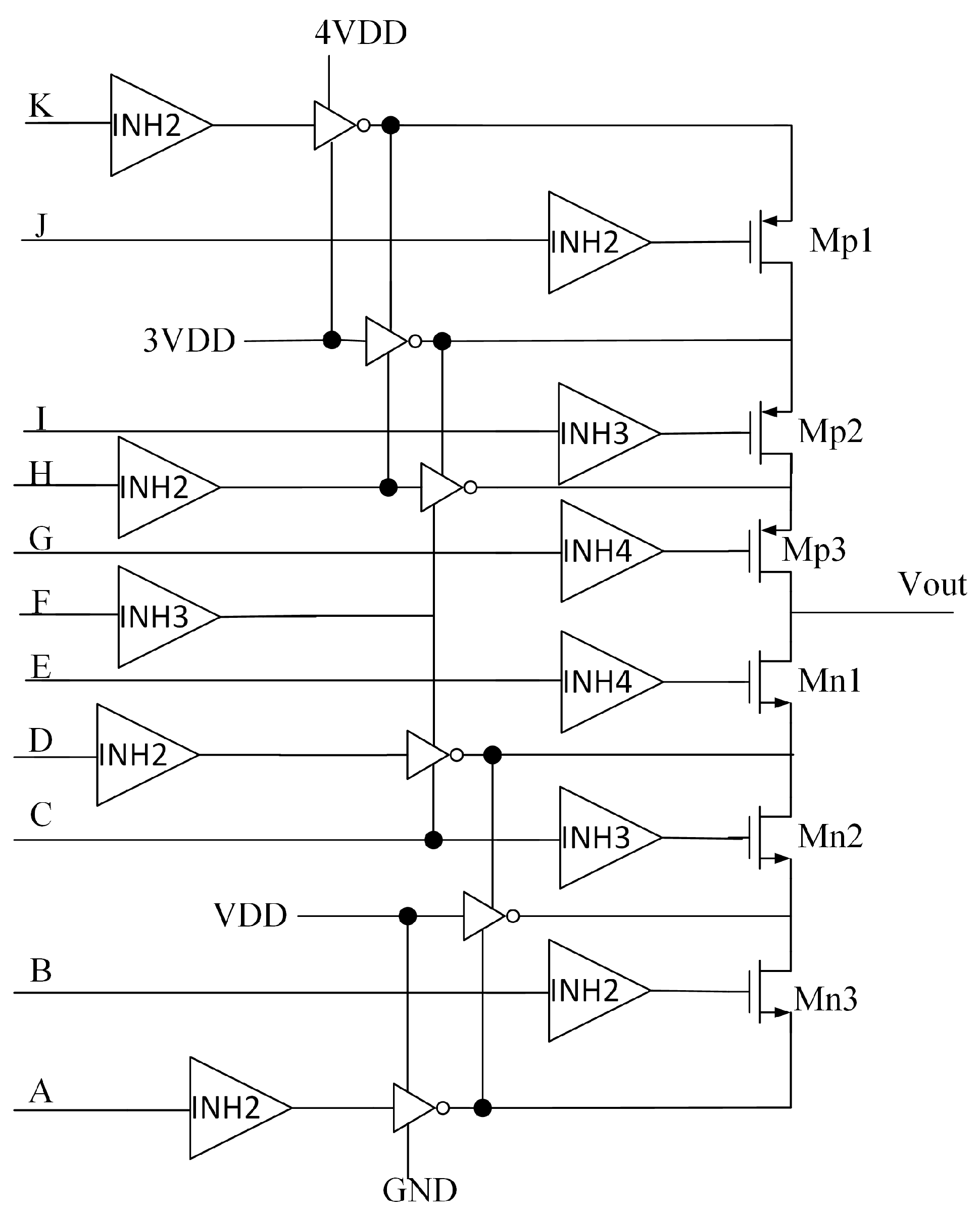

3.3. Output Driver Circuit Design

4. Results

4.1. High-Voltage-Generation Circuit Simulation

4.2. Constant-Current Source Simulation

4.3. Output Driver Circuit Simulation

4.4. Neural Stimulation System

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Chen, W.M.; Chiueh, H.; Chen, T.J. A fully integrated 8-channel closed-loop neural-prosthetic SoC for real-time epileptic seizure control. In Proceedings of the IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; Volume 49, pp. 286–287. [Google Scholar]

- Oluigbo, C.O.; Salma, A.; Rezai, A.R. Deep Brain Stimulation for Neurological Disorders. IEEE Rev. Biomed. Eng. 2012, 5, 88–99. [Google Scholar] [CrossRef] [PubMed]

- Lu, Z.; Chen, W.; Liu, X. A High-voltage Tolerant and Current-accurate Neural Stimulator Based on A Low-voltage CMOS Process. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Taipei, Taiwan, 7–9 November 2024; pp. 562–565. [Google Scholar]

- Ahn, W.; Kim, D.; Park, J. A Reconfigurable Neural Stimulation IC with a High-Resolution Strength Control and In-Situ Neural Recording Function for Cochlear Implant Systems. IEEE Solid-State Circuits Lett. 2022, 5, 162–165. [Google Scholar] [CrossRef]

- Huang, Y.E.; Peng, S.Y. A Current-Mode Electrical Stimulator with Charge Balance for Neural Stimulation Applications. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Taipei, Taiwan, 7–9 November 2024; pp. 772–775. [Google Scholar]

- Xin, H.; Zhou, M.; Wegberg, R.V. A 16-Output 10-V Compliant Stimulator ASIC with Sub-10-nA Mismatch and Simultaneous ETI Sensing for Selective Neural Stimulation. IEEE J. Solid-State Circuits 2025, 60, 908–920. [Google Scholar] [CrossRef]

- Alfia, A.; Hyouk-Kyu, C. A regulated multiple-output high-voltage charge pump IC for implantable neural stimulators. Microelectron. J. 2019, 92, 104617. [Google Scholar] [CrossRef]

- Bisoni, L.; Carboni, C.; Raffo, L.; Carta, N.; Barbaro, M. An HV-CMOS Integrated Circuit for Neural Stimulation in Prosthetic Applications. IEEE Trans. Circuits Syst. II Express Briefs 2015, 62, 184–188. [Google Scholar] [CrossRef]

- Arfin, S.K.; Sarpeshkar, R. An Energy-Efficient, Adiabatic Electrode Stimulator with Inductive Energy Recycling and Feedback Current Regulation. IEEE Trans. Biomed. Circuits Syst. 2012, 2, 1–14. [Google Scholar] [CrossRef] [PubMed]

- Lee, H.M.; Park, H.; Ghovanloo, M. A Power-Efficient Wireless System with Adaptive Supply Control for Deep Brain Stimulation. IEEE J. Solid-State Circuits 2013, 48, 2203–2216. [Google Scholar] [CrossRef] [PubMed]

- Luo, Z.; Ker, M.D.; Yang, T.Y.; Cheng, W.H. A Digitally Dynamic Power Supply Technique for 16-Channel 12 V-Tolerant Stimulator Realized in a 0.18- μm 1.8-V/3.3-V Low-Voltage CMOS Process. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 1087–1096. [Google Scholar] [CrossRef] [PubMed]

- You, Y.; Tian, R.; Zhang, Y.; Chen, Z.; Lu, W.; Zhang, Y. A High-Voltage-Compliant 86% Peak Efficiency Current-Mode Stimulator with Dynamic Voltage Supply for Implantable Medical Devices. IEEE J. Solid-State Circuits 2024, 35, 1–13. [Google Scholar] [CrossRef]

- Tanzawa, T. On-Chip-High-Voltage Generator Design: Design Methodology for Charge Pumps, 2nd ed.; Springer International Publishing: Berlin/Heidelberg, Germany, 2016; ISBN 978-3-319-21974-5. [Google Scholar]

- Ballo, A.; Grasso, A.D.; Palumbo, D. A Bulk Current Regulation Technique for Dual-Branch Cross-Coupled Charge Pumps. IEEE Trans. Circuits Syst. II: Express Briefs 2022, 69, 4128–4132. [Google Scholar] [CrossRef]

- Ballo, A.; Grasso, A.D.; Palumbo, G. A Review of Charge Pump Topologies for the Power Management of IoT Nodes. Electronics 2019, 8, 480. [Google Scholar] [CrossRef]

- Abdi, A.; Kim, H.S.; Cha, H.K. A High-Voltage Generation Charge-Pump IC Using Input Voltage Modulated Regulation for Neural Implant Devices. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 342–346. [Google Scholar] [CrossRef]

- Zhou, Y.; Wang, K.; Yin, S. A Fully Integrated Stimulator with High Stimulation Voltage Compliance Using Dynamic Bulk Biasing Technique in a Bulk CMOS Technology. IEEE Trans. Circuits Syst. I Regul. Pap. 2024, 71, 2525–2537. [Google Scholar] [CrossRef]

- Zhao, J.; Yao, L.; Xue, R.F.; Li, P.; Je, M.; Xu, Y.P. An Integrated Wireless Power Management and Data Telemetry IC for High-Compliance-Voltage Electrical Stimulation Applications. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 113–124. [Google Scholar] [CrossRef] [PubMed]

- Urso, A.V.; Giagka, M.; Dongen, V.; Serdijn, W.A. An Ultra High-Frequency 8-Channel Neurostimulator Circuit with 68% Peak Power Efficiency. IEEE Trans. Biomed. Circuits Syst. 2019, 13, 882–892. [Google Scholar] [CrossRef] [PubMed]

- Palomeque-Mangut, D.; Rodríguez-Vázquez, Á.; Delgado-Restituto, M. A Fully Integrated, Power-Efficient, 0.07–2.08 mA, High-Voltage Neural Stimulator in a Standard CMOS Process. Sensors 2022, 22, 6429. [Google Scholar] [CrossRef] [PubMed]

- Feyerick, M.; Dehaene, W. Dense, 11 V-Tolerant, Balanced Stimulator IC with Digital Time-Domain Calibration for $< $100 nA Error. IEEE Trans. Biomed. Circuits Syst. 2023, 17, 1166–1176. [Google Scholar] [CrossRef] [PubMed]

- Luo, Z.; Ker, M.D. A High-Voltage-Tolerant and Power-Efficient Stimulator with Adaptive Power Supply Realized in Low-Voltage CMOS Process for Implantable Biomedical Applications. IEEE J. Emerg. Sel. Top. Circuits Syst. 2018, 8, 178–186. [Google Scholar] [CrossRef]

| This Work | [8] | [16] | [17] | [18] | |

|---|---|---|---|---|---|

| Vin | 1.65 V | 3.3 V | 2.8 V | 3.3 V | 4.6 V |

| Vout | 4.20, 7.02, 9.86, 12.69 V | 17.0 V | 12.8 V | 16.5 V | 20.0 V |

| Max Iout | 1 mA | 0.31 mA | 1 mA | 1 mA | 0.6 mA |

| CLK freq | 500 Hz | 2.5 MHz | 10 kHz | 20 MHz | 3 kHz–1 MHz |

| Vout ripple | 0.244% | N/A | 1% @Max load | 1%@Max load | <0.6%@Max load |

| Max efficiency | 74.9% | <10% | 84.7% | 53% | 82% |

| CMOS technology | 0.18 μm | 0.35 μm | 0.18 μm | 0.18 μm | HV 0.18 μm |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, Y.; Cheong, J.; Liu, C. High-Efficiency, Low-Power, Fully Integrated Neural Electrical Stimulation Circuit. Appl. Sci. 2025, 15, 6737. https://doi.org/10.3390/app15126737

Wang Y, Cheong J, Liu C. High-Efficiency, Low-Power, Fully Integrated Neural Electrical Stimulation Circuit. Applied Sciences. 2025; 15(12):6737. https://doi.org/10.3390/app15126737

Chicago/Turabian StyleWang, Yujiao, Jiahao Cheong, and Cheng Liu. 2025. "High-Efficiency, Low-Power, Fully Integrated Neural Electrical Stimulation Circuit" Applied Sciences 15, no. 12: 6737. https://doi.org/10.3390/app15126737

APA StyleWang, Y., Cheong, J., & Liu, C. (2025). High-Efficiency, Low-Power, Fully Integrated Neural Electrical Stimulation Circuit. Applied Sciences, 15(12), 6737. https://doi.org/10.3390/app15126737