Electrical Performance of ZTO Thin-Film Transistors and Inverters

Abstract

1. Introduction

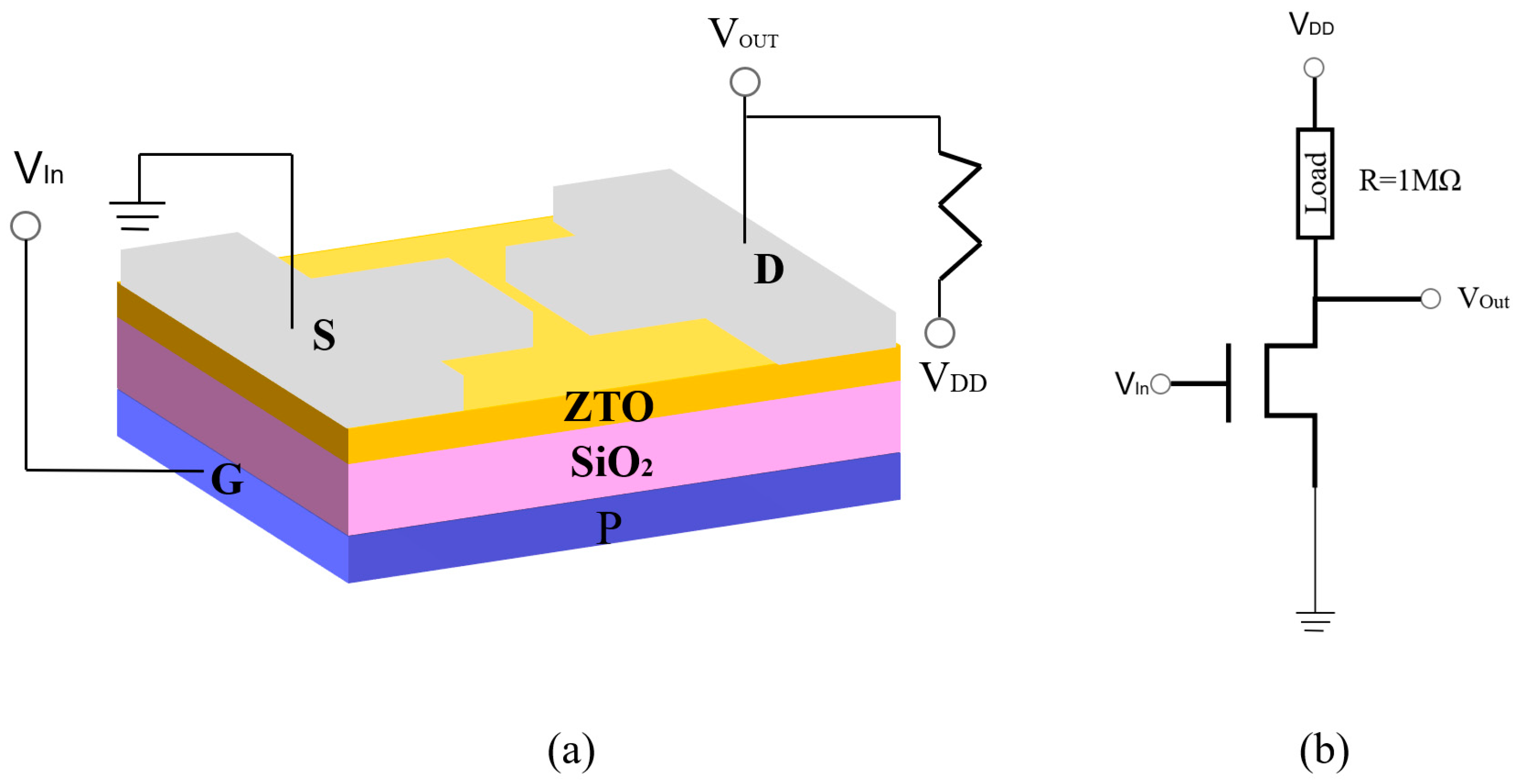

2. Experimental Process

3. Results and Discussion

3.1. Thin-Film Transmission Spectrum Analysis

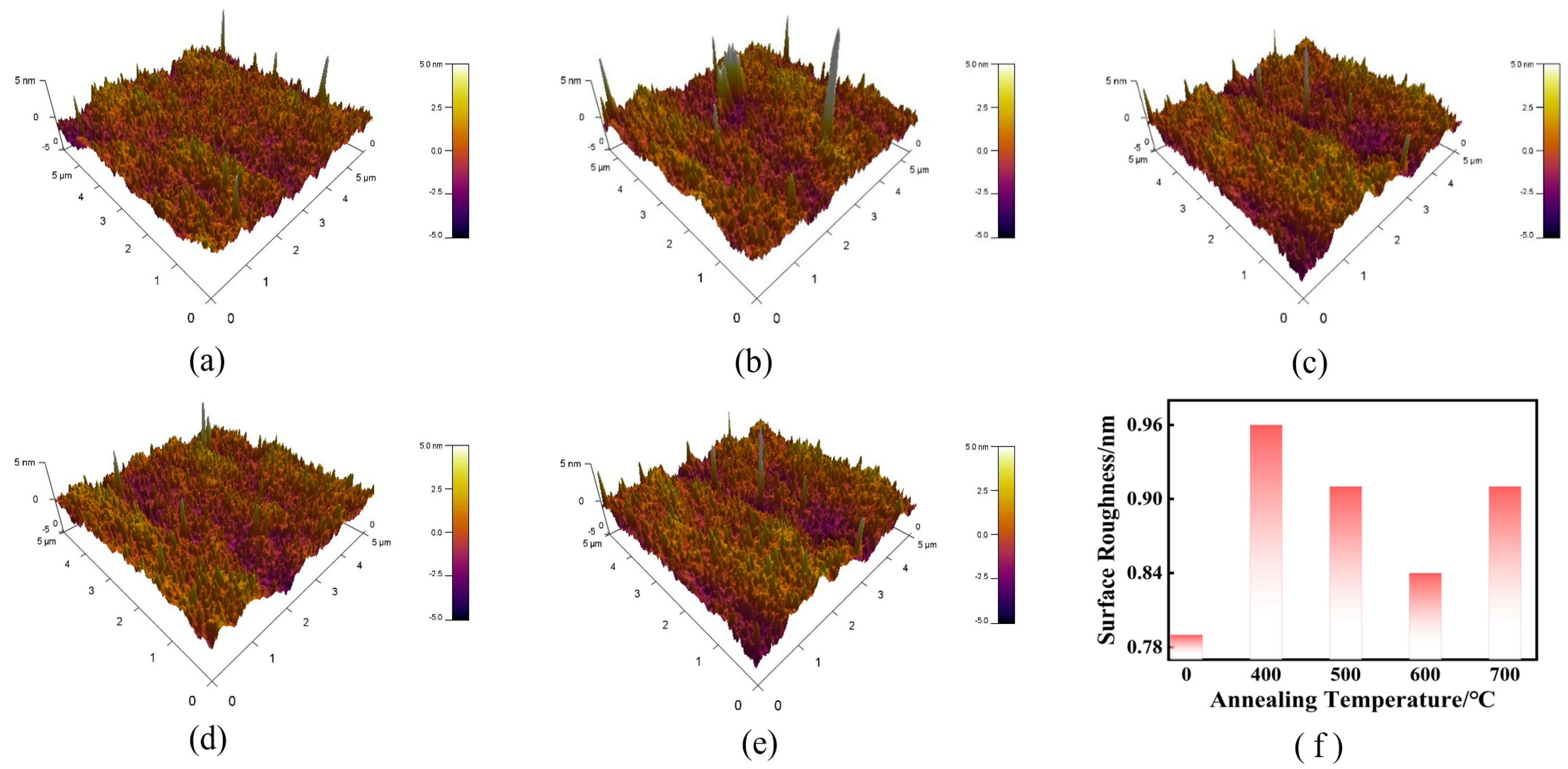

3.2. Film AFM Characterization Analysis

3.3. XPS Analysis of ZTO Thin Films

3.4. Electrical Performance of ZTO TFTs

3.5. Resistor-Load Inverter

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Lim, H.S.; Rim, Y.S.; Kim, D.L.; Jeong, W.H.; Kim, H.J. Carrier-Suppressing Effect of Mg in Solution-Processed Zn-Sn-O Thin-Film Transistors. Electrochem. Solid-State Lett. 2012, 15, H78. [Google Scholar] [CrossRef]

- Kim, M.H.; Lee, H.S. Effect of In Addition and Annealing Temperature on the Device Performance of Solution-Processed In–Zn–Sn–O Thin Film Transistors. Solid-State Electron. 2014, 96, 14–18. [Google Scholar] [CrossRef]

- Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors Using Amorphous Oxide Semiconductors. Nature 2004, 432, 488–492. [Google Scholar] [CrossRef] [PubMed]

- Zhu, Y.; He, Y.; Jiang, S.; Zhu, L.; Chen, C.; Wan, Q. Indium–Gallium–Zinc–Oxide Thin-Film Transistors: Materials, Devices, and Applications. J. Semicond. 2021, 42, 031101. [Google Scholar] [CrossRef]

- Estrada, M.; Hernandez-Barrios, Y.; Moldovan, O.; Cerdeira, A.; Lime, F.; Pavanello, M.; Iñiguez, B. Effect of the Distribution of States in Amorphous In-Ga-Zn-O Layers on the Conduction Mechanism of Thin Film Transistors on Its Base. Facta Univ. Ser. Electron. Energ. 2018, 31, 1–9. [Google Scholar] [CrossRef]

- Estrada, M.; Rivas, M.; Garduño, I.; Avila-Herrera, F.; Cerdeira, A.; Pavanello, M.; Mejia, I.; Quevedo-Lopez, M.A. Temperature Dependence of the Electrical Characteristics up to 370 K of Amorphous In-Ga-ZnO Thin Film Transistors. Microelectron. Reliab. 2016, 56, 29–33. [Google Scholar] [CrossRef]

- Seok, M.J.; Choi, M.H.; Mativenga, M.; Geng, D.; Kim, D.Y.; Jang, J. A Full-Swing a-IGZO TFT-Based Inverter with a Top-Gate-Bias-Induced Depletion Load. IEEE Electron Device Lett. 2011, 32, 1089–1091. [Google Scholar] [CrossRef]

- Park, J.-S. Characteristics of Short-Channel Amorphous In-Ga-Zn-O Thin Film Transistors and Their Circuit Performance as a Load Inverter. J. Electroceram. 2012, 28, 74–79. [Google Scholar] [CrossRef]

- Wang, M.; Liang, L.; Luo, H.; Zhang, S.; Zhang, H.; Javaid, K.; Cao, H. Threshold Voltage Tuning in A-IGZO TFTs with Ultrathin SnOx Capping Layer and Application to Depletion-Load Inverter. IEEE Electron Device Lett. 2016, 37, 422–425. [Google Scholar] [CrossRef]

- Zhang, Y.C.; He, G.; Zhang, C.; Zhu, L.; Yang, B.; Lin, Q.B.; Jiang, X.S. Oxygen Partial Pressure Ratio Modulated Electrical Performance of Amorphous InGaZnO Thin Film Transistor and Inverter. J. Alloys Compd. 2018, 765, 791–799. [Google Scholar] [CrossRef]

- Wager, J.F.; Yeh, B.; Hoffman, R.L.; Keszler, D.A. An Amorphous Oxide Semiconductor Thin-Film Transistor Route to Oxide Electronics. Curr. Opin. Solid State Mater. Sci. 2014, 18, 53–61. [Google Scholar] [CrossRef]

- Raj, R.; Gupta, H.; Purohit, L.P. ZTO Transparent Conducting Thin Films for Optoelectronic Applications. Bull. Mater. Sci. 2021, 44, 165. [Google Scholar] [CrossRef]

- Yu, S.; Xu, W.; Zhu, H.; Qiu, W.; Fu, Q.; Kong, L. Effect of Sputtering Power on Structure and Properties of ZTO Films. J. Alloys Compd. 2021, 883, 160622. [Google Scholar] [CrossRef]

- Xu, Y.; Li, X.; Zhu, L.; Zhang, J. Defect Modification in ZnInSnO Transistor with Solution-Processed Al2O3 Dielectric by Annealing. Mater. Sci. Semicond. Process. 2016, 46, 23–28. [Google Scholar] [CrossRef]

- Pan, W.; Zhou, X.; Lin, Q.; Chen, J.; Lu, L.; Zhang, S. Low Temperature and High-Performance ZnSnO Thin-Film Transistors Engineered by in Situ Thermal Manipulation. J. Mater. Chem. C 2022, 10, 3129–3138. [Google Scholar] [CrossRef]

- Wang, C.; Guo, L.; Lei, M.; Wang, C.; Chu, X.; Yang, F.; Gao, X.; Wamg, H.; Chi, Y.; Yang, X. Effect of Annealing Temperature on Electrical Properties of ZTO Thin-Film Transistors. Nanomaterials 2022, 12, 2397. [Google Scholar] [CrossRef] [PubMed]

- Yue, S.; Lu, J.; Lu, R.; Li, S.; Lu, B.; Li, X.; Zhang, J.; Zeng, Y.-J.; Ye, Z. Ultra-Thin-Film Transistors Based on Ultra-Thin Amorphous ZnSnO Films. Appl. Phys. A 2018, 124, 848. [Google Scholar] [CrossRef]

- Ghosh, D.S.; Chen, T.L.; Pruneri, V. High Figure-of-Merit Ultrathin Metal Transparent Electrodes Incorporating a Conductive Grid. Appl. Phys. Lett. 2010, 96, 041109. [Google Scholar] [CrossRef]

- Wang, Y.; Miska, P.; Pilloud, D.; Horwat, D.; Mücklich, F.; Pierson, J.F. Transmittance Enhancement and Optical Band Gap Widening of Cu2O Thin Films after Air Annealing. J. Appl. Phys. 2014, 115, 073505. [Google Scholar] [CrossRef]

- Oh, B.-Y.; Jeong, M.-C.; Ham, M.-H.; Myoung, J.-M. Effects of the Channel Thickness on the Structural and Electrical Characteristics of Room-Temperature Fabricated ZnO Thin-Film Transistors. Semicond. Sci. Technol. 2007, 22, 608–612. [Google Scholar] [CrossRef]

- Zhu, D.L.; Wang, Q.; Han, S.; Cao, P.J.; Liu, W.J.; Jia, F.; Zeng, Y.X.; Ma, X.C.; Lu, Y.M. Optimization of Process Parameters for the Electrical Properties in Ga-Doped ZnO Thin Films Prepared by r.f. Magnetron Sputtering. Appl. Surf. Sci. 2014, 298, 208–213. [Google Scholar] [CrossRef]

- Zhong, W.; Li, G.; Lan, L.; Li, B.; Chen, R. Effects of Annealing Temperature on Properties of InSnZnO Thin Film Transistors Prepared by Co-Sputtering. RSC Adv. 2018, 8, 34817–34822. [Google Scholar] [CrossRef] [PubMed]

- Song, E.; Lan, L.; Xiao, P.; Lin, Z.; Sun, S.; Li, Y.; Song, W.; Gao, P.; Peng, J. Thin-Film Transistors with Neodymium-Incorporated Indium–Zinc-Oxide Semiconductors. IEEE Trans. Electron Devices 2016, 63, 1916–1920. [Google Scholar] [CrossRef]

- Kamiya, T.; Nomura, K.; Hosono, H. Origins of High Mobility and Low Operation Voltage of Amorphous Oxide TFTs: Electronic Structure, Electron Transport, Defects and Doping. J. Disp. Technol. 2009, 5, 273–288. [Google Scholar] [CrossRef]

- Jiang, Q.; Feng, L.; Wu, C.; Sun, R.; Li, X.; Lu, B.; Ye, Z.; Lu, J. Amorphous ZnAlSnO Thin-Film Transistors by a Combustion Solution Process for Future Displays. Appl. Phys. Lett. 2015, 106, 053503. [Google Scholar] [CrossRef]

- Cho, D.-H.; Yang, S.; Byun, C.; Shin, J.; Ryu, M.K.; Park, S.-H.K.; Hwang, C.-S.; Chung, S.M.; Cheong, W.-S.; Yoon, S.M.; et al. Transparent Al–Zn–Sn–O Thin Film Transistors Prepared at Low Temperature. Appl. Phys. Lett. 2008, 93, 142111. [Google Scholar] [CrossRef]

- Liu, Y.; Wan, X.; Zhu, L.Q.; Shi, Y.; Wan, Q. Laterally Coupled Dual-Gate Oxide-Based Transistors on Sodium Alginate Electrolytes. IEEE Electron Device Lett. 2014, 35, 1257–1259. [Google Scholar] [CrossRef]

- Lee, S.-K.; Humayun Kabir, S.M.; Sharma, B.K.; Kim, B.J.; Cho, J.H.; Ahn, J.-H. Photo-Patternable Ion Gel-Gated Graphene Transistors and Inverters on Plastic. Nanotechnology 2014, 25, 014002. [Google Scholar] [CrossRef]

- Li, S.; Miyazaki, H.; Lee, M.V.; Liu, C.; Kanda, A.; Tsukagoshi, K. Complementary-Like Graphene Logic Gates Controlled by Electrostatic Doping. Small 2011, 7, 1552–1556. [Google Scholar] [CrossRef]

- Cho, I.-T.; Lee, J.-W.; Park, J.-M.; Cheong, W.-S.; Hwang, C.-S.; Kwak, J.-S.; Cho, I.-H.; Kwon, H.-I.; Shin, H.; Park, B.-G.; et al. Full-Swing a-IGZO Inverter with a Depletion Load Using Negative Bias Instability Under Light Illumination. IEEE Electron Device Lett. 2012, 33, 1726–1728. [Google Scholar] [CrossRef]

| Annealing Temperature/°C | Surface Roughness/nm |

|---|---|

| Not annealed | 0.79 |

| 400 | 0.96 |

| 500 | 0.91 |

| 600 | 0.84 |

| 700 | 0.91 |

| Annealing Temperature | Mobility (cm2 V−1 s−1) | Vth (V) | SS (Decade−1) | Ion/Ioff |

|---|---|---|---|---|

| 400 | 9.12 | 11.21 | 3.46 | 5.70 × 107 |

| 500 | 11.26 | 11.06 | 3.18 | 6.42 × 107 |

| 600 | 12.39 | 6.13 | 0.78 | 1.09 × 108 |

| 700 | 3.41 | 16.30 | 0.95 | 3.20 × 107 |

| VDD (V) | VOH (V) | VOL (V) | VIL (V) | VIH (V) | Vgain (V) | NMH (V) | NML (V) | TW (V) |

|---|---|---|---|---|---|---|---|---|

| 10 | 9.07 | 1.50 | 3.50 | 6.20 | 2.98 | 2.87 | 2.00 | 2.70 |

| 15 | 13.60 | 1.75 | 3.90 | 6.80 | 5.21 | 6.80 | 2.15 | 2.90 |

| 20 | 18.20 | 1.98 | 4.20 | 7.20 | 7.89 | 11.00 | 2.22 | 3.00 |

| 25 | 22.70 | 2.05 | 4.30 | 7.60 | 8.94 | 15.10 | 2.25 | 3.30 |

| 30 | 27.30 | 2.15 | 4.50 | 7.98 | 11.77 | 19.32 | 2.35 | 3.48 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Wang, J.; Guo, L.; Chu, X.; Yang, F.; Gao, H.; Wang, C.; Chi, Y.; Yang, X. Electrical Performance of ZTO Thin-Film Transistors and Inverters. Micromachines 2025, 16, 751. https://doi.org/10.3390/mi16070751

Wang J, Guo L, Chu X, Yang F, Gao H, Wang C, Chi Y, Yang X. Electrical Performance of ZTO Thin-Film Transistors and Inverters. Micromachines. 2025; 16(7):751. https://doi.org/10.3390/mi16070751

Chicago/Turabian StyleWang, Jieyang, Liang Guo, Xuefeng Chu, Fan Yang, Hansong Gao, Chao Wang, Yaodan Chi, and Xiaotian Yang. 2025. "Electrical Performance of ZTO Thin-Film Transistors and Inverters" Micromachines 16, no. 7: 751. https://doi.org/10.3390/mi16070751

APA StyleWang, J., Guo, L., Chu, X., Yang, F., Gao, H., Wang, C., Chi, Y., & Yang, X. (2025). Electrical Performance of ZTO Thin-Film Transistors and Inverters. Micromachines, 16(7), 751. https://doi.org/10.3390/mi16070751