Novel Quantum-Dot Cellular Automata-Based Gate Designs for Efficient Reversible Computing

Abstract

1. Introduction

2. Background

2.1. Sustainable Computing

2.2. Reversible Computing

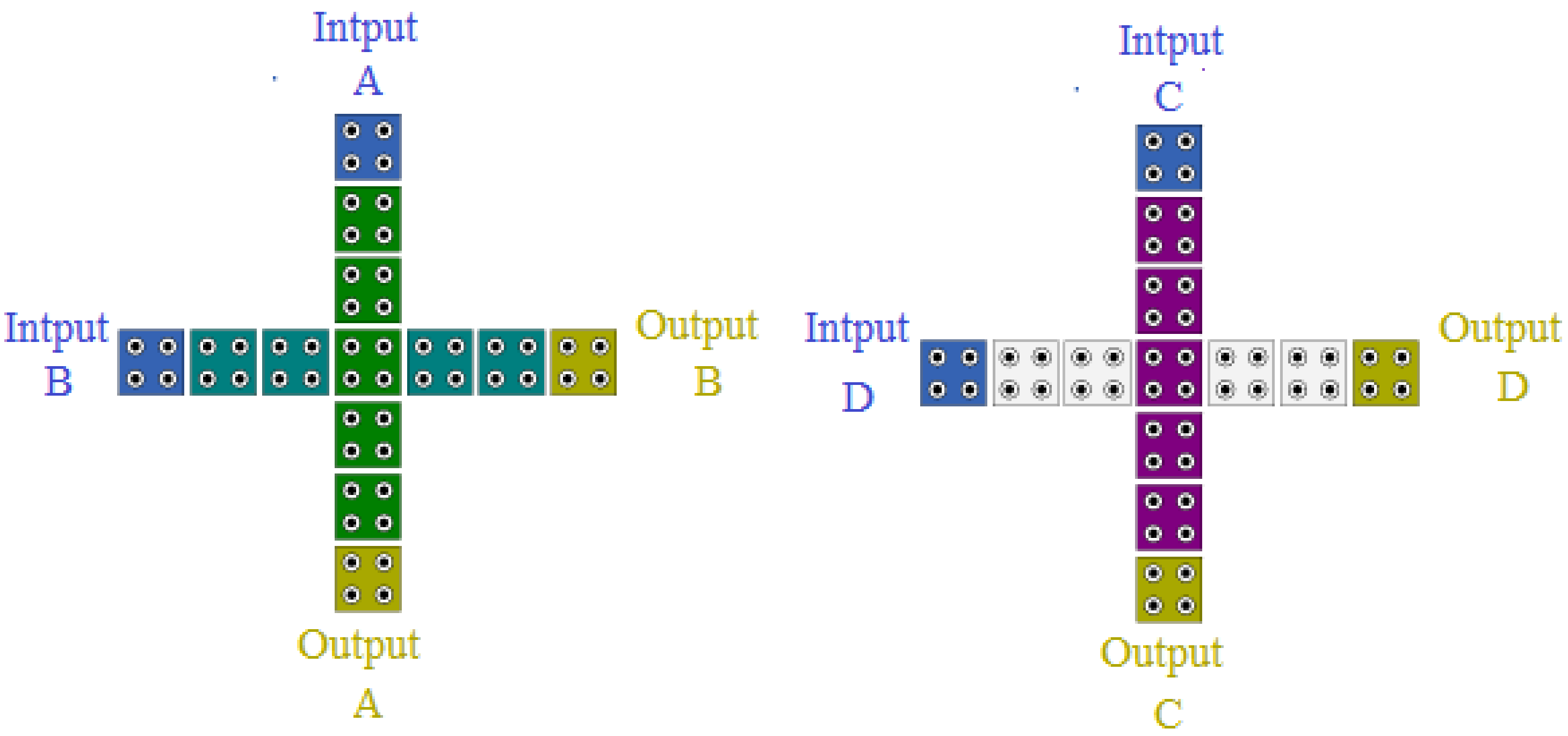

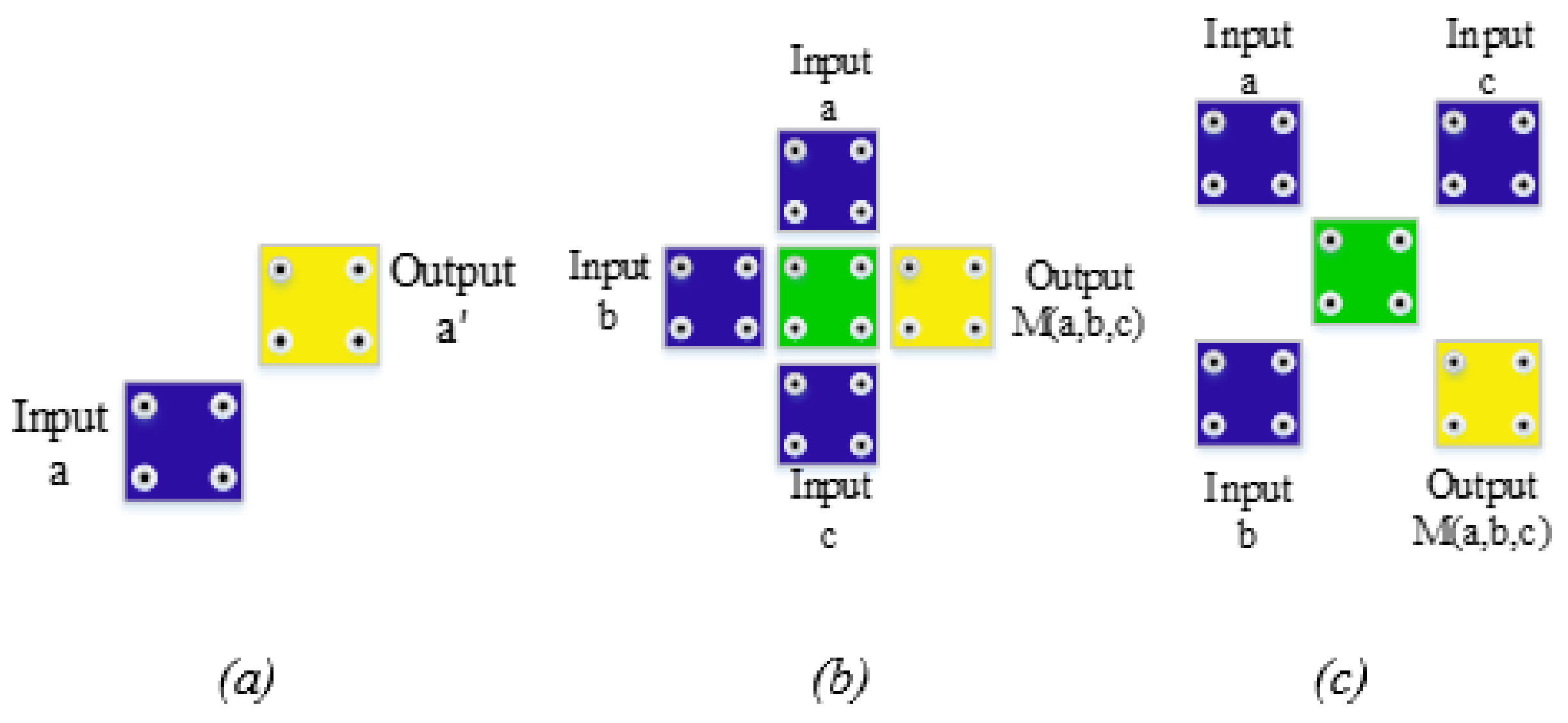

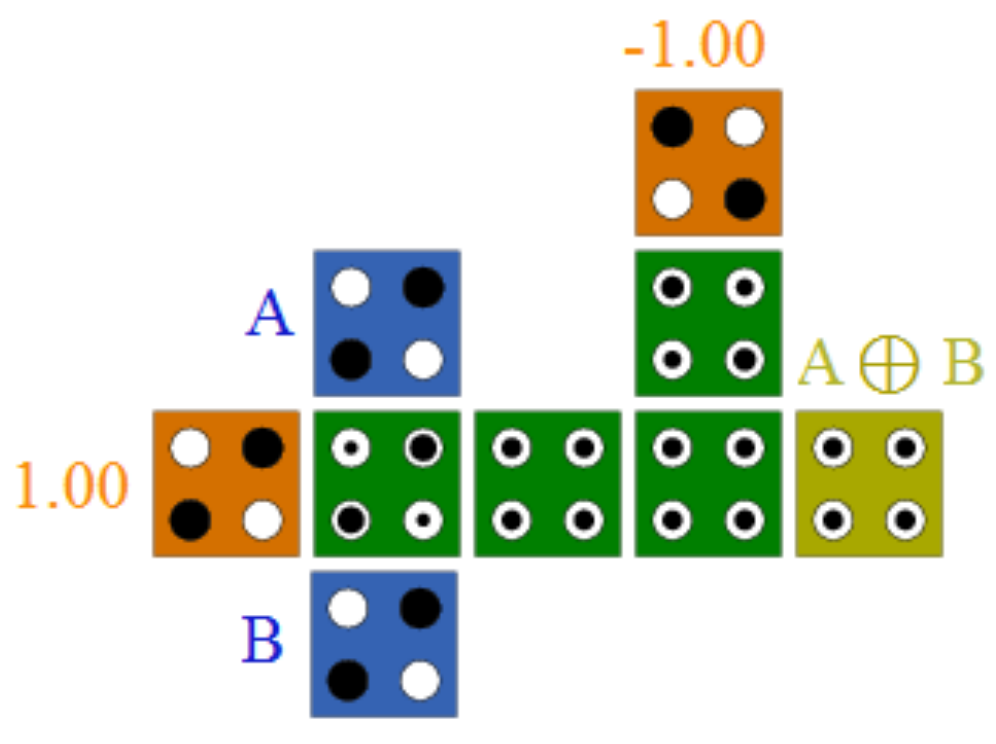

2.3. Quantum-Dot Cellular Automata

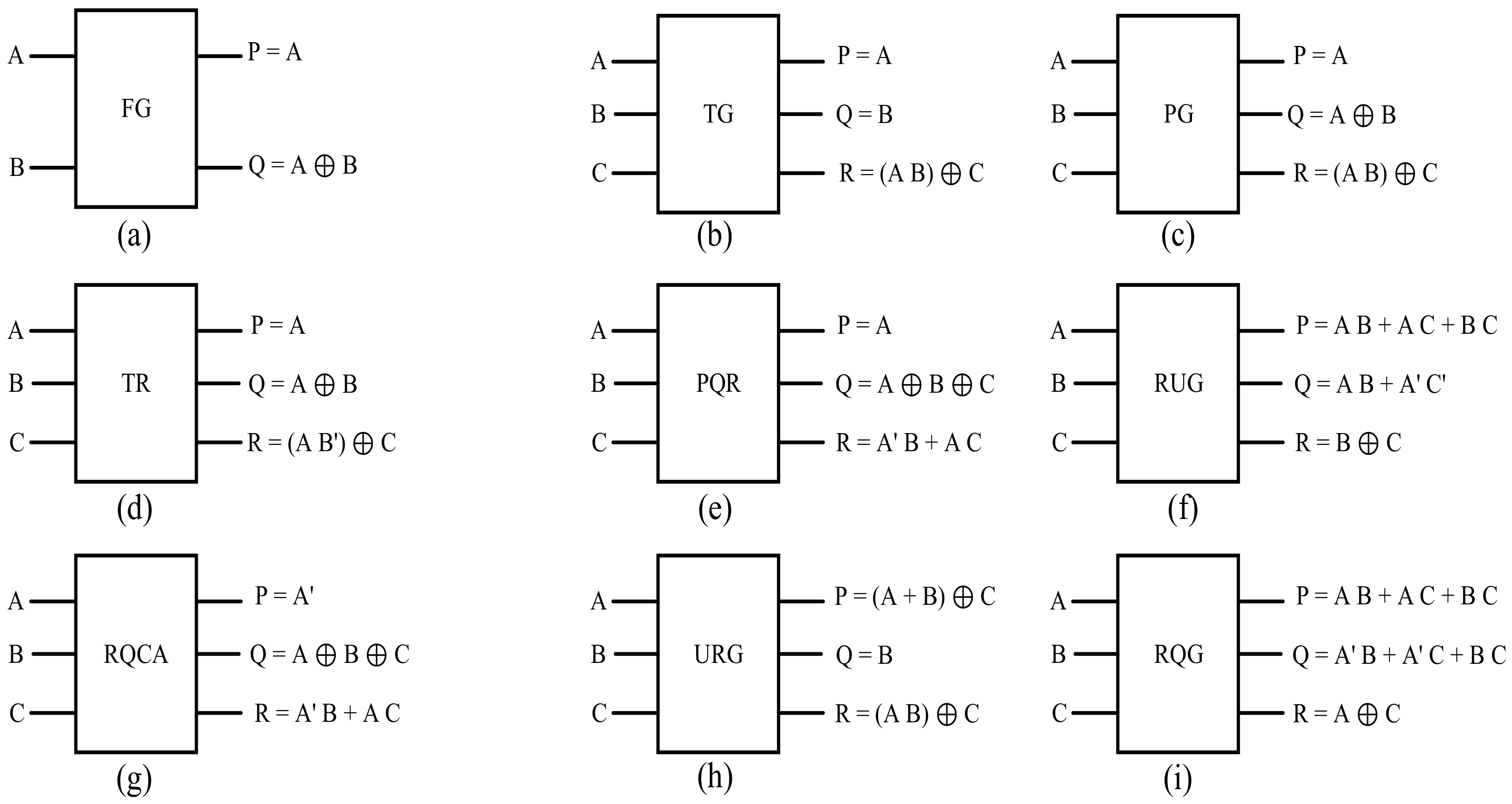

3. The Proposed Circuits

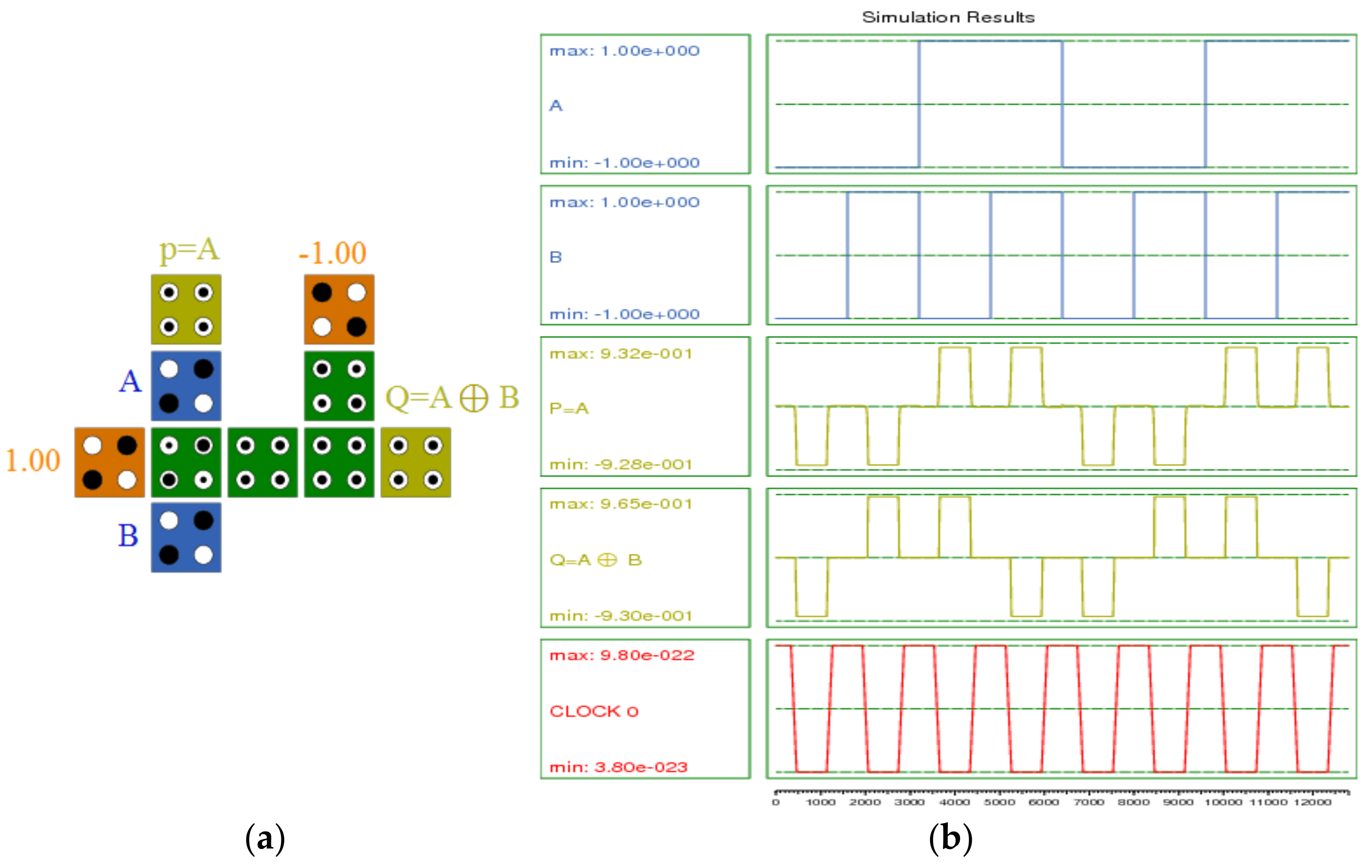

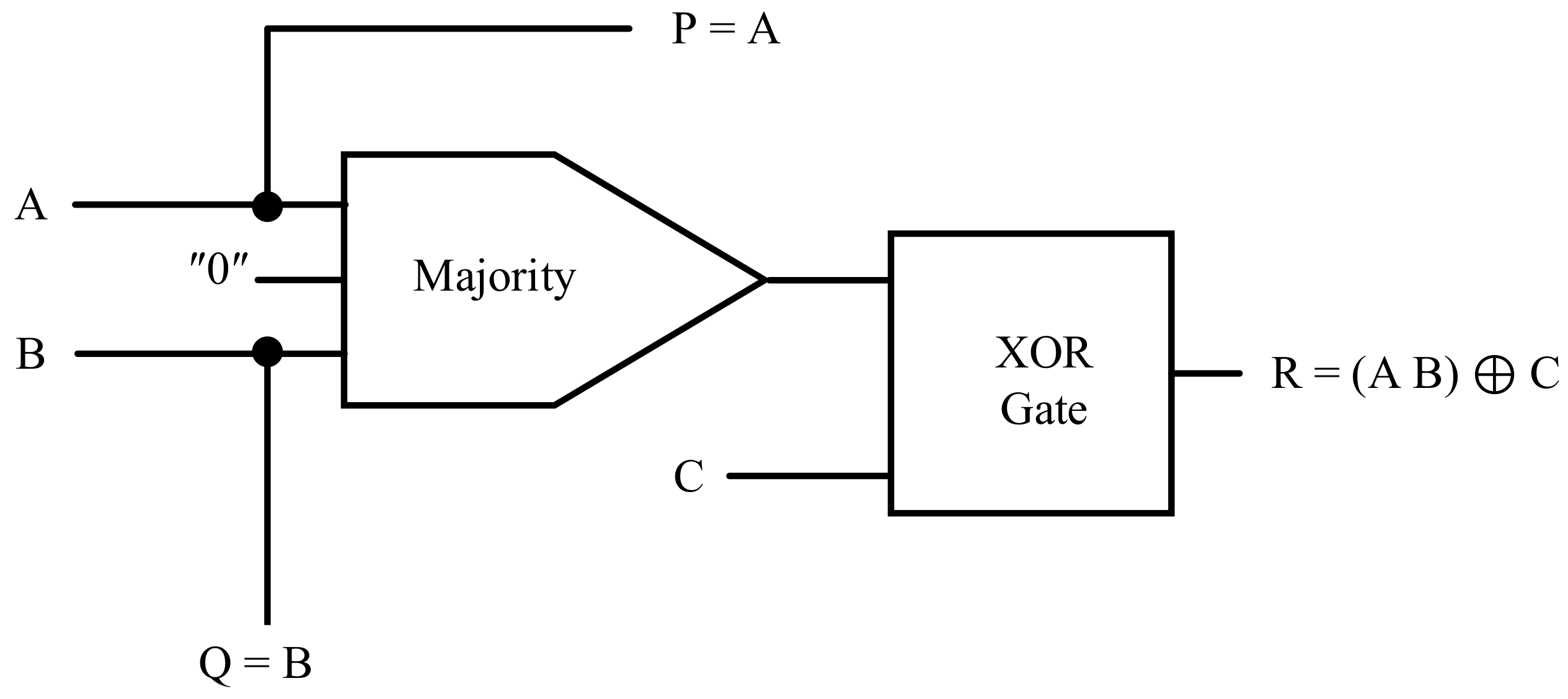

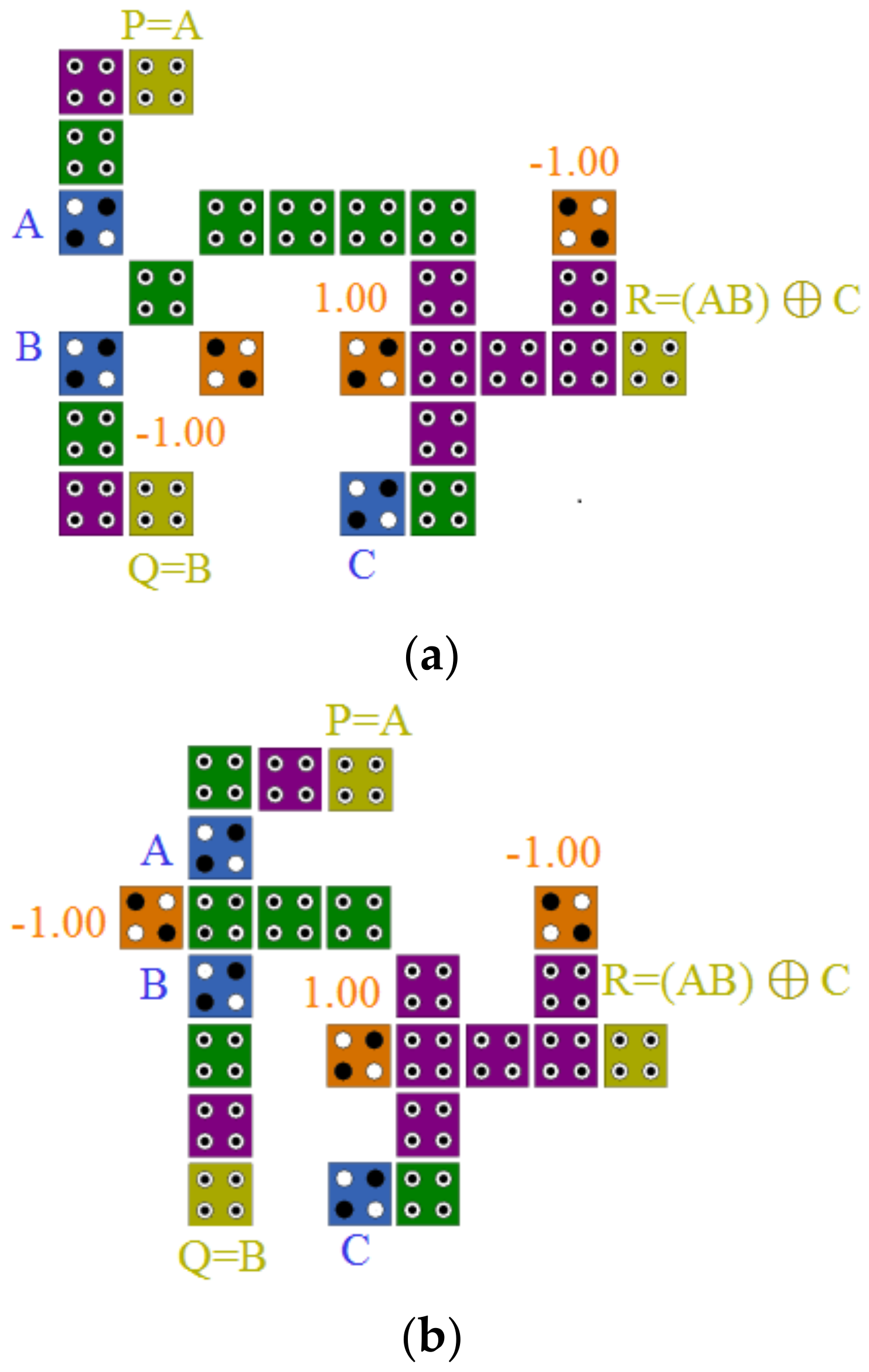

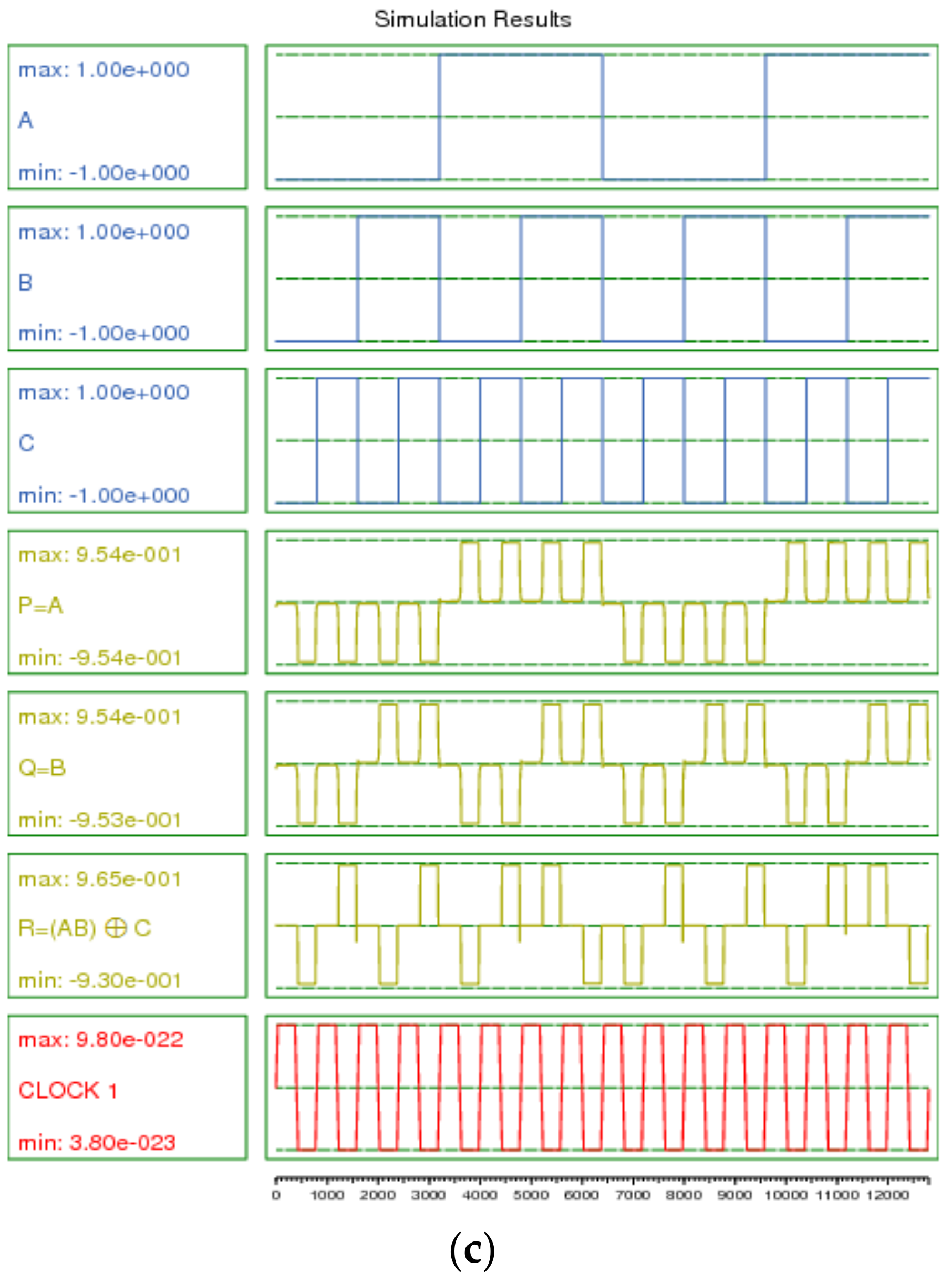

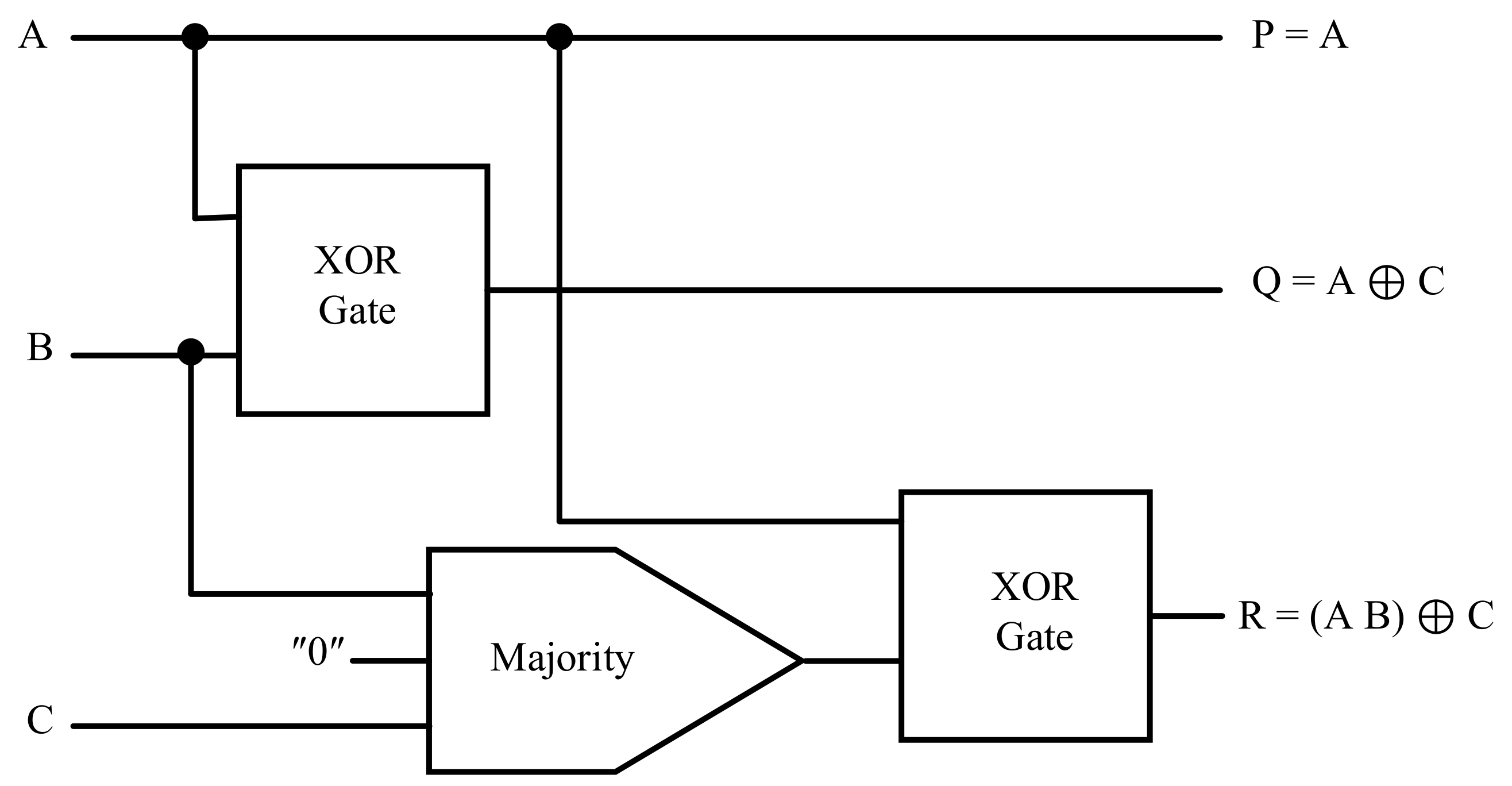

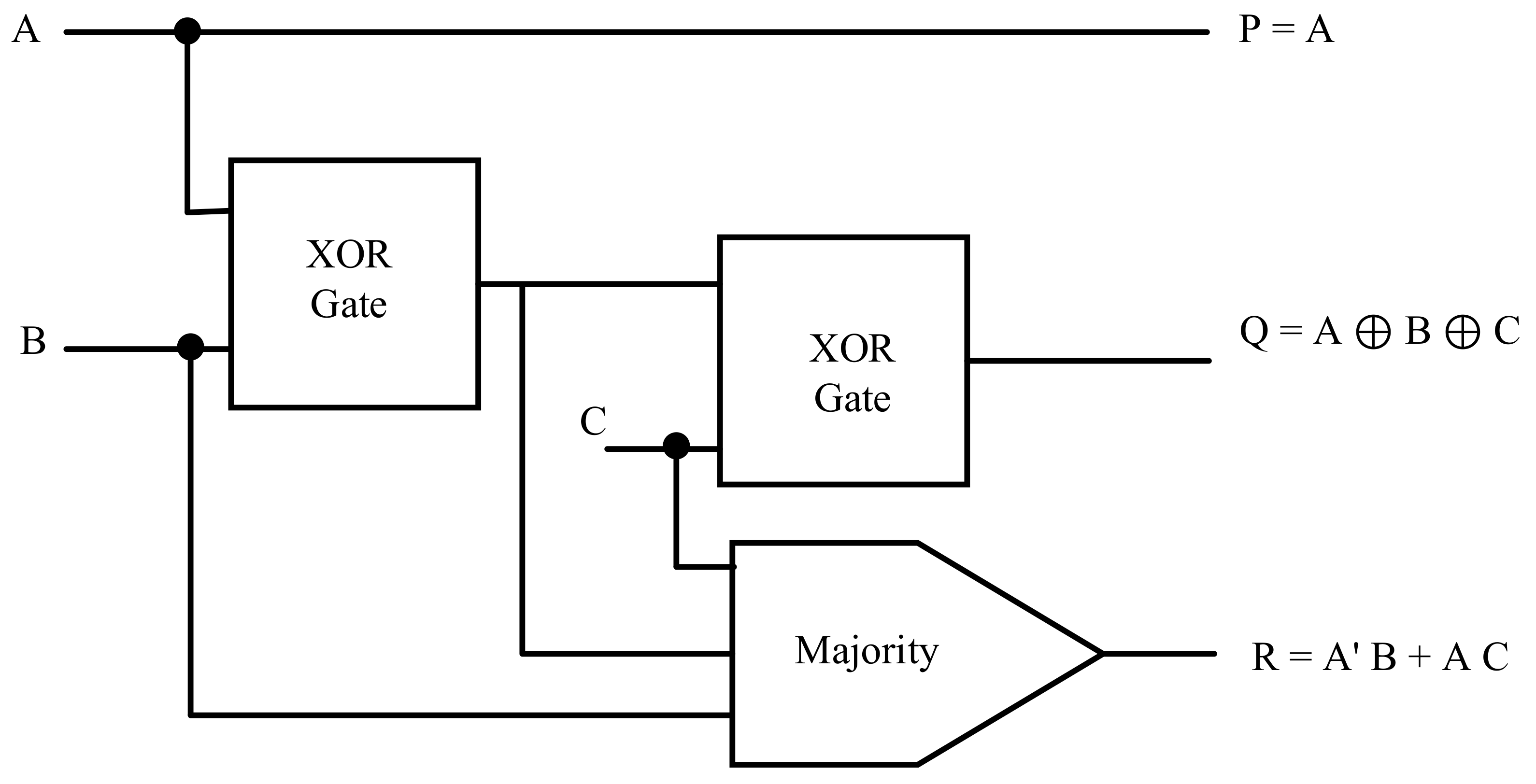

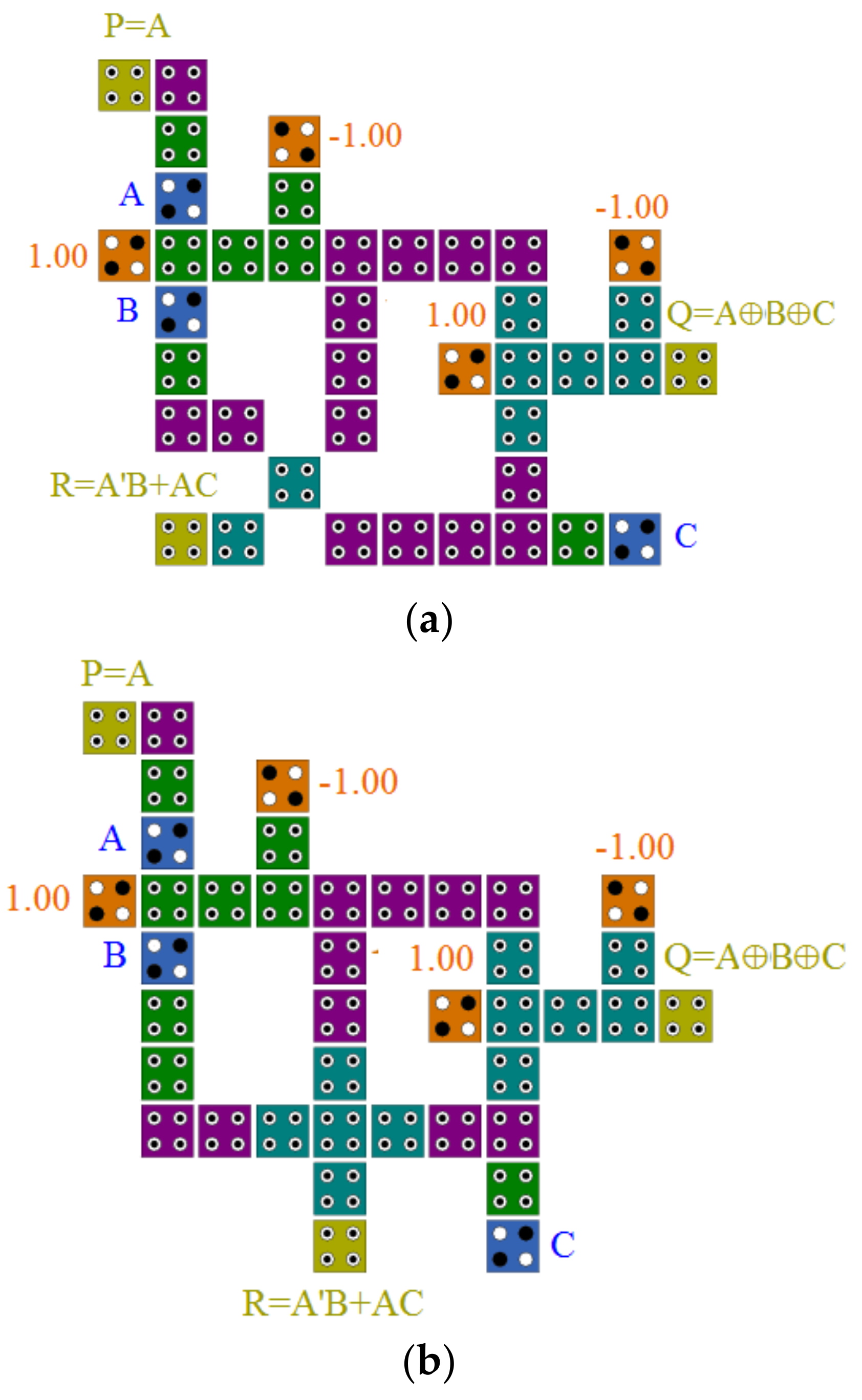

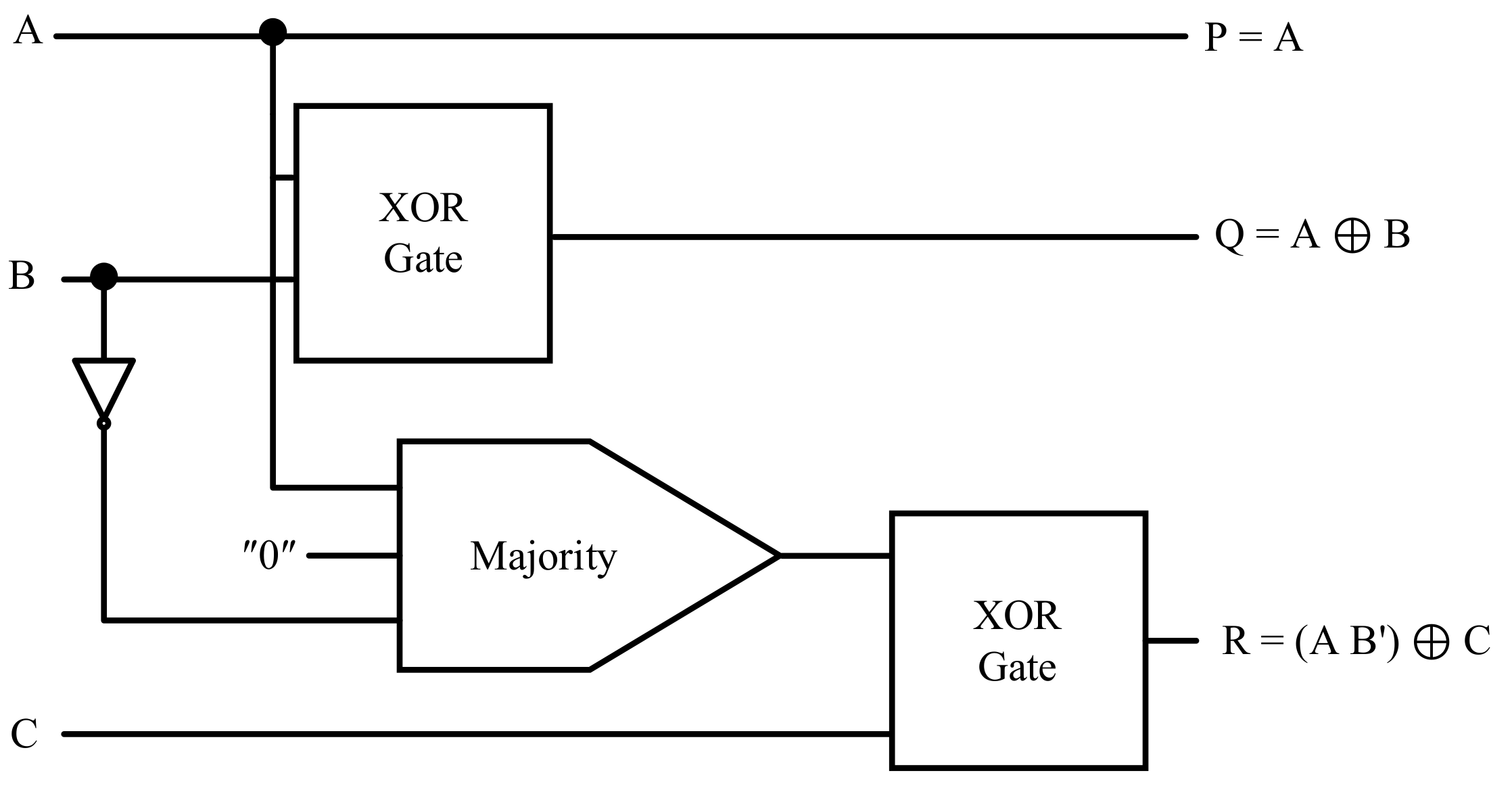

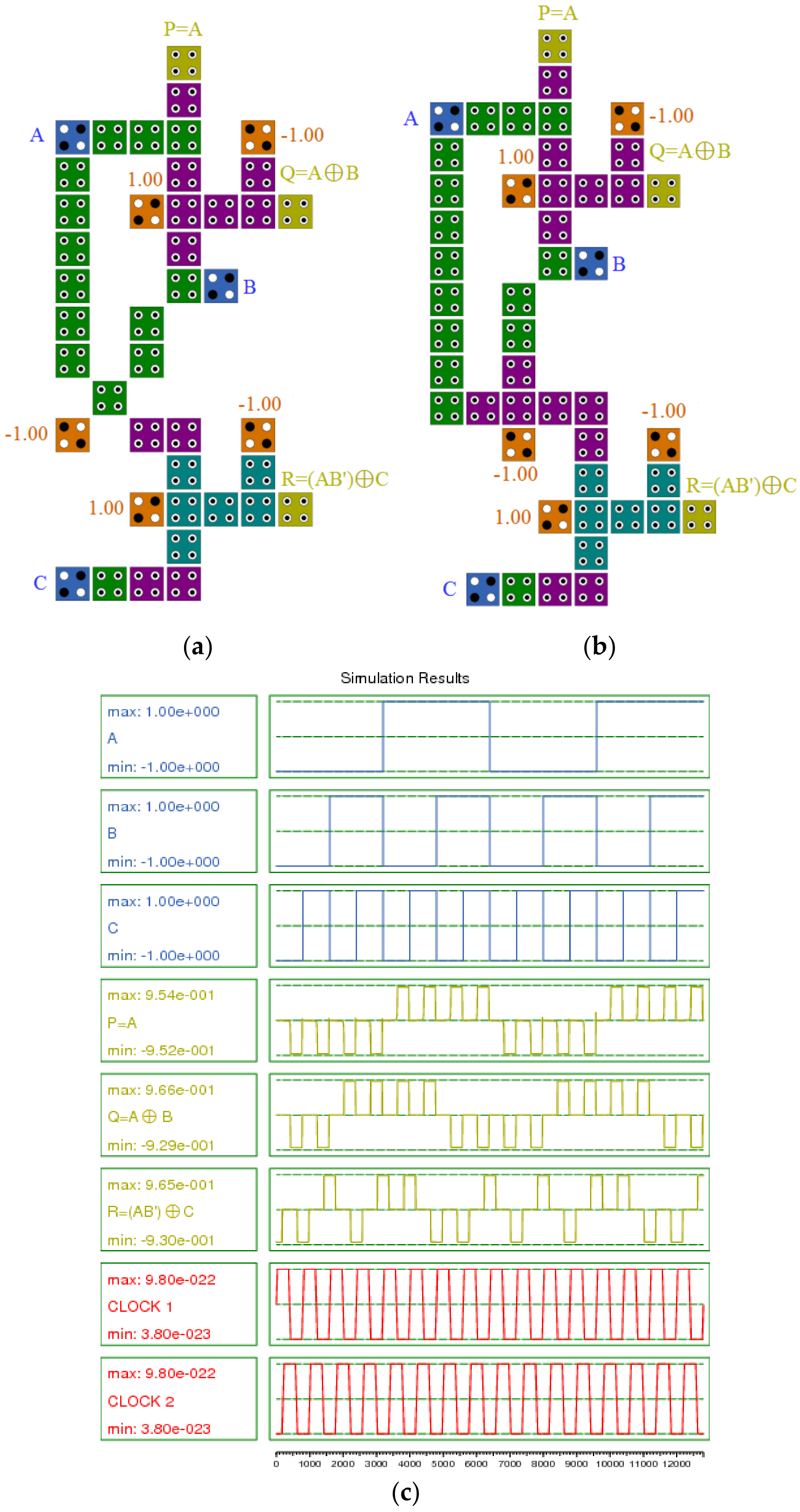

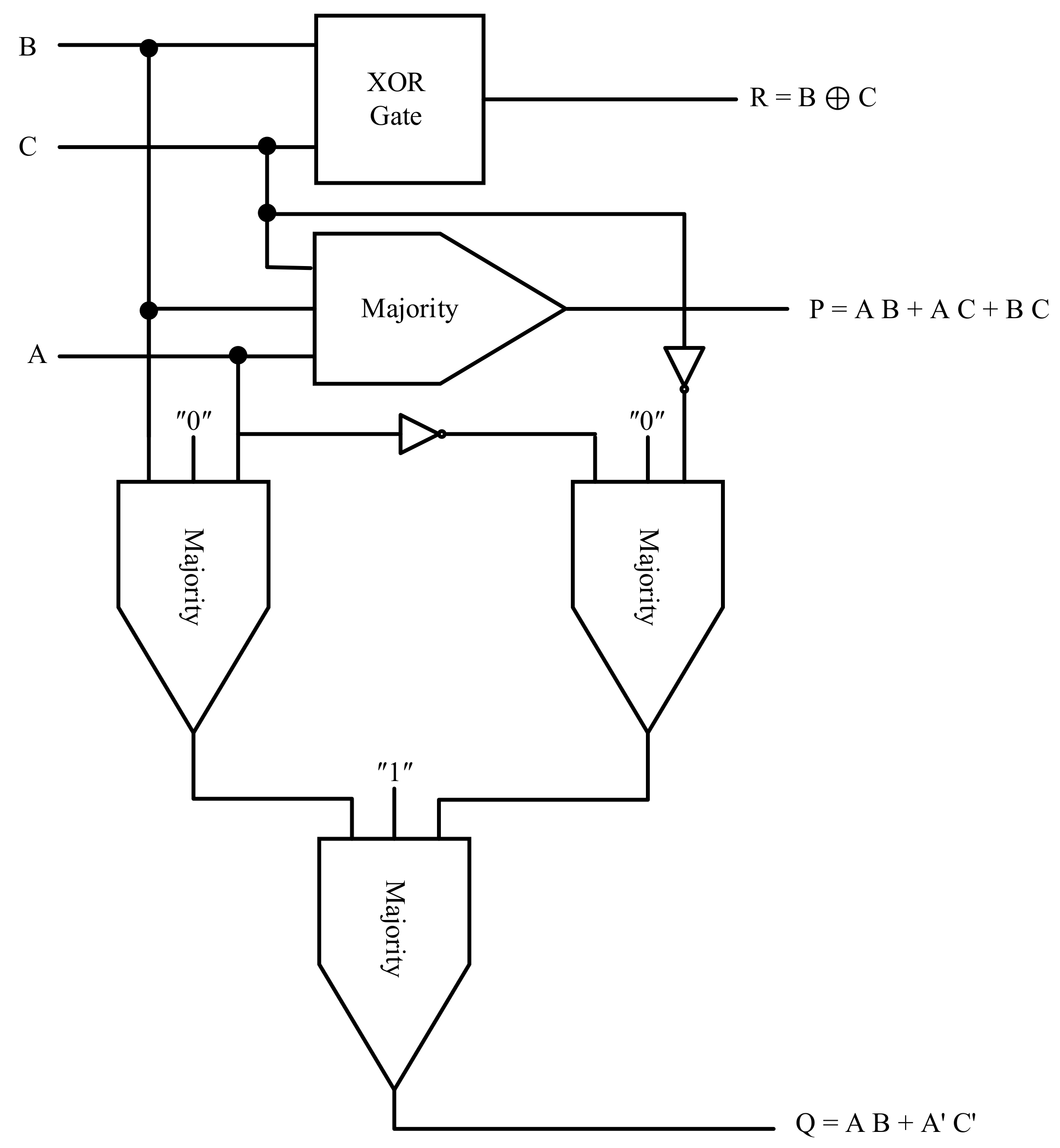

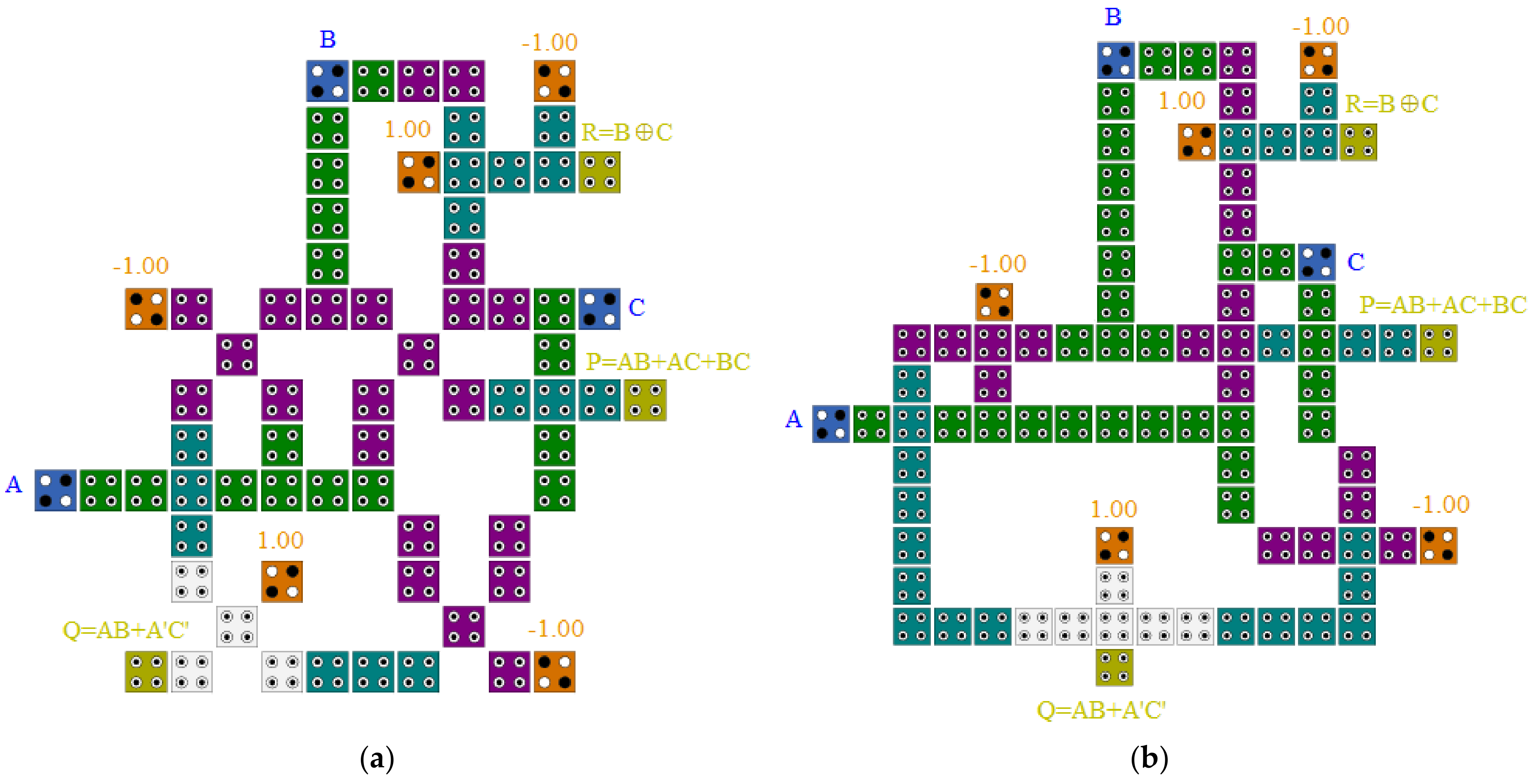

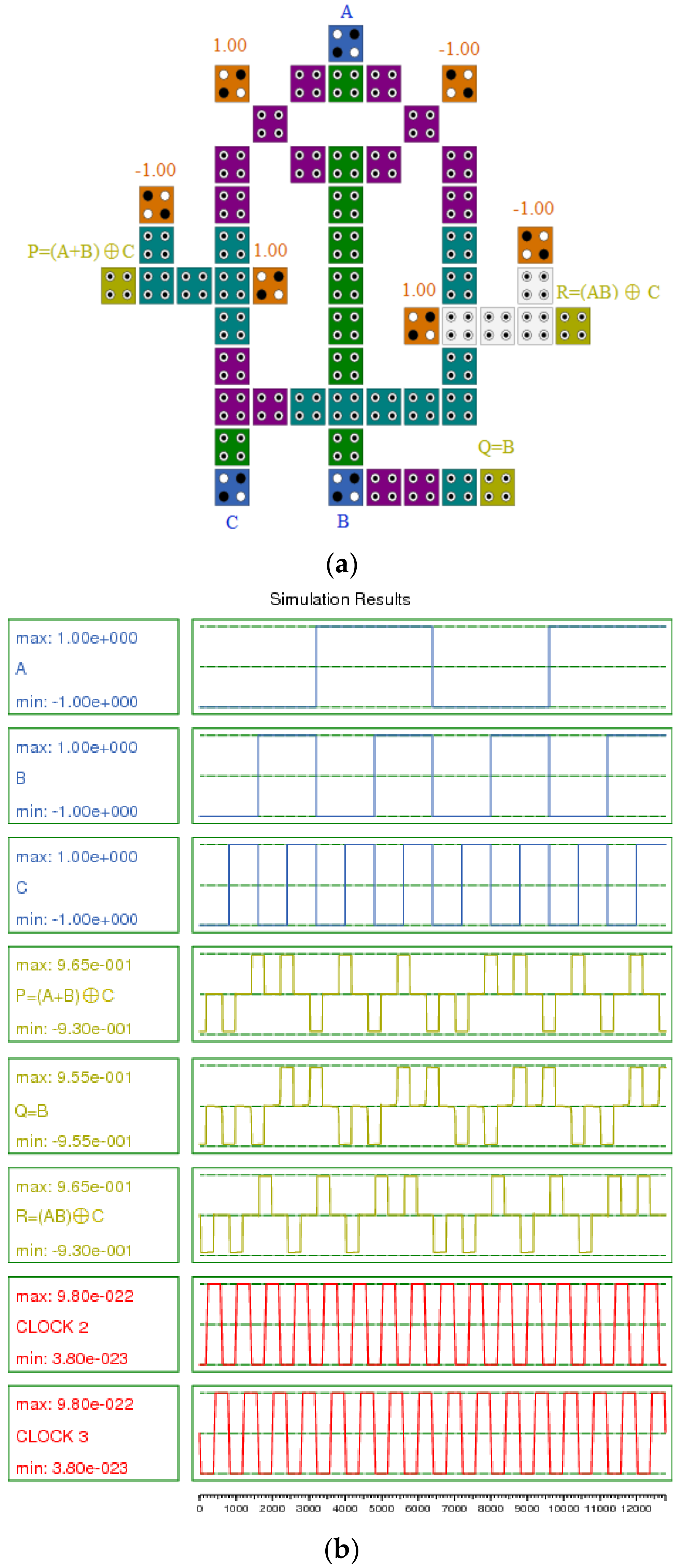

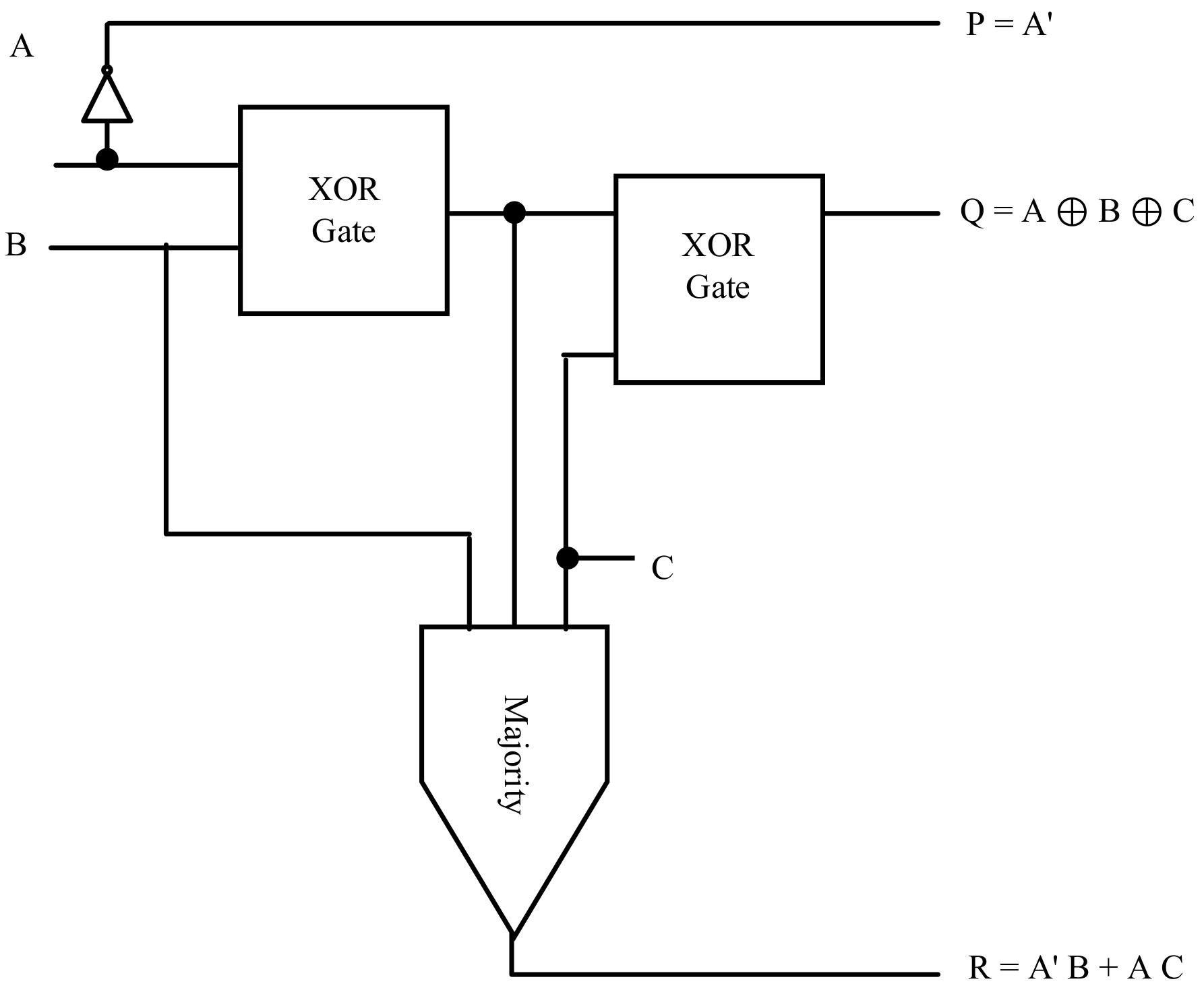

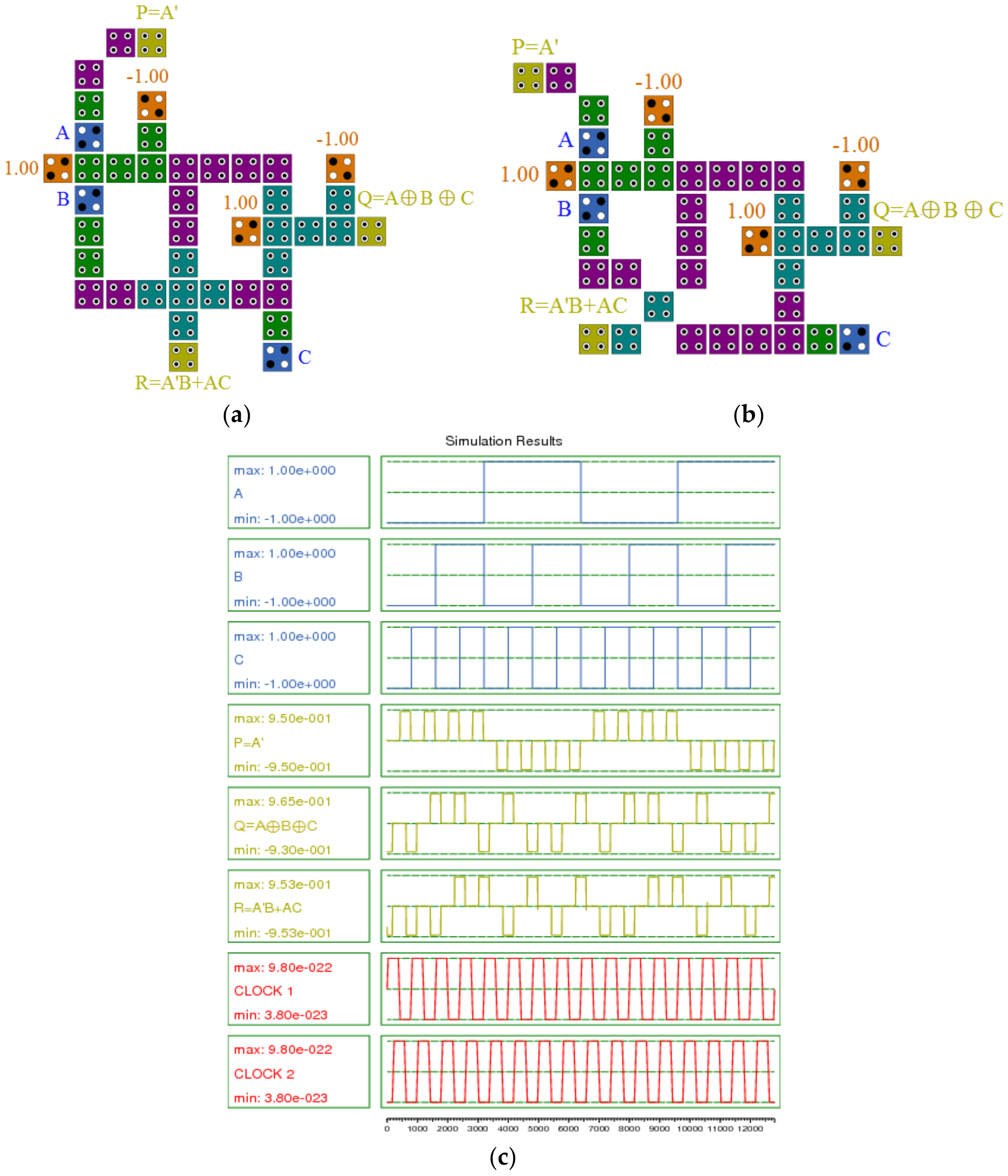

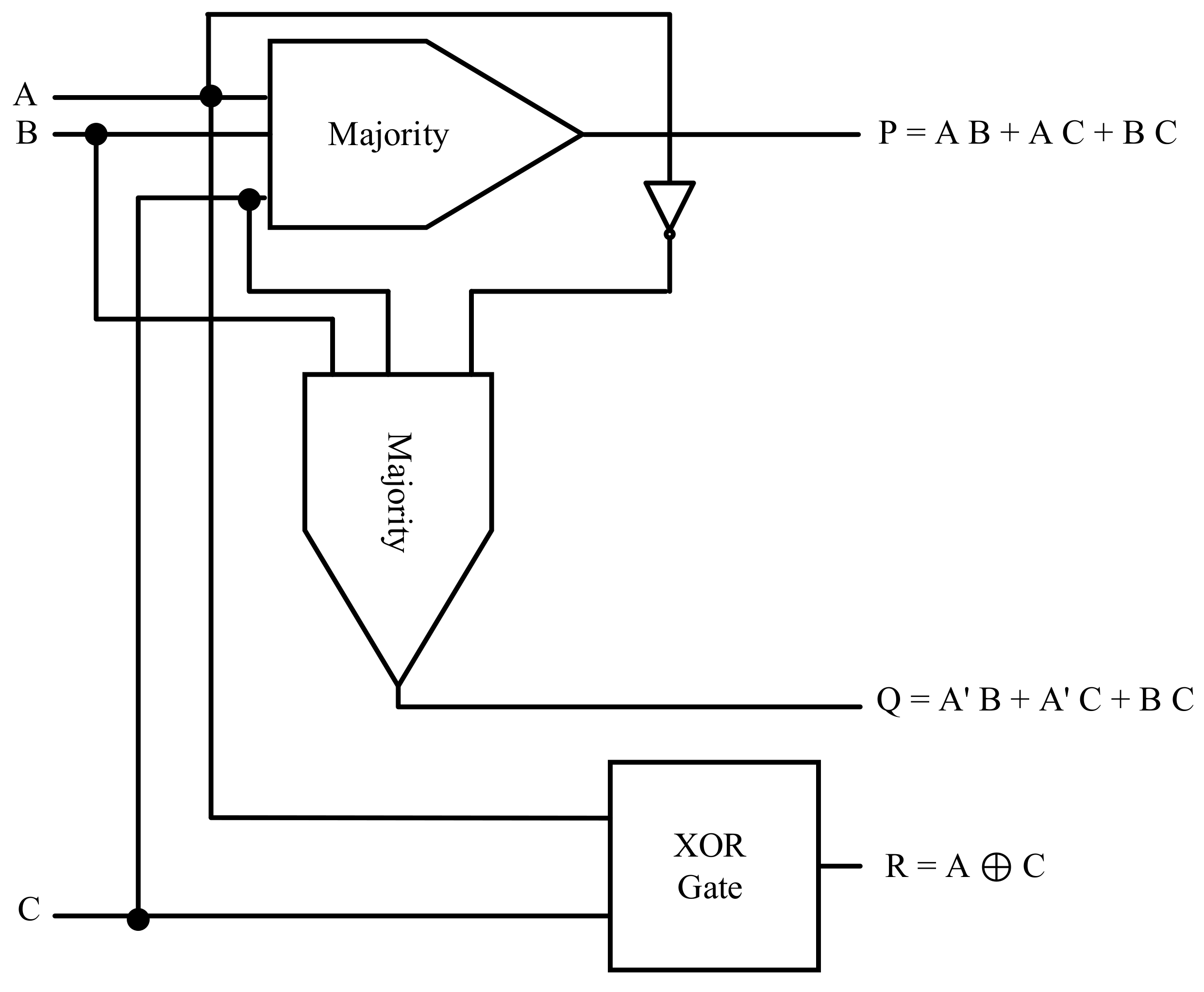

3.1. Implementation of the Proposed Reversible Gates

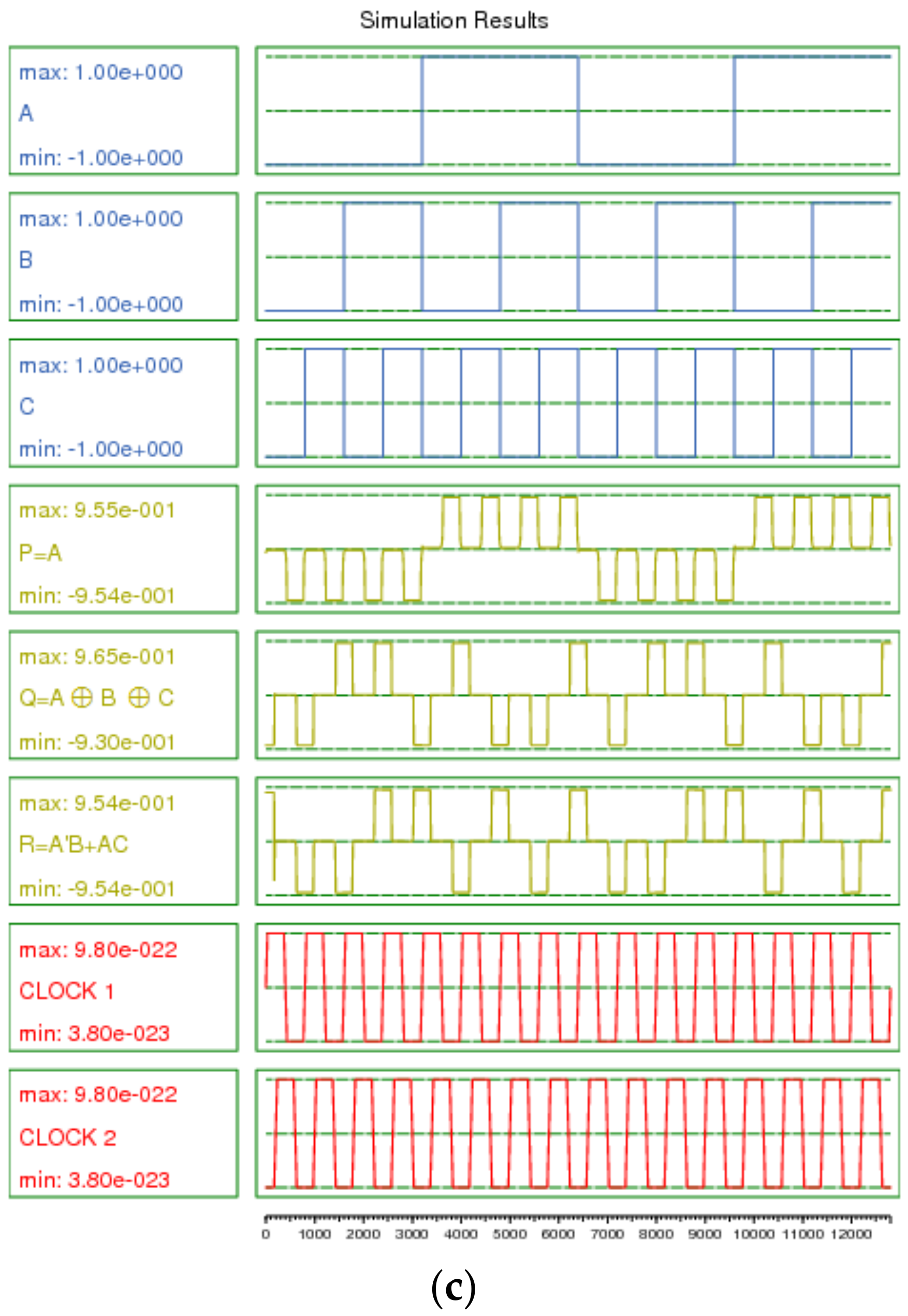

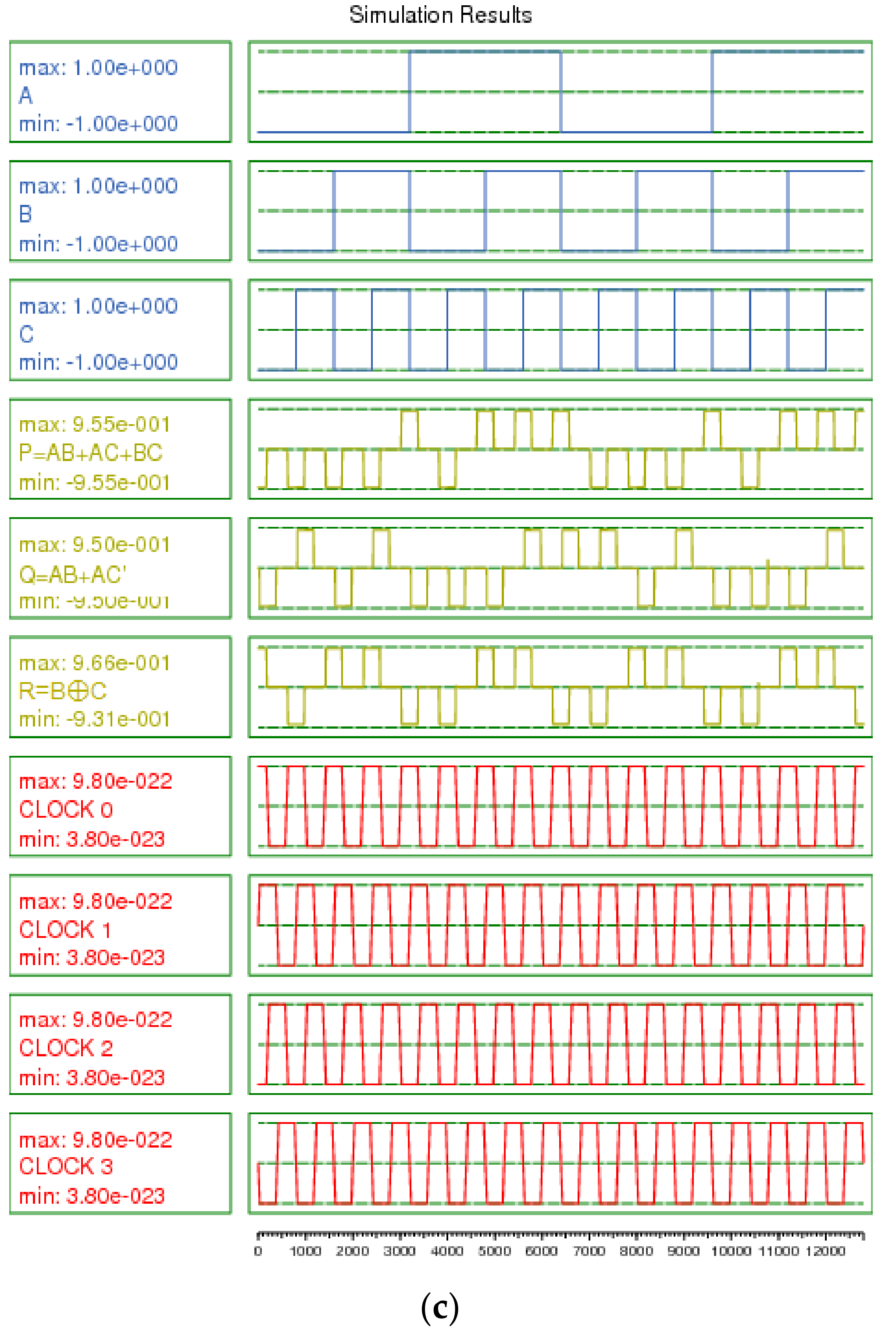

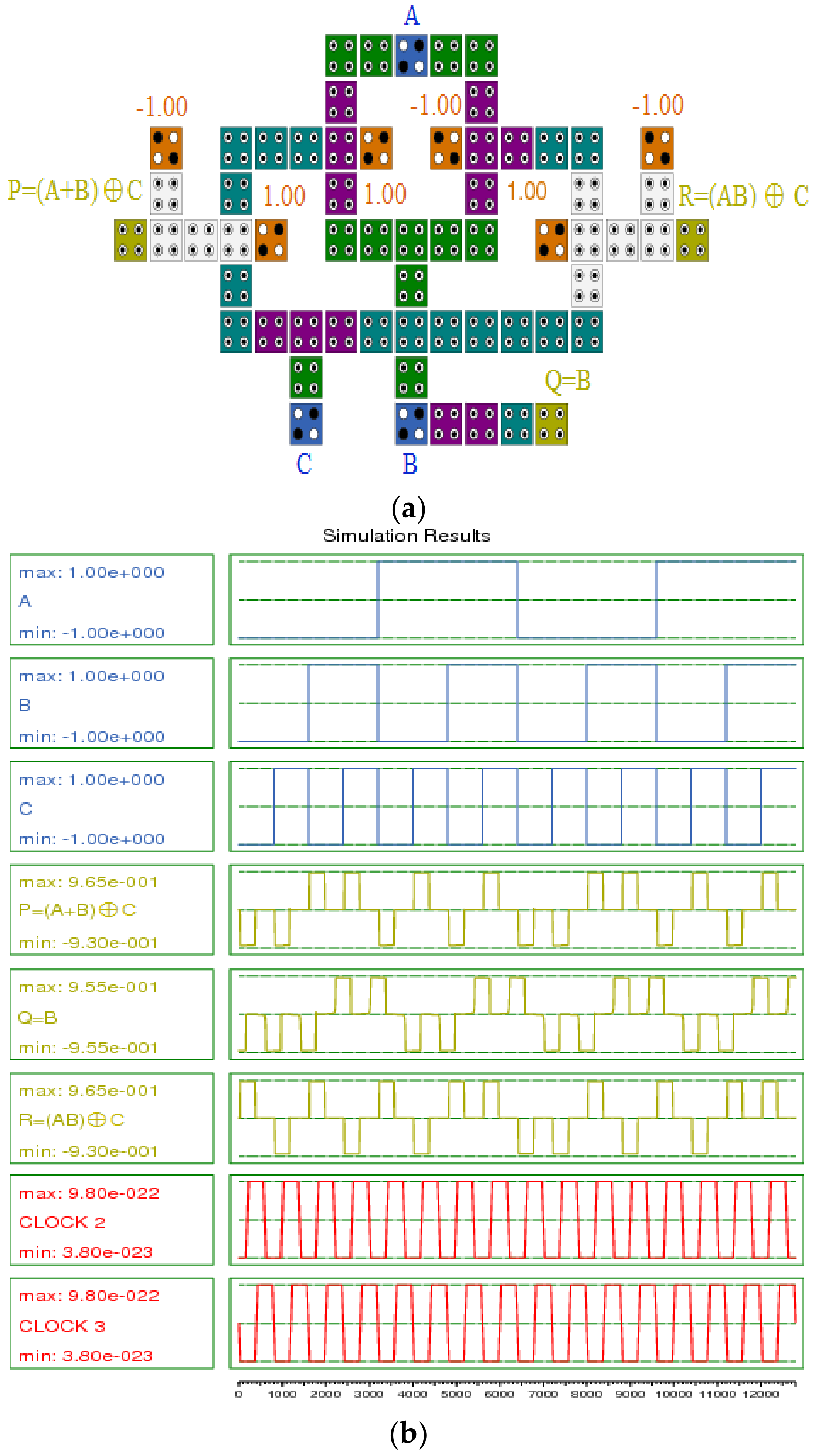

3.2. The Proposed QCA Implementation of Reversible Full Adder\Full Subtractor Circuit

4. Performance Evaluation

5. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Conte, T.M.; DeBenedictis, E.P.; Gargini, P.A.; Track, E. Rebooting Computing: The Road Ahead. Computer 2017, 50, 20–29. [Google Scholar] [CrossRef]

- DeBenedictis, E.P. Computer Architecture's Changing Role in Rebooting Computing. Computer 2017, 50, 96–99. [Google Scholar] [CrossRef]

- Chang, C.-H.; Molahosseini, A.S.; Zarandi, A.A.E.; Tay, T.F. Residue Number Systems: A New Paradigm to Datapath Optimization for Low-Power and High-Performance Digital Signal Processing Applications. IEEE Circuits Syst. Mag. 2015, 15, 26–44. [Google Scholar] [CrossRef]

- Bennett, C.H. Logical reversibility of computation. IBM J. Res. Dev. 1973, 17, 525–532. [Google Scholar] [CrossRef]

- Chen, A.; Hutchby, J.; Zhirnov, V.; Bourianoff, G. Emerging Nanoelectronic Devices; Chen, A., Hutchby, J., Zhirnov, V., Bourianoff, G., Eds.; John Wiley & Sons Ltd.: Chichester, UK, 2014; ISBN 9781118958254. [Google Scholar]

- DeBenedictis, E.P.; Mee, J.K.; Frank, M.P. The Opportunities and Controversies of Reversible Computing. Computer 2017, 50, 76–80. [Google Scholar] [CrossRef]

- Taha, S.M.R. Reversible Logic Synthesis Methodologies with Application to Quantum Computing; Springer: Berlin, Germany, 2016. [Google Scholar]

- Thapliyal, H.; Ranganathan, N. Reversible Logic-Based Concurrently Testable Latches for Molecular QCA. IEEE Trans. Nanotechnol. 2009, 9, 62–69. [Google Scholar] [CrossRef]

- Roohi, A.; DeMara, R.F.; Khoshavi, N. Design and evaluation of an ultra-area-efficient fault-tolerant QCA full adder. Microelectron. J. 2015, 46, 531–542. [Google Scholar] [CrossRef]

- Liu, W.; O’Neill, M.; Swartzlander, E. Design of Semiconductor QCA Systems; ArTech House Publication: London, UK, 2013. [Google Scholar]

- Macucci, M. Quantum Cellular Automata; Imperial College Press: London, UK, 2006. [Google Scholar]

- Walus, K.; Dysart, T.; Jullien, G.; Budiman, R. QCA Designer: A Rapid Design and Simulation Tool for Quantum-Dot Cellular Automata. IEEE Trans. Nanotechnol. 2004, 3, 26–31. [Google Scholar] [CrossRef]

- Teodosio, T.; Sousa, L. QCA-LG: A tool for the automatic layout generation of QCA combinational circuits. In Proceedings of the IEEE Norchip, Aalborg, Denmark, 19–20 November 2007; pp. 1–5. [Google Scholar] [CrossRef]

- Swartzlander, E.E.; Cho, H.; Kong, I.; Kim, S.-W. Computer arithmetic implemented with QCA: A progress report. In Proceedings of the Forty Fourth Asilomar Conference on Signals, Systems and Computers, Pacific Grove, CA, USA, 7–10 November 2010; pp. 1392–1398. [Google Scholar] [CrossRef]

- Das, J.C.; De, D.; Mondal, S.P.; Ahmadian, A.; Ghaemi, F.; Senu, N. QCA Based Error Detection Circuit for Nano Communication Network. IEEE Access 2019, 7, 67355–67366. [Google Scholar] [CrossRef]

- Shin, S.-H.; Jeon, J.-C.; Yoo, K.-Y. Design of Wire-Crossing Technique Based on Difference of Cell State in Quantum-Dot Cellular Automata. Int. J. Control. Autom. 2014, 7, 153–164. [Google Scholar] [CrossRef]

- Scott, A.; Lewis, T.G. Sustainable computing. Ubiquity 2021, 1–10. [Google Scholar] [CrossRef]

- Landauer, R. Irreversibility and Heat Generation in the Computing Process. IBM J. Res. Dev. 1961, 5, 183–191. [Google Scholar] [CrossRef]

- Denning, P.; Lewis, T. Computers That Can Run Backwards. Am. Sci. 2017, 105, 270. [Google Scholar] [CrossRef]

- Fredkin, E.; Toffoli, T. Conservative logic. Int. J. Theor. Phys. 1982, 21, 219–253. [Google Scholar] [CrossRef]

- Vahabi, M.; Lyakhov, P.; Bahar, A.N.; Wahid, K.A. Design and Implementation of New Coplanar FA Circuits without NOT Gate and Based on Quantum-Dot Cellular Automata Technology. Appl. Sci. 2021, 11, 12157. [Google Scholar] [CrossRef]

- Kianpour, M.; Sabbaghi-Nadooshan, R. Optimized Design of Multiplexor by Quantum-dot Cellular Automata. Int. J. Nanosci. Nanotechnol. 2013, 9, 15–24. [Google Scholar]

- Vahabi, M.; Bahar, A.N.; Otsuki, A.; Wahid, K.A. Ultra-Low-Cost Design of Ripple Carry Adder to Design Nanoelectronics in QCA Nanotechnology. Electronics 2022, 11, 2320. [Google Scholar] [CrossRef]

- Vahabi, M.; Lyakhov, P.; Bahar, A.N. Design and Implementation of Novel Efficient Full Adder/Subtractor Circuits Based on Quantum-Dot Cellular Automata Technology. Appl. Sci. 2021, 11, 8717. [Google Scholar] [CrossRef]

- Chabi, A.M.; Roohi, A.; Khademolhosseini, H.; Sheikhfaal, S.; Angizi, S.; Navi, K.; DeMara, R.F. Towards ultra-efficient QCA reversible circuits. Microprocess. Microsyst. 2017, 49, 127–138. [Google Scholar] [CrossRef]

- Feynman, R. Quantum Mechanical Computers. Opt. News 1985, 11, 11–20. [Google Scholar] [CrossRef]

- Toffoli, T. Reversible computing. In International Colloquium on Automata, Languages, and Programming; Springer: Berlin/Heidelberg, Germany, 1980; pp. 632–644. [Google Scholar]

- Peres, A. Reversible logic and quantum computers. Phys. Rev. A 1985, 32, 3266–3276. [Google Scholar] [CrossRef] [PubMed]

- Saravanan, S.; Vennila, I.; Mohanram, S. Design and Implementation of an Efficient Reversible Comparator Using TR Gate. Circuits Syst. 2016, 07, 2578–2592. [Google Scholar] [CrossRef]

- Sen, B.; Adak, T.; Anand, A.S.; Sikdar, B.K. Synthesis of reversible universal QCA gate structure for energy efficient digital design. In Proceedings of the IEEE Region 10 Conference TENCON, Bali, Indonesia, 21–24 November 2011; pp. 806–810. [Google Scholar] [CrossRef]

- Sen, B.; Dutta, M.; Some, S.; Sikdar, B.K. Realizing Reversible Computing in QCA Framework Resulting in Efficient Design of Testable ALU. ACM J. Emerg. Technol. Comput. Syst. 2014, 11, 1–22. [Google Scholar] [CrossRef]

- Islam, M.S.; Abdullah-Al-Shafi, M.; Bahar, A.N. A new approach of presenting universal reversible gate in nanoscale. Int. J. Comput. Appl. 2016, 134, 1–4. [Google Scholar]

- Taherkhani, E.; Moaiyeri, M.H.; Angizi, S. Design of an ultra-efficient reversible full adder-subtractor in quantum-dot cellular automata. Optik 2017, 142, 557–563. [Google Scholar] [CrossRef]

- Chen, H.; Lv, H.; Zhang, Z.; Cheng, X.; Xie, G. Design and Analysis of a Novel Low-Power Exclusive-OR Gate Based on Quantum-Dot Cellular Automata. J. Circuits Syst. Comput. 2019, 28, 1950141. [Google Scholar] [CrossRef]

- Karkaj, E.T.; Heikalabad, S.R. Binary to gray and gray to binary converter in quantum-dot cellular automata. Optik 2017, 130, 981–989. [Google Scholar] [CrossRef]

- Vahabi, M.; Lyakhov, P.; Bahar, A.N.; Otsuki, A.; Wahid, K.A. Novel Reversible Comparator Design in Quantum Dot-Cellular Automata with Power Dissipation Analysis. Appl. Sci. 2022, 12, 7846. [Google Scholar] [CrossRef]

- Kumar, P.; Singh, S. Optimization of the area efficiency and robustness of a QCA-based reversible full adder. J. Comput. Electron. 2019, 18, 1478–1489. [Google Scholar] [CrossRef]

- Ahmed, S.; Naz, S.F.; Sharma, S. Quantum dot Cellular Automata based Fault Tolerant Fingerprint Authentication Systems using Reversible Logic Gates. GAZI Univ. J. Sci. 2021, 35, 586–604. [Google Scholar] [CrossRef]

- Das, J.C.; De, D. Computational fidelity in reversible quantum-dot cellular automata channel routing under thermal randomness. Nano Commun. Netw. 2018, 18, 17–26. [Google Scholar] [CrossRef]

- Bahar, A.N.; Ahmad, F.; Nahid, N.M.; Hassan, K.; Al Shafi, A.; Ahmed, K. An optimal design of conservative efficient reversible parity logic circuits using QCA. Int. J. Inf. Technol. 2018, 11, 785–794. [Google Scholar] [CrossRef]

- Das, J.C.; De, D. Feynman gate based design of n-bit reversible inverter and its implementation on quantum-dot cellular automata. Nano Commun. Netw. 2020, 24, 100298. [Google Scholar] [CrossRef]

- Seyedi, S.; Otsuki, A.; Navimipour, N. A New Cost-Efficient Design of a Reversible Gate Based on a Nano-Scale Quantum-Dot Cellular Automata Technology. Electronics 2021, 10, 1806. [Google Scholar] [CrossRef]

- Patidar, M.; Gupta, N. An ultra-efficient design and optimized energy dissipation of reversible computing circuits in QCA technology using zone partitioning method. Int. J. Inf. Technol. 2021, 14, 1483–1493. [Google Scholar] [CrossRef]

- Debnath, B.; Das, J.C.; De, D.; Ghaemi, F.; Ahmadian, A.; Senu, N. Reversible Palm Vein Authenticator Design with Quantum Dot Cellular Automata for Information Security in Nanocommunication Network. IEEE Access 2020, 8, 174821–174832. [Google Scholar] [CrossRef]

- Roy, A.; Singh, A.D.; Saha, A.; Saha, S.; Gupta, V.; Qingyi, Z.; Bhattacharya, S.; Bhattacharjee, S. A Novel Design of Reversible Gate using Quantum-Dot Cellular Automata (QCA). In Proceedings of the 2020 IEEE 1st International Conference for Convergence in Engineering (ICCE), Kolkata, India, 5–6 September 2020; pp. 110–115. [Google Scholar]

- Mukherjee, C.; Panda, S.; Mukhopadhyay, A.K.; Maji, B. Utilization of LTEx Feynman Gate in Designing the QCA Based Reversible Binary to Gray and Gray to Binary Code Converters. Micro Nanosyst. 2020, 12, 187–200. [Google Scholar] [CrossRef]

- Sasamal, T.N.; Singh, A.K.; Ghanekar, U. Toward Efficient Design of Reversible Logic Gates in Quantum-Dot Cellular Automata with Power Dissipation Analysis. Int. J. Theor. Phys. 2017, 57, 1167–1185. [Google Scholar] [CrossRef]

- Iqbal, J.; Banday, M.T. Applications of Toffoli Gate for designing the classical gates using quantum-dot cellular automata. Int. J. Recent Sci. Res. 2015, 6, 7764–7769. [Google Scholar]

- Kianpour, M.; Sabbaghi-Nadooshan, R. Novel 8-bit reversible full adder/subtractor using a QCA reversible gate. J. Comput. Electron. 2017, 16, 459–472. [Google Scholar] [CrossRef]

- Bhoi, B.K.; Misra, N.K.; Pradhan, M. Analysis on Fault Mapping of Reversible Gates with Extended Hardware Description Language for Quantum Dot Cellular Automata Approach. Sens. Lett. 2019, 17, 371–378. [Google Scholar] [CrossRef]

- Safoev, N.; Abdukhalil, G.; Abdisalomovich, K.A. QCA based Priority Encoder using Toffoli gate. In Proceedings of the 2020 IEEE 14th International Conference on Application of Information and Communication Technologies (AICT), Tashkent, Uzbekistan, 7–9 October 2020; pp. 1–4. [Google Scholar]

- Reshi, J.I.; Banday, M.T. Realization of Peres gate as universal structure using quantum Dot cellular automata. J. Nanosci. Technol. 2016, 2, 115–118. [Google Scholar]

- Das, J.C.; De, D. Novel low power reversible binary incrementer design using quantum-dot cellular automata. Microprocess. Microsyst. 2016, 42, 10–23. [Google Scholar] [CrossRef]

- Das, J.C.; De, D. Reversible Comparator Design Using Quantum Dot-Cellular Automata. IETE J. Res. 2015, 62, 323–330. [Google Scholar] [CrossRef]

- Bahar, A.N.; Waheed, S.; Hossain, N.; Bahar, A.N. A new approach of presenting reversible logic gate in nanoscale. Springerplus 2015, 4, 1–7. [Google Scholar] [CrossRef] [PubMed]

- Sarma, R.; Jain, R. Quantum Gate Implementation of a Novel Reversible Half Adder and Subtractor Circuit. In Proceedings of the 2018 International Conference on Intelligent Circuits and Systems (ICICS), Phagwara, India, 20–21 April 2018; pp. 72–76. [Google Scholar] [CrossRef]

- Das, J.C.; De, D. Optimized Design of Reversible Gates in Quantum Dot-Cellular Automata: A Review. Rev. Theor. Sci. 2016, 4, 279–286. [Google Scholar] [CrossRef]

- Sasamal, T.N.; Mohan, A.; Singh, A.K. Efficient Design of Reversible Logic ALU Using Coplanar Quantum-Dot Cellular Automata. J. Circuits Syst. Comput. 2017, 27, 1850021. [Google Scholar] [CrossRef]

- Al-Shafi, A.; Aneek, R.H.; Bahar, A.N. Universal Reversible Gate in Quantum-Dot Cellular Automata (QCA): A Multilayer Design Paradigm. Int. J. Grid Distrib. Comput. 2017, 10, 43–50. [Google Scholar] [CrossRef]

- Ahmad, F.; Ahmed, S.; Kakkar, V.; Bhat, G.M.; Bahar, A.N.; Wani, S. Modular Design of Ultra-Efficient Reversible Full Adder-Subtractor in QCA with Power Dissipation Analysis. Int. J. Theor. Phys. 2018, 57, 2863–2880. [Google Scholar] [CrossRef]

- Hashemi, S.; Azghadi, M.R.; Navi, K. Design and analysis of efficient QCA reversible adders. J. Supercomput. 2018, 75, 2106–2125. [Google Scholar] [CrossRef]

| A | B | Cin | S\D | Cout | Bout |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 | 1 | 1 |

| 1 | 0 | 0 | 1 | 0 | 0 |

| 1 | 0 | 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 1 | 1 |

| Parameter | Value |

|---|---|

| Cell width | 18 nm |

| Cell height | 18 nm |

| Dot diameter | 5 nm |

| Number of samples | 12800 |

| Convergence tolerance | 0.001 |

| Radius of effect | 65 nm |

| Relative permittivity | 12.9 |

| Clock high | 9.8 × 10−22 J |

| Clock low | 3.8 × 10−23 J |

| Clock amplitude factor | 2 |

| Layer separation | 11.5 nm |

| Maximum iteration per sample | 100 |

| Circuit | Area (µm2) | Cell Count | Latency (clock) | Inverter | Crossover Type | |

|---|---|---|---|---|---|---|

| Feynman | Proposed [33] [35] [36] [37] [38] [39] [40] [41] [42] [43] [44] [45] [46] [47] | 0.008 0.050 0.020 0.010 0.064 0.0350.066 0.017 0.019 0.019 0.012 0.112 0.034 0.025 0.016 | 10 26 22 11 58 15 56 16 27 25 13 90 32 34 23 | 0.25 0.5 0.75 0.0.25 1.5 0.25 0.75 0.5 0.75 0.5 0.5 1.75 0.75 0.75 0.5 | 0 1 1 0 1 1 2 0 2 2 0 3 2 0 1 | Not required Not required Not required Not required Not required Not required Not required Not required Not required Not required Not required Coplanar Not required Not required Not required |

| Toffoli | Proposed-a Proposed-b [48] [49] [37] [38] [50] [39] [45] [51] [47] | 0.022 0.025 0.043 0.100 0.088 0.025 0.07 0.143 0.051 0.058 0.034 | 24 25 45 100 64 27 39 114 40 50 34 | 0.5 0.5 1 1.25 1.5 0.5 0.75 1.25 0.75 1 0.75 | 0 0 2 6 1 1 1 2 2 0 1 | Not required Not required Not required Coplanar Not required Not required Coplanar (rotated cells) Coplanar (clocking) Not required Coplanar Not required |

| Peres | Proposed-a Proposed-b [52] [53] [39] [45] [47] | 0.046 0.049 0.071 0.075 0.175 0.083 0.066 | 51 51 87 97 136 79 56 | 0.75 0.75 1 1 2.5 1.25 0.75 | 0 0 4 4 4 4 2 | Coplanar Coplanar Not required Multi-Layer Coplanar Not required Not required |

| PQR | Proposed-a Proposed-b [25] | 0.039 0.043 0.090 | 40 40 90 | 0.75 0.751 | 0 0 4 | Not required Not required Coplanar |

| TR | Proposed-a Proposed-b [54] [55] [56] | 0.041 0.050 0.090 0.079 0.54 | 42 47 122 69 225 | 0.75 0.75 1 1 1.5 | 1 1 5 4 8 | Not required Not required Multi-Layer Not required Coplanar (rotated cells) |

| RUG | Proposed-a Proposed-b [57] [58] | 0.077 0.101 0.104 0.22 | 68 85 106 187 | 0.75 1 1 1.25 | 2 2 4 4 | Coplanar Coplanar Not required Coplanar |

| URG | Proposed-a Proposed-b [32] [59] | 0.060 0.061 0.173 0.078 | 62 55 134 114 | 1 1 1 1 | 0 0 4 4 | Coplanar Coplanar Not required Multi-Layer |

| RQCA | Proposed-a Proposed-b [31] | 0.047 0.042 0.210 | 41 40 194 | 0.75 0.75 1.25 | 1 1 2 | Not required Not required Coplanar |

| RQG | Proposed-a Proposed-b [33] | 0.087 0.087 0.210 | 90 35 128 | 1 1 1.25 | 1 1 2 | Coplanar Coplanar Coplanar |

| Circuit | Area (µm2) | Cell Count | Latency (clock) | Inverter | Crossover Type |

|---|---|---|---|---|---|

| Full adder [37] | 0.23 | 178 | 3.25 | 3 | Coplanar (clocking) |

| Full adder [60] | 0.14 | 121 | 1.25 | 2 | Coplanar (clocking) |

| Full adder [61] | 0.32 | 236 | 3.25 | 6 | Coplanar (clocking) |

| FA\FS [49] | 0.50 | 399 | 2 | 23 | Coplanar (rotated cells) |

| FA\FS [33] | 0.28 | 228 | 1.75 | 4 | Coplanar (clocking) |

| Proposed-a FA\FS | 0.120 | 123 | 1.25 | 1 | Coplanar (clocking) |

| Proposed-b FA\FS | 0.121 | 121 | 1.25 | 1 | Coplanar (clocking) |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Vahabi, M.; Rahimi, E.; Lyakhov, P.; Bahar, A.N.; Wahid, K.A.; Otsuki, A. Novel Quantum-Dot Cellular Automata-Based Gate Designs for Efficient Reversible Computing. Sustainability 2023, 15, 2265. https://doi.org/10.3390/su15032265

Vahabi M, Rahimi E, Lyakhov P, Bahar AN, Wahid KA, Otsuki A. Novel Quantum-Dot Cellular Automata-Based Gate Designs for Efficient Reversible Computing. Sustainability. 2023; 15(3):2265. https://doi.org/10.3390/su15032265

Chicago/Turabian StyleVahabi, Mohsen, Ehsan Rahimi, Pavel Lyakhov, Ali Newaz Bahar, Khan A. Wahid, and Akira Otsuki. 2023. "Novel Quantum-Dot Cellular Automata-Based Gate Designs for Efficient Reversible Computing" Sustainability 15, no. 3: 2265. https://doi.org/10.3390/su15032265

APA StyleVahabi, M., Rahimi, E., Lyakhov, P., Bahar, A. N., Wahid, K. A., & Otsuki, A. (2023). Novel Quantum-Dot Cellular Automata-Based Gate Designs for Efficient Reversible Computing. Sustainability, 15(3), 2265. https://doi.org/10.3390/su15032265