Comparison of Interleaved Boost Converter and Two-Phase Boost Converter Characteristics for Three-Level Inverters

Abstract

1. Introduction

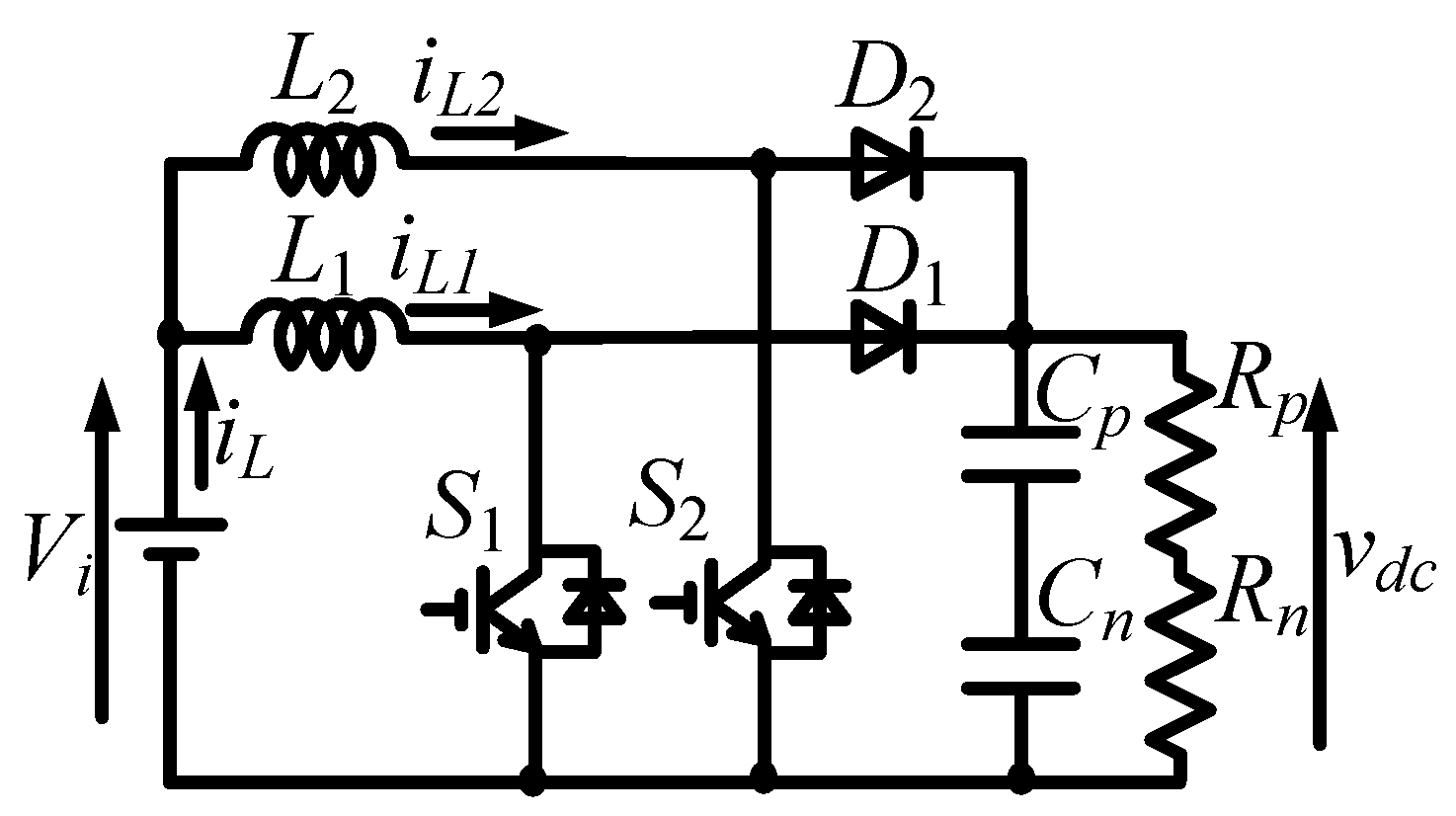

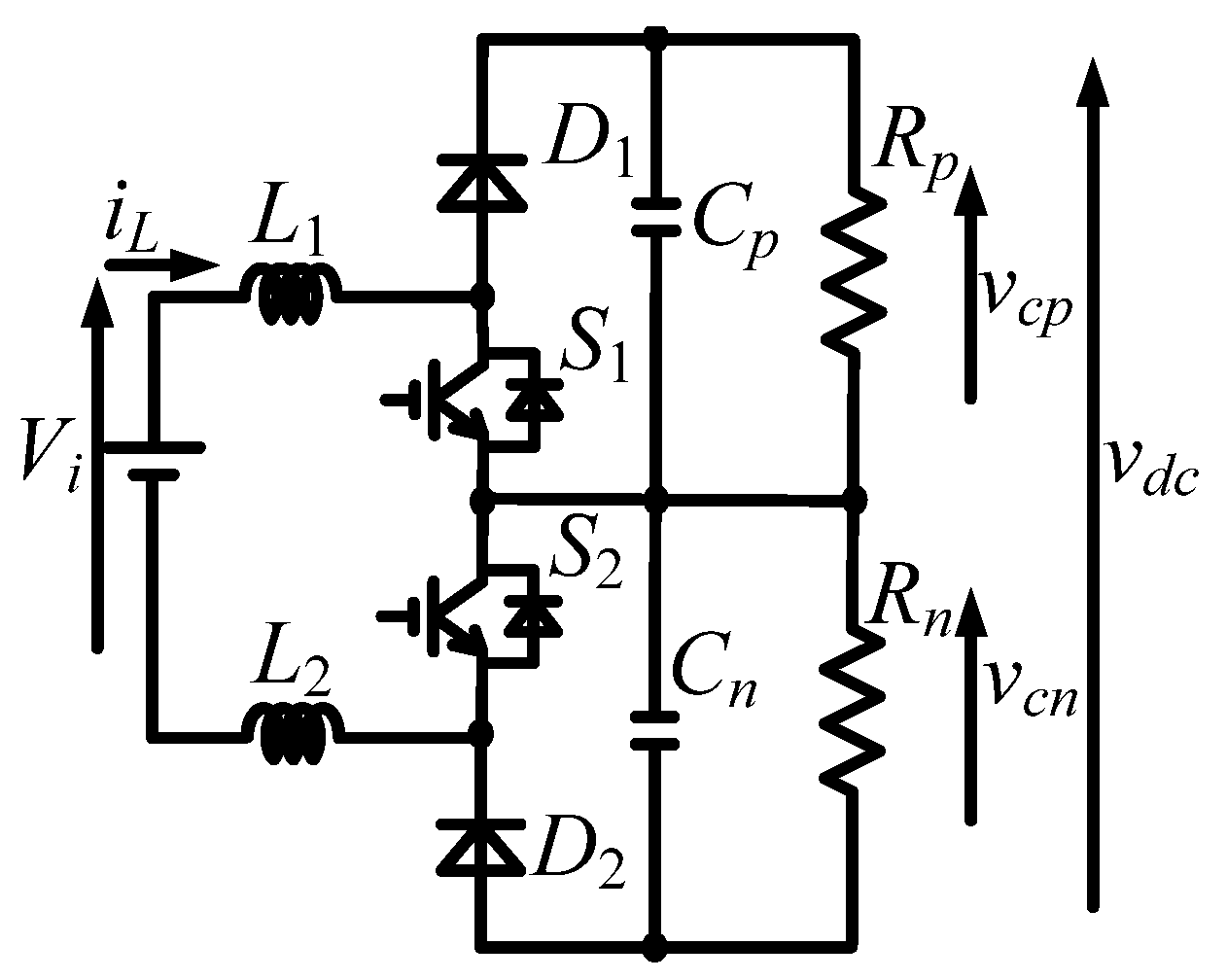

2. Circuit Configuration

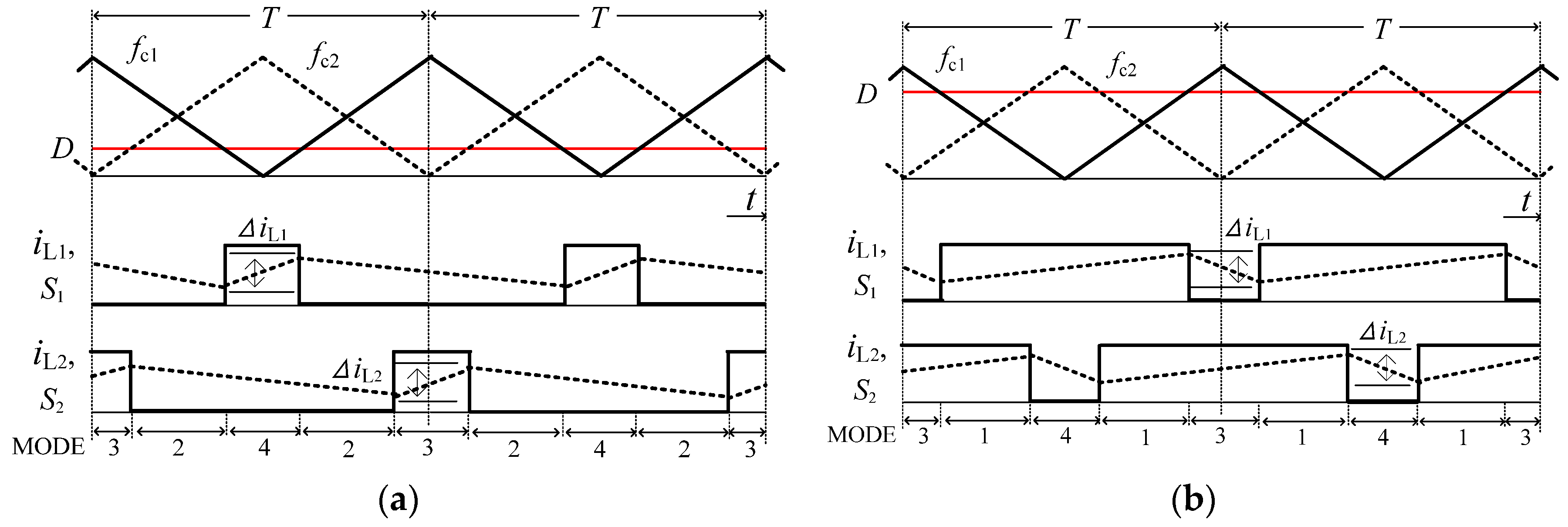

2.1. Interleaving Scheme

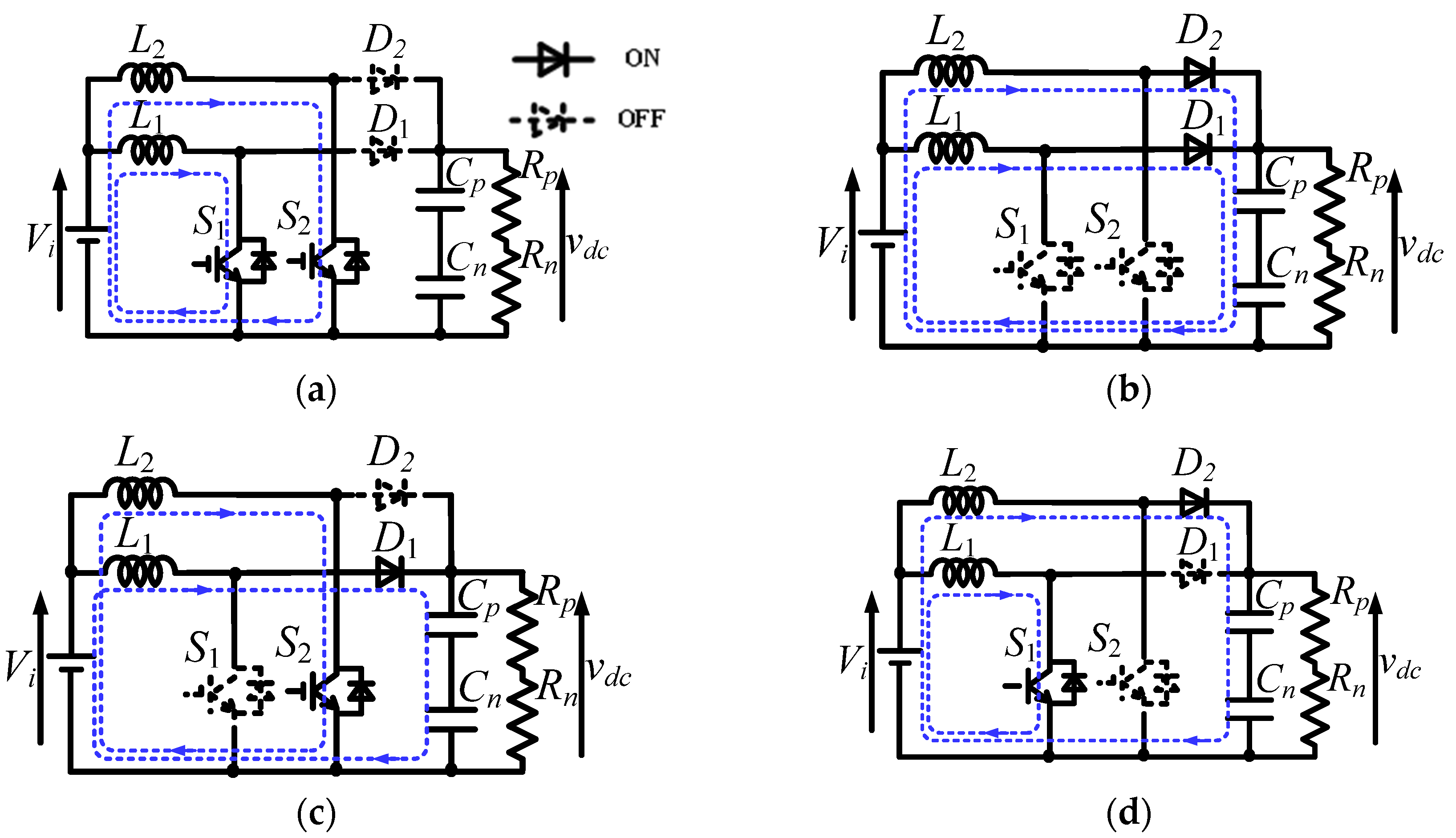

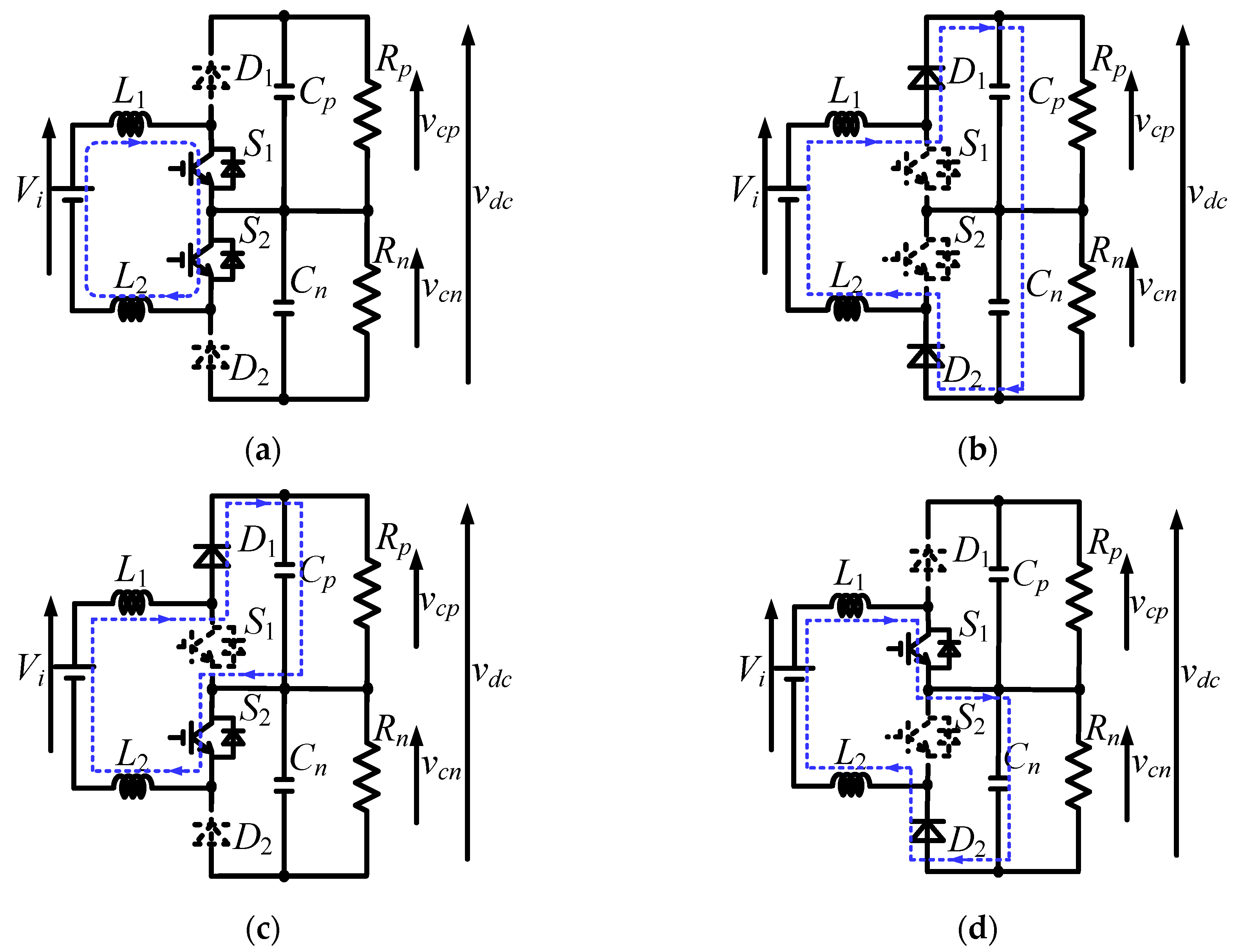

2.2. Switching Modes

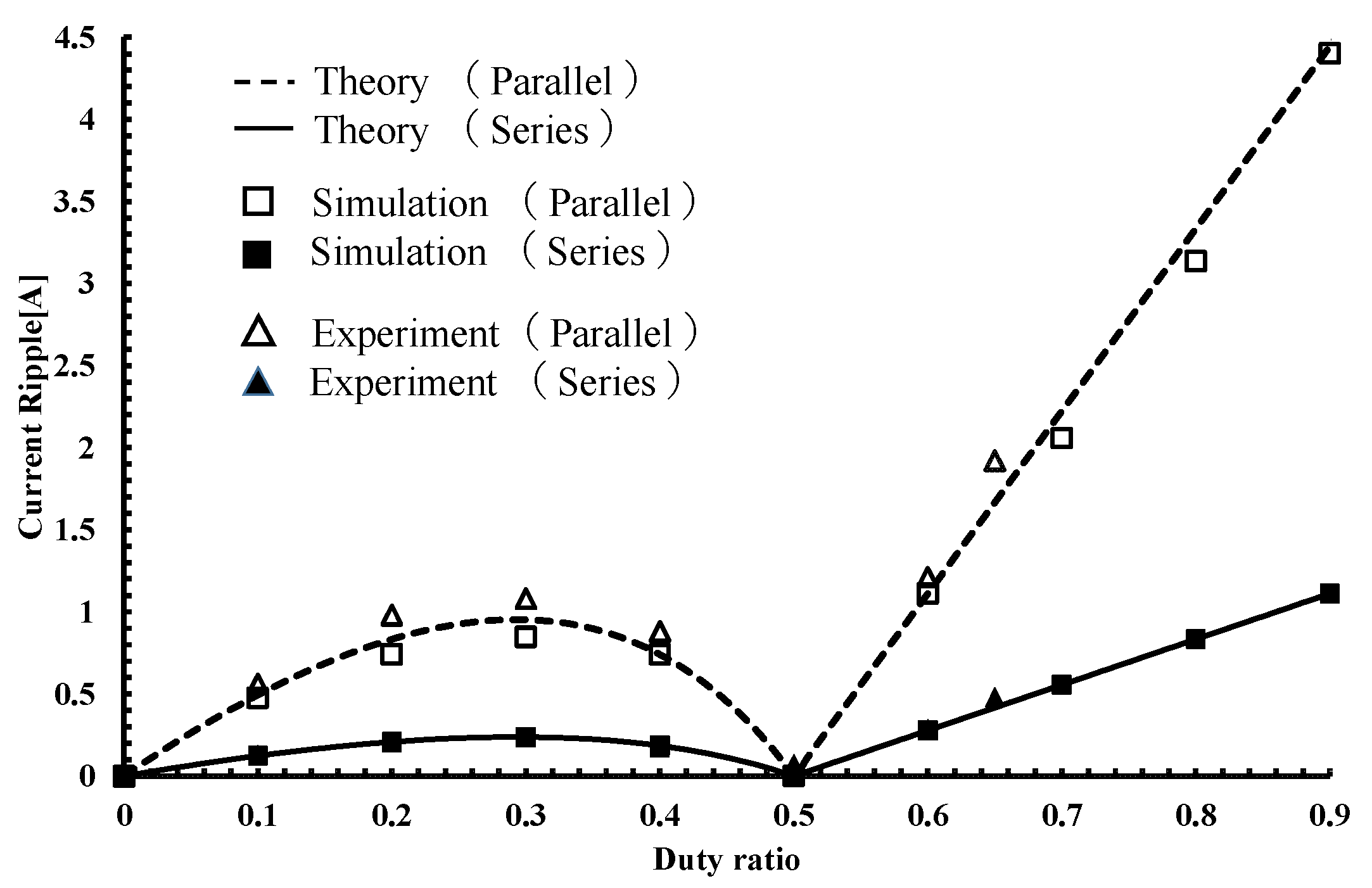

3. Input Current Ripple Analysis

3.1. Input Current Ripple in Parallel Circuits

3.2. Input Current Ripple in Series Circuits

4. Output Voltage Control

4.1. PI Control

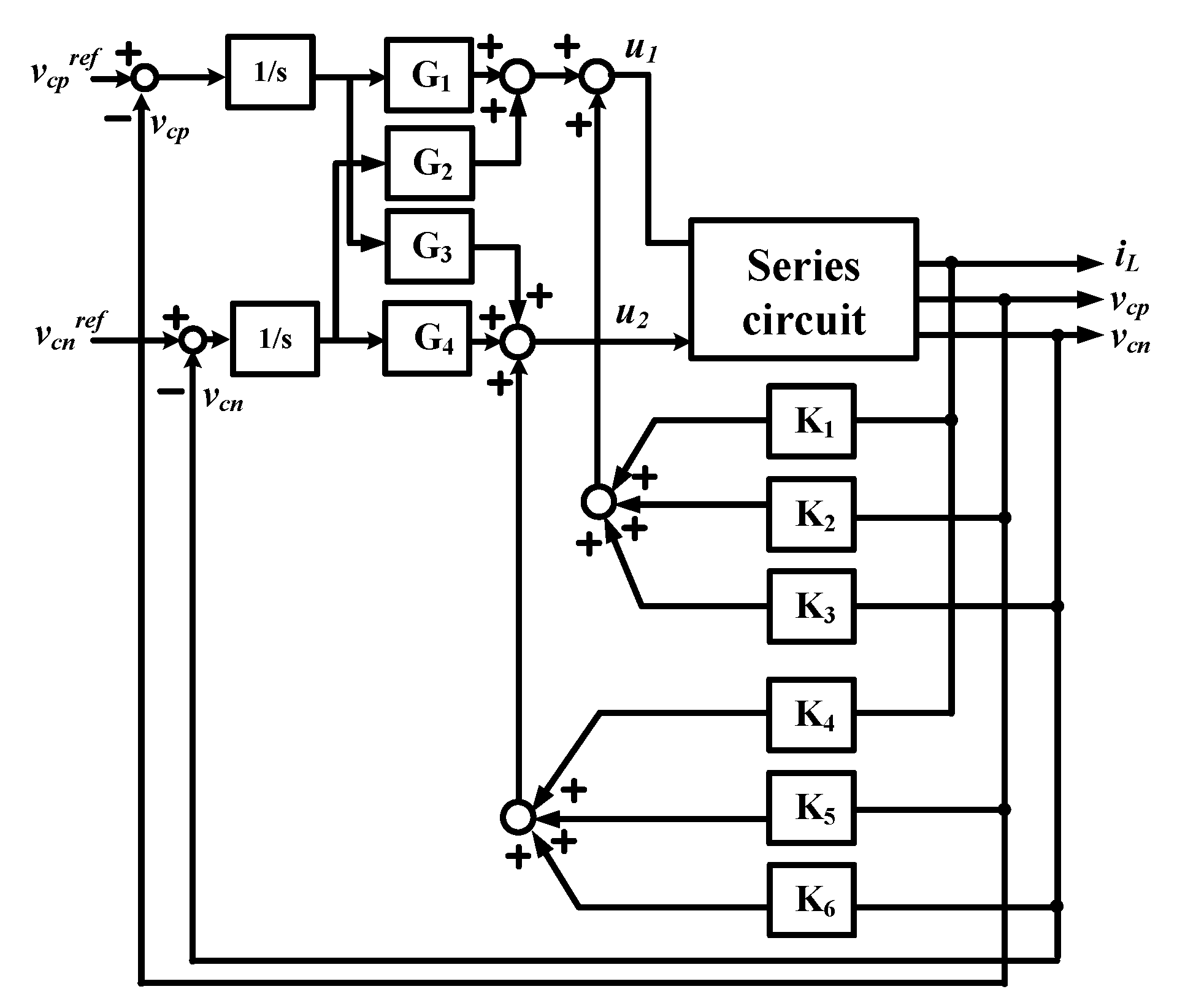

4.2. Output Voltage Control Using Optimal Regulator

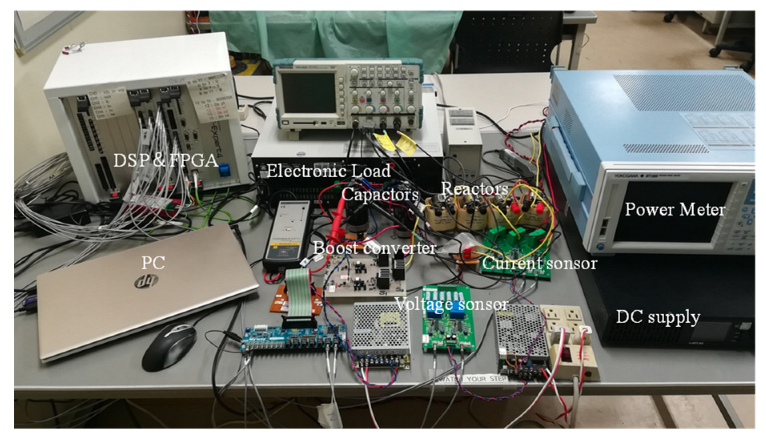

5. Experimental Verification

5.1. PI Control Design

5.2. Optimal Regulator Design

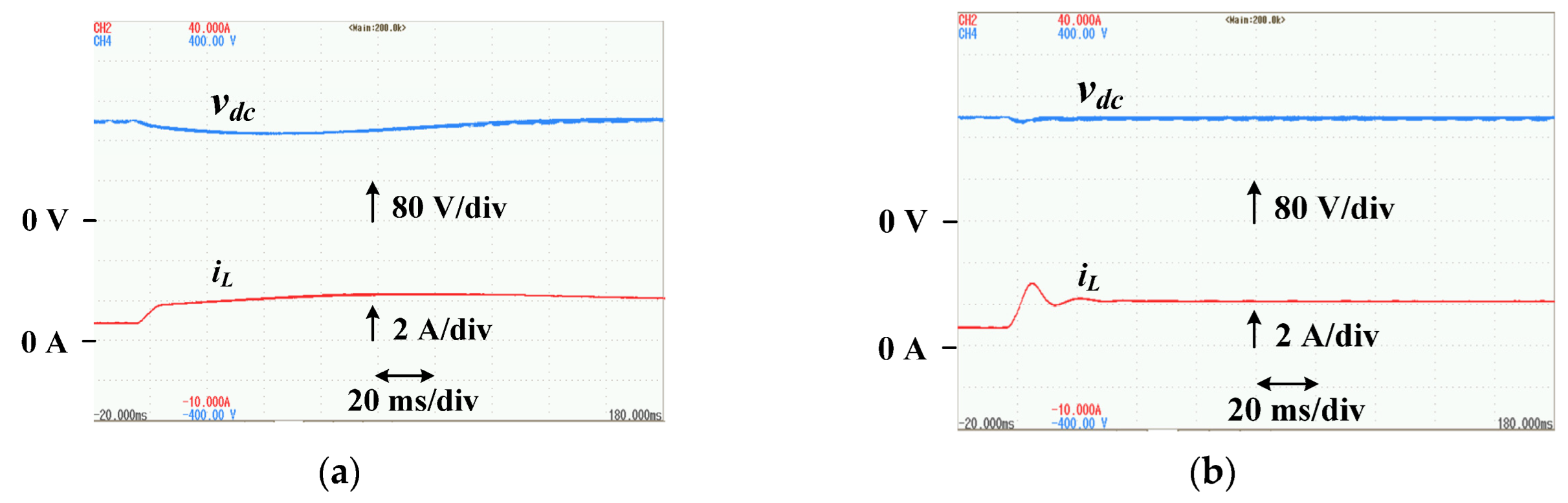

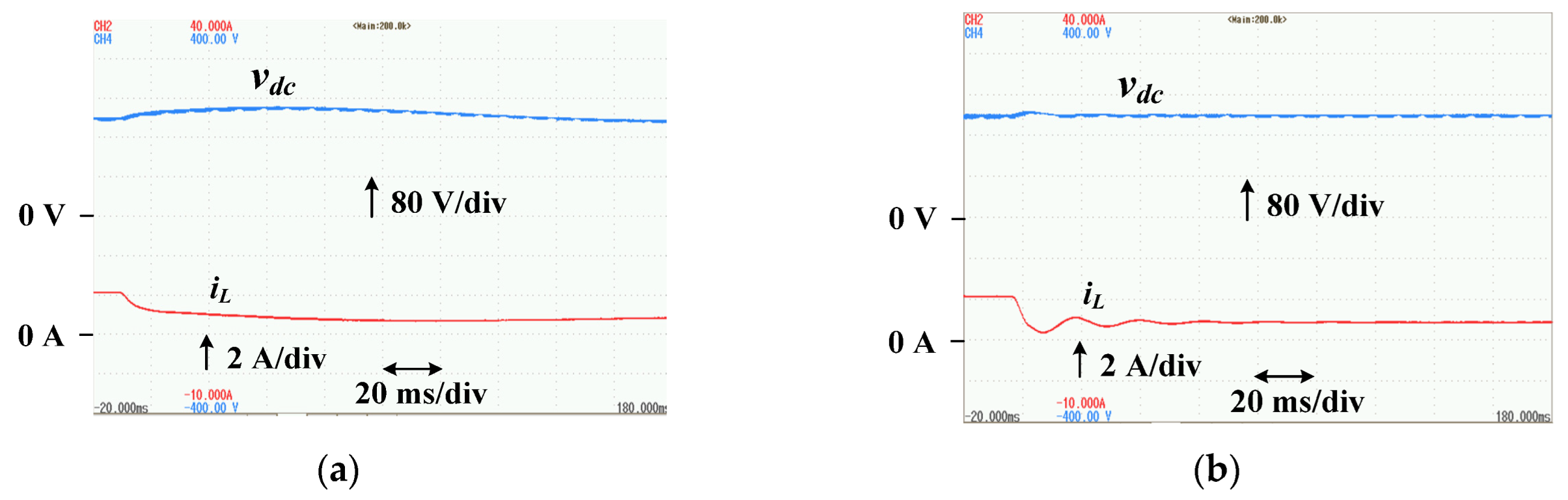

5.3. Boost Operation and Neutral Point Potential Control Characteristics

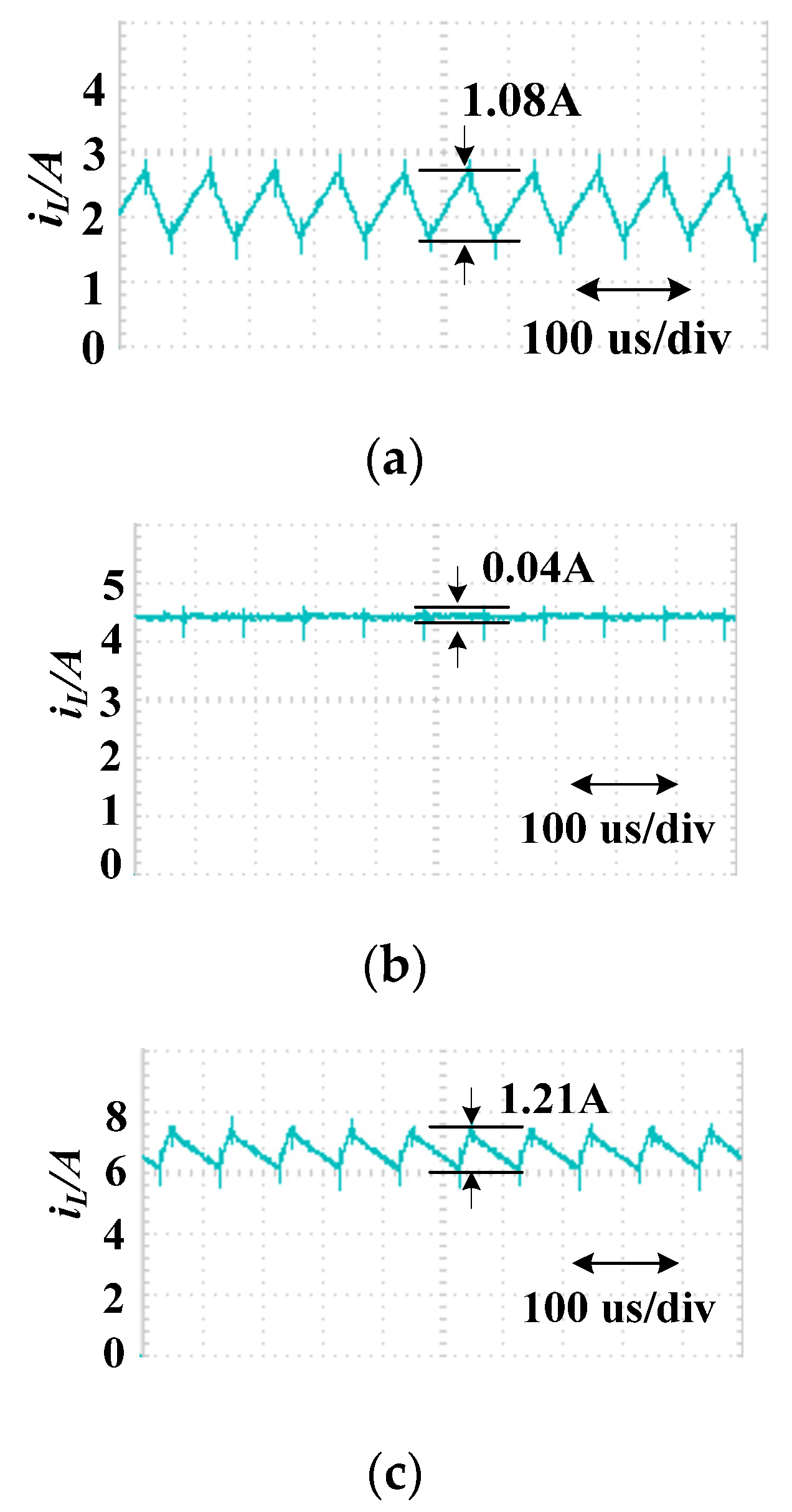

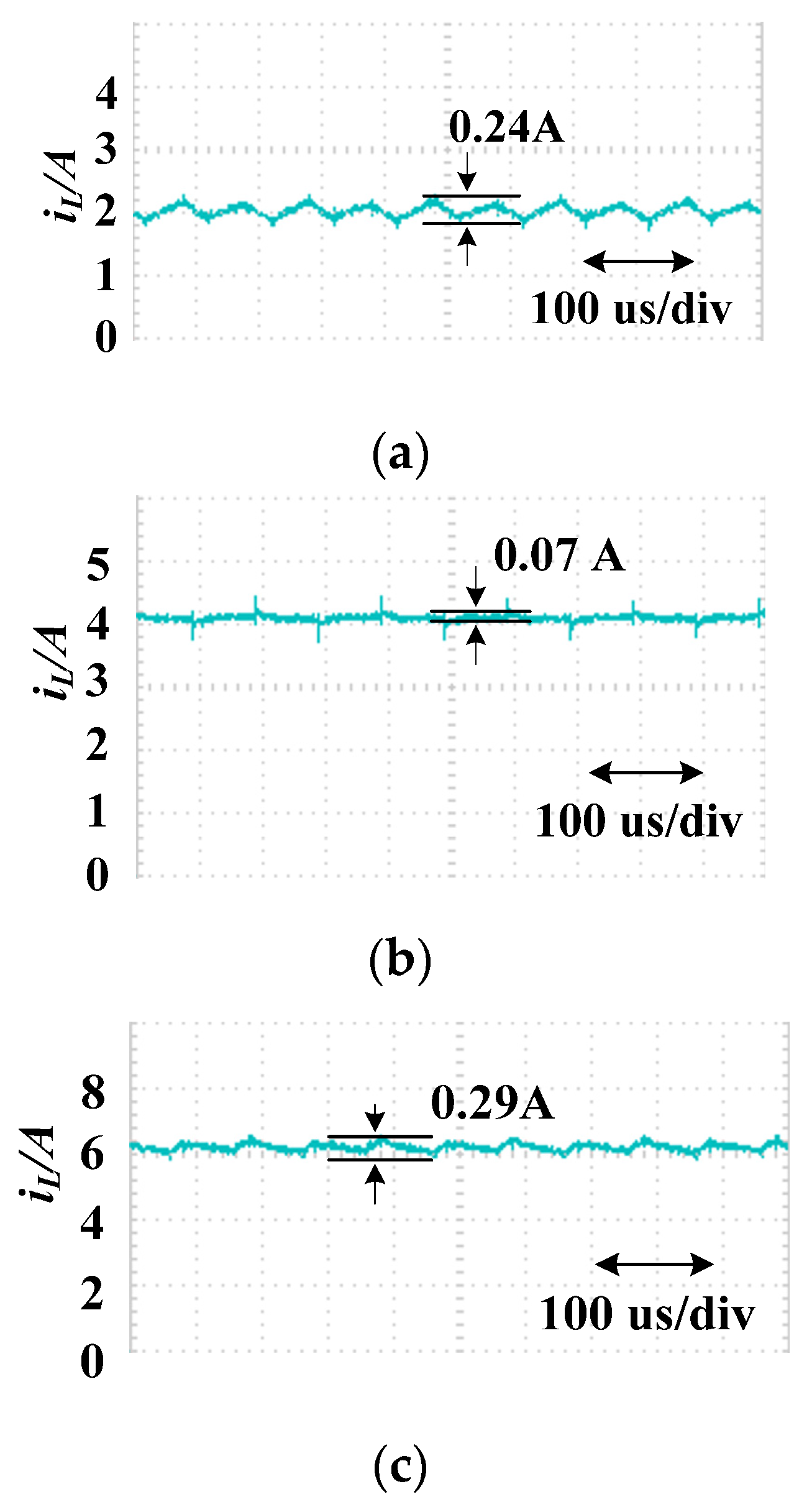

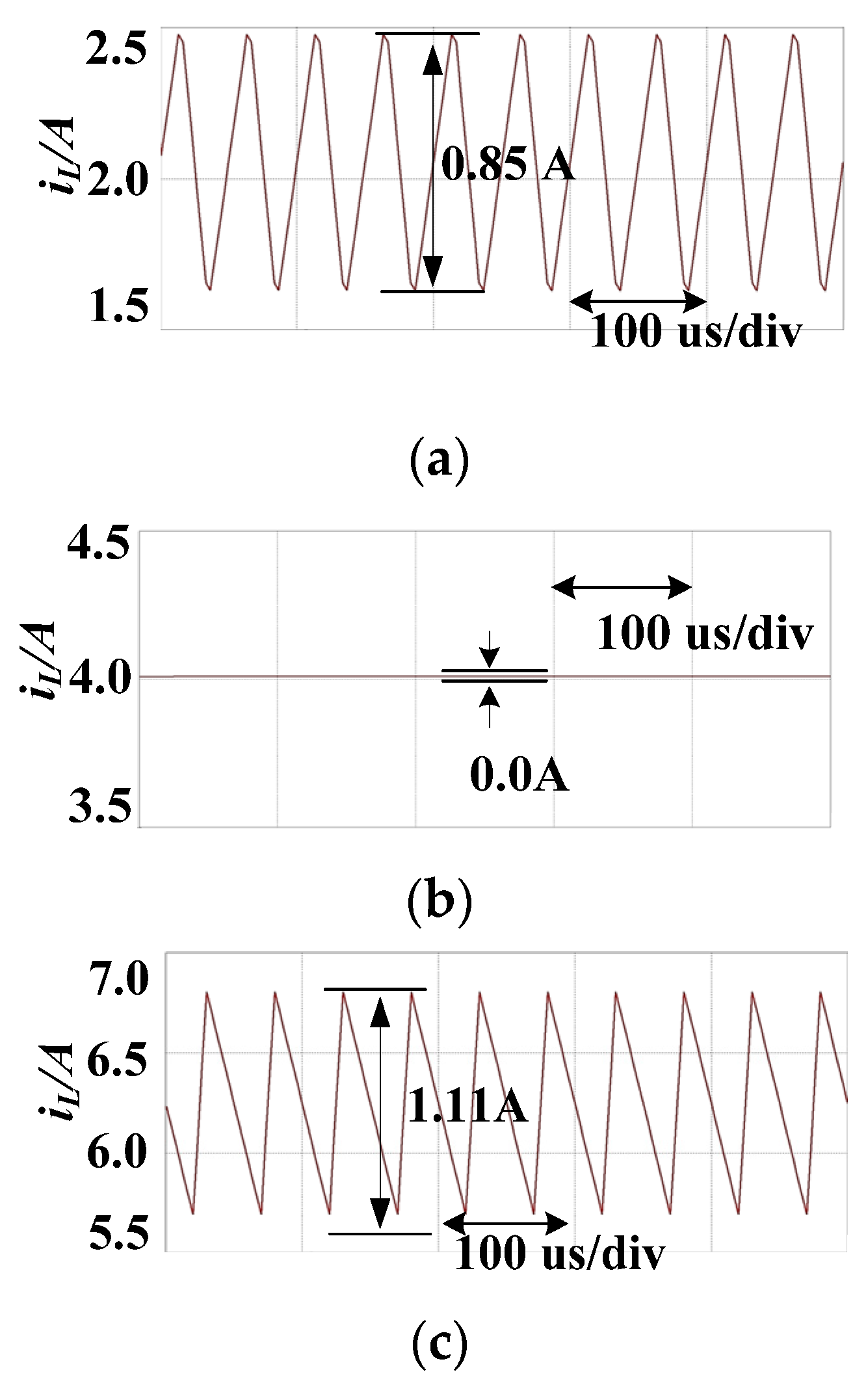

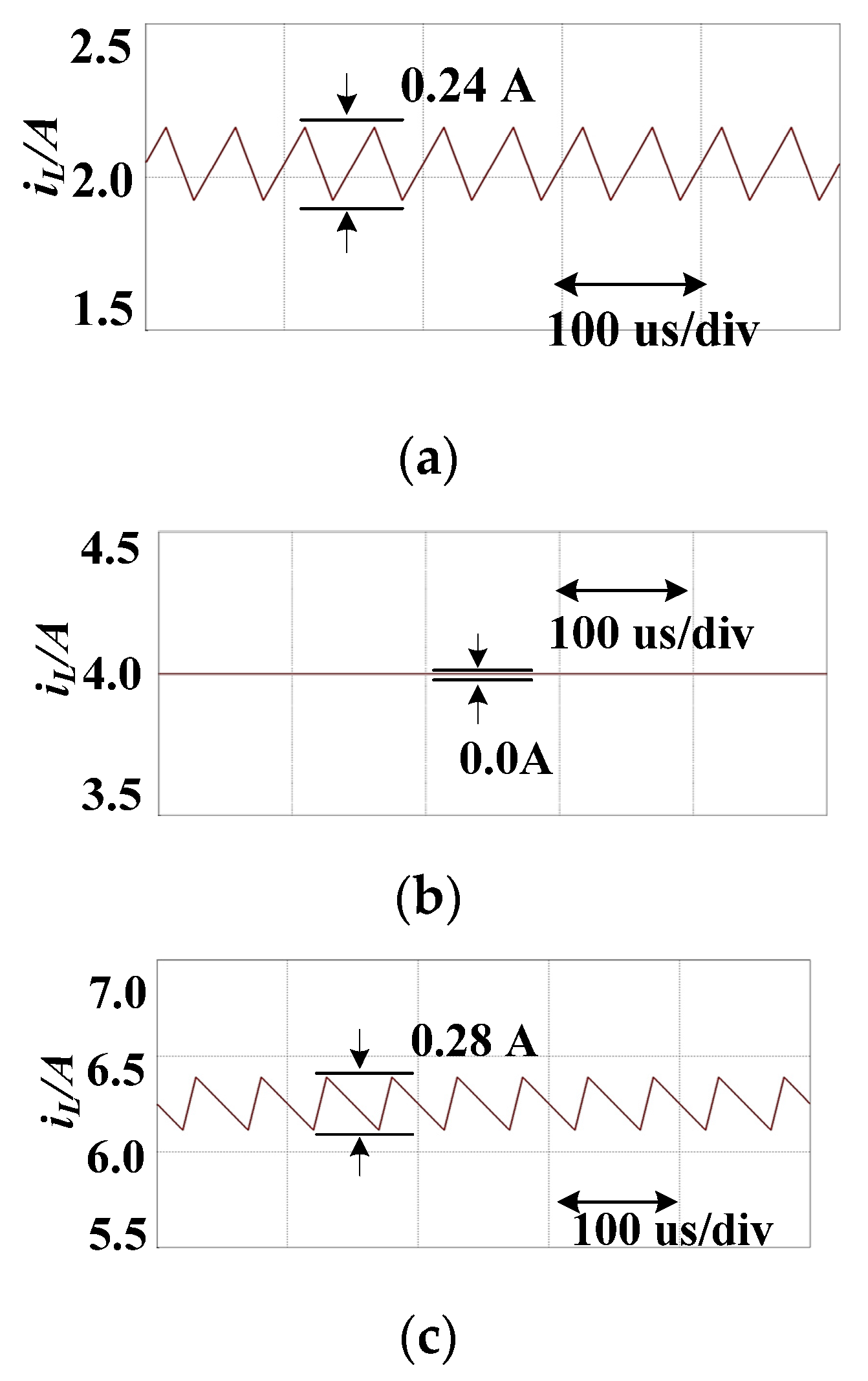

5.4. Input Current Ripple Characteristics

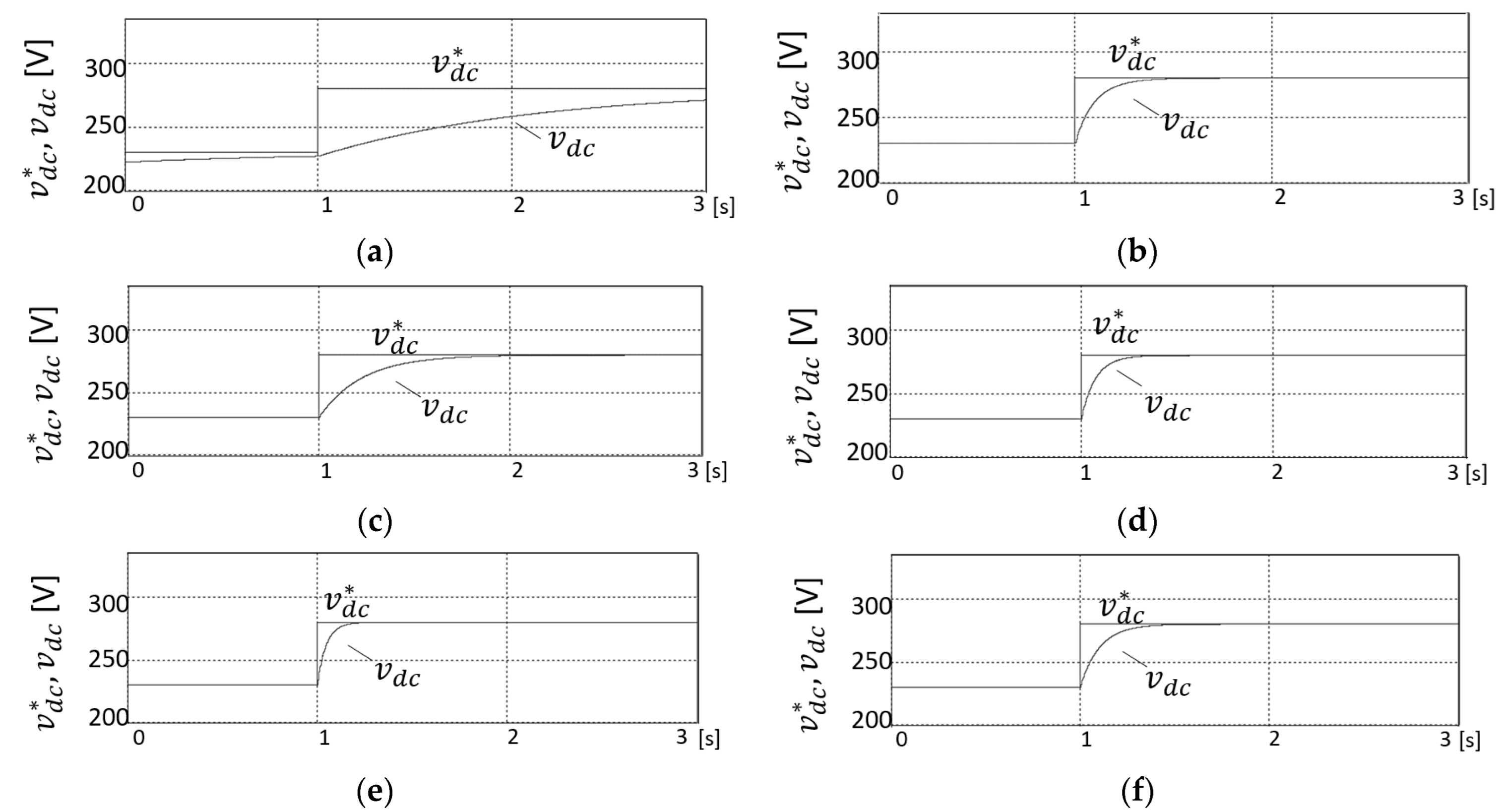

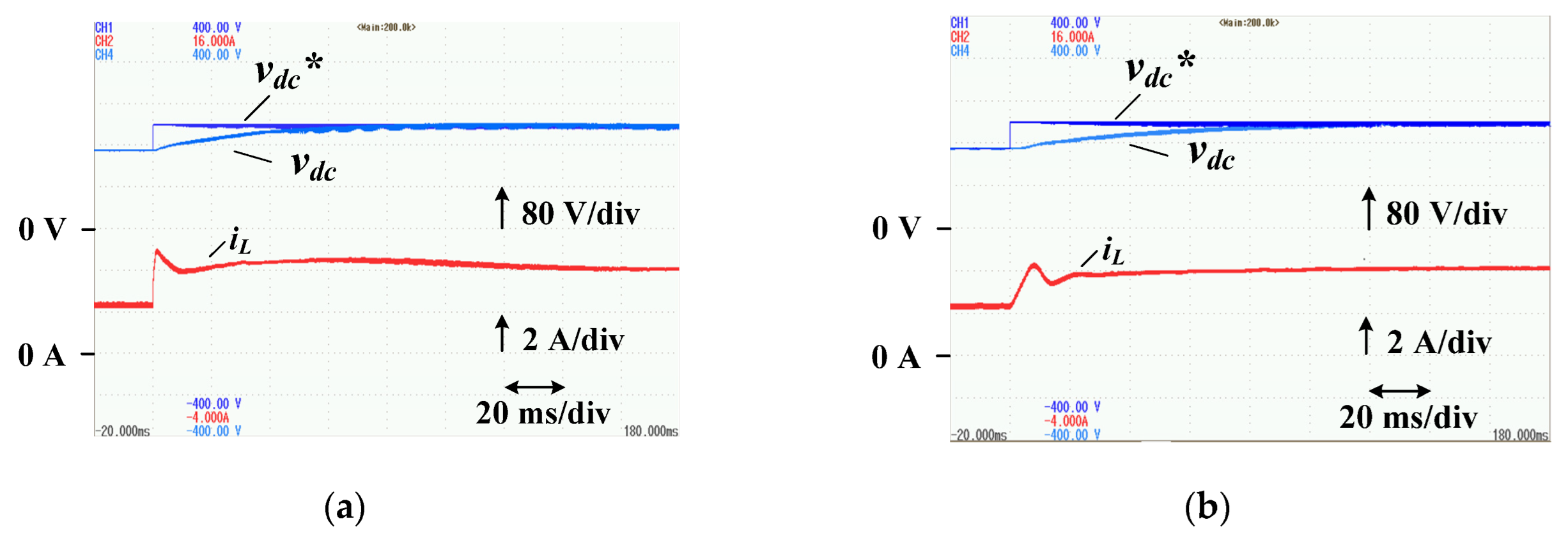

5.5. Output Voltage Response Characteristics

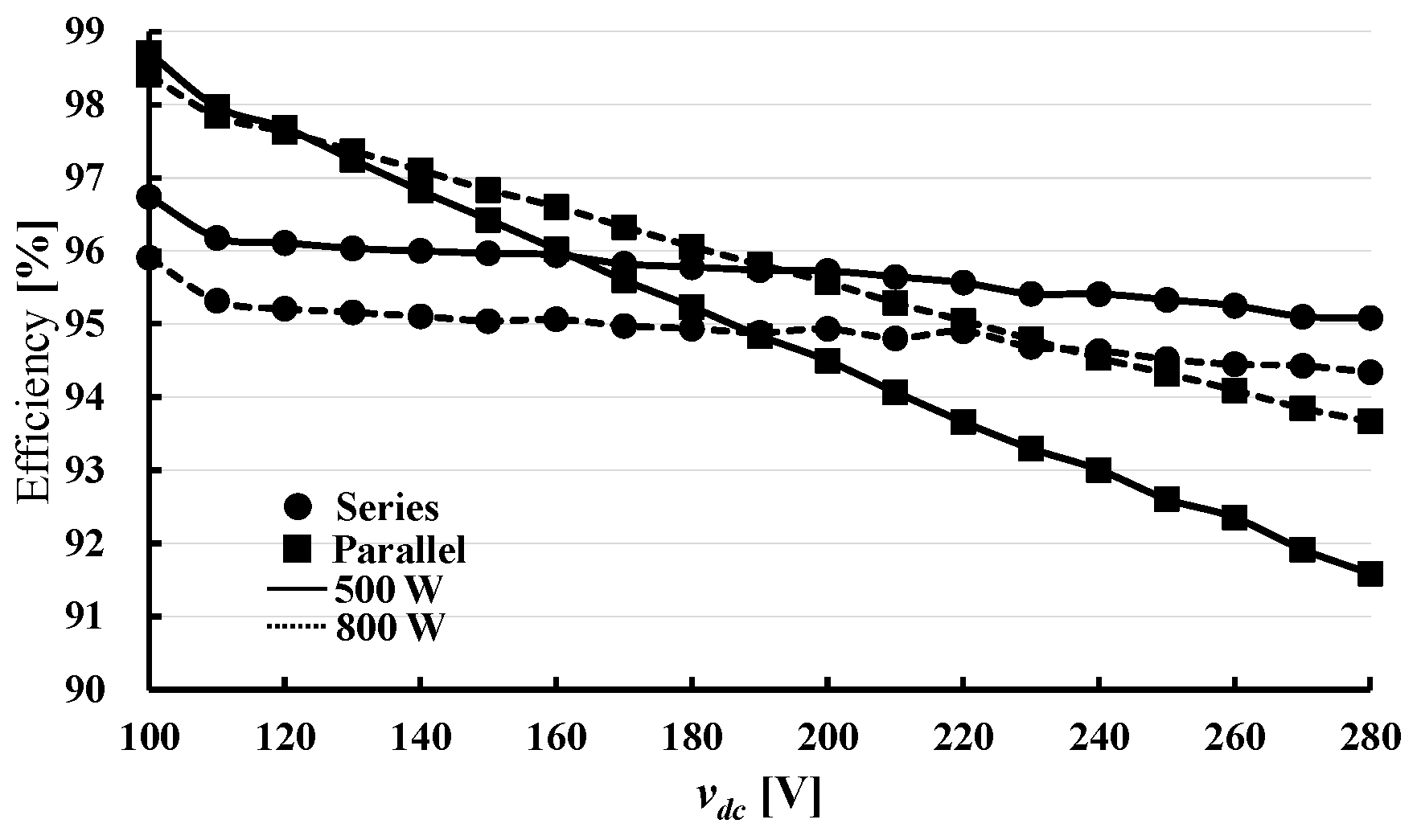

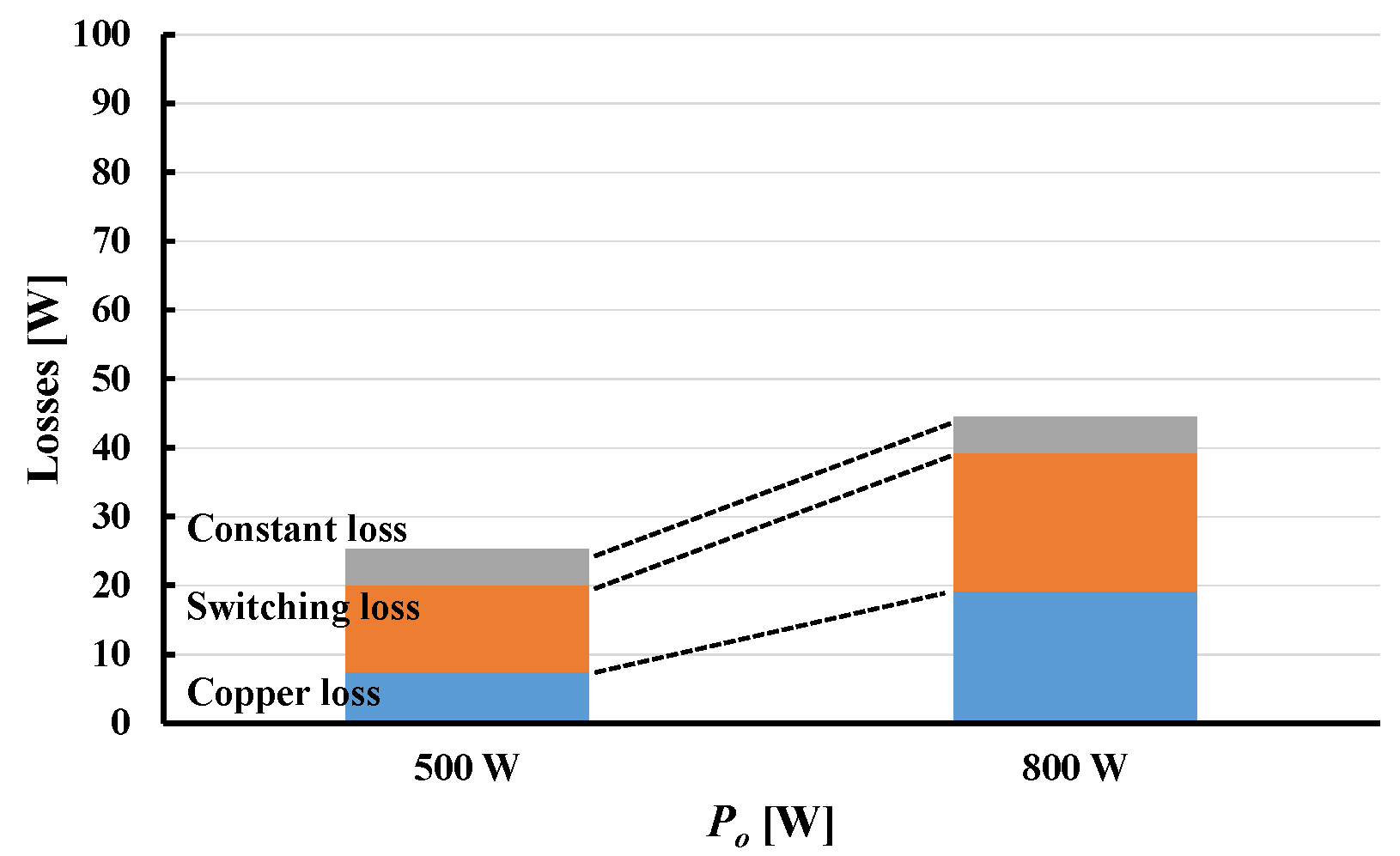

5.6. Efficiency Characteristics

6. Conclusions

- The series circuit is capable of both boosting and neutral potential control by means of a boost converter connected in a dependent manner, and is effective for use in a three-level inverter.

- A theoretical analysis of the input current ripple of the series circuit was performed. The validity of the analysis was demonstrated by experiments and simulations using an experimental apparatus with an output voltage of 280 V.

- When the inductances of the series circuit and the parallel circuit are equal, the input current ripple of the series circuit is one-quarter that of the parallel circuit.

- When the inductance of the series circuit is one-quarter of the parallel circuit and the volume and weight of both circuits are equal, the input current ripple of the two circuits are equal.

- As an output voltage control method for the series circuit, a control method using an optimal regulator was proposed, and a design method using the state averaging method is presented. The proposed optimal regulator has a better load regulation response than the general PI control method, suggesting that it is effective in downsizing the smoothing capacitor.

- The series circuit has higher conversion efficiency in the light load, high voltage region than the parallel circuit, and is suitable for operation in this region.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Mizutani, M.; Tachibana, T.; Morimoto, M.; Akatsu, K.; Hoshi, N. Electric Drive Technologies Contributing to Low-Fuel-Consumption Vehicles. IEEJ Trans. Ind. Appl. 2015, 135, 884–891. (In Japanese) [Google Scholar] [CrossRef]

- Imai, K.; Kawamura, A.; Kinoshita, S.; Ashikaga, T.; Yokoe, K.; Asano, M. Electric Vehicle Related Technologies. Present Technologies and Future Trend on Power Electronics for Electric Vehicle. IEEJ Trans. Ind. Appl. 1996, 116, 223–244. (In Japanese) [Google Scholar] [CrossRef][Green Version]

- Nagai, M.; Wang, Y. Motion Control of Electric Vehicles by Distribution Control of Traction Forces. IEEJ Trans. Ind. Appl. 1996, 116, 279–284. (In Japanese) [Google Scholar] [CrossRef][Green Version]

- Heo, J.; Kondo, K. Design Method Considering the Frequency Band of the Disturbance in the DC Link Voltage Control System of Hybrid Electric Vehicle Driving Systems. IEEJ Trans. Ind. Appl. 2019, 139, 699–707. (In Japanese) [Google Scholar] [CrossRef]

- Marchesoni, M.; Vacca, C. New DC-DC Converter for Energy Storage System Interfacing in Fuel Cell Hybrid Electric Vehicles. IEEE Trans. PE. 2007, 22, 301–308. [Google Scholar] [CrossRef]

- Yamamoto, K.; Imakiire, A.; Iimori, K. PWM Inverter with Voltage Boosters with Regenerating Capability Augmented by Electric Double-Layer Capacitor. IEEJ Trans. Ind. Appl. 2011, 131, 671–678. (In Japanese) [Google Scholar] [CrossRef]

- Toru, A.; Haga, H.; Kondo, S. Comparison between Phase Number and Operation Mode of Multiphase Boost Chopper for Reducing Input Current Ripple. IEEJ Trans. Ind. Appl. 2012, 132, 250–257. (In Japanese) [Google Scholar] [CrossRef]

- Okuda, T.; Urakabe, T.; Tsunoda, Y.; Kikunaga, T.; Iwata, A. Ripple Current Reduction in DC Link Capacitor by Harmonic Control of DC/DC Converter and PWM Inverter. IEEJ Trans. Ind. Appl. 2009, 129, 144–149. (In Japanese) [Google Scholar] [CrossRef]

- Takei, D.; Fujimoto, H.; Hori, Y. Load Current Feedforward Control of Boost Converter for Downsizing the Output Filter Capacitor. IEEJ Trans. Ind. Appl. 2015, 135, 457–466. (In Japanese) [Google Scholar] [CrossRef]

- Sato, D.; Itoh, J. Improvement of the Electric Energy Consumption of Permanent Magnet Synchronous Motor Drive System Using Three-level Inverter. IEEJ Trans. Ind. Appl. 2015, 135, 632–640. (In Japanese) [Google Scholar] [CrossRef]

- Schweizer, M.; Kolar, W.J. Design and Implementation of a Highly Efficient Three-Level T-Type Converter for Low-Voltage Applications. IEEE Trans. PE. 2013, 28, 899–907. [Google Scholar] [CrossRef]

- Ogasawara, S.; Sawada, T.; Akagi, H. Analysis of the Neutral Point Potential Variation of Neutral-Point-Clamped Voltage Source PWM Inverters. IEEJ Trans. Ind. Appl. 1993, 113, 41–48. (In Japanese) [Google Scholar] [CrossRef][Green Version]

- Sakasegawa, E.; Shinohara, K. Compensation for Neutral Point Potential in Three Level Inverter by using Motor Currents. In Proceedings of the 15th International Conference on Electrical Machines, ICEM2002, Brugge, Belgium, 25–28 August 2002. [Google Scholar]

- Zaragoza, J.; Pou, J.; Ceballos, S.; Robles, E.; Ibanez, P.; Villate, L.J. A Comprehensive Study of a Hybrid Modulation Technique for the Neutral-Point-Clamped Converter. IEEE Trans. IE. 2009, 56, 294–303. [Google Scholar] [CrossRef]

- Yaramasu, V.; Wu, B.; Alepuz, S.; Kouro, S. Predictive Control for Low-Voltage Ride-Through Enhancement of Three-Level-Boost and NPC-Converter-Based PMSG Wind Turbine. IEEE Trans. IE. 2014, 61, 6832–6843. [Google Scholar] [CrossRef]

- Sakasegawa, E.; Matsumoto, T.; Tokunaga, K.; Haga, H. Control Method to Reduce Current Ripple of Boost Chopper Suitable for NPC Inverter. In Proceedings of the IEEE 9th IPEMC 2020 ECCE Asia, Nanjing, China, 29 November–2 December 2020; pp. 2467–2642. [Google Scholar]

| Input voltage Vi | 100 V |

| Carrier frequency fc1, fc2 | 10 kHz |

| IGBT | FGH40T120SMD |

| rated voltage | 1200 V |

| rated current | 40 A |

| Diode | FEP16DT |

| rated voltage | 600 V |

| rated current | 16 A |

| DC reactor | - |

| inductance L1, L2 | 1.8 mH |

| rated current | 9 A |

| core | silicon steel plate |

| resistance | 68.6 mΩ |

| Capacitanc Cp,Cn | 1500 uF |

| Parameter | Value |

|---|---|

| Kpi | 4 |

| Tii | 4 ms |

| Kpv | 0.075 |

| Tiv | 40 ms |

| Kpn | 2 |

| Tin | 0.1s |

| Feedback Gain | |||

|---|---|---|---|

| K1 | −0.028 | K6 | 1.310 |

| K2 | −1.060 | G1 | 8.072 |

| K3 | 0.744 | G2 | 0.886 |

| K4 | 0.133 | G3 | −56.322 |

| K5 | 3.302 | G4 | −45.360 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sakasegawa, E.; Chishiki, R.; Sedutsu, R.; Soeda, T.; Haga, H.; Kennel, R.M. Comparison of Interleaved Boost Converter and Two-Phase Boost Converter Characteristics for Three-Level Inverters. World Electr. Veh. J. 2023, 14, 7. https://doi.org/10.3390/wevj14010007

Sakasegawa E, Chishiki R, Sedutsu R, Soeda T, Haga H, Kennel RM. Comparison of Interleaved Boost Converter and Two-Phase Boost Converter Characteristics for Three-Level Inverters. World Electric Vehicle Journal. 2023; 14(1):7. https://doi.org/10.3390/wevj14010007

Chicago/Turabian StyleSakasegawa, Eiichi, Rin Chishiki, Rintarou Sedutsu, Takumi Soeda, Hitoshi Haga, and Ralph Mario Kennel. 2023. "Comparison of Interleaved Boost Converter and Two-Phase Boost Converter Characteristics for Three-Level Inverters" World Electric Vehicle Journal 14, no. 1: 7. https://doi.org/10.3390/wevj14010007

APA StyleSakasegawa, E., Chishiki, R., Sedutsu, R., Soeda, T., Haga, H., & Kennel, R. M. (2023). Comparison of Interleaved Boost Converter and Two-Phase Boost Converter Characteristics for Three-Level Inverters. World Electric Vehicle Journal, 14(1), 7. https://doi.org/10.3390/wevj14010007