A 326,000 fps 640 × 480 Resolution Continuous-Mode Ultra-High-Speed Global Shutter CMOS BSI Imager †

Abstract

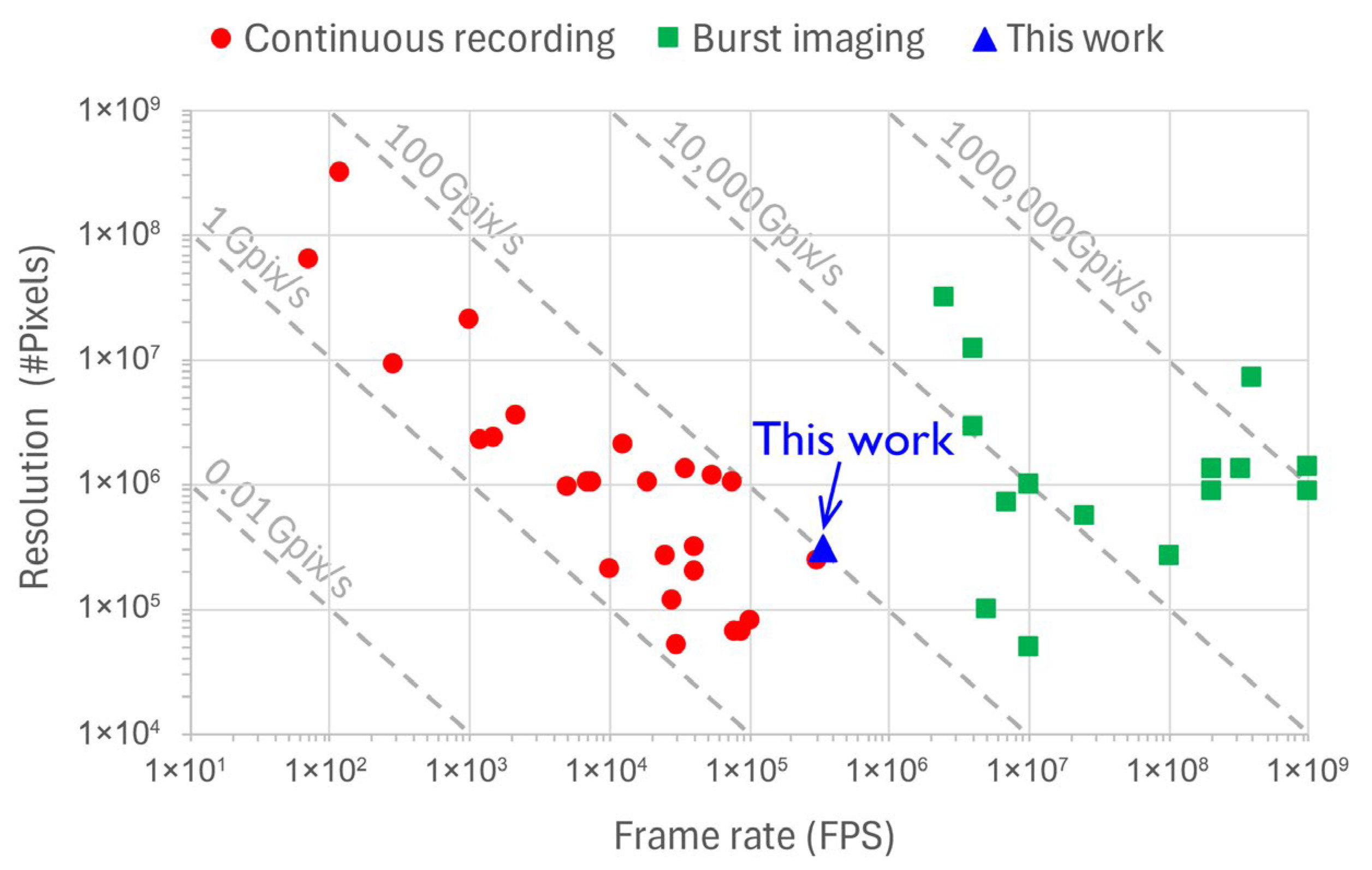

1. Introduction

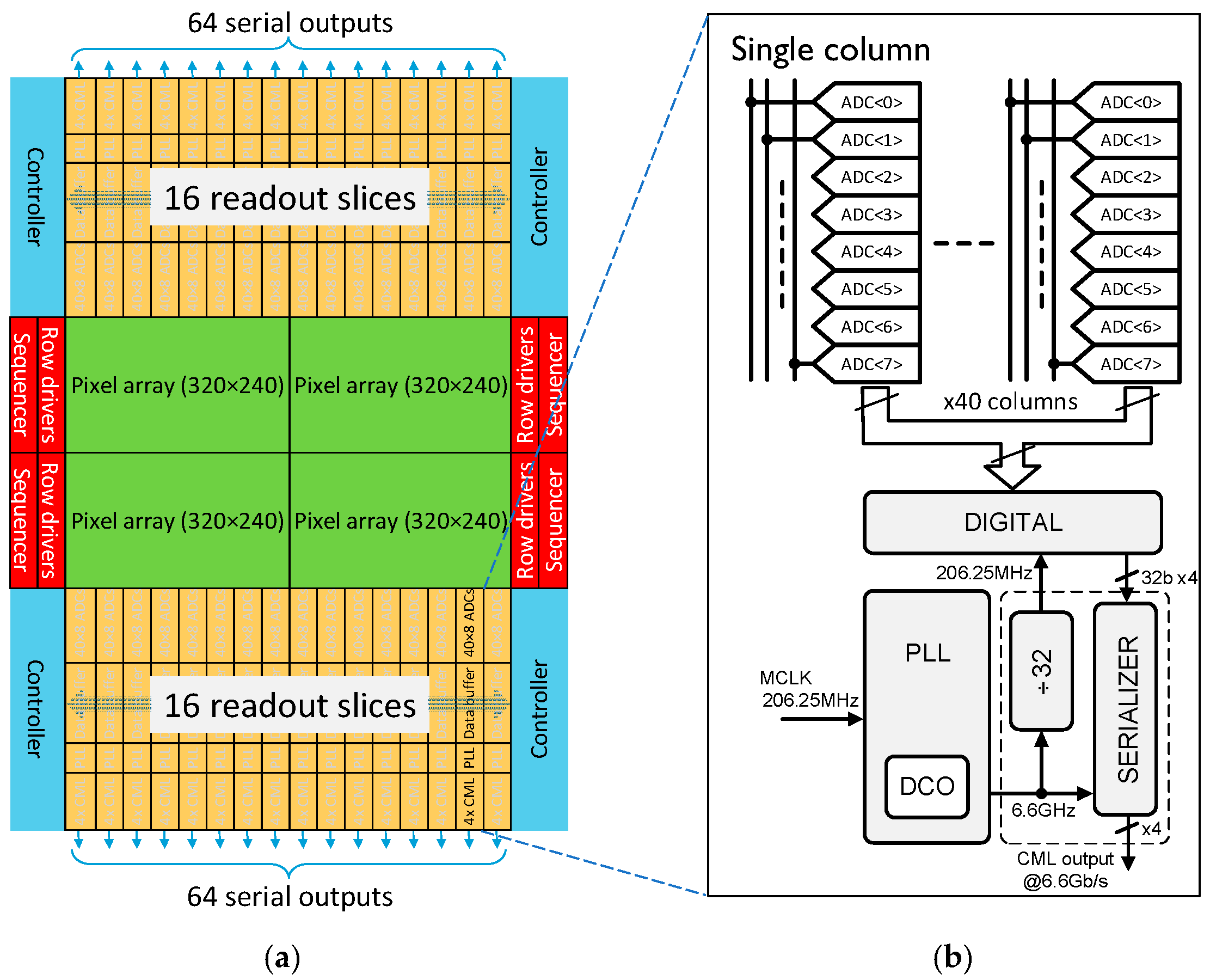

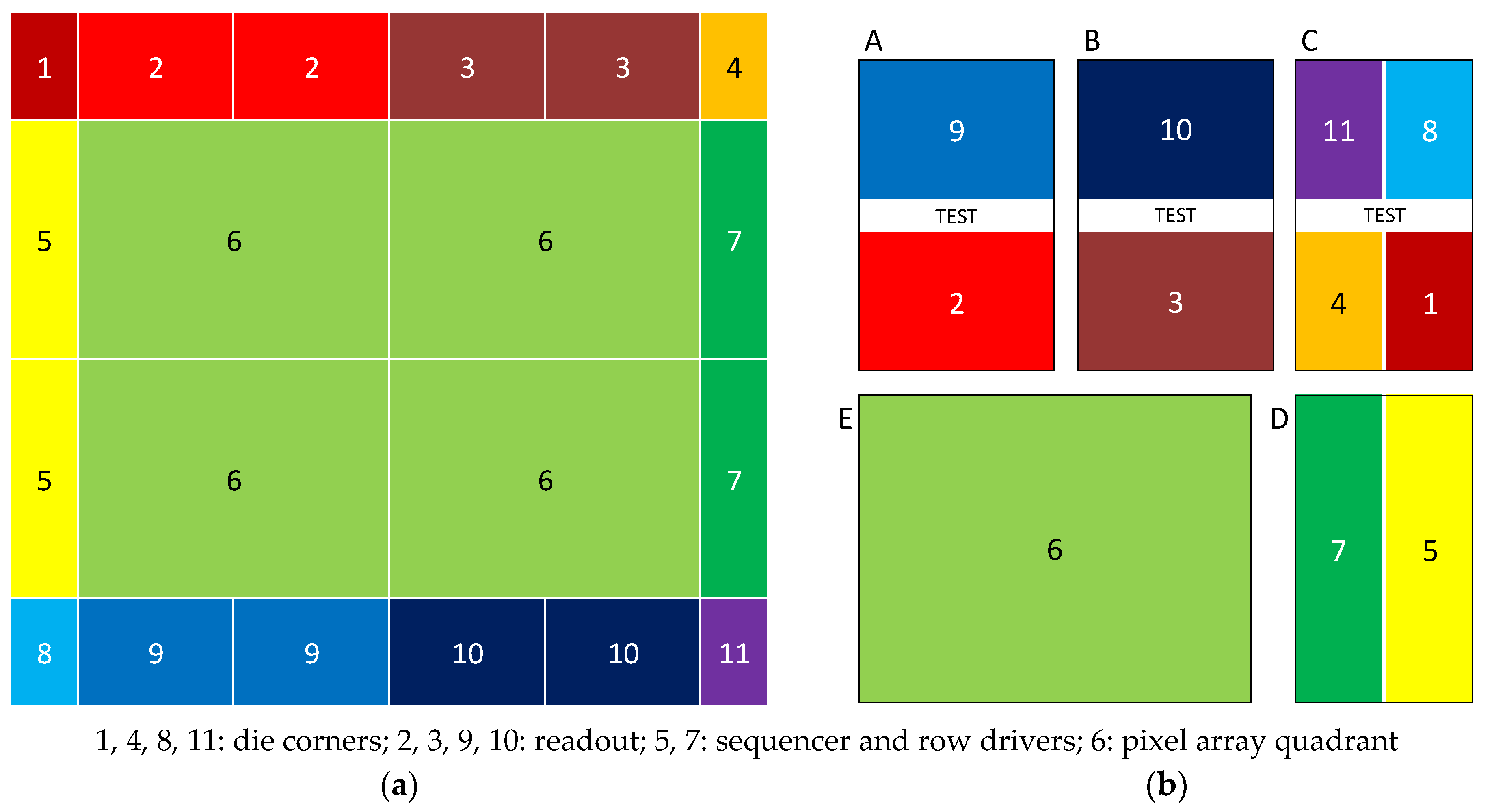

2. Imager Architecture

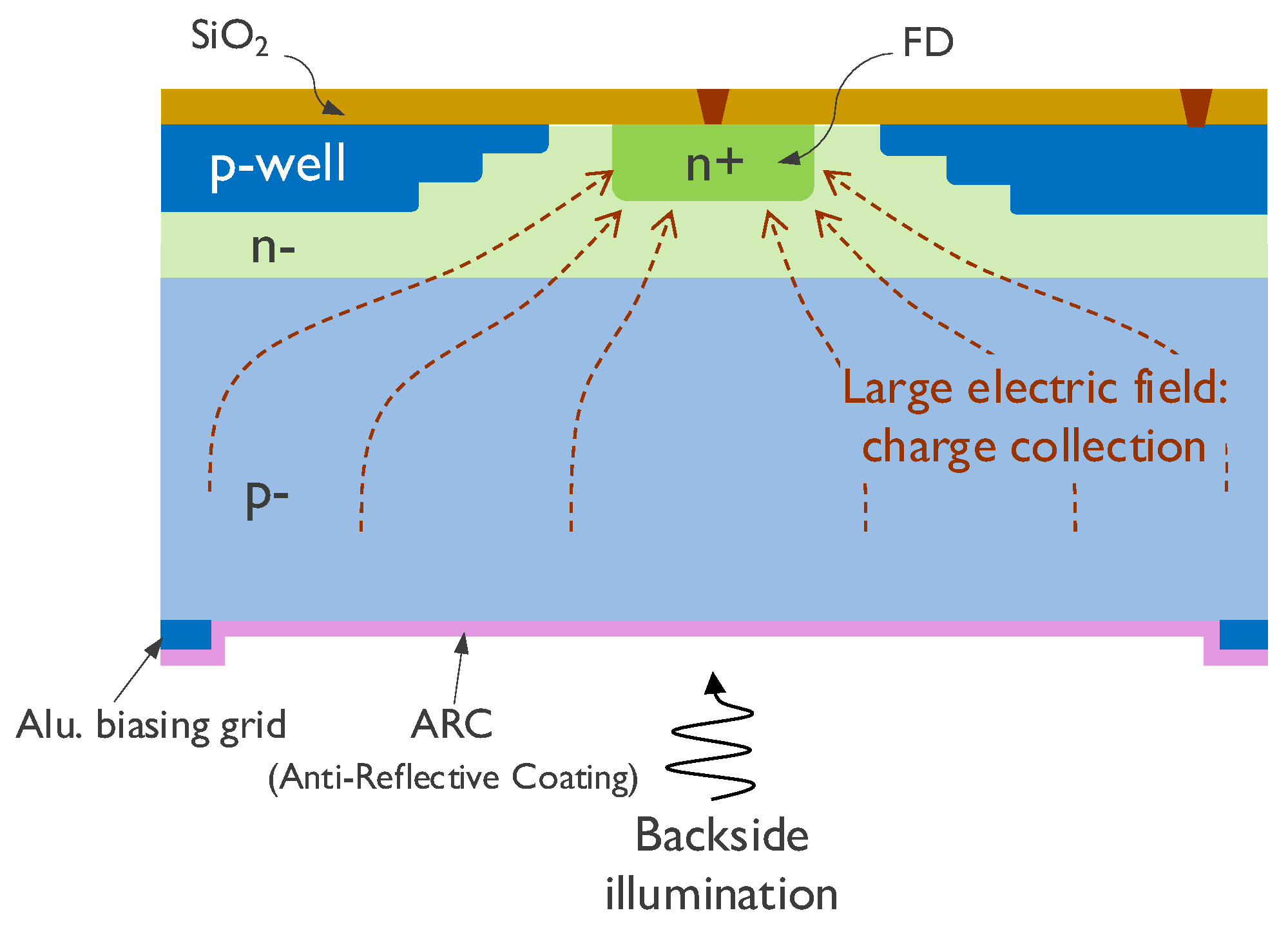

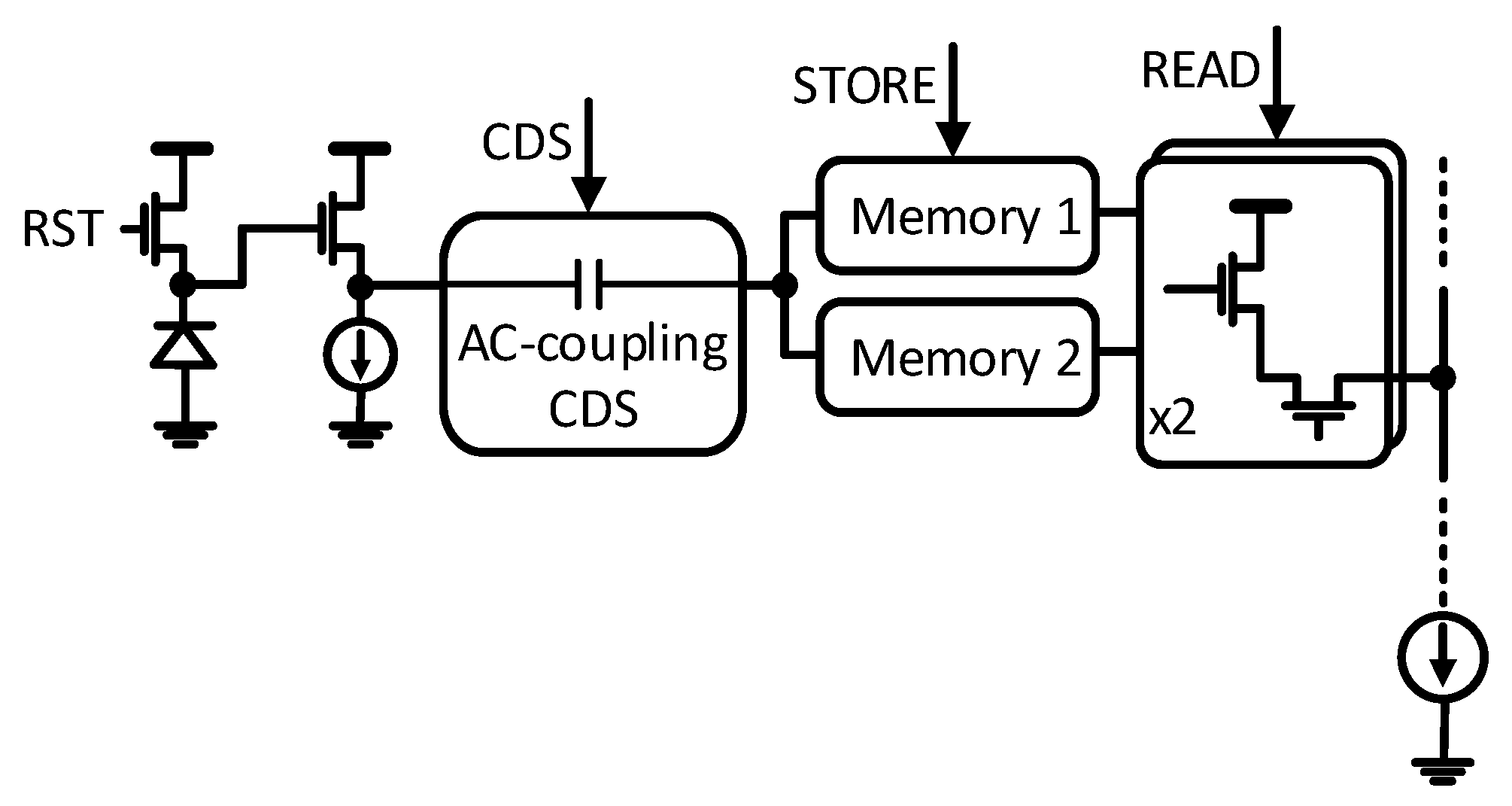

2.1. Pixel Array

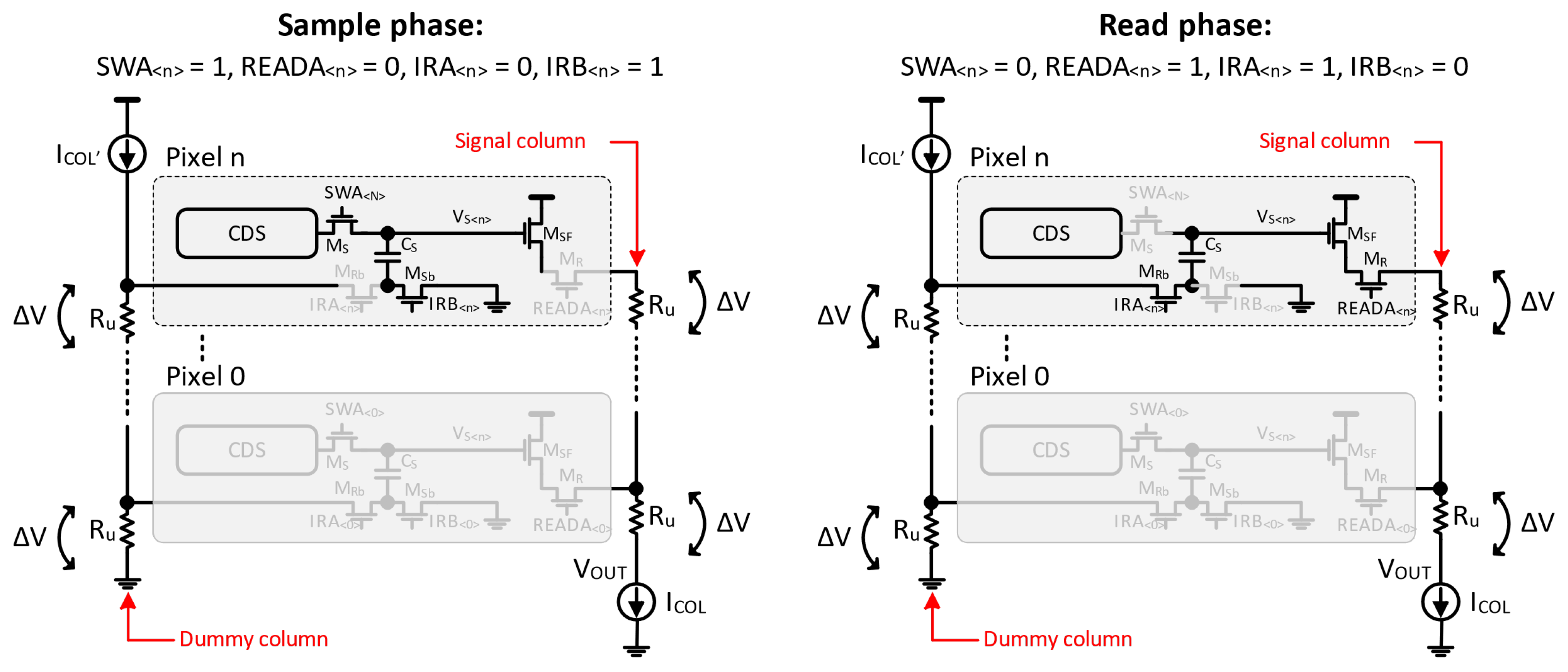

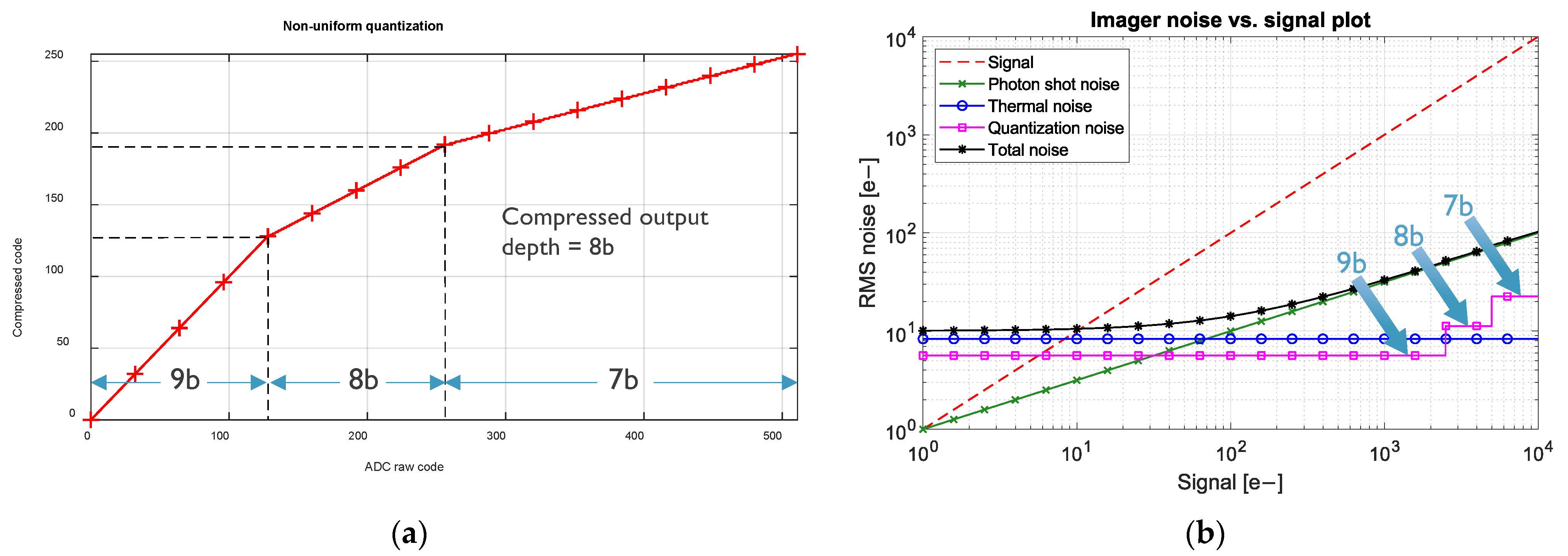

2.2. Sensor Architecture

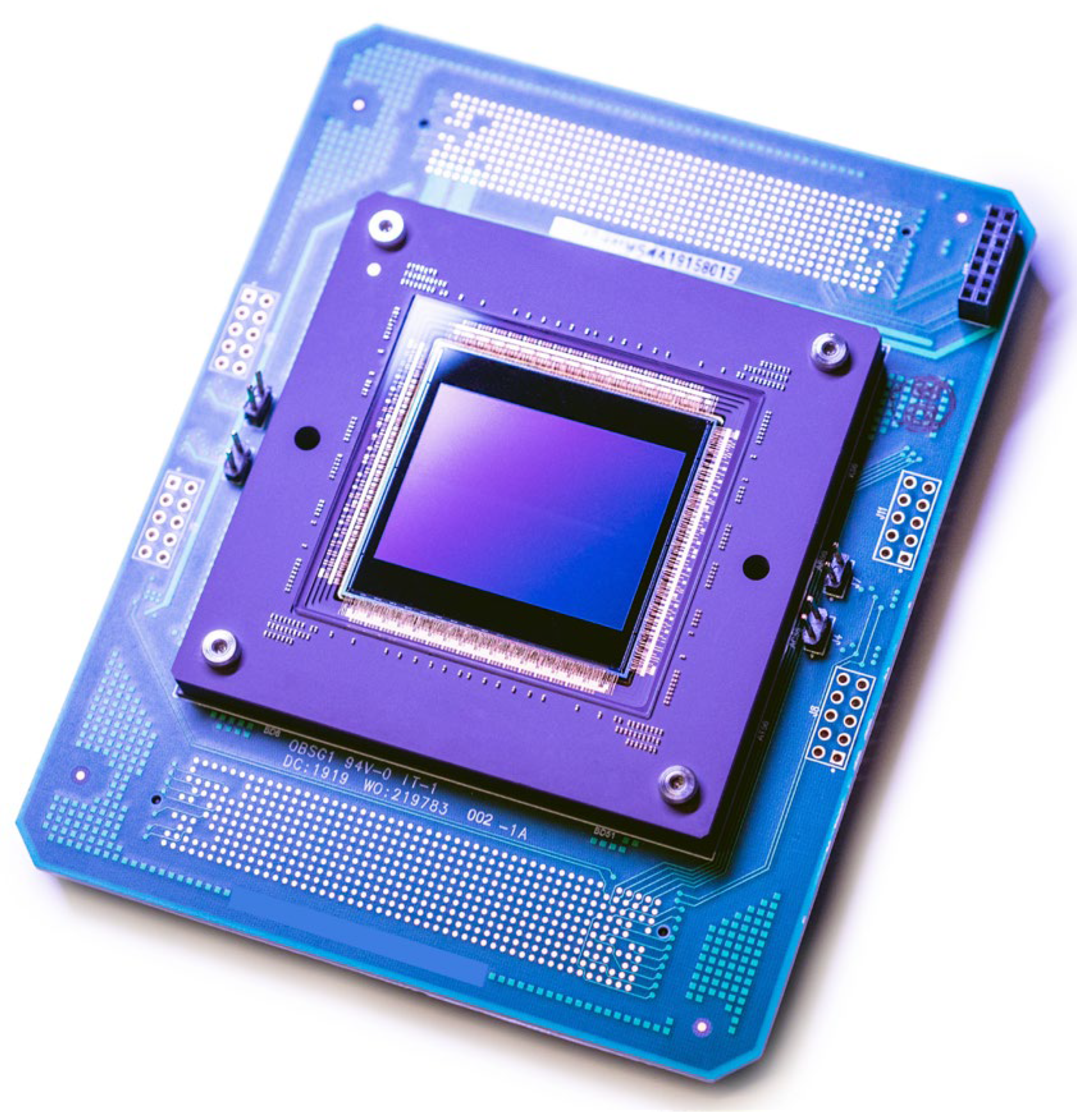

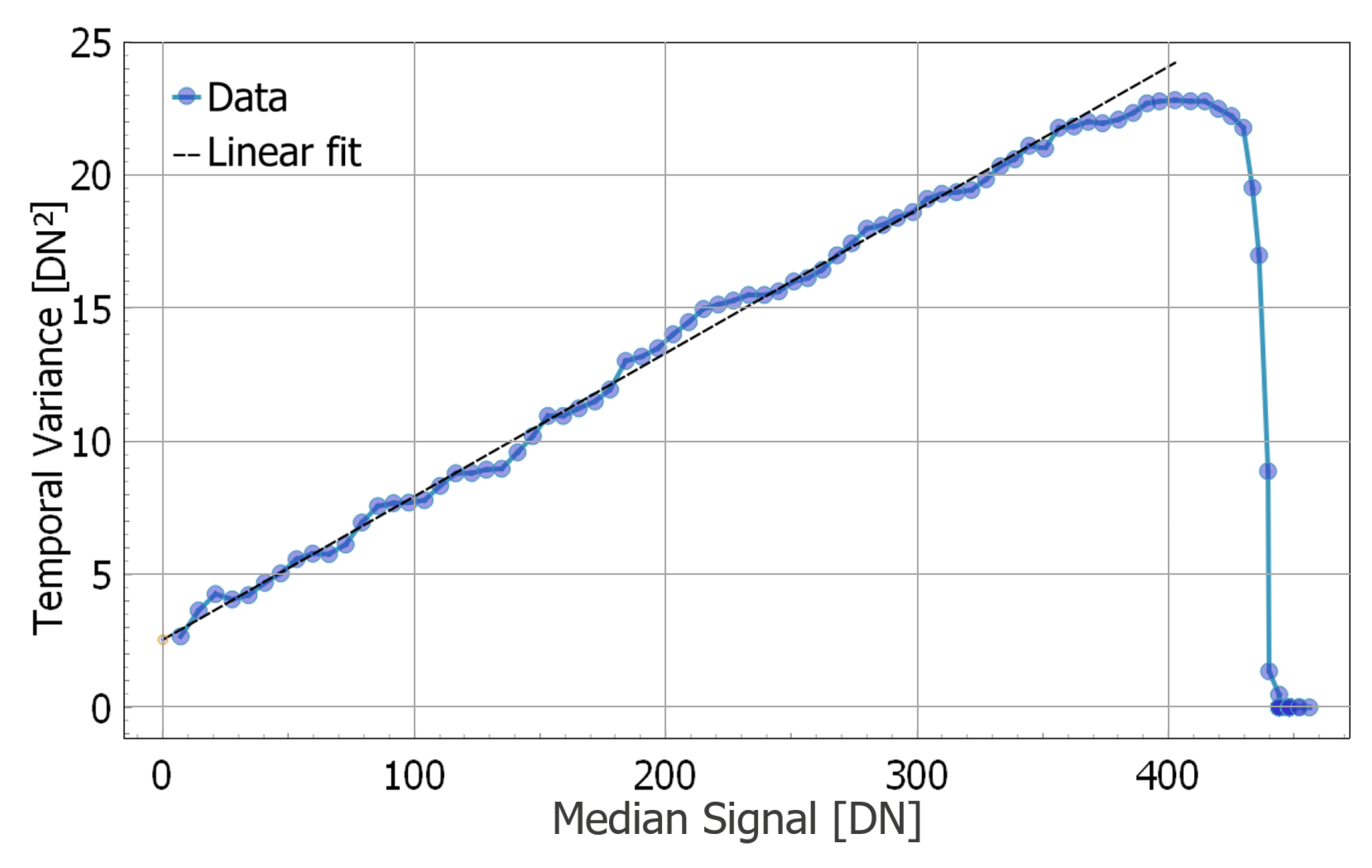

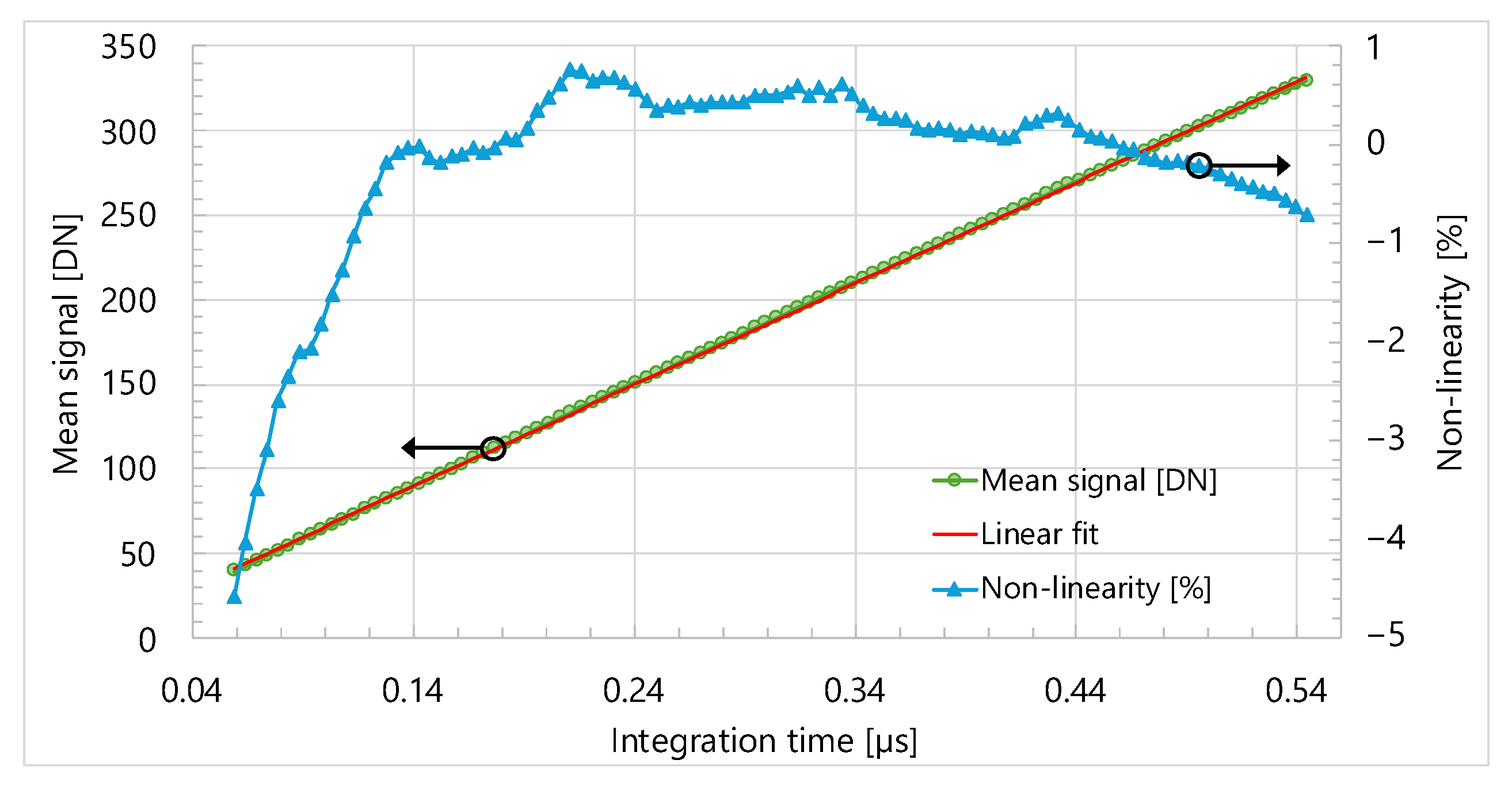

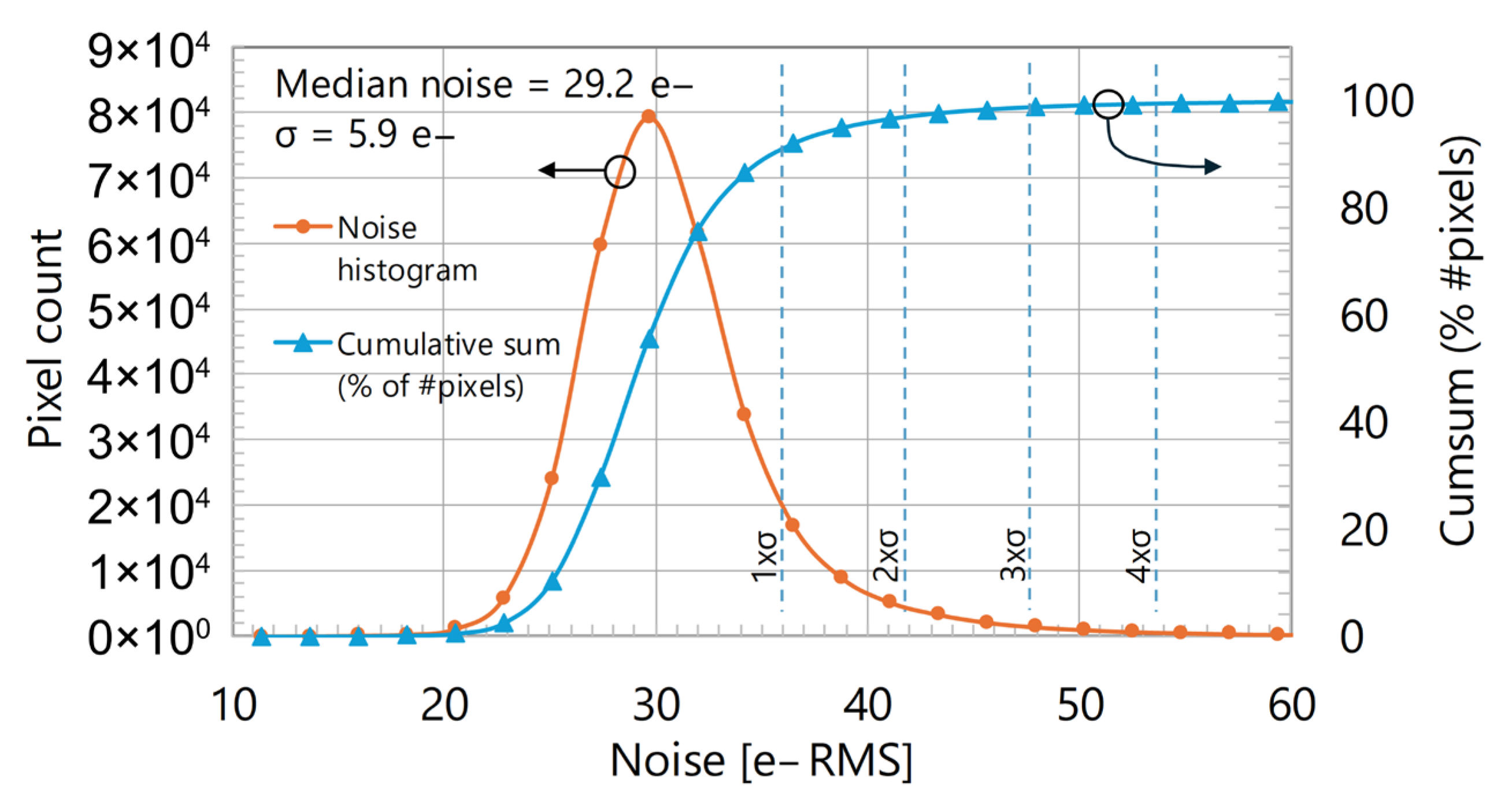

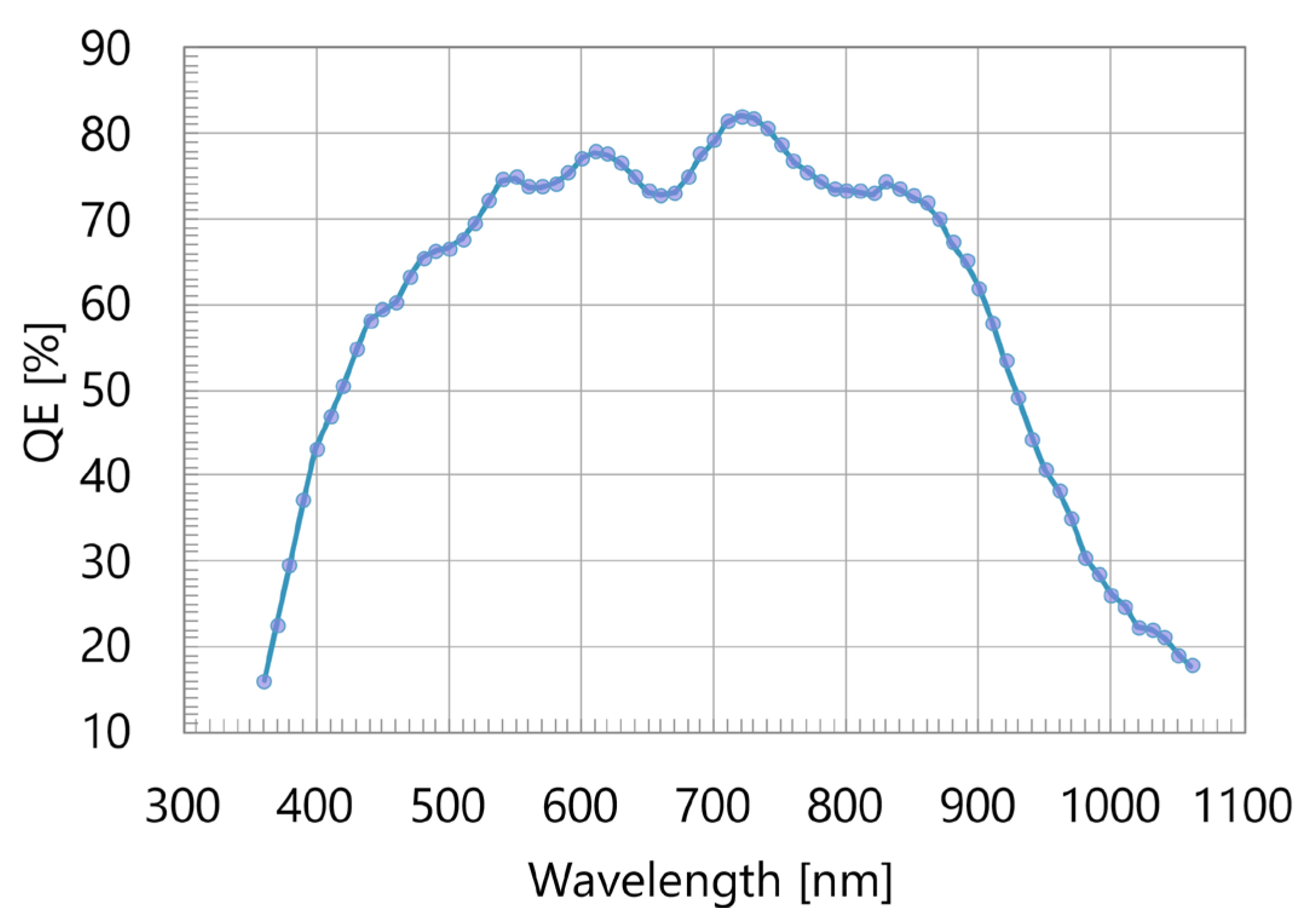

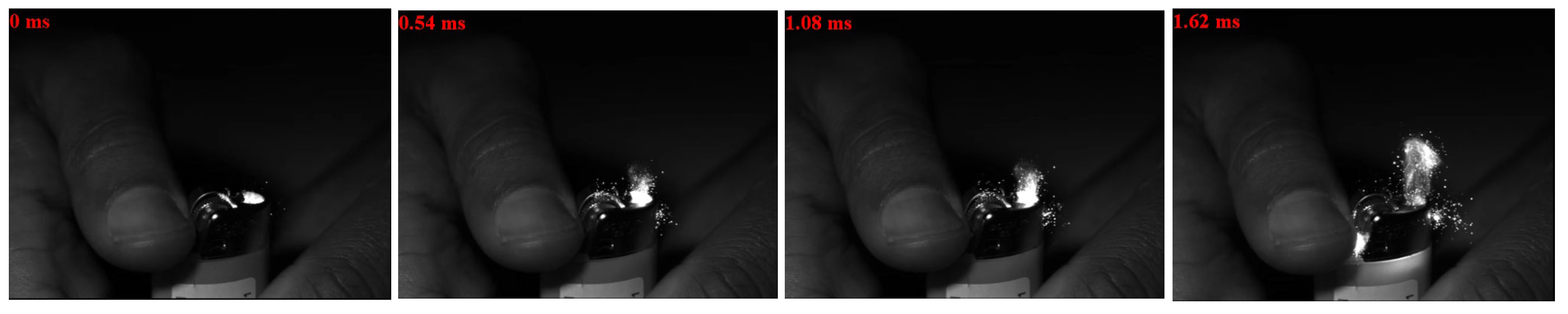

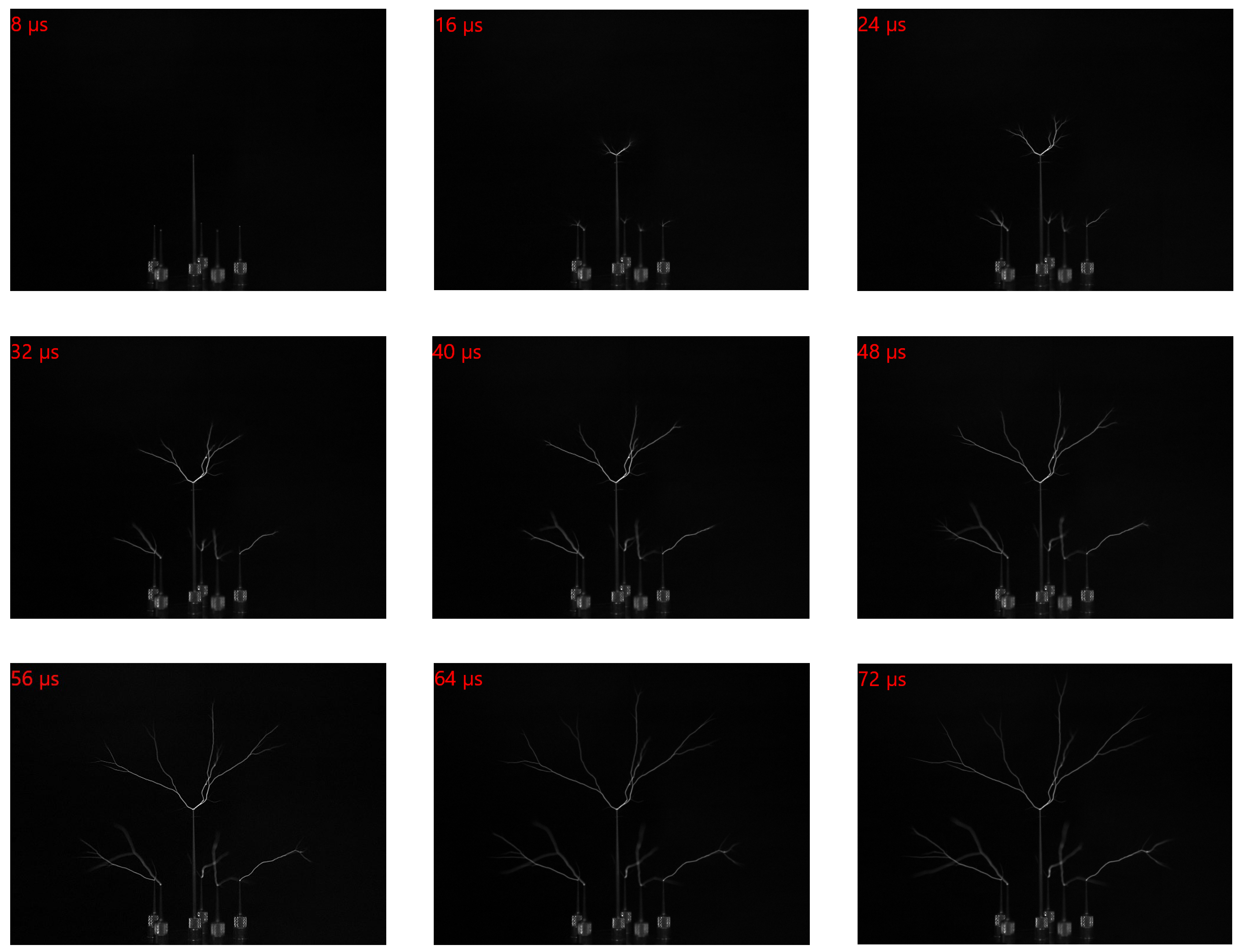

3. Measurement Results

4. Conclusions

5. Patents

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Süss, A.; Wu, L.; Bacq, J.-L.; Spagnolo, A.; Coppejans, P.; Motsnyi, V.; Haspeslagh, L.; Borremans, J.; Rosmeulen, M. A Fully Depleted 52 μm GS CIS Pixel with 6 ns Charge Transfer, 7 e-rms Read Noise, 80 μV/e-CG and >80% VIS-QE. In Proceedings of the IISW, Hiroshima, Japan, 30 May–2 June 2017. [Google Scholar]

- Mahato, S.B.; Bacq, J.-L.; Boulenc, P.; Chang, Y.-T.; Van Lijnschoten, B.; Malainou, A.; Cavaco, C. Fully Depleted CIS Pixel Using Reverse Substrate Bias without Undesirable Leakage Currents. In Proceedings of the IISW, Hyogo, Japan, 2–5 June 2025. [Google Scholar]

- Stark, L.; Raynor, J.M.; Lalanne, F.; Henderson, R.K. A Back-illuminated Voltage-domain Global Shutter Pixel with Dual In-pixel Storage. IEEE Trans. Electron Devices 2018, 65, 4394–4400. [Google Scholar] [CrossRef]

- Merrill, R. Intra-Pixel Reset Noise Cancellation. In Proceedings of the 2001 IEEE Workshop on Charge Coupled Devices and Advanced Image Sensors, Lake Tahoe, NV, USA, 7–9 June 2001. [Google Scholar]

- Inoue, T.; Takeuchi, S.; Kawahito, S. CMOS Active Pixel Image Sensor with in-Pixel CDS for High-Speed Cameras; SPIE: Bellingham, WA, USA, 2005. [Google Scholar]

- Spagnolo, A.; Borremans, J. Image Sensor and a Method for Read-Out of Pixel Signal. United States Patent US 10,778,926 B2, 15 September 2020. [Google Scholar]

- Van Blerkom, D.; Truong, L.; Rysinski, J.; Corlan, R.; Venkatesan, K.; Bagwell, S.; Oniciuc, L.; Bergey, J. A 1Mpixel, 80k fps Global Shutter CMOS Image Sensor for High Speed Imaging. In Proceedings of the IISW, Online, 20–23 September 2021. [Google Scholar]

- Cai, G.; Tajima, K.; Van Hoorebeeck, A.; Stampoglis, P.; Luyssaert, B.; Dierickx, B.; Gokel, C.; Van Uffelen, T.; Ruttens, G.; Yamane, J.; et al. A 1.3M Pixel 34,700fps Global-Shutter BSI Imager with HDR and Motion Blur Suppression Capability. In Proceedings of the IISW, Online, 20–23 September 2021. [Google Scholar]

- Snoeij, M.F.; Theuwissen, A.J.P.; Makinwa, K.A.A.; Huijsing, J.H. Multiple-Ramp Column-Parallel ADC Architectures for CMOS Image Sensors. IEEE J. Solid-State Circuits 2007, 42, 2968–2977. [Google Scholar] [CrossRef]

- Vision Research. Phantom TMX 7510 Datasheet (Binned Mode). [Online]. Available online: https://www.phantomhighspeed.com/products/cameras/tmx/7510 (accessed on 10 June 2025).

- Bacq, J.-L.; Thite, M.; Vandebriel, R.; Mahato, S.B.; Coppejans, P.; Borremans, J.; Wu, L.; Rączkowski, K.; Cevik, I.; Motsnyi, V.; et al. A 640 × 480 Resolution 326,000fps Continuous-Mode Ultra-High Speed Global-Shutter CMOS BSI Imager with Exceptional Light Sensitivity. In Proceedings of the International Image Sensor Workshop, Hyogo, Japan, 2–5 June 2025. [Google Scholar]

| Parameter | This Work [11] | [7] | [10] |

|---|---|---|---|

| Technology | 130 nm, 5 metal CMOS, BSI | 110 nm, 6 metal CMOS, BSI | CMOS, BSI |

| Binning | Not available | 2 × 2 | 2 × 2 |

| Resolution | 640 × 480 | 1280 × 832 | Binned 640 × 384 |

| Pixel pitch | 52 µm | 18.54 µm | Binned 37 µm |

| Shutter type | Global | Global | Global |

| FWC | 7.5 ke- | N/A | 33 ke- |

| Conversion Gain | 0.054 DN/e- | N/A | N/A |

| QE @ 532 nm | 72.7% | N/A | 72.0% |

| Max. FPS (max. ROI) | 326,000 | 80,000 | 308,820 |

| Equivalent row time | 6.4 ns | 15.0 ns (no binning) | 8.4 ns |

| Readout noise | 29.5 e- RMS | N/A | 70.7 e- RMS |

| μe.min.area ‡ (EMVA 1288) | 0.011 e-/μm2 | N/A | 0.056 e-/μm2 † |

| Min. integration time | 59 ns | Binned 95 ns | 95 ns/38 ns |

| Dynamic range | 48 dB | 52 dB | 53.4 dB |

| Bit depth | 9 bits | 10/11/12 bits depending on row time | 12 bits |

| Output channels | 128 channels @ 6.6 Gbps | 160 channels @ 6.25 Gbps | N/A |

| Image lag | 1 DN (9-bit) | N/A | N/A |

| Non-linearity | <5% | <1.75% | 1.29% † |

| Dark current @ room temperature | 3.41 nA/cm2 | N/A | 2.3 nA/cm2 † |

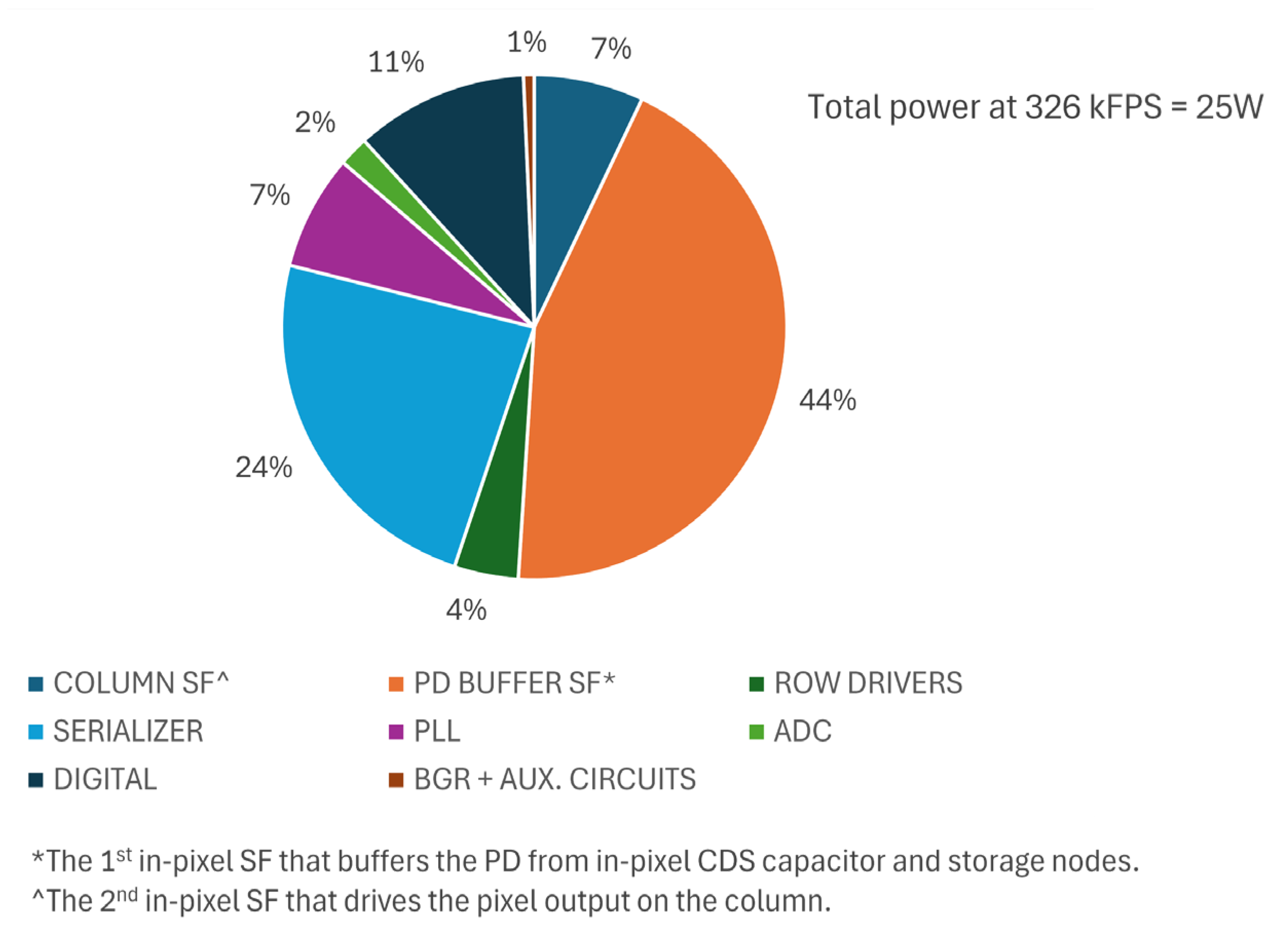

| Power consumption | 25 W | <40 W | N/A |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Bacq, J.-L.; Thite, M.; Vandebriel, R.; Mahato, S.B.; Coppejans, P.; Borremans, J.; Wu, L.; Rączkowski, K.; Cevik, I.; Motsnyi, V.; et al. A 326,000 fps 640 × 480 Resolution Continuous-Mode Ultra-High-Speed Global Shutter CMOS BSI Imager. Sensors 2025, 25, 7372. https://doi.org/10.3390/s25237372

Bacq J-L, Thite M, Vandebriel R, Mahato SB, Coppejans P, Borremans J, Wu L, Rączkowski K, Cevik I, Motsnyi V, et al. A 326,000 fps 640 × 480 Resolution Continuous-Mode Ultra-High-Speed Global Shutter CMOS BSI Imager. Sensors. 2025; 25(23):7372. https://doi.org/10.3390/s25237372

Chicago/Turabian StyleBacq, Jean-Luc, Mandar Thite, Roeland Vandebriel, Swaraj Bandhu Mahato, Philippe Coppejans, Jonathan Borremans, Linkun Wu, Kuba Rączkowski, Ismail Cevik, Vasyl Motsnyi, and et al. 2025. "A 326,000 fps 640 × 480 Resolution Continuous-Mode Ultra-High-Speed Global Shutter CMOS BSI Imager" Sensors 25, no. 23: 7372. https://doi.org/10.3390/s25237372

APA StyleBacq, J.-L., Thite, M., Vandebriel, R., Mahato, S. B., Coppejans, P., Borremans, J., Wu, L., Rączkowski, K., Cevik, I., Motsnyi, V., Haspeslagh, L., Suess, A., Flon, B., Jantzen, D., Jantzen, P., Cavaco, C., & Spagnolo, A. (2025). A 326,000 fps 640 × 480 Resolution Continuous-Mode Ultra-High-Speed Global Shutter CMOS BSI Imager. Sensors, 25(23), 7372. https://doi.org/10.3390/s25237372