A 209 ps Shutter-Time CMOS Image Sensor for Ultra-Fast Diagnosis

Abstract

1. Introduction

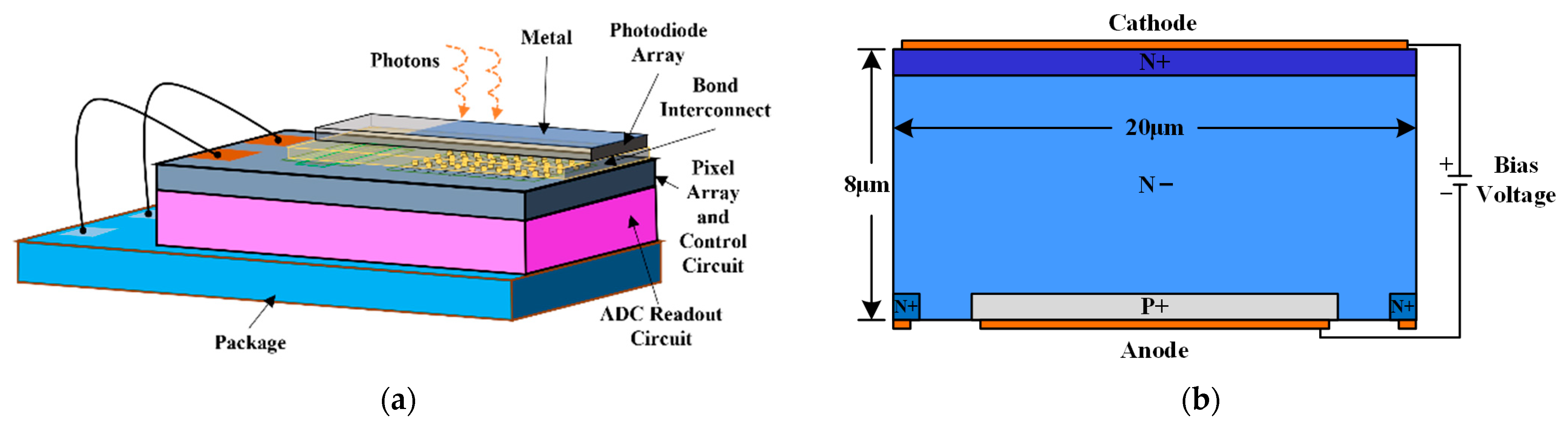

2. CMOS Image Sensor Design Methodology

3. Results

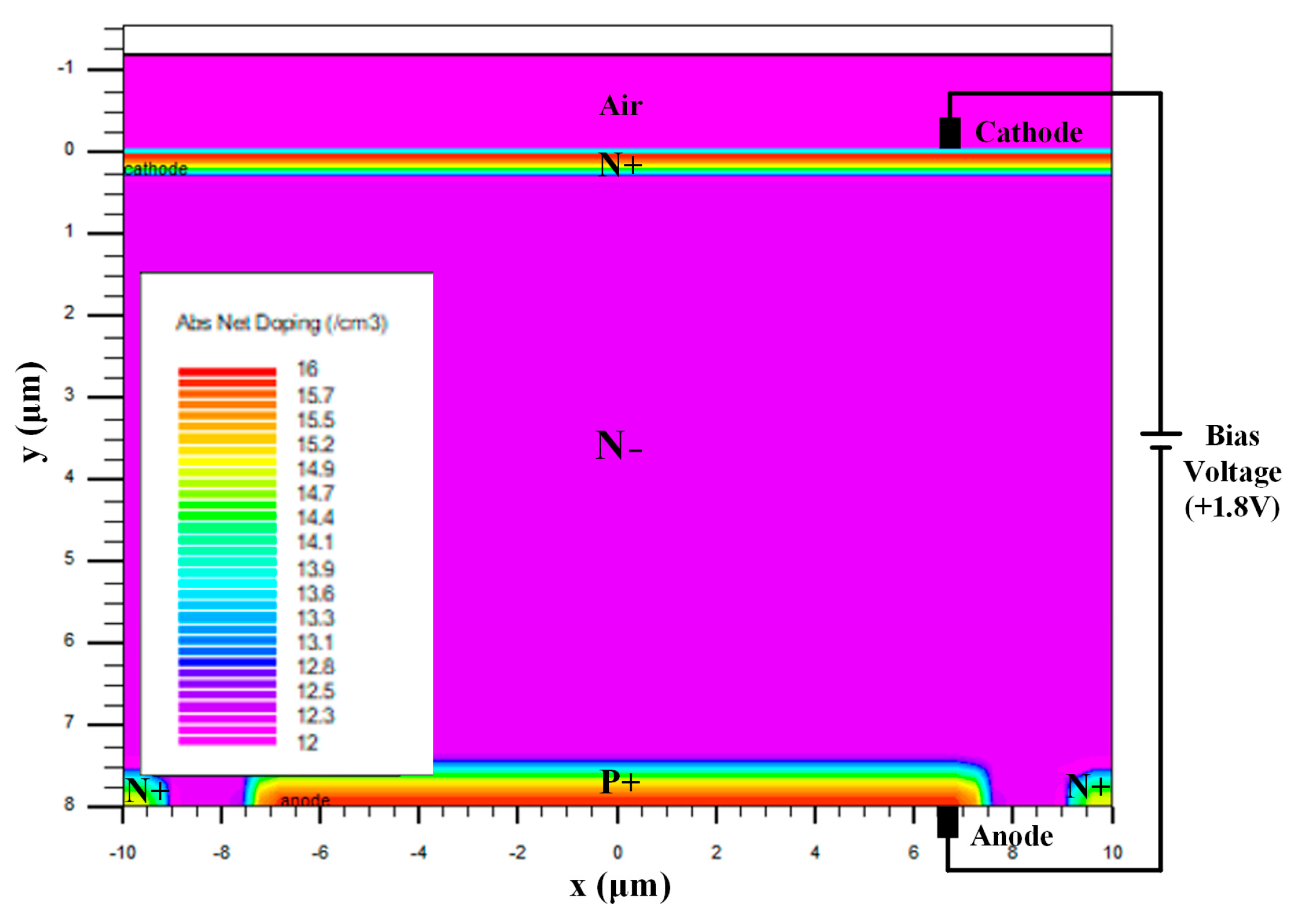

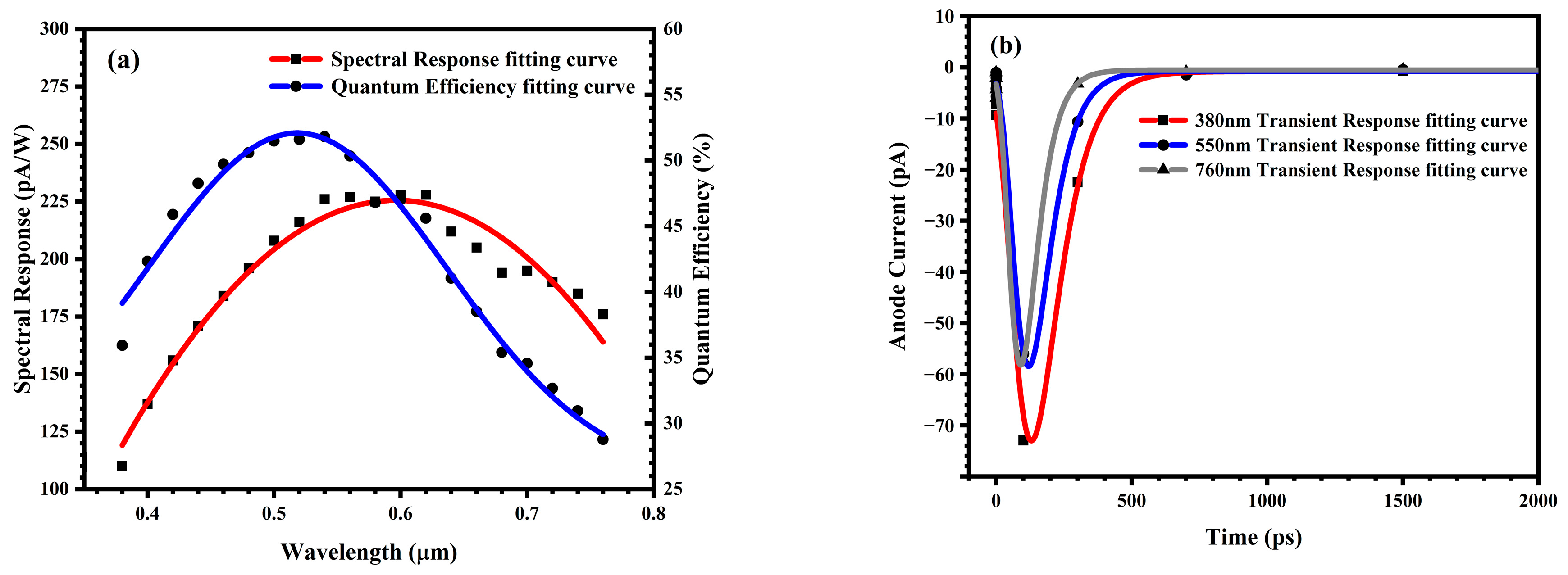

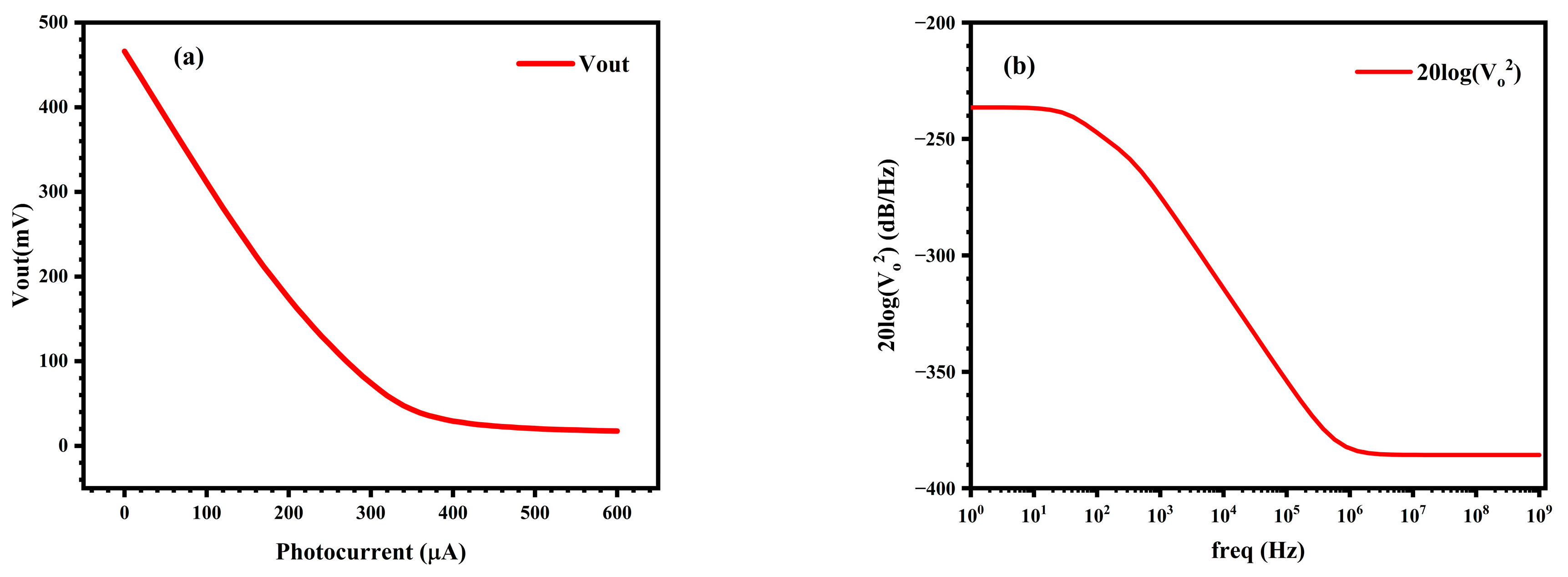

3.1. Performance Test of the Photodiodes

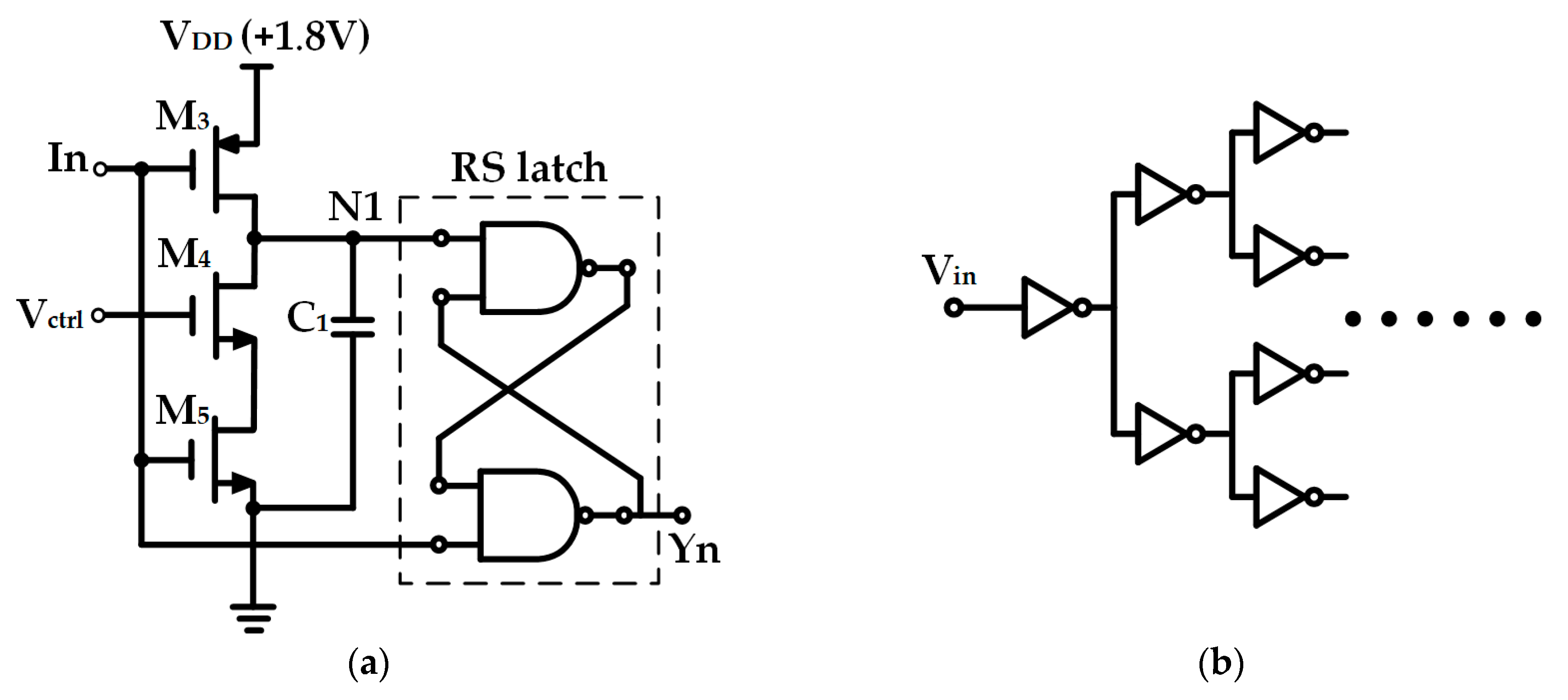

3.2. Performance Test of the Pixel Circuit

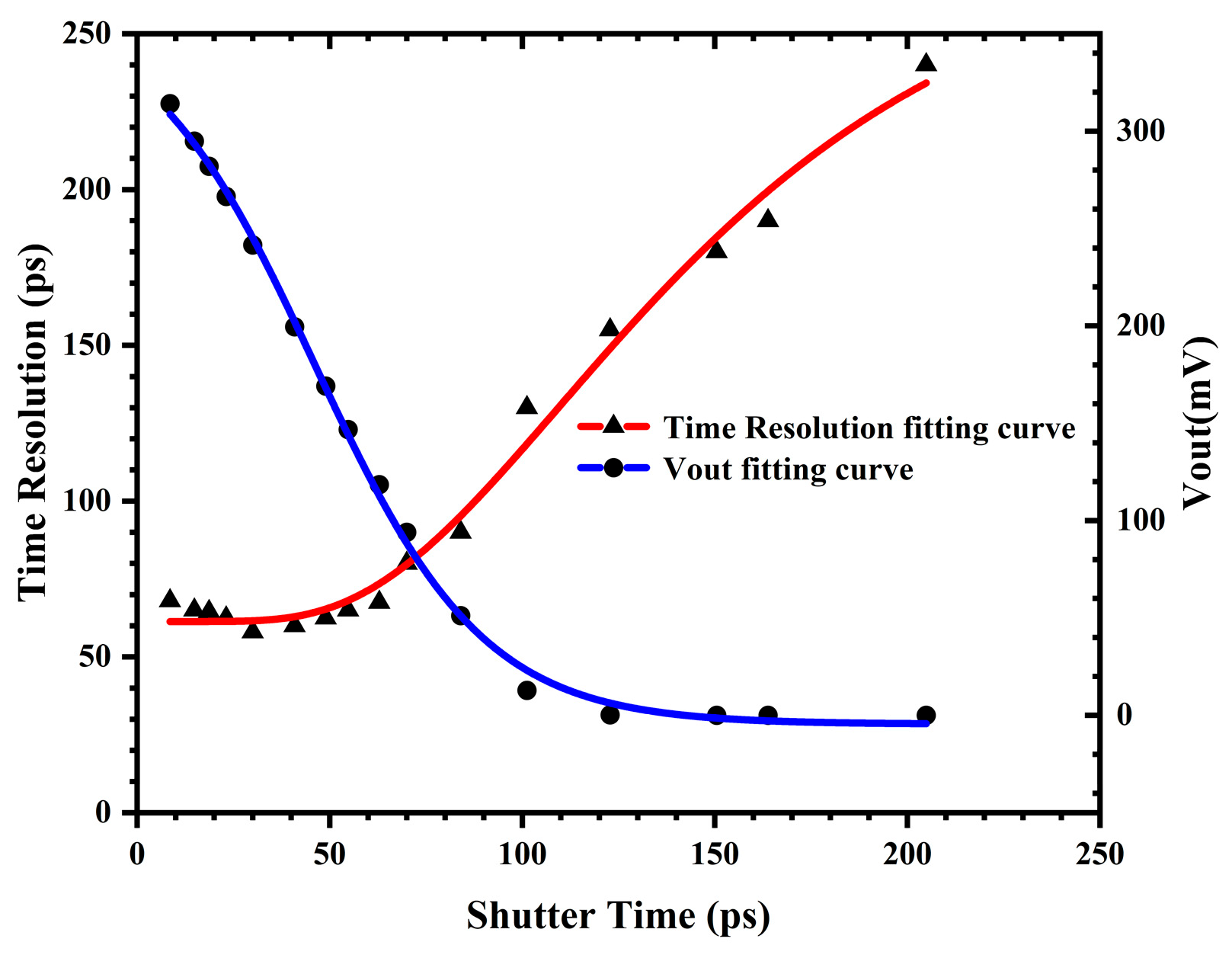

3.2.1. Analysis of the Theoretical Optimal Time Resolution Capacity of Pixel Circuit

3.2.2. Simulation of the Pixel Circuit

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Fu, W.; Hu, C.; Chen, P.; Zhou, R.; Li, L. The Development of an Electron Pulse Dilation Photomultiplier Tube Diagnostic Instrument. Sensors 2024, 24, 7497. [Google Scholar] [CrossRef] [PubMed]

- Cai, H.; Luo, Q.; Lin, K.; Deng, X.; Liu, J.; Yang, K.; Wang, D.; Chen, J.; Wang, J.; Long, J.; et al. Ultrafast pulse-dilation framing camera and its application for time-resolved X-ray diagnostic. Nucl. Sci. Tech. 2024, 35, 126. [Google Scholar] [CrossRef]

- Gao, L.; Liang, J.; Li, C.; Wang, L.V. Single-shot compressed ultrafast photography at one hundred billion frames per second. Nature 2014, 516, 74–77. [Google Scholar] [CrossRef] [PubMed]

- Nagel, S.R.; Hilsabeck, T.J.; Bell, P.M.; Bradley, D.K.; Ayers, M.J.; Barrios, M.A.; Felker, B.; Smith, R.F.; Collins, G.W.; Jones, O.S.; et al. Dilation x-ray imager a new/faster gated x-ray imager for the NIF. Rev. Sci. Instrum. 2012, 83, 2. [Google Scholar] [CrossRef] [PubMed]

- Cai, H.; Lin, K.; Luo, Q.; Wang, D.; Huang, J.; Xu, K.; Luo, L.; Liu, J. Two-Dimensional Ultrafast X-ray Imager for Inertial Confinement Fusion Diagnosis. Photonics 2022, 9, 287. [Google Scholar] [CrossRef]

- Claus, L.; Fang, L.; Kay, R.; Kimmel, M.; Long, J.; Robertson, G.; Sanchez, M.; Stahoviak, J.; Trotter, D.; Porter, J.L. An overview of the Ultra-Fast X-ray Imager (UXI) program at Sandia Labs. In Proceedings of the Target Diagnostics Physics and Engineering for Inertial Confinement Fusion IV, San Diego, CA, USA, 12–13 August 2015; pp. 177–188. [Google Scholar]

- Gao, G.; He, K.; Tian, J.; Zhang, C.; Zhang, J.; Wang, T.; Chen, S.; Jia, H.; Yuan, F.; Liang, L.; et al. Ultrafast all-optical solid-state framing camera with picosecond temporal resolution. Opt. Express 2017, 25, 8721–8729. [Google Scholar] [CrossRef] [PubMed]

- Cai, H.; Zhao, X.; Liu, J.; Xie, W.; Bai, Y.; Lei, Y.; Liao, Y.; Niu, H. Dilation framing camera with 4 ps resolution. APL Photon. 2016, 1, 9. [Google Scholar] [CrossRef]

- Yi, S.; Zhang, F.; Huang, Q.; Wei, L.; Gu, Y.; Wang, Z. High-resolution X-ray flash radiography of Ti characteristic lines with multilayer Kirkpatrick-Baez microscope at the Shenguang-II Update laser facility. High Power Laser Sci. Eng. 2021, 9, 7. [Google Scholar] [CrossRef]

- Xu, X.; Xu, J.; Mu, B.; Chen, L.; Ye, L.; Li, M.; Li, W.; Wang, X.; Zhang, X.; Wang, F. High-resolution elliptical Kirkpatrick-Baez microscope for implosion higher-mode instability diagnosis. Opt. Express 2022, 30, 26761–26773. [Google Scholar] [CrossRef] [PubMed]

- Engelhorn, K.; Hilsabeck, T.J.; Kilkenny, J.; Morris, D.; Chung, T.M.; Dymoke-Bradshaw, A.; Hares, J.D.; Bell, P.; Bradley, D.; Carpenter, A.C.; et al. Sub-nanosecond single line-of-sight (SLOS) x-ray imagers (invited). Rev. Sci. Instrum. 2018, 89, 123. [Google Scholar] [CrossRef] [PubMed]

- Nguyen, A.Q.; Dao, V.T.S.; Shimonomura, K.; Kamakura, Y.; Etoh, T.G. Crosstalk in Multi-Collection-Gate Image Sensors and its Improvement. In Proceedings of the Selected Papers from the 31st International Congress on High-Speed Imaging and Photonics, Osaka, Japan, 6–10 November 2016. [Google Scholar]

- Porter, J.L.; Looker, Q.; Claus, L. Hybrid CMOS detectors for high-speed X-ray imaging. Rev. Sci. Instrum. 2023, 94, 17. [Google Scholar] [CrossRef] [PubMed]

- Berger, R.; Rathman, D.D.; Tyrrell, B.M.; Kohler, E.J.; Rose, M.K.; Murphy, R.A.; Perry, T.S.; Robey, H.F.; Weber, F.A.; Craig, D.M.; et al. A 64x64- pixel CMOS test chip for the development of large-format ultra-high-speed snapshot imagers. IEEE J. Solid-State Circuits 2008, 43, 1940–1950. [Google Scholar] [CrossRef]

- Teruya, A.T.; Vernon, S.P.; Moody, J.D.; Hsing, W.W.; Brown, C.G.; Griffin, M.; Mead, A.S.; Tran, V. Performance of a 512 x 512 Gated CMOS Imager with a 250 ps Exposure Time. In Proceedings of the Target Diagnostics Physics and Engineering for Inertial Confinement Fusion, San Diego, CA, USA, 14 August 2012; p. 9. [Google Scholar]

- Mochizuki, F.; Kagawa, K.; Okihara, S.; Seo, M.; Zhang, B.; Takasawa, T.; Yasutomi, K.; Kawahito, S. Single-Shot 200Mfps 5x3-Aperture Compressive CMOS Imager. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 22–26 February 2015. [Google Scholar]

- Zhang, F.; Niu, H. A 75-ps Gated CMOS Image Sensor with Low Parasitic Light Sensitivity. Sensors 2016, 16, 999. [Google Scholar] [CrossRef] [PubMed]

- Nagel, S.R.; Carpenter, A.C.; Park, J.; Dayton, M.S.; Bell, P.M.; Bradley, D.K.; Funsten, B.T.; Hatch, B.W.; Heerey, S.; Hill, J.M.; et al. The dilation aided single-line-of-sight x-ray camera for the National Ignition Facility: Characterization and fielding. Rev. Sci. Instrum. 2018, 89, 125. [Google Scholar] [CrossRef] [PubMed]

- Claus, L.; England, T.; Fang, L.; Robertson, G.; Sanchez, M.; Trotter, D.; Carpenter, A.; Dayton, M.; Patel, P.; Porter, J.L. Design and characterization of an improved, 2 ns, multi-frame imager for the Ultra-Fast X-ray Imager (UXI) program at Sandia National Laboratories. In Proceedings of the Target Diagnostics Physics and Engineering for Inertial Confinement Fusion VI, San Diego, CA, USA, 7–8 August 2017; pp. 16–26. [Google Scholar]

- Looker, Q.; Colombo, A.P.; Kimmel, M.; Porter, J.L. X-ray characterization of the Icarus ultrafast x-ray imager. Rev. Sci. Instrum. 2020, 91, 043502. [Google Scholar] [CrossRef] [PubMed]

- Chen, H.; Golick, B.; Palmer, N.; Carpenter, A.; Claus, L.D.; Dayton, M.; Dean, J.; Durand, C.; Funsten, B.; Petre, R.B.; et al. Upgrade of the gated laser entrance hole imager G-LEH-2 on the National Ignition Facility. Rev. Sci. Instrum. 2021, 92, 033506. [Google Scholar] [CrossRef] [PubMed]

- Looker, Q.; Kimmel, M.; Yang, C.; Porter, J.L. Optical and x-ray characterization of the Daedalus ultrafast x-ray imager. Rev. Sci. Instrum. 2023, 94, 3505. [Google Scholar] [CrossRef] [PubMed]

- Sukegawa, S.; Umebayashi, T.; Nakajima, T.; Kawanobe, H.; Koseki, K.; Hirota, I.; Haruta, T.; Kasai, M.; Fukumoto, K.; Wakano, T.; et al. A 1/4-inch 8Mpixel Back-Illuminated Stacked CMOS Image Sensor. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers (ISSCC), San Francisco, CA, USA, 17–21 February 2013. [Google Scholar]

- Mistyuk, S. Simulation, Fabrication, and Testing of Epitaxial Germanium X-Ray Photodiodes. Ph.D. Thesis, University of California, Davis, CA, USA, 2024. [Google Scholar]

| Reference | Robert Berger [14] | Fan Zhang [17] | Looker Quinn [22] | This Work |

|---|---|---|---|---|

| Supply voltage | 1.8 V | 5 V | 5 V | 1.8 V |

| Process | 0.18-μm CMOS | 0.5-μm CMOS | 0.35-μm CMOS | 0.18-μm CMOS |

| Resolution | 64 × 64 pixels | 40 × 48 pixels | 1024 × 512 pixels | 8 × 8 pixels |

| Power consumption | 125 mW | 50 mW | - | 0.35 mW |

| Full capacity | 0.7 Me− | 1.2 Me− | 1.5 Me− | 2.3 Me− |

| Small-signal responsivity | 1.1 × 10−7 V/e− | 1.47 × 10−6 V/e− | 9.58 × 10−7 V/e− | 1.93 × 10−7 V/e− |

| Output swing | 0.8 V | 1.8 V | 1.4 V | 448 mV |

| Shortest shutter time | 200 ps | 75 ps | 1 ns | 209 ps |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Cai, H.; Xie, Z.; Ma, Y.; Xiang, L. A 209 ps Shutter-Time CMOS Image Sensor for Ultra-Fast Diagnosis. Sensors 2025, 25, 3835. https://doi.org/10.3390/s25123835

Cai H, Xie Z, Ma Y, Xiang L. A 209 ps Shutter-Time CMOS Image Sensor for Ultra-Fast Diagnosis. Sensors. 2025; 25(12):3835. https://doi.org/10.3390/s25123835

Chicago/Turabian StyleCai, Houzhi, Zhaoyang Xie, Youlin Ma, and Lijuan Xiang. 2025. "A 209 ps Shutter-Time CMOS Image Sensor for Ultra-Fast Diagnosis" Sensors 25, no. 12: 3835. https://doi.org/10.3390/s25123835

APA StyleCai, H., Xie, Z., Ma, Y., & Xiang, L. (2025). A 209 ps Shutter-Time CMOS Image Sensor for Ultra-Fast Diagnosis. Sensors, 25(12), 3835. https://doi.org/10.3390/s25123835