Abstract

SiC MOSFETs are widely employed in power converters due to their superior efficiency and reliability at high temperatures. For this reason, it is crucial to implement accurate thermal models capable of indirectly estimating the junction temperature and its fluctuations: both are caused by power losses in the device. In this framework, the evaluation of switching losses remains the most challenging task. To enable real-time monitoring of the junction temperature, this work presents the development of a virtual sensor specifically designed for SiC MOSFETs. The sensor relies on a num-analytical model (NAM), which employs only datasheet parameters and leverages electrical quantities—namely, bus voltage and current—available from sensors integrated into power converter systems. The proposed NAM is implemented in MATLAB using an iterative algorithm that accounts for the main physical phenomena involved in switching transitions. The computed energy losses are then used to thermally model the SiC MOSFETs within the PLECS environment, where a digital twin of an all-SiC board is created. Finally, the accuracy of the model is validated by comparing simulation results with experimental efficiency data obtained from a real half-bridge converter, with explicit consideration of measurement uncertainty.

1. Introduction

1.1. Motivation

Advanced modeling and simulation of electrical equipment are key issues in the development and design of high-efficiency power converters for industrial and automotive applications. The constantly growing interest in SiC-based devices is a natural result of their better merit figures compared to traditional Si-based solutions [1,2,3]. The adoption of SiC devices typically allows for a significant increase in both efficiency and power density thanks to their faster switching time and reduced conduction losses. Moreover, they can also operate at higher temperatures [4]. While on the performance side, the advantage is clear and sound, cost-wise, the adoption of SiC-based devices needs to deal with a trade-off between the final system improvements and cost. Even though the advantage on the performance side is clear and sound, the increase in power density provokes a rise in thermal stress on SiC MOSFETs, which leads to a decrease in the system MTTF (Mean Time To Failure) without appropriate monitoring of losses and device temperature. Since the junction temperature and its fluctuation are responsible for the thermal aging and failure of the transistors, it is essential to monitor this physical quantity. A virtual sensor, especially, allows for the estimation of the junction temperature both online under a real operating condition and offline if the converter/inverter behavior and load profile are known beforehand, avoiding the need for thermocouples. These sensors are also less reliable in high-end applications with bare-die components, since they cannot be placed on the devices, but close to them. Because the temperature depends on the thermal chain between the device and the ambient and on the power dissipated, a proper estimation of the transistor losses represents the first and most important step of a lifetime evaluation. Several lifetime models and procedures already exist in the literature for traditional IGBT devices [5,6,7]. Similarly, some were developed for SiC MOSFETs: the authors of [8] presented a great overview of the state of the art. Considering also that in high-power applications, an error of 1 % on the efficiency estimation could significantly impact the heat sink design and the online evaluation of the thermal status, the importance of estimating power loss in a SiC MOSFET becomes evident.

1.2. Overview of the Topic

In this framework, the evaluation of switching losses remains the most challenging task. Therefore, in recent years, several authors have put their efforts into the development of a model that could estimate them [9,10,11,12,13,14,15,16,17,18,19,20,21,22,23,24]. An old and well-established model such as [9] is very easy to understand and implement; however, it lacks precision due to the strong approximations made on the gate drain capacitance and on constant rise and fall times. Others such as refs. [10,11,12] are very complete but require preliminary measurements to derive the dynamic characteristics. Refs. [11,12] both take into account the short-channel and the drain-induced lowering barrier (DIBL) effects, but they require a single-pulse test to obtain the saturation characteristic. Even though this approach is formally correct, it requires a dedicated setup for parameter extraction and additional time, which may be very impactful for several companies approaching a SiC power converter design. The authors of [13] made great efforts in the analytical derivation of turn-on losses. However, even though turn-on losses are predominant, turn-off losses are not negligible. Other papers, such as [14], focused on the influence of single parameters on switching losses, charge and discharge in this case, which is relevant for and computation but introduces a further level of complexity, which is secondary in the total computation. Some numerical analytical models based on datasheet parameters already exist in the literature [15,16]. They either are mathematically challenging [15] or make strong assumptions on the equivalent transconductance and capacitance [16]. In both cases, it is not clear how to estimate the parasitic inductances without carrying out any measurement. These models work well with discrete SiC devices in very standard packages; in this way, these lumped parameters can be assumed from similar part numbers, but for bare-die components or non-standard packages, additional measures would be mandatory. The authors of [17] focused on reverse-recovery estimation, but their method also requires preliminary measurements. The same goes for [18], who adapted the model for a specific condition (quasi-zero turn-off losses). Moreover, their procedure also demands previous measurements. Ref. [19] made strong assumptions on temperature independency and also required the computation of some dynamic characteristics. Refs. [10,11,12,13,14,15,16,17,18,19] are all num-analytical models (NAMs), such as the one presented in this work; in addition, full-analytical models (FAMs) exist [20,21,22,23,24]. Refs. [20,21,22] studied linearized waveforms and, especially the first two, also made an assumption of constant transconductance. The most complete FAM in the literature is the one derived by Hu and Biela in [23,24]. However, its mathematical complexity is extremely challenging, and even though they provide good accuracy, they make step-wise approximations and a temperature independency assumption of the and losses. These assumptions become relevant as the switching frequency increases. In this paper, a new NAM model is therefore presented, entirely based on datasheet parameters, to estimate the switching losses of an application with all-SiC, SiC MOSFETs, and SiC Schottky diodes in anti-parallel. This model is based on an iterative method, which can be solved in any commonly used language: C++, MATLAB, Python, etc. This model considers all the possible information provided by the manufacturer: non-linear capacitance, channel modulation mode, and dependency of and on the load current. Nevertheless, this approach aims to be easily implemented by any company or research group, following the trend of a more efficient and widespread electric vehicle drive design and of the development of renewable energy systems with better performances. Moreover, none of the aforementioned models were validated considering the efficiency computation and the measurement uncertainty, which makes this work innovative in the literature perspective.

1.3. Article Structure

In Section 2, the SiC MOSFET switching loss model is explained in comparison with a simplified reference model [9], an analytical model of similar complexity [16], and a FAM model [24]. At the end of the section, its universality is discussed. Proceeding to Section 3, the setup for the experiments is presented. In Section 4, a digression on the expanded uncertainty evaluation is carried out: this is a needed premise to compare the measured efficiency with the one obtained in the simulation. In the same section, the results are summarized and compared with the aforementioned models. Finally, some conclusions and future development hints are given in Section 5 and Section 6.

2. SiC MOSFET Switching Loss Evaluation

2.1. Introduction to the Analysis

In this section, after presenting the well-known half-bridge architecture and its main parasitic components, a brief overview of the state of the art of SiC switching loss estimation is presented. Then, the proposed model is detailed and shown in comparison with three existing ones: the simplified reference model found in [9], a NAM of similar complexity in [16], and a FAM in [24]. Afterwards, a paragraph is dedicated to the universality of the model, and at the end of the section, a subsection addresses the junction temperature estimation based on the proposed model.

2.2. Half-Bridge Architecture and Lumped Parasitic Parameters

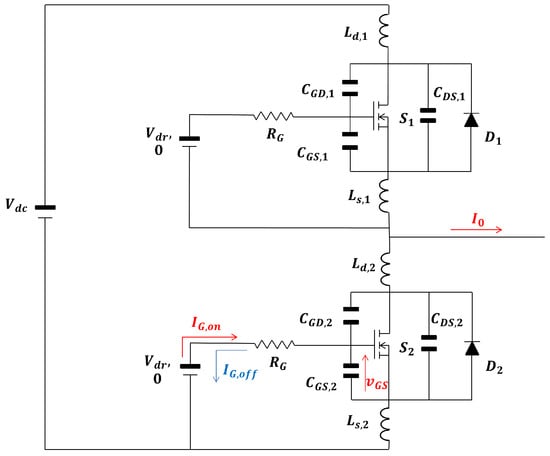

The architecture under study consists of a half-bridge with two SiC MOSFETs and two SiC Schottky diodes in anti-parallel. The same architecture is tested in Section 3. The electric model including all parasitic components is drawn in Figure 1 and is common throughout the section. Regarding the parameters, is the sum of the external and internal gate resistance; further, in this section, , the total gate resistance during turn-on, and , the total gate resistance during turn-off, are distinguished; and are the parasitic inductance of the source and drain, respectively; , , and are the capacitance of the gate source, gate drain, and drain source, respectively; is the DC bus supply voltage; and is the high-level voltage gate supply, with off-state 0 V applied to the control pins.

Figure 1.

SiC MOSFET electric model with parasitic inductance.

2.3. Overview of SiC Switching Loss Models

As mentioned in the Introduction, several authors tried to model switching losses in recent years; some of them also proved good compliance with the experimental tests, which had always consisted of a double-pulse test (DPT). However, each of them lacks either accuracy or results in excessive complexity. Moreover, most of them require some preliminary tests for parameter extraction. The authors of this work, instead, believe in ease of application of the model with the best possible accuracy. Here, a brief summary of each model problem is provided, and the synthesis can be found in Table 1. Ref. [9] is better detailed later on in this section, since it will be used as one of the benchmarks in Section 4: it consists of a well-established but very raw model. is approximated as a step function and current rise and fall times are considered independent from the load current. Ref. [10] presented a good summary of several factors influencing the switching loss mechanism; however, it demands the measurement of dynamic characteristics of the MOSFET parasitic capacitances. Moreover, several variables, which are changed on purpose in the analysis, are normally parameters of the already existing power board, such as the loop inductance . Other parameters are difficult to estimate: the parasitic inductances and cannot be easily computed; usually a DPT is required or a very accurate LTSpice model, provided by the manufacturer. In most cases, this is not possible without building a dedicated setup. Furthermore, an error of on the total energy losses is significant: especially at high switching frequencies, it leads to significant deviation on the efficiency estimation. Ref. [11] shows better accuracy but maintains the same problem of the dynamic characterization of , the gate drain charge, and of the transfer characteristic of the device, resulting in time and practical effort. Ref. [12] is very accurate but presents the same problem of previous characterization. In [13], great insights on the energy turn-on loss computation are given, but even if they represent the predominant part, the turn-off losses are not negligible. On the contrary, Ref. [14] focuses on the charge and discharge of the output capacitance , which is a real physical phenomenon but does not allow for better estimation of the total losses, since the energy absorbed in one switching transient, , is then returned in the other: aiming to estimate the efficiency; this sophistication can be neglected. The authors of [15,16], which is detailed later on, provided a NAM based on datasheet parameters, even though the estimation of and and its difficulty are not well delved into. The first one showed a great accuracy but high mathematically complexity. Ref. [16] is lacking a bit in accuracy, even though it is more understandable. Ref. [17], on the contrary, requires preliminary tests to extract the lumped parameters, even though it is accurate. Ref. [18] gave interesting insights into the switching losses in the quasi-ZTL (zero turn-off losses) condition but remained very specific and needs preliminary tests for the dynamic curve extraction. The exact same problem can be found in [19], where the authors made an assumption of temperature independency, as well. Full analytical models such as [20,21,22] supposed linearized waveforms. These assumptions, added to a constant transconductance supposition, allow for faster evaluation but reduce the models’ accuracy. Finally, Hu and Biela developed a FAM in [23] and refined it in [24], which is quite accurate and based on datasheet parameters, even though it makes strong assumptions such as temperature independency and equivalent capacitance approximation. To reduce the computational effort, which is a goal for models of this kind, it solves all the differential equations in a closed form, leading to a very challenging and almost prohibitive complexity. Also, this model is briefly described later on in this section.

Table 1.

Overview of the state-of-the-art switching loss models.

2.4. Simplified Reference Model

First, the simple model proposed by [9], based on datasheet parameters, is taken into account. This model gives a rough estimation of switching losses: in fact, it assumes a linear approximation for both voltage and current during turn-on and turn-off transients. During the current rise time , the gate source voltage increases linearly from the threshold voltage , to the Miller plateau voltage , which is considered constant and equal to the typical value reported in the datasheet. The same happens during in the turn-off transient: decreases linearly from to . The model assumes that both the rising time of the current and the falling time of the current are constant and equal to their typical values, which can be found in the datasheet. The voltage fall time, during the turn-on transient is the time required to discharge . The discharging process starts when the drain source voltage equals the supply voltage and ends when the MOSFET is conducting, i.e., when reaches the drain source voltage of the MOSFET in the on-state , where is the device on resistance. At the beginning of , the voltage across is and, at the end, is ; therefore, it is possible to consider the discharging of the capacitance at the constant current provided by the gate driver. This statement is not an assumption, since is clamped to throughout the period of time. Time could be estimated as in (1).

where is the voltage applied by the gate driver. One of the main issues is the value assumed by or , reverse transfer capacitance. Since this capacitance is dependent on the drain source voltage , the authors of [9] suggest a zero-hold interpolation based on two points: the first one at and the second one at for the - curve that is found in the datasheet. A falling time is correlated with both values. The mean value between the two falling times is . Therefore, the switch-on losses can be calculated as the area of a triangle, as can be seen in (2).

where is the load current. A very similar approach is employed to evaluate the voltage rise time and, therefore, to calculate the turn-off losses , with two differences: the voltage applied by the gate driver is 0 V and the total gate resistance is generally different from .

As can be seen in Section 4, the Infineon model leads to a significant overestimation of the switching losses. Although very simple, it lacks of precision. The following subsection analyzes the num-analytical model of Christen and Biela [16] in brief.

2.5. Existing Analytical Model of Similar Complexity

In this subsection, the steps employed by the authors of [16] to evaluate are briefly resumed; are calculated in a similar way. Firstly, the input capacitance , the output capacitance , and the reverse-transfer capacitance are considered fixed at an equivalent value, calculated through the integral of each respective curve. The capacitances are then derived from algebraic operations of the three above. From , an equivalent value is derived for the charge stored in , . Because plays an important role in the voltage switching transients, it is believed that this approximation is the main cause of the deviation with respect to the experimental results, which can be appreciated in Section 4. Then, a second-order equation, if parasitic inductances and are considered, or a first-order equation, if not, is solved through a numerical method, for example, the Newton–Raphson method, in order to obtain a value for . is the current needed to charge during the current rise. A value for the transconductance is then found [25].

Consider that is negative during turn-on and positive during turn-off, which means that the actual current flowing in the channel during the voltage drop is greater than the load current and vice versa during the voltage rise [26]. Thus, the current rise time and the voltage fall time are calculated through (3).

Finally, if the reverse-recovery phenomenon is neglected, is calculated as in (4). A similar approach is followed for losses.

where if parasitic inductances are considered; here, . This model is implemented in MATLAB, similarly to the one proposed in this paper.

2.6. Fully Analytical Model

A merit of a fully analytical model is its computational time, which is reduced significantly, usually at the expense of its accuracy. However, very recently, a fast and accurate FAM was developed by Hu and Biela [23,24] at the expense of its complexity. Solving the equations of the switching transients in closed form is mathematically challenging, and even if the algorithm is provided, the implementation remains difficult Moreover, its performances are inferior, even if slightly, to the proposed model. Ref. [24] divides the turn-on and turn-off switching intervals into six parts, and for each, it computes a contribution to the total loss. The model was always implemented in MATLAB, as proposed in the next section.

2.7. Proposed Analytical Model

2.7.1. Overview and Assumptions of the Proposed Analytical Model

This section delves into the proposed model, starting from its assumptions, which are only the necessary hypotheses to implement a fully datasheet-based model. Then, its merits will be manifested. Here is a list of the three assumptions.

- Parasitic inductances and are neglected. Because bare-die components are employed, typical inductance values of a standard package cannot be used. The overall inductance of the half-bridge could be estimated, but its distribution in every parasitic inductance is rather challenging. Considering that the PCB layout is achieved while trying to minimize these inductances as much as possible and that the highest switching frequency at which the half-bridge is tested is 80 kHz, it is assumed that they do not play a significant role.

- Reverse-recovery losses are neglected. SiC Schottky diodes are placed in anti-parallel to the SiC MOSFETs, and since they manifest a very low reverse-recovery peak current , the assumption is acceptable. The omission of reverse-recovery losses is compelling if SiC Schottky diodes are employed in anti-parallel to SiC MOSFETs. If, instead, body diodes of the SiC MOSFET are used, these losses should be considered. In this case, refs. [16,17] propose an effective way to compute the reverse-recovery losses. Particularly, in [16], a set of formulae is derived from the physical model presented in [27], which could be numerically solved with the Newton–Raphson method.

- Drain-induced Barrier Lowering (DIBL) and the short channel effect are neglected. In the switching process, especially during current rise or fall, depending on which transient, turn-on or turn-off, is considered, the MOSFET operates in the saturation region. During this period of time, when powered by high DC bus voltages, the device experiences the DIBL effect, resulting in an increase in the channel current for a given and in a reduction in the threshold voltage . The complete expression of the channel current would be described by (5), as stated in [12]. With respect to the - characteristic provided by the manufacturers at low and fixed , the real characteristic at higher bus voltages is shifted to the left and expresses a higher slope. Thus, the DIBL effect neglect implies an overestimation of the losses during current rise and fall. However, the estimation of requires an experimental characterization of the device, especially a single-pulse test circuit [11], which would be out of the scope of this paper. The initial estimation of as described in [28] is not possible for most of the SiC MOSFET part numbers, and the relation between and cannot be derived from the datasheet. Therefore, the effect is neglected.where is the channel current, is the transconductance coefficient, and is the short-channel coefficient.

Before proceeding, it should be clarified that the channel current is considered equal to the load current during and : . The actual current flowing in the channel during turn-on, when the voltage drops, is greater than the load current because an additional current must be applied to discharge . The opposite happens during turn-off. As explained in [26], the actual losses are greater than the ones measured throughout the use of a voltage and a current probe; in contrast, the measured losses are lower than the measured ones. However, if the aim is to evaluate the efficiency, this deviation is no longer significant since is stored but then completely released throughout the switching period, which allows one to simplify the model.

Apart from the aforementioned assumptions, the model aims to maintain the highest possible accuracy, taking into account the main aspects of the switching process. Differently from [10,11,12,13,14,15,17], it does not require prior measurements. Similarly to [16], it employs an iterative method, and consequently, it avoids the direct resolution of differential equations. However, a step-by-step with feedback updating of the main variables is chosen instead of making strong assumptions on the capacitances and on the transfer characteristic. This allows for obtaining, on average, a better accuracy than that in [24], while maintaining good understandability, avoiding closed-form expressions. The proposed model chooses to compute the main switching times , , , and with a step-by-step algorithm. A merit of the model is also to be efficiency-oriented, since it omits the calculation of .

2.7.2. Calculation

About the switching losses, two contributions are distinguished: one due to the current raising and the other to the voltage falling. These processes are considered separately, as in the simplified model. Before the current rises, when , the channel current is negligible and therefore the power loss contribution of this time period. After the voltage drop goes from to but , which is very close to zero, this contribution to power loss is also negligible. Since during , it is true that , the condition of channel modulation is considered true. The same formula explained in [25] and employed in [16] can be used.

where and x are three coefficients, which can be found from a fitting of the curve that is found in the datasheet. For the tested part number, these values can be extracted for 25 °C and 150 °C.

varies during , and defines the trend of , which is equal to during this time period. The two main issues in the evaluation of the switching loss contribution of this time period are the non-linear trend of during and the dependence of by the drain current itself. These difficulties in the power loss evaluation are solved by employing a feedback algorithm. After defining a time-step ns, is initialized and is derived from (6) at load current . The expression is also defined by hypothesizing that changes linearly during .

where is the load-considered current; , x, and are constant and assume different values if °C or °C; and is initialized at the lowest available value based on the datasheet curve. A good amount of points can be extracted from the curve in the datasheet, and then, a zero-hold interpolation is considered for this curve, i.e., the value of is constant in between the two following samples. The number of points, if considerable, increases the precision of the model: in this case, 100 are taken in correspondence with the 100 possible load currents that were considered to build the model (from 0 A to 50 A with a step of 0.5 A). After that, a while cycle starts and continues until either or becomes false. Inside the cycle, if the new value of surpasses the mean value of between one sample and the following one, both and are updated (9). At each iteration of the while cycle, whether the above mentioned inequality is true or not, and are calculated: see (10).

where i stands for the ith iteration. The trend of or during this time is not linear; therefore, a numerical integration method needs to be adopted to evaluate the switching losses: the trapezoidal rule, (11), is employed. The time interval is always ns. The voltage across the MOSFET during does not change and remains equal to .

where corresponds to the effective rise time. In this way, the non-linear trend of the channel current is considered. The other contribution to the switch-on losses is due to the voltage falling. To estimate the voltage falling time , points are extracted from the curve that is found in the datasheet. A curve fitting could be used, as in [17], but a zero-hold interpolation of the extracted points is simple and effective. The number of points should be significant, and the sampling rate should be higher, near the “knee” of the curve; in this case, 68 values are taken. Since changes significantly, along with , a weighted average value is calculated for . The following indexes are defined (13):

where is the sample of the reverse-transfer capacitance curve. After defining the extremes, is initialized, considering that is discharged at a constant current (14), and then, is initialized as well (15).

where assumes the value calculated in (8). At each iteration of the while cycle, is updated and a variable c is increased by one unit to count the integer number of , during which is considered constant to the sample value (16). Whenever , k is decreased by one unit and c is reset to zero: this operation can occur until (17). Saving the value of for each sample, the weighted average value of can be calculated (18) at the end of the cycle, when .

Assuming the linear falling of the voltage during this time, (19) represents the other contribution to the switch-on losses.

becomes the algebraic sum of the two contributes.

2.7.3. Calculation

The losses also consists of two contributes: , due to the non-instantaneous voltage rising, and , due to the current falling. The method employed to evaluate is the same as that for , but the equations in (14)–(18) must be re-arranged. The charging current for becomes (21) if a zero voltage is applied by the gate driver. k is increased until , and the while cycle stop condition is .

It follows that can be evaluated as in (26).

In addition to , varies along with ; therefore, a step-by-step method is used similarly to that for . In this case, has already been calculated during the evaluation of losses. In (27), the initialization of the variables is shown.

A while cycle is always considered to continue until becomes false or > becomes false. Inside the cycle, if the new value of is lower than the mean value between one sample of and the following one, and are updated. Firstly, is updated to the next sampled value, and then, is evaluated again. At each iteration of the while cycle, whether the inequality mentioned above is true or not, the values are updated similarly to that for the switch-on losses (10). Subsequently, has the following expression.

losses are then the sum of two contributions (29):

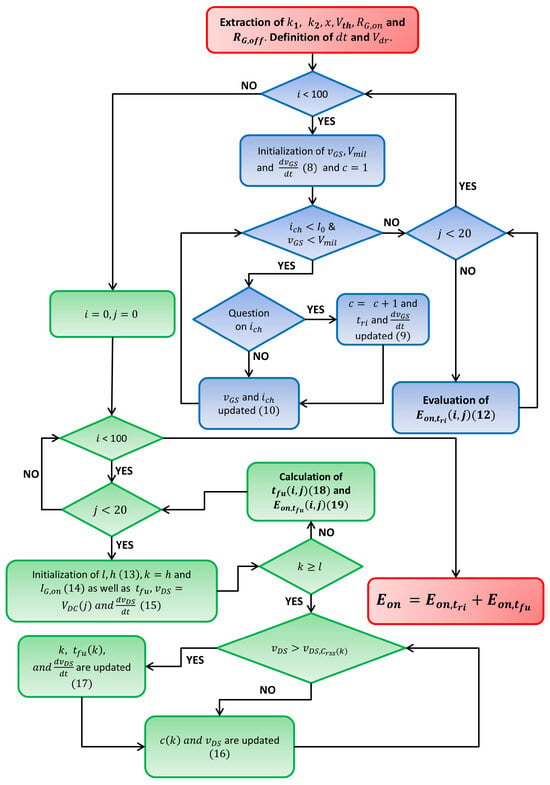

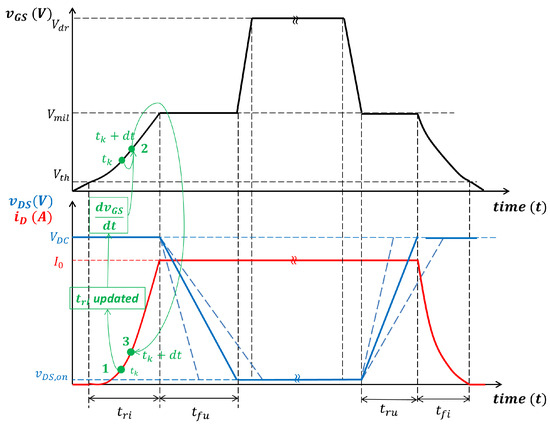

The algorithm used for the calculation of the losses is summarized in Figure 2 and can be implemented in MATLAB R2024a. In this figure, i is the index of the current values = 0, 0.5 A, 1.0 A, 1.5 A, …, 50 A, and j is the index of supply voltage values = 0 V, 10 V, 20 V, …, 100 V, 200 V, …, 1000 V. That is very similar to the one used to evaluate . Consider that it is implemented for °C and °C. In Figure 3, the algorithm is explained graphically and the assumed switching transients are shown for the gate source voltage and the drain source voltage and current. Once the and matrices have been evaluated, they can be uploaded as a look-up table in PLECS to evaluate power losses due to the switching process in several simulating conditions [29]. The efficiency results over the half-bridge architecture are shown in comparison with the experimental results; see Section 4.

Figure 2.

Flow chart of the algorithm used to evaluate .

Figure 3.

Switching transients assumed for the algorithm implementation.

2.7.4. Universality and Further Discussions on the Proposed Model

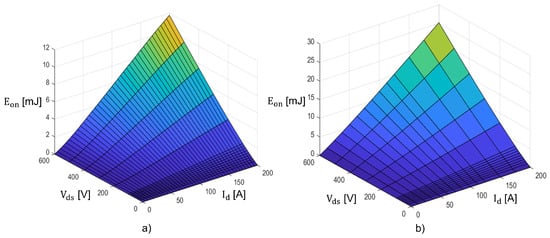

The proposed model is meant to be applied to any SiC MOSFET since it is not dependent on the individual part number technology: all the equations in the previous subsection do not include any reference to a specific topology. To further underline that, the algorithm was applied to two 2nd Gen. CoolSiC: IMW65R007M2H [30] and IMW65R020M2H [31]. These have the same blocking voltage, technology, and package but very different switching losses and : 7 m and 20 m, respectively. As shown in Figure 4, the algorithm results are in agreement with the information provided by the manufacturer. Since it implies an iterative method, any development environment in C or C++ can be employed as a substitution of MATLAB; therefore, its applicability is also notable. In this paper, an application with all-SiC board, SiC MOSFETs, and SiC Schottky diodes in anti-parallel was employed. If MOSFET body diodes were employed, reverse recovery should be considered: in this case, it is sufficient to add the calculations found in [16] or [17] at the end of the algorithm.

Figure 4.

Comparison of the losses at °C between (a) IMW65R020M2H and (b) IMW65R007M2H.

2.7.5. Virtual Junction Temperature Estimation

The estimation of the junction temperature is the first and most important step in evaluating the thermal stress and lifetime of the SiC MOSFET. If is the sum of the switching and conduction losses of a single device under a certain operating condition, it is sufficient to employ the turn-on and turn-off losses as look-up tables in the micro controller to derive the junction temperature of the device. The process implicitly requires knowledge of the thermal chain between the junction and the environment. The expression of is given in (30).

where and are the thermal impedance from junction to heat sink and from heat sink to ambient. The first one is generally expressed as , but only if the device comes in a package. Otherwise, if a bare-die part number is chosen in the application, the two terms collapse into one. can be derived from the part number datasheet curve for the evaluation of or in the case where a bare-die component [32] can be used. Each thermal impedance can be represented as a foster thermal RC network, thus the explanation of the temperature dependency of these quantities. changes along with the operating condition and ; should be continuously updated; and therefore, they are also time-dependent. If an operating condition is maintained until a stable temperature is reached, only the thermal resistances are significant and the expression in (30) transforms into (31).

The switching loss model calculates and from the load current and the bus voltage; thus, a commercial current sensor like the coreless TLI4971 [33], from Infineon, employed for the board tested in this work can be used. The bus voltage can instead be measured with a simple voltage divider. Since these physical quantities are important for every electric power drive unit or converter connected to the grid, the implementation of the virtual temperature sensor based on the proposed NAM model is straightforward and requires sustainable efforts.

3. Experimental Setup

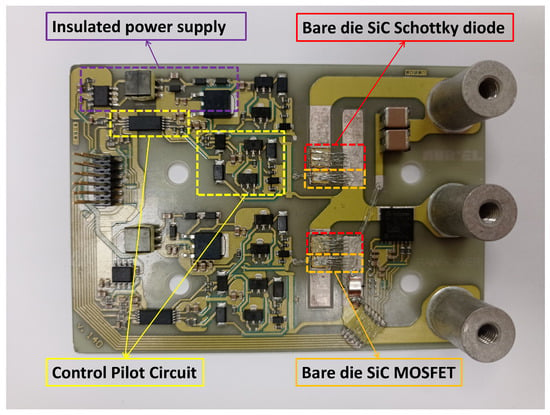

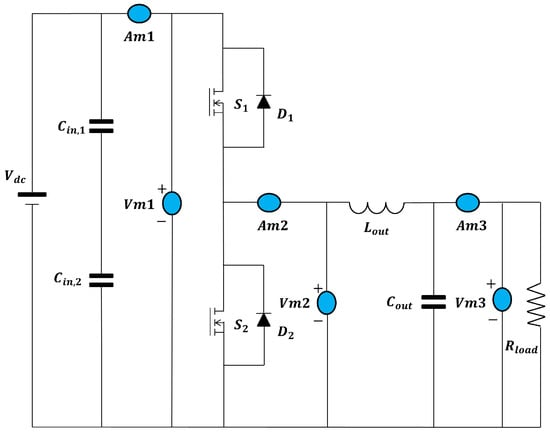

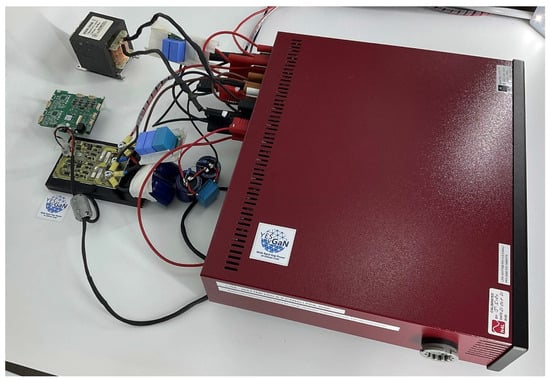

The conversion unit has been realized as a PCB, produced over a ceramic support that also contains the insulated power supply for the Control Pilot Circuit. The components are two SiC MOSFETs, s4101 [34], and two SiC Schottky diodes, s6305 [35], placed in anti-parallel; see Figure 5. The PCB has been assembled over an aluminum heat sink. A STM32F765II micro controller by STMicroelectronics, Geneva, Switzerland has been used to pilot the driver and select both the work frequency and duty cycle. The input filter consists of two film capacitors, one of 56 nF and one of 47 nF, directly placed in parallel to the DC supply voltage source. In addition, three film capacitors (two of 56 nF and one of µF) are placed in parallel with three electrolytic capacitors of 470 µF between ’+’ and ’−’ of the half-bridge. The DC power supply provides constant voltage to the half-bridge: experiments are carried out at = 400 V, 450 V and 500 V; the LC output filter consists of a ferrite core inductor of 1.2 mH and a group of three capacitors, one ceramic and two electrolytic of µF and 470 µF, respectively. The resistive load is the parallel of two 47 resistances. Voltages, currents, and powers are acquired after the bulk input filter at the input and before and after the LC filter at the output with a PPA 3500 power analyzer, manufactured by N4l (Loughborough, UK), in order to measure the converter efficiency before and after the output filter: both measures are needed to compute the filter AC losses. The wiring has been made with short cables to enhance impedance matching and reduce noise during acquisition. The wiring schematic is shown in Figure 6. In Figure 7, the entire measurement setup is shown, apart from the resistive load, which consists of two 47 resistances placed in parallel. The results of the experiments take into account the expanded uncertainty, and they are shown in Section 4.

Figure 5.

All-SiC half-bridge module.

Figure 6.

Wiring diagram.

Figure 7.

Measurement setup.

4. Comparison with the Experiments

In order to validate the analytical model for switching loss calculation, the measurement uncertainty is evaluated for several operating conditions. The aim of this calculation is to define a proper way to compare simulations and experiments. Specifically, efficiency estimation is considered competent if the simulation result is included between the range defined by the expanded uncertainty around the mean measured efficiency. Therefore, a series of 11 measurements is conducted on the half-bridge module. Each of these measurements consists of 10 samples, where the RMS voltage, the RMS current, the power in the three channels, and the frequency only in the second channel to which the LC filter is connected are acquired. This procedure is repeated for the duty cycles 0.2, 0.3, 0.4, 0.5, and 0.7, as well as for three switching frequencies: 40, 60 and 80 kHz. In this way, for each simulation result, there is a respective experimental range. It is believed that a proper estimation of the real unknown value, or the center of the range, is represented by the mean value over the 11 runs of the arithmetic mean above each of the 10 samples. Then, it is possible to express the A-type uncertainty or the repeatability deviation as in (32), following the guideline in [36].

where n equals 11, the number of runs; is the mean efficiency among the 10 samples of the run; j is the duty cycle index; f is the switching frequency index; and is the mean value of the efficiency over the 11 sets of measurements for a specific duty cycle and switching frequency. The computation of the B-type uncertainty, instead, depends on the measurement instrument. Since the PPA 3500 power analyzer is used for the measurements, the authors refer to the user manual [37] to define this bias. For both input and output power, the accuracy of the power measurement is expressed by (33).

where and are the voltage and ampere range of the instruments and is the measured power, which can be either substituted with or . represents the maximum deviation in from the mean measured power. is the power factor, which can be simply evaluated by dividing the measured power by the product of the input voltage and the input current, and is the switching frequency expressed in kHz, 40, 60, or 80. Once the maximum deviations, and , are found, they are then put together to find the B-type uncertainty for the measured output efficiency; see (34). The reason for is the assumption of a uniform distribution of the systematic error.

The compound uncertainty is considered the square root of the two components squared (35). Finally, the expanded uncertainty can be defined with a level of confidence of , therefore with a coverage factor ; see (36).

Applying these formulae, it is possible to find range values around the mean efficiency for every duty cycle and switching frequency, which allows for comparing the simulation results with those of the measurements tests.

The uncertainty range is defined in (37), and it varies under different test conditions.

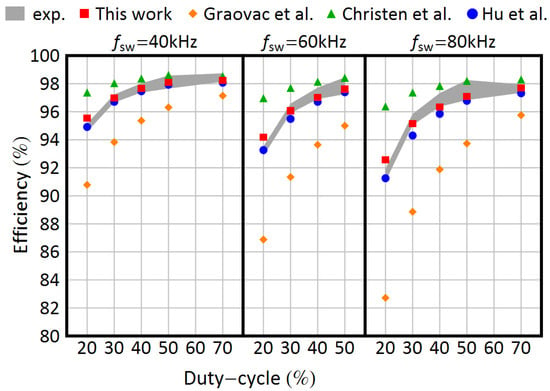

As shown in Table 2, Table 3 and Table 4, the simulation results are consistent with the experimental tests. The efficiencies estimated throughout PLECS show great compliance with the measurements at 40, 60, and 80 kHz. To compare this work with the state of the art, the authors investigated three additional models. The first is the old simplified Infineon model [9]; the second is a NAM model developed by Christen and Biela [16]; and the last is a FAM model, initially developed in [23] and then refined in [24] by Hu and Biela. These, similarly to the one presented in this work, are based on datasheet parameters. As stated at the beginning of this work, other authors introduced further levels of sophistication at the expense of carrying out some preliminary measurements. Since the proposed model is entirely based on the information provided by the manufacturers, a comparison with those would be beyond the scope of this paper. To develop the reference models, first, a MATLAB script was built; then, the resultant losses were uploaded in the thermal description of the device in PLECS; and as a last step, simulations were carried out. Except for the algorithm, the same procedure employed in this work was also applied to the state-of-the-art models. To make a comparison between the proposed model and the existing ones, four KPIs were used. Each KPI should be intended per switching frequency (Table 2, Table 3 and Table 4).

Table 2.

Efficiency comparisons at 40 kHz.

Table 3.

Efficiency comparisons at 60 kHz.

Table 4.

Efficiency Comparisons at 80 kHz.

- The number of simulation results , which lie in the uncertainty range defined around the measured efficiency.

- The mean absolute error , which represents the average displacement with respect to the measured value (38).

- The mean absolute percentage error , which is the unsigned average displacement normalized over the measured value (39). This error suggests the average displacement with respect to the test itself.

- The Modified Mean Absolute Percentage Error (40) is a well-known relative measure of the forecasting accuracy [38].

Figure 8.

Comparison among experimental and simulation results. The filled area represents the experimental results, including measurement uncertainty. Simulation results are reported for the model proposed in this work (filled rectangle) and those proposed in [9] (filled diamond), in [16] (filled triangle) and in [24] (filled circle).

5. Conclusions

SiC devices enable higher efficiency and power density due to faster switching and lower conduction losses, as well as operation at elevated temperatures. A comprehensive loss model supports the development of online virtual sensors for indirect efficiency and junction temperature monitoring. As power density increases, thermal stress on MOSFETs grows, which without proper loss and device status monitoring, reduces system MTTF. This paper proposes an effective analytical model to estimate SiC MOSFET switching losses, based exclusively on information derived from datasheets. The model is kept as simple as possible by neglecting some secondary effects on total switching losses, such as the charging and discharging of the output capacitance , which is a useful approximation and does not hinder its applicability in the power electronics industry. Additional assumptions regarding parasitic inductances and the short-channel effect are made to avoid preliminary and time-consuming measurements for parameter extraction. The reverse-recovery approximation applies specifically to the case studied in this work, although this contribution can be easily integrated if needed. Despite these simplifications, the model proved to be consistent with experimental tests and outperformed state-of-the-art models across all selected KPIs. A maximum MMAPE of 0.51 % was recorded at 80 kHz. The accuracy of the model is validated by the experimental results presented in Section 4, which also account for measurement uncertainty. The model demonstrates high versatility, as it can be applied to any SiC MOSFET part number for all-SiC applications and can be easily adapted to lower-performance drives without SiC Schottky diodes. Since the algorithm can run in both C/C++ environments and MATLAB scripts, its implementation for a virtual sensor or online efficiency measurements is also straightforward.

6. Future Developments

As a further development, the authors aim to implement the model for the calculation of efficiency and temperature in real time under various load conditions in a typical electric drive application. These tests will also prove the effectiveness of the proposed model in estimating junction temperature and allow for a proper lifetime evaluation, which will be carried out in the next work.

Author Contributions

Conceptualization, C.B. and M.V.; methodology, C.B., M.V., and A.C.; software, M.V.; validation, C.B. and M.V.; formal analysis, A.C.; investigation, C.B. and M.V.; resources, C.B. and M.V.; data curation, C.B. and M.V.; writing—original draft preparation, M.V.; writing—review and editing, C.B., A.C., and G.F.; visualization, C.B., M.V., and A.C.; supervision, G.F.; project administration, C.B.; funding acquisition, C.B. and G.F. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by ECSEL joint undertaking (JU) under grant agreement No 101007229. The JU receives support from the European Union’s Horizon 2020 research and innovation program in Germany, France, Belgium, Austria, Sweden, Spain, and Italy. This study is also financed by European Union-NextgenerationEU, PCI2021-121970/AEI/10.13039/501100011033.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

All data and additional information about the experimental setup and the code can be provided under requirement.

Acknowledgments

The authors thank the Raw Power Srl team as well as Aurel Spa, which produced the hardware prototypes.

Conflicts of Interest

The authors declare no conflicts of interest.

Abbreviations

The following abbreviations are used in this manuscript:

| NAM | Num-analytical model |

| FAM | Full analytical model |

| Drain source capacitance | |

| Gate drain capacitance | |

| Gate source capacitance | |

| Input capacitance | |

| Output capacitance | |

| Equivalent output capacitance | |

| Algorithm discrete time-step | |

| Turn-off losses | |

| Falling current contribution to the losses | |

| Rising voltage contribution to the losses | |

| Turn-on losses | |

| Rising current contribution to the losses | |

| Falling voltage contribution to the losses | |

| MOSFET switching frequency | |

| MOSFET channel transconductance | |

| Load current | |

| MOSFET channel current | |

| Drain current | |

| Gate turn-on current during Miller’s plateau | |

| Gate turn-off current during Miller’s plateau | |

| Current through the output capacitance | |

| Reverse-recovery current | |

| Drain parasitic inductance | |

| Source parasitic inductance | |

| Equivalent output charge capacitance | |

| Turn-on gate resistance | |

| Turn-off gate resistance | |

| MOSFET on-conduction resistance | |

| Silicon carbide | |

| Current fall time | |

| Voltage fall time | |

| Junction temperature | |

| Current rise time | |

| Voltage rise time | |

| DC supply voltage | |

| Gate driver supply voltage | |

| Drain source voltage | |

| MOSFET drain source voltage drop during conduction | |

| Miller’s plateau voltage | |

| MOSFET threshold voltage | |

| Expanded uncertainty | |

| Estimated efficiency | |

| Mean measured efficiency |

References

- Mantooth, H.A.; Glover, M.D.; Shepherd, P. Wide Bandgap Technologies and Their Implications on Miniaturizing Power Electronic Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2014, 2, 374–385. [Google Scholar] [CrossRef]

- Do, T.V.; Trovão, J.P.F.; Li, K.; Boulon, L. Wide-Bandgap Power Semiconductors for Electric Vehicle Systems: Challenges and Trends. IEEE Veh. Technol. Mag. 2021, 16, 89–98. [Google Scholar] [CrossRef]

- Yu, S.; Wang, J.; Zhang, X.; Liu, Y.; Jiang, N.; Wang, W. The Potential Impact of Using Traction Inverters With SiC MOSFETs for Electric Buses. IEEE Access 2021, 9, 51561–51572. [Google Scholar] [CrossRef]

- Biela, J.; Schweizer, M.; Waffler, S.; Kolar, J.W. SiC versus Si—Evaluation of Potentials for Performance Improvement of Inverter and DC–DC Converter Systems by SiC Power Semiconductors. IEEE Trans. Ind. Electron. 2011, 58, 2872–2882. [Google Scholar] [CrossRef]

- Andresen, M.; Buticchi, G.; Liserre, M. Thermal Stress Analysis and MPPT Optimization of Photovoltaic Systems. IEEE Trans. Ind. Electron. 2016, 63, 4889–4898. [Google Scholar] [CrossRef]

- Falck, J.; Buticchi, G.; Liserre, M. Thermal Stress Based Model Predictive Control of Electric Drives. IEEE Trans. Ind. Appl. 2017, 54, 1513–1522. [Google Scholar] [CrossRef]

- He, J.; Sangwongwanich, A.; Yang, Y.; Iannuzzo, F. Lifetime Evaluation of Three-Level Inverters for 1500-V Photovoltaic Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 4285–4298. [Google Scholar] [CrossRef]

- Ni, Z.; Lyu, X.; Yadav, O.P.; Singh, B.N.; Zheng, S.; Cao, D. Overview of Real-Time Lifetime Prediction and Extension for SiC Power Converters. IEEE Trans. Power Electron. 2020, 32, 7765–7794. [Google Scholar] [CrossRef]

- Graovac, D.D.; Pürschel, M.; Kiep, A. MOSFET Power Losses Calculation Using the Data-Sheet Parameters. 2006. Available online: https://application-notes.digchip.com/070/70-41484.pdf (accessed on 10 October 2024).

- Ma, Z.; Pei, Y.; Wang, L.; Yang, Q.; Qi, Z.; Zeng, G. An Accurate Analytical Model of SiC MOSFETs for Switching Speed and Switching Loss Calculation in High-Voltage Pulsed Power Supplies. IEEE Trans. Power Electron. 2023, 38, 3281–3297. [Google Scholar] [CrossRef]

- Dong, Z.; Wu, x.; Xu, H.; Re, N.; Sheng, K. Accurate Analytical Switching-On Loss Model of SiC MOSFET Considering Dynamic Transfer Characteristic and Qgd. IEEE Trans. Power Electron. 2020, 35, 12264–12273. [Google Scholar] [CrossRef]

- Xue, P.; Davari, P. A Temperature-Dependent Analytical Transient Model of SiC MOSFET in Half-Bridge Circuits. IEEE Trans. Power Electron. 2025, 40, 892–905. [Google Scholar] [CrossRef]

- Roy, S.K.; Basu, K. Analytical Estimation of Turn on Switching Loss of SiC MOSFET and Schottky Diode Pair From Datasheet Parameters. IEEE Trans. Power Electron. 2019, 34, 9118–9130. [Google Scholar] [CrossRef]

- Li, X.; Jiang, J.; Huang, A.Q.; Guo, S.; Deng, X.; Zhang, B. A SiC Power MOSFET Loss Model Suitable for High-Frequency Applications. IEEE Trans. Ind. Electron. 2017, 64, 8268–8276. [Google Scholar] [CrossRef]

- Ahmed, M.R.; Todd, R.; Forsyth, A.J. Predicting SiC MOSFET Behavior Under Hard-Switching, Soft-Switching, and False Turn-On Conditions. IEEE Trans. Ind. Electron. 2017, 64, 9001–9011. [Google Scholar] [CrossRef]

- Christen, D.; Biela, J. Analytical Switching Loss Modeling Based on Datasheet Parameters for MOSFETs in a Half-Bridge. IEEE Trans. Power Electron. 2019, 34, 3700–3710. [Google Scholar] [CrossRef]

- Nayak, D.P.; Yakala, R.K.; Kumar, M.; Pramanick, S.K. Temperature-Dependent Reverse Recovery Characterization of SiC MOSFETs Body Diode for Switching Loss Estimation in a Half-Bridge. IEEE Trans. Power Electron. 2022, 37, 5574–5582. [Google Scholar] [CrossRef]

- Song, S.; Peng, H.; Chen, X.; Hao, X. General Analytical Model for SiC MOSFETs Turn-Off Loss Considering No Miller Plateau. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023. [Google Scholar] [CrossRef]

- Hu, A.; Biela, J. An Analytical Switching Loss Model for a SiC MOSFET and Schottky Diode Half-Bridge Based on Nonlinear Differential Equations. In Proceedings of the 2021 23rd European Conference on Power Electronics and Applications (EPE’21 ECCE Europe), Ghent, Belgium, 6–10 September 2021. [Google Scholar] [CrossRef]

- Peng, K.; Eskandari, S.; Santi, E. Analytical loss model for power converters with SiC MOSFET and SiC schottky diode pair. In Proceedings of the 2015 IEEE Energy Conversion Congress and Exposition (ECCE), Montreal, QC, Canada, 20–24 September 2015. [Google Scholar] [CrossRef]

- Hu, A.; Biela, J. Evaluation of the Imax-fsw-dv/dt Trade-off of High Voltage SiC MOSFETs Based on an Analytical Switching Loss Model. In Proceedings of the 2020 22nd European Conference on Power Electronics and Applications (EPE’20 ECCE Europe), Lyon, France, 7–11 September 2020. [Google Scholar] [CrossRef]

- Wang, X.; Zhao, Z.; Li, K.; Zhu, Y.; Chen, K. Analytical Methodology for Loss Calculation of SiC MOSFETs. IEEE J. Emerg. Slected Top. Power Electron. 2019, 5, 71–83. [Google Scholar] [CrossRef]

- Hu, A.; Biela, J. Fast and Accurate Data Sheet based Analytical Turn-on Switching Loss Model for a SiC MOSFET and Schottky Diode Half-Bridge. In Proceedings of the 2023 25th European Conference on Power Electronics and Applications (EPE’23 ECCE Europe), Aalborg, Denmark, 4–8 September 2023. [Google Scholar] [CrossRef]

- Hu, A.; Biela, J. Fast and Accurate Data Sheet Based Analytical Switching Loss Model for a SiC MOSFET and Schottky Diode Half-Bridge. IEEE Open J. Power Electron. 2024, 5, 1684–1696. [Google Scholar] [CrossRef]

- Perret, R. Power Electronics Semiconductor Devices; Wiley: New York, NY, USA, 2013; Chapter 1. [Google Scholar]

- Li, X.; Zhang, L.; Guo, S.; Lei, Y.; Huang, A.Q.; Zhang, B. Understanding switching losses in SiC MOSFET: Toward lossless switching. In Proceedings of the 2015 IEEE 3rd Workshop on Wide Bandgap Power Devices and Applications (WiPDA), Blacksburg, VA, USA, 2–4 November 2015; pp. 3700–3710. [Google Scholar] [CrossRef]

- Ma, C.L.; Lauritzen, P.O. A Simple Power Diode Model with Forward and Reverse Recovery. In Proceedings of the PESC ’91 Record 22nd Annual IEEE Power Electronics Specialists Conference, Cambridge, MA, USA, 24–27 June 1991; pp. 411–415. [Google Scholar] [CrossRef]

- Bryant, A.T.; Kang, X.; Santi, E.; Palmer, P.R.; Hudgins, J.L. Two-step parameter extraction procedure with formal optimization for physics-based circuit simulator IGBT and p-i-n diode models. IEEE Trans. Power Electron. 2006, 21, 295–309. [Google Scholar] [CrossRef]

- Plexim GmbH. The Simulation Platform for Power Electronics Systems: User’s Manual; Plexim GmbH: Zürich, Switzerland, 2017; Chapter 4: Thermal Modeling. [Google Scholar]

- Infineon. IMW65R007M2H CoolSiCTM MOSFET 650 V 7 mΩ G2, 171 A. rev. 2.2. 2024. Available online: https://www.infineon.com/cms/en/product/power/mosfet/silicon-carbide/discretes/imw65r007m2h/ (accessed on 11 December 2024).

- Infineon. IMW65R020M2H CoolSiCTM MOSFET 650 V 20 mΩ G2, 83 A. rev. 2.2. 2024. Available online: https://www.infineon.com/cms/en/product/power/mosfet/silicon-carbide/discretes/imw65r020m2h/ (accessed on 11 December 2024).

- Renesas. Carrying the Heat Away from Power Module PCB Designs, 2019. Available online: https://www.powerelectronictips.com/carrying-the-heat-away-from-power-module-pcb-designs (accessed on 2 February 2025).

- Infineon. TLI4971 High Precision Coreless Current Sensor for Industrial Applications in 8x8mm SMD Package. Available online: https://www.infineon.com/cms/en/product/sensor/current-sensors/tli4971-a120t5-e0001/ (accessed on 30 March 2025).

- ROHM Semiconductors. s4101 1200 V 55 A, N-Channel SiC Power MOSFET Bare Die. rev. 1. 2018. Available online: https://www.rohm.com/products/sic-power-devices/sic-mosfet-bare-die/s4101-product#productDetail (accessed on 1 September 2024).

- ROHM Semiconductors. 1200V, 50A, Silicon-Carbide (SiC) SBD Bare Die rev. 2. 2022. Available online: https://www.rohm.com/products/sic-power-devices/sic-schottky-barrier-diodes-bare-die/s6305-product (accessed on 1 September 2024).

- JCGM 100:2008; Evaluation of Measurements Data-Guide to the Expression of Uncertainty in Measurements. JCGM: Paris, France, 2008.

- Newtons4th Ltd. PPA 3500 User Manual; Newtons4th Ltd.: Loughborough, UK, 2021. [Google Scholar]

- Makridakis, S. Accuracy measures: Theoretical and practical concerns. Int. J. Forecast. 1993, 9, 527–529. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).