Digital Image Decoder for Efficient Hardware Implementation

Abstract

1. Introduction

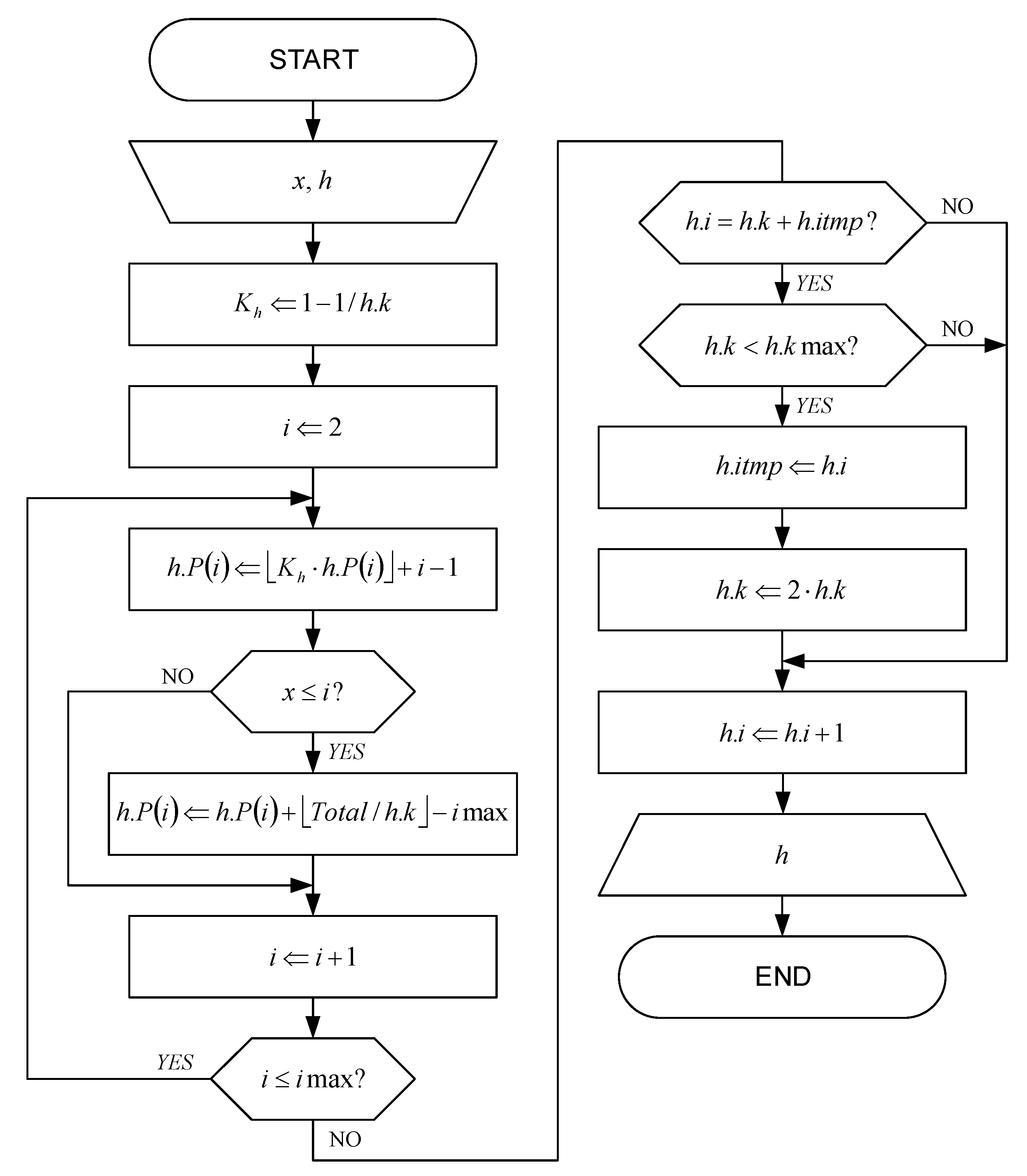

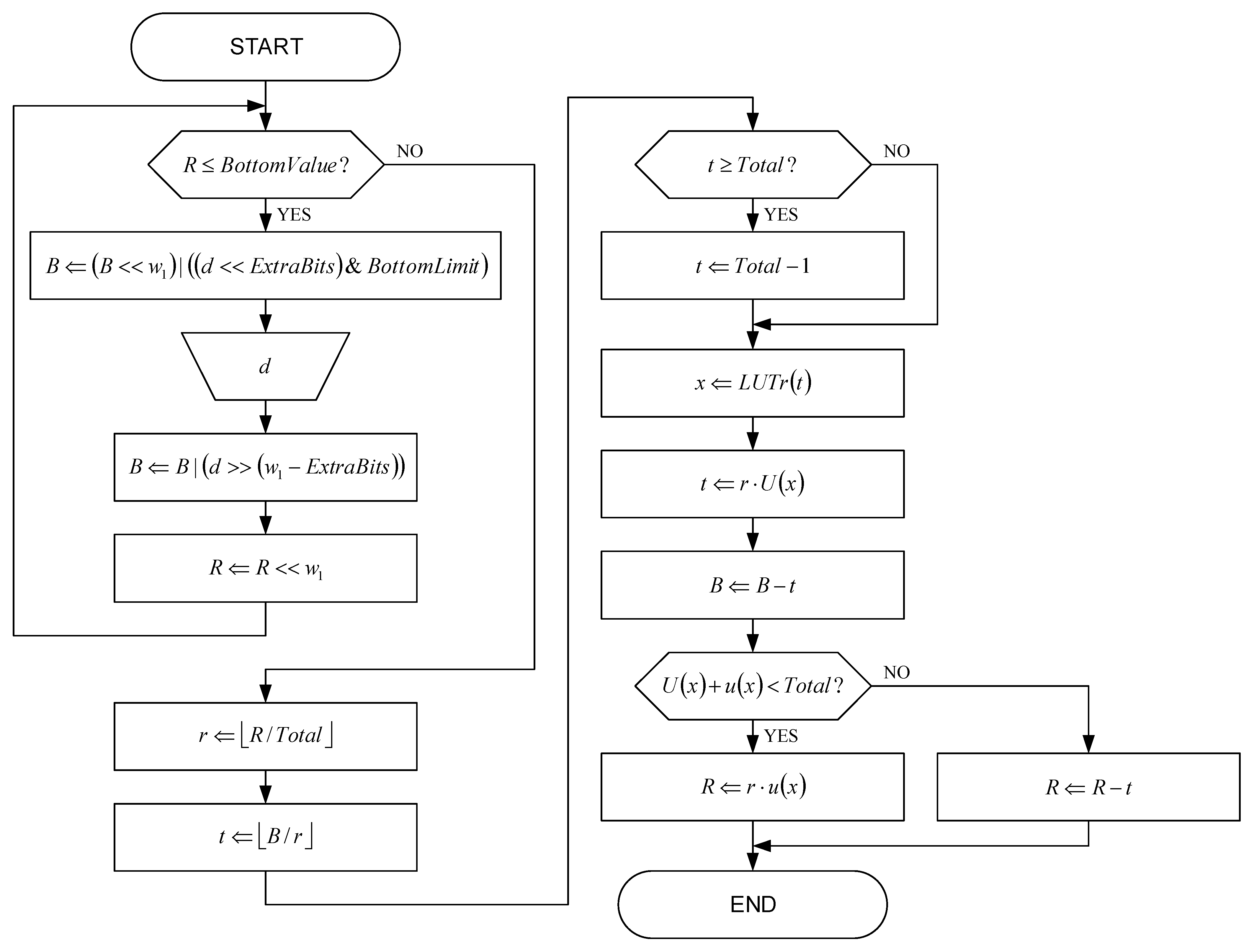

2. Entropy Decoder and Decoding Probability Estimator

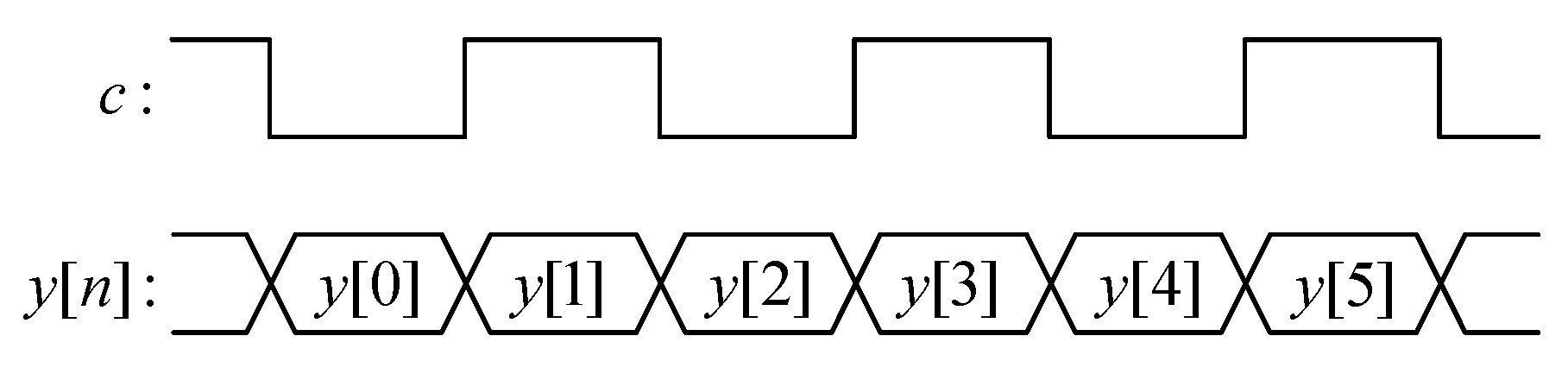

- lower range limit;

- range;

- constant with preferable value 8;

- constant with preferable value 32;

- constant with preferable value ;

- constant with preferable value ;

- constant with preferable value 4;

- constant with preferable value .

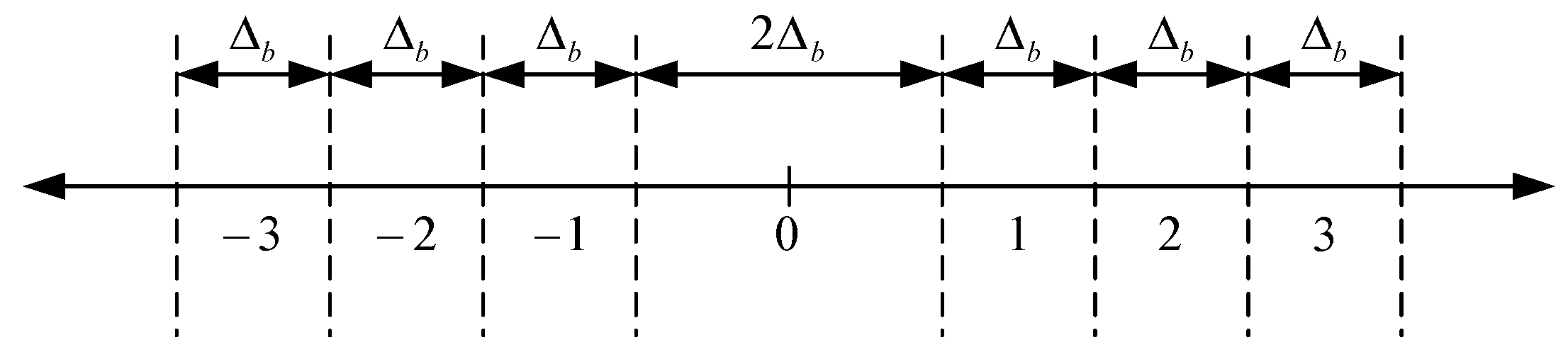

3. Dequantizer

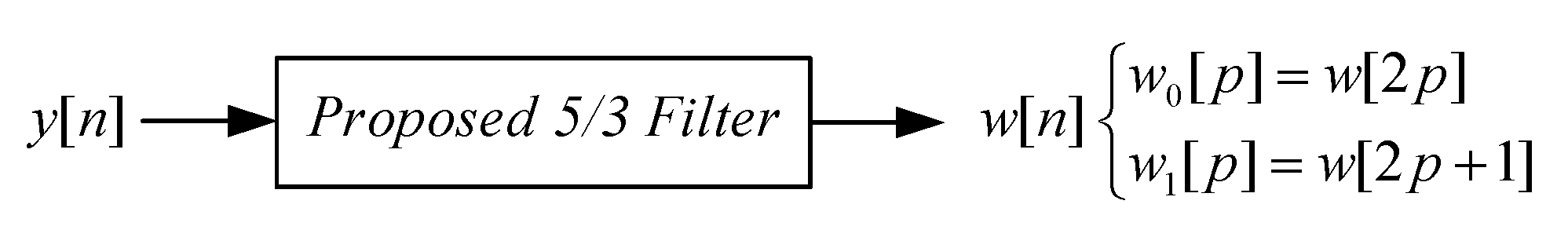

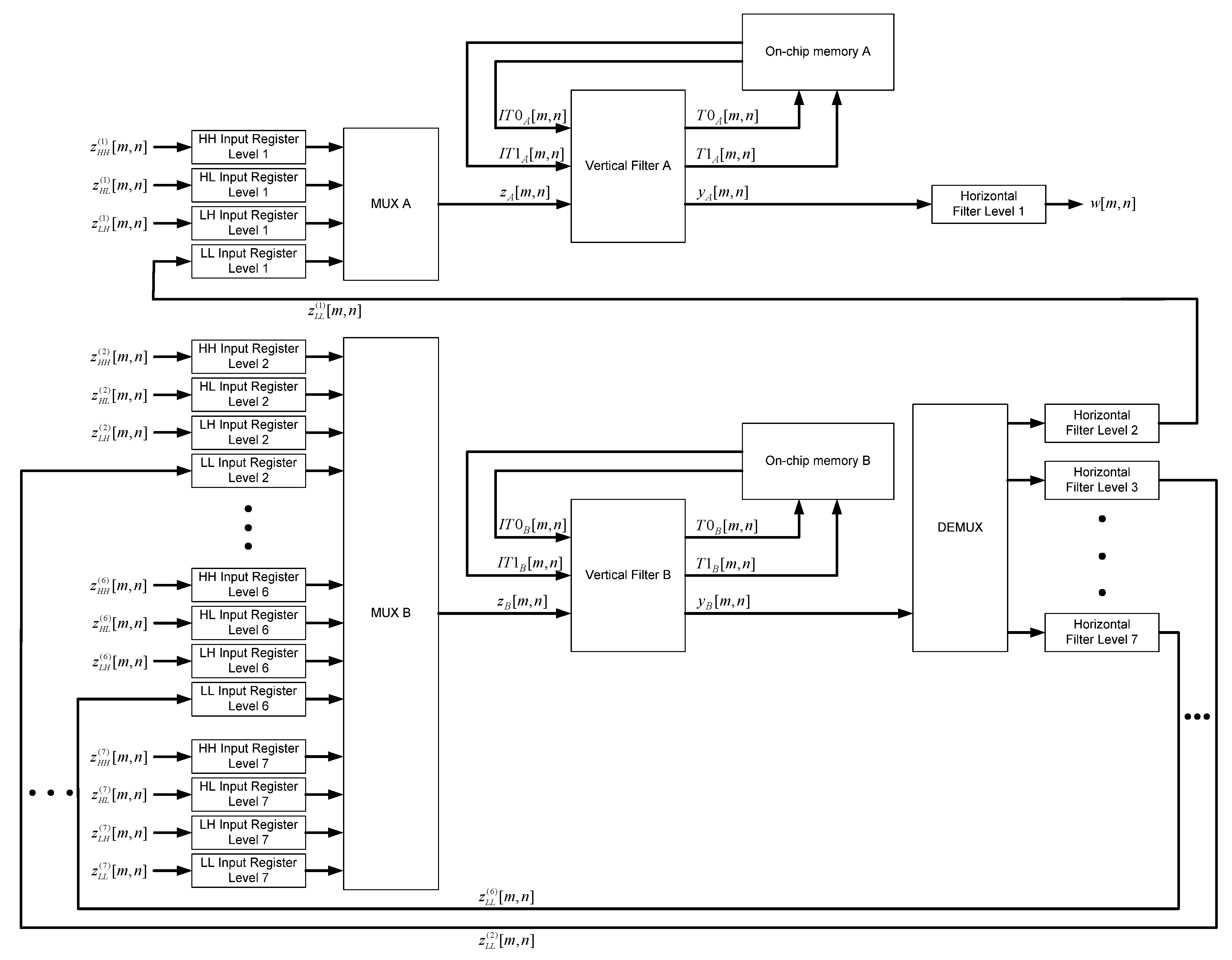

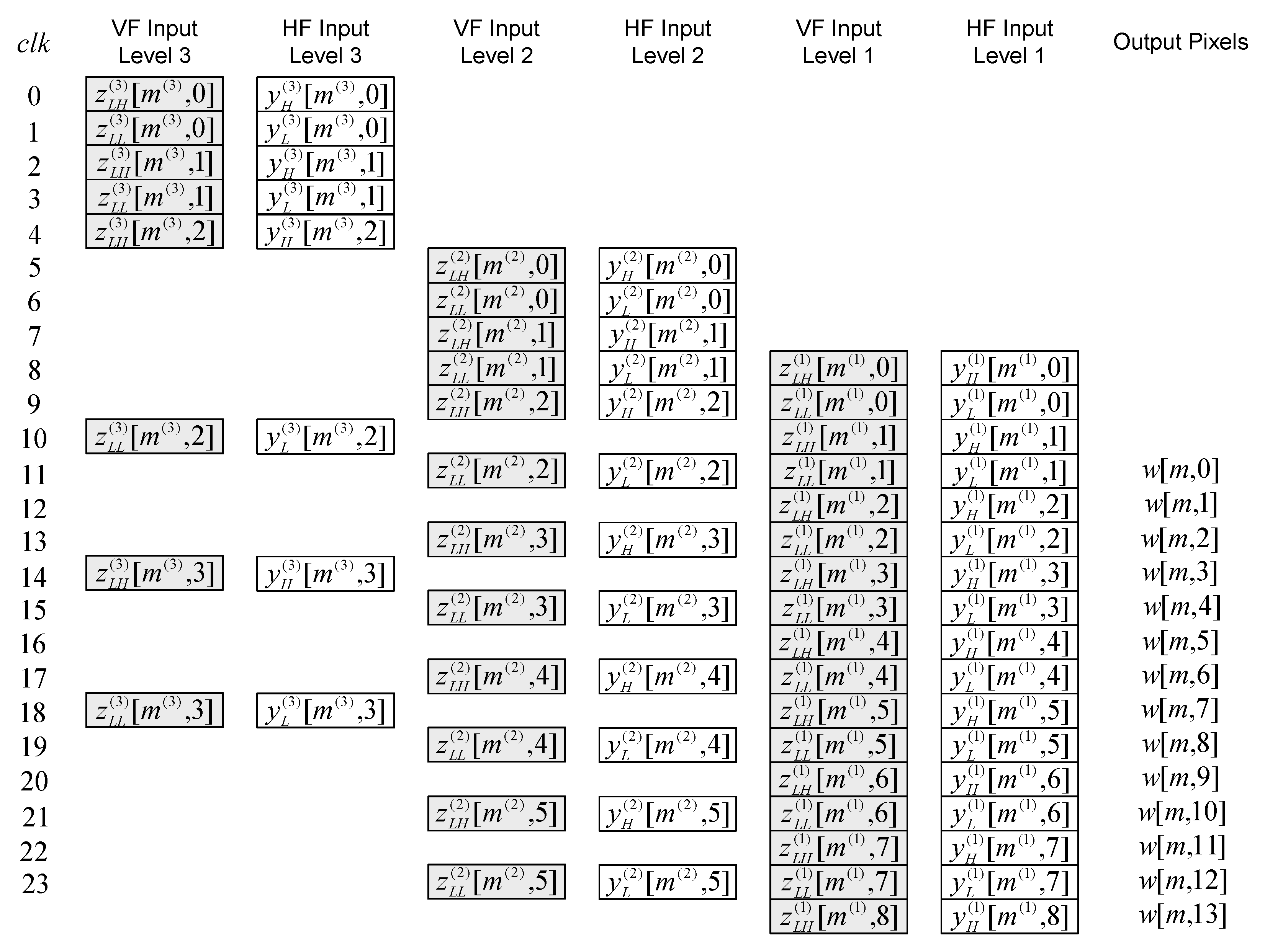

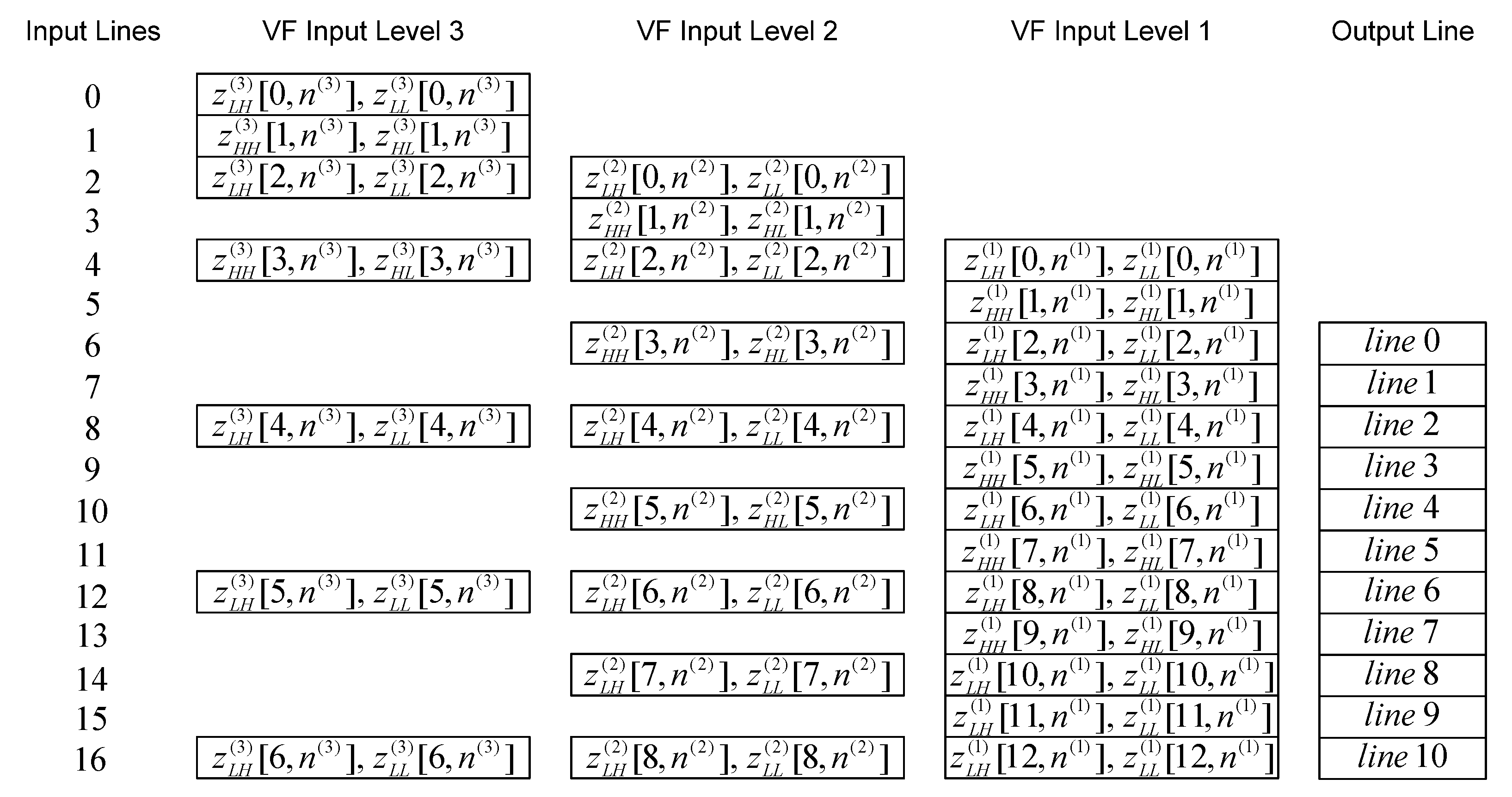

4. Inverse Subband Transformer

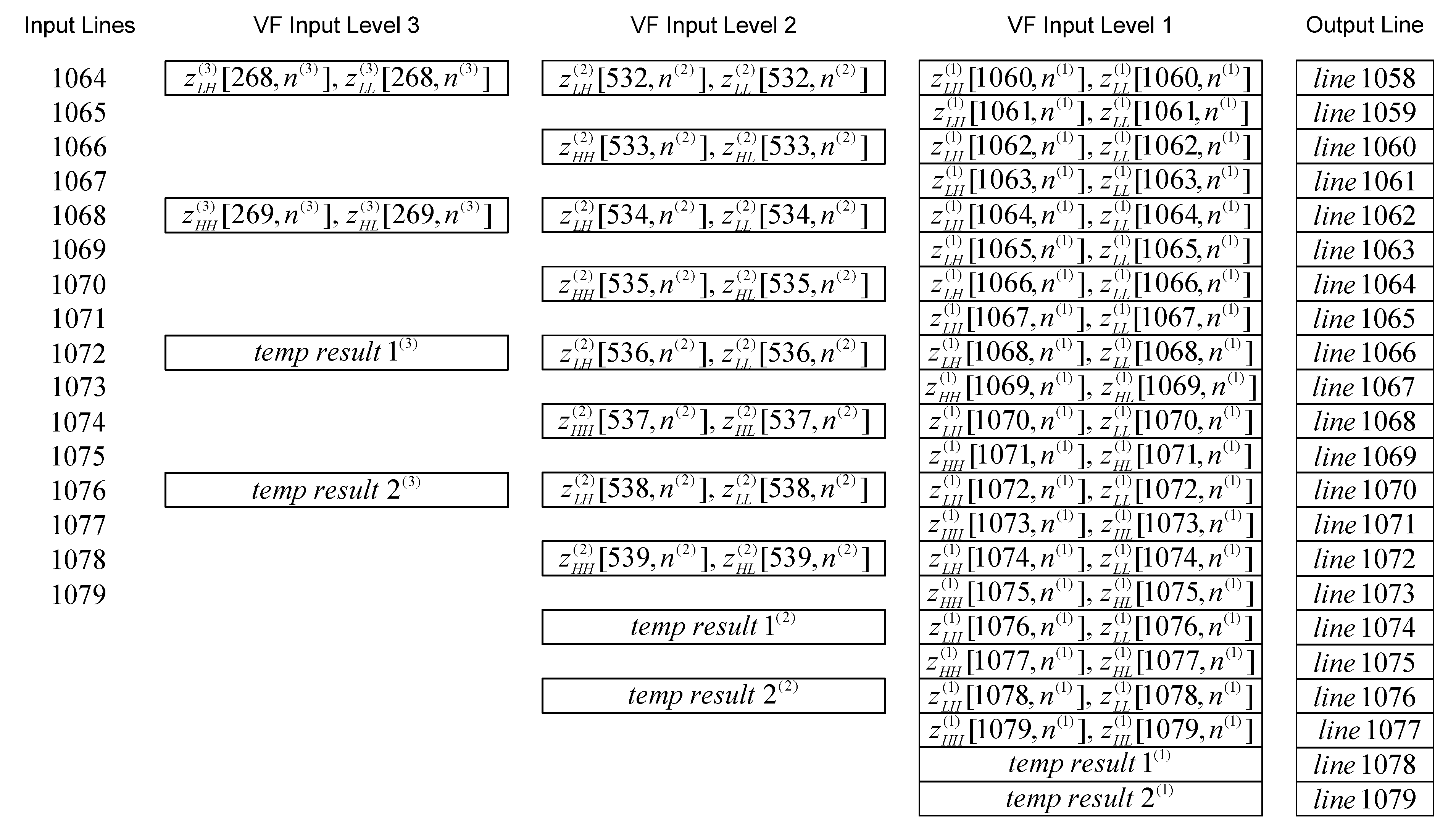

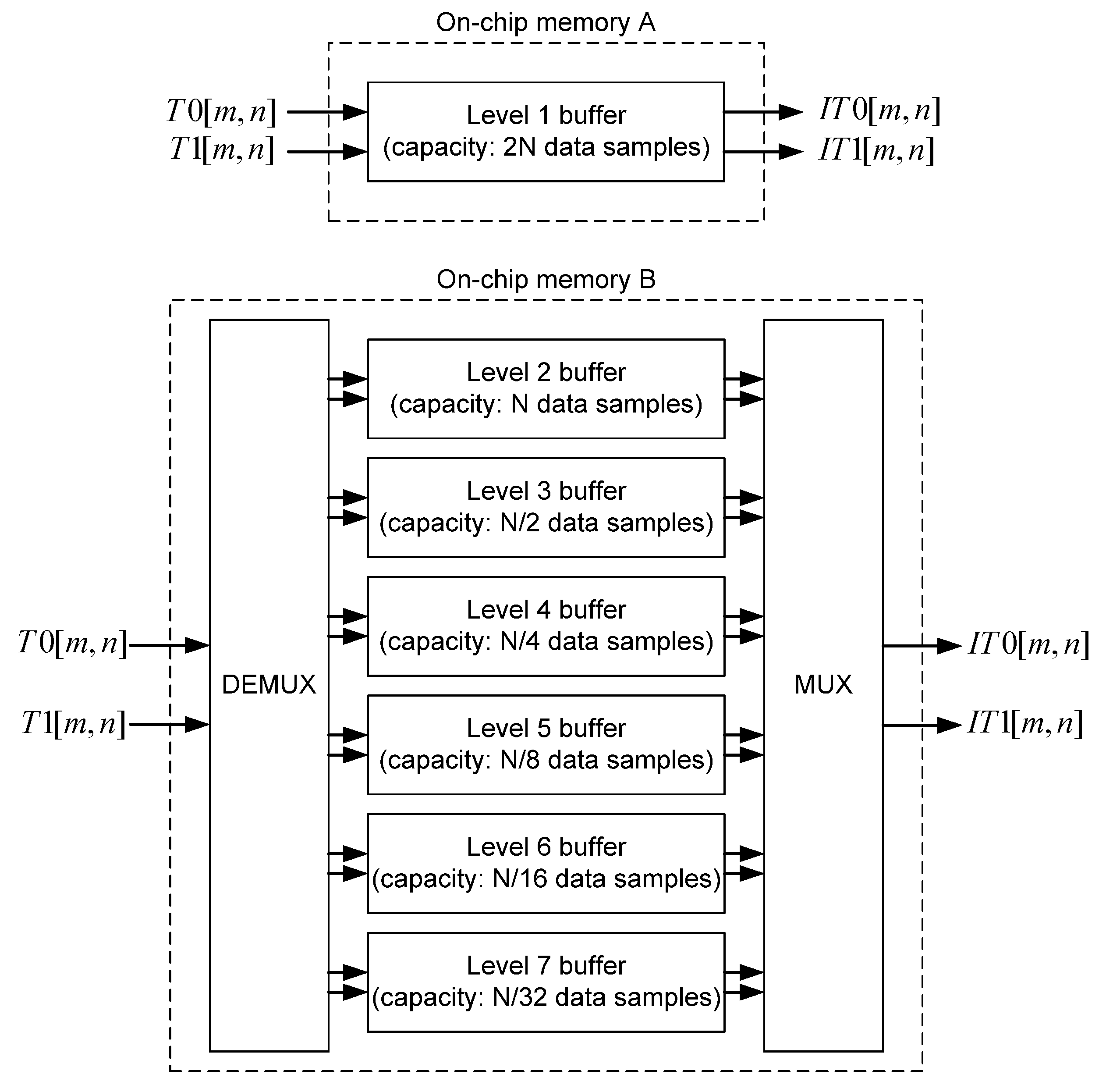

5. Synthesis Results of the Hardware Implementation of the Proposed Digital Image Decoder

6. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Bakr, M.; Salama, A.E. Implementation of 3D-DCT based video encoder/decoder system. In Proceedings of the 45th Midwest Symposium on Circuits and Systems (MWSCAS-2002), Tulsa, OK, USA, 4–7 August 2002. [Google Scholar]

- Descampe, A.; Devaux, F. A flexible, line-based JPEG 2000 decoder for digital cinema. In Proceedings of the 12th IEEE Mediterranean Electrotechnical Conference, Dubrovnik, Croatia, 12–15 May 2004. [Google Scholar]

- Schumacher, P.; Denolf, K.; Chilira-Rus, A.; Turney, R.; Fedele, N.; Vissers, K.; Bormans, J. A scalable, multi-stream MPEG-4 video decoder for conferencing and surveillance applications. In Proceedings of the IEEE International Conference on Image Processing, Genoa, Italy, 11–14 September 2005. [Google Scholar]

- Warsaw, T.; Lukowiak, M. Architecture design of an H.264/AVC decoder for real-time FPGA implementation. In Proceedings of the IEEE 17th International Conference on Application-specific Systems, Architectures and Processors (ASAP’06), Steamboat Springs, CO, USA, 11–13 September 2006. [Google Scholar]

- Descampe, A.; Devaux, F.; Rouvroy, G.; Legat, J.; Quisquater, J.; Macq, B. A Flexible Hardware JPEG 2000 Decoder for Digital Cinema. IEEE Trans. Circuits Syst. Video Technol. 2006, 16, 1397–1410. [Google Scholar] [CrossRef]

- Xu, R.; Xiao, T.; Xu, C. A High-Performance JPEG2000 Decoder Based on FPGA According to DCI Specification. In Proceedings of the Symposium on Photonics and Optoelectronics, Chengdu, China, 19–21 June 2010. [Google Scholar]

- Bonatto, A.; Negreiros, M.; Soares, A.; Susin, A. Towards an Efficient Memory Architecture for Video Decoding Systems. In Proceedings of the Brazilian Symposium on Computing System Engineering, Natal, Brazil, 5–7 November 2012. [Google Scholar]

- Engelhardt, D.; Moller, J.; Hahlbeck, J.; Stabernack, B. FPGA implementation of a full HD real-time HEVC main profile decoder. IEEE Trans. Cons. Electr. 2014, 60, 476–484. [Google Scholar] [CrossRef]

- Stabernack, B.; Moller, J.; Hahlbeck, J.; Brandenburg, J. Demonstrating an FPGA implementation of a full HD real-time HEVC decoder with memory optimizations for range extensions support. In Proceedings of the Conference on Design and Architectures for Signal and Image Processing (DASIP), Krakow, Poland, 23–25 September 2015. [Google Scholar]

- Barge, I.; Ababei, C. H.264 video decoder implemented on FPGAs using 3 × 3 and 2 × 2 networks-on-chip. In Proceedings of the International Conference on ReConFigurable Computing and FPGAs (ReConFig), Cancun, Mexico, 4–6 December 2017. [Google Scholar]

- Witten, I.H.; Neal, R.M.; Cleary, J.G. Arithmetic coding for data compression. Commun. ACM 1987, 30, 520–540. [Google Scholar] [CrossRef]

- Moffat, A.; Neal, R.M.; Witten, I.H. Arithmetic coding revisited. In Proceedings of the Data Compression Conference, Snowbird, UT, USA, 28–30 March 1995; pp. 202–211. [Google Scholar]

- Moffat, A.; Neal, R.M.; Witten, I.H. Arithmetic coding revisited. ACM Trans. Inform. Syst. 1998, 16, 256–294. [Google Scholar] [CrossRef]

- Mitchell, J.L.; Pennebaker, W.B. Software implementations of the Q-coder. IBM J. Res. Dev. 1988, 21, 753–774. [Google Scholar] [CrossRef]

- Pennebaker, W.B.; Mitchell, J.L.; Langdon, G.G.; Arps, R.B. An overview of the basic principles of the Q-coder adaptive binary arithmetic coder. IBM J. Res. Dev. 1988, 32, 717–726. [Google Scholar] [CrossRef]

- Pennebaker, W.B.; Mitchell, J.L. Probability Adaptation for Arithmetic Coders. U.S. Patent 4,933,883, 12 June 1990. [Google Scholar]

- Pennebaker, W.B.; Mitchell, J.L. Probability Adaptation for Arithmetic Coders. U.S. Patent 4,935,882, 19 June 1990. [Google Scholar]

- Bottou, L.; Howard, P.G.; Bengio, Y. The Z-coder adaptive binary coder. In Proceedings of the Data Compression Conference, Snowbird, UT, USA, 30 March–1 April 1998; pp. 13–22. [Google Scholar]

- Bengio, Y.; Bottou, L.; Howard, P.G. Z-Coder: Fast Adaptive Binary Arithmetic Coder. U.S. Patent 6,188,334, 13 February 2001. [Google Scholar]

- Bengio, Y.; Bottou, L.; Howard, P.G. Z-Coder: A Fast Adaptive Binary Arithmetic Coder. U.S. Patent 6,225,925, 1 May 2001. [Google Scholar]

- Bengio, Y.; Bottou, L.; Howard, P.G. Z-Coder: A Fast Adaptive Binary Arithmetic Coder. U.S. Patent 6,281,817, 28 August 2001. [Google Scholar]

- Wallace, G.K. The JPEG still picture compression standard. IEEE Trans. Consum. Electron. 1992, 38, 18–34. [Google Scholar] [CrossRef]

- Ono, F.; Denki, M.; Kaisha, K. Coding Method of Image Information. U.S. Patent 5,059,976, 22 October 1991. [Google Scholar]

- Ono, F.; Denki, M.; Kaisha, K. Coding System. U.S. Patent 5,307,062, 26 April 1994. [Google Scholar]

- The Data Compression Resource on the Internet. Available online: http://www.data-compression.info/Algorithms/RC/ (accessed on 10 June 2021).

- Soman, K.P.; Ramachandran, K.I.; Resmi, N.G. Insight into Wavelets from Theory to Practice; PHI Learning: Delhi, India, 2010. [Google Scholar]

- Parhi, K.K.; Nishitani, T. VLSI architectures for discrete wavelet transforms. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 1993, 1, 191–202. [Google Scholar] [CrossRef]

- Wu, P.C.; Chen, L.G. An efficient architecture for two-dimensional discrete wavelet transform. IEEE Trans. Circuit Syst. Video Technol. 2001, 11, 536–545. [Google Scholar]

- Zervas, N.D.; Anagnostopoulos, G.P.; Spiliotopoulos, V.; Andreopoulos, Y.; Goutis, C.E. Evaluation of design alternatives for the 2-D-discrete wavelet transform. IEEE Trans. Circuits Syst. Video Technol. 2001, 11, 1246–1262. [Google Scholar] [CrossRef]

- Cheng, C.; Parhi, K.K. High-speed VLSI implementation of 2-D discrete wavelet transform. IEEE Trans. Signal Process. 2008, 56, 393–403. [Google Scholar] [CrossRef]

- Usha Bhanu, N.; Chilambuchelvan, A. Efficient VLSI architecture for discrete wavelet transform. Int. J. Comput. Sci. Issues 2011, 1, 32–36. [Google Scholar]

- Ghantous, M.; Bayoumi, M. P2E-DWT: A parallel and pipelined efficient VLSI architecture of 2-D discrete wavelet transform. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 941–944. [Google Scholar]

- Liu, C.C.; Shiau, Y.H.; Jou, J.M. Design and implementation of a progressive image coding chip based on the lifted wavelet transform. In Proceedings of the 11th VLSI Design/CAD Symposium, Pingtung, China, 16-19 August 2000. [Google Scholar]

- Jou, J.M.; Shiau, Y.H.; Liu, C.C. Efficient VLSI architectures for the biorthogonal wavelet transform by filter bank and lifting scheme. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Sydney, Australia, 6–9 May 2001; pp. 529–532. [Google Scholar]

- Lian, C.J.; Chen, K.F.; Chen, H.H.; Chen, L.G. Lifting based discrete wavelet transform architecture for JPEG2000. In Proceedings of the IEEE International Symposium on Circuits and Systems (ISCAS), Sydney, Australia, 6–9 May 2001; pp. 445–448. [Google Scholar]

- Andra, K.; Chakrabarti, C.; Acharya, T. A VLSI architecture for lifting-based forward and inverse wavelet transform. IEEE Trans. Signal Process. 2002, 50, 966–977. [Google Scholar] [CrossRef]

- Chakrabarti, C.; Vishwanath, M. Efficient realizations of the discrete and continuous wavelet transforms: From single chip implementations to mappings on SIMD array computers. IEEE Trans. Signal Process. 1995, 43, 759–771. [Google Scholar] [CrossRef]

- Vishwanath, M.; Owens, R.M.; Irwin, M.J. VLSI architectures for the discrete wavelet transform. IEEE Trans. Circuits Syst. II 1995, 42, 305–316. [Google Scholar] [CrossRef]

- Liao, H.; Mandal, M.K.; Cockburn, B.F. Efficient implementation of lifting-based discrete wavelet transform. Electron. Lett. 2002, 38, 1010–1012. [Google Scholar] [CrossRef]

- Tseng, P.C.; Huang, C.T.; Chen, L.G. Generic RAM-based architecture for two-dimensional discrete wavelet transform with line-based method. In Proceedings of the APCCAS, Asia-Pacific Conference on Circuits and Systems, Denpasar, Indonesia, 28–31 October 2002; pp. 363–366. [Google Scholar]

- Xiong, C.Y.; Tian, J.; Liu, J. Efficient high-speed/low-power line-based architecture for two-dimensional discrete wavelet transform using lifting scheme. IEEE Trans. Circuits Syst. Video Technol. 2006, 16, 309–316. [Google Scholar] [CrossRef]

- Mohanty, B.K.; Meher, P.K. Memory efficient modular VLSI architecture for highthroughput and low-latency implementation of multilevel lifting 2-D DWT. IEEE Trans. Signal Process. 2011, 59, 2072–2084. [Google Scholar] [CrossRef]

- Aziz, S.M.; Pham, D.M. Efficient parallel architecture for multi-level forward discrete wavelet transform processors. Comp. Elect. Eng. 2012, 38, 1325–1335. [Google Scholar] [CrossRef]

- Mohanty, B.K.; Meher, P.K. Memory-efficient high-speed convolution-based generic structure for multilevel 2-D DWT. IEEE Trans. Circuits Syst. Video Technol. 2013, 23, 353–363. [Google Scholar] [CrossRef]

- Hsia, C.H.; Chiang, J.S.; Guo, J.M. Memory-efficient hardware architecture of 2-D dual-mode lifting-based discrete wavelet transform. IEEE Trans. Circuits Syst. Video Technol. 2013, 23, 671–683. [Google Scholar] [CrossRef]

- Darji, A.D.; Kushwah, S.S.; Merch, S.N.; Chandorkar, A.N. High-performance hardware architectures for multi-level lifting-based discrete wavelet transform. Eurasip J. Image Video Process. 2014, 47, 1–19. [Google Scholar] [CrossRef]

- Hsia, C.H.; Chiang, J.S.; Chang, S.H. An efficient VLSI architecture for 2-D dual-mode SMDWT. In Proceedings of the 2013 IEEE International Conference on Networking, Sensing and Control (ICNSC), Paris, France, 10–12 April 2013; pp. 775–779. [Google Scholar]

- Hsia, C.H. A New VLSI Architecture Symmetric Mask-Based Discrete Wavelet Transform. J. Internet Technol. 2014, 15, 1083–1090. [Google Scholar]

- Ballesteros, D.M.L.; Renza, D.; Pedraza, L.F. Hardware Design of the Discrete Wavelet Transform: An Analysis of Complexity, Accuracy and Operating Frequency. Ing. Cienc. 2016, 12, 129–148. [Google Scholar] [CrossRef]

- Wang, H.; Wang, J.; Zhang, X. Architecture and Implementation of Shape Adaptive Discrete Wavelet Transform for Remote Sensing Image Onboard Compression. In Proceedings of the 3rd IEEE International Conference on Computer and Communications, Chengdu, China, 13–16 December 2017; pp. 1803–1808. [Google Scholar]

- Basiri, M.A.M.; Noor, M.S. An Efficient VLSI Architecture for Convolution Based DWT Using MAC. In Proceedings of the 31st International Conference on VLSI Design and 17th International Conference on Embedded System, Pune, India, 6–10 January 2018; pp. 271–276. [Google Scholar]

- Aziz, F.; Javed, S.; Gardezi, S.E.I.; Younis, C.J.; Alam, M. Design and Implementation of Efficient DA Architecture for LeGall 5/3 DWT. In Proceedings of the 2018 International Symposium on Recent Advances in Electrical Engineering (RAEE), Islamabad, Pakistan, 17–18 October 2018. [Google Scholar]

- Ganapathi, H.; Kotha, S.R.; Telugu, K.S.R. A new approach for 1-D and 2-D DWT architectures using LUT based lifting and flipping cell. Int. J. Electron. Commun. 2018, 97, 165–177. [Google Scholar]

- Gardezi, S.E.I.; Aziz, F.; Javed, S.; Younis, C.J.; Alam, M.; Massoud, Y. Design and VLSI Implementation of CSD based DA Architecture for 5/3 DWT. In Proceedings of the 16th International Bhurban Conference on Applied Sciences and Technology (IBCAST), Islamabad, Pakistan, 8–12 January 2019; pp. 548–552. [Google Scholar]

- Tausif, M.; Khan, E.; Mohd, H.; Reisslein, M. Lifting-Based Fractional Wavelet Filter: Energy-Efficient DWT Architecture for Low-Cost Wearable Sensors. Adv. Multimed. 2020, 2020, 8823689. [Google Scholar] [CrossRef]

- Chakraborty, A.; Banerjee, A. A memory and area-efficient distributed arithmetic based modular VLSI architecture of 1D/2D reconfigurable 9/7 and 5/3 DWT filters for real-time image decomposition. J. Real-Time Image Process. 2020, 17, 1421–1446. [Google Scholar] [CrossRef]

- Chakraborty, A.; Banerjee, A. A Memory Efficient, Multiplierless & Modular VLSI Architecture of 1D/2D Re-Configurable 9/7 & 5/3 DWT Filters Using Distributed Arithmetic. J. Circuits Syst. Comput. 2020, 29, 2050151. [Google Scholar]

- Pinto, R.; Shama, K. An Efficient Architecture for Modifed Lifting-Based Discrete Wavelet Transform. Sens. Imaging 2020, 21, 53. [Google Scholar] [CrossRef]

- Joshi, A. Hardware Implementation of Audio Watermarking Based on DWT Transform. In Security and Privacy from a Legal, Ethical, and Technical Perspective; IntechOpen: London, UK, 2019; pp. 1–17. [Google Scholar]

- Tausif, M.; Jain, A.; Khan, E.; Hasan, M. Memory-efficient architecture for FrWF-based DWT of high-resolution images for IoMT applications. Multimed. Tools Appl. 2021, 80, 11177–11199. [Google Scholar] [CrossRef]

- Rajović, V.; Savić, G.; Čeperković, V.; Prokin, M. Combined one-dimensional lowpass and highpass filters for subband transformer. Electron. Lett. 2013, 49, 1150–1152. [Google Scholar] [CrossRef]

- Savić, G.; Prokin, M.; Rajović, V.; Prokin, D. Novel one-dimensional and two-dimensional forward discrete wavelet transform 5/3 filter architectures for efficient hardware implementation. J. Real-Time Image Process. 2019, 16, 1459–1478. [Google Scholar] [CrossRef]

- Savić, G.; Prokin, M.; Rajović, V.; Prokin, D. High-Performance 1-D and 2-D Inverse DWT 5/3 Filter Architectures for Efficient Hardware Implementation. Circuits Syst. Signal Process. 2017, 36, 3674–3701. [Google Scholar] [CrossRef]

- Savić, G.; Prokin, M.; Rajović, V.; Prokin, D. Efficient Hardware Realization of Digital Image Decoder. In Proceedings of the 25th Telecommunications Forum (TELFOR), Belgrade, Serbia, 21–22 November 2017; pp. 534–541. [Google Scholar]

- Čeperković, V.; Pavlović, S.; Mirković, D.; Prokin, M. Fast Codec with High Compression Ratio and Minimum Required Resources. U.S. Patent 8,306,340, 6 November 2012. [Google Scholar]

- Martin, G.N.N. Range encoding: An algorithm for removing redundancy from a digitised message. In Proceedings of the Video & Data Recording Conference, Southampton, UK, 24–27 July 1979. [Google Scholar]

- Schindler, M. A fast renormalization for arithmetic coding. In Proceedings of the Data Compression Conference, Snowbird, UT, USA, 30 March–1 April 1998. [Google Scholar]

- Range Encoder Homepage. Available online: http://www.compressconsult.com/rangecoder/ (accessed on 10 June 2021).

- Magenheimer, D.J.; Peters, L.; Pettis, K.W.; Zuras, D. Integer multiplication and division on the HP precision architecture. IEEE Trans. Comput. 1988, 37, 980–990. [Google Scholar] [CrossRef]

- Granlud, T.; Montgomery, P.L. Division by invariant integers using multiplication. SIGPLAN Not. 1994, 29, 61. [Google Scholar] [CrossRef]

- Altera Press. Cyclone IV Device Handbook—Volume 1; Version 1.8; Altera Press: Blacksburg, VA, USA, 2013. [Google Scholar]

- Terasic Technologies. DE2-115 User Manual; Version 2.1; Terasic Technologies: Hsinchu, Taiwan, 2012. [Google Scholar]

| Limits of the Samples (Inclusive) | Range of the Samples | MS | |

|---|---|---|---|

| Lower | Upper | ||

| 0 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 |

| 2 | 2 | 1 | 2 |

| 3 | 3 | 1 | 3 |

| 4 | 5 | 2 | 4 |

| 6 | 7 | 2 | 5 |

| 8 | 11 | 4 | 6 |

| 12 | 15 | 4 | 7 |

| 16 | 23 | 8 | 8 |

| 24 | 31 | 8 | 9 |

| 32 | 47 | 16 | 10 |

| 48 | 63 | 16 | 11 |

| 64 | 95 | 32 | 12 |

| 96 | 127 | 32 | 13 |

| 128 | 191 | 64 | 14 |

| 192 | 255 | 64 | 15 |

| 256 | 383 | 128 | 16 |

| 384 | 511 | 128 | 17 |

| 512 | 767 | 256 | 18 |

| 768 | 1023 | 256 | 19 |

| 1024 | 1535 | 512 | 20 |

| 1536 | 2047 | 512 | 21 |

| 2048 | 3071 | 1024 | 22 |

| 3072 | 4095 | 1024 | 23 |

| 4096 | 6143 | 2048 | 24 |

| 6144 | 8191 | 2048 | 25 |

| 8192 | 12,287 | 4096 | 26 |

| 12,288 | 16,383 | 4096 | 27 |

| 16,384 | 24,575 | 8192 | 28 |

| 24,576 | 32,767 | 8192 | 29 |

| 32,768 | 49,151 | 16,384 | 30 |

| 49,152 | 65,535 | 16,384 | 31 |

| S0 | S1 | S2 | S3 | TC | SC | S0 | S1 | S2 | S3 | TC | SC | S0 | S1 | S2 | S3 | TC | SC |

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 1 | 0 | 0 | 0 | 27 | 2 | 2 | 0 | 0 | 0 | 54 | 1 |

| 0 | 0 | 0 | 1 | 1 | 0 | 1 | 0 | 0 | 1 | 28 | 1 | 2 | 0 | 0 | 1 | 55 | 0 |

| 0 | 0 | 0 | 2 | 2 | 0 | 1 | 0 | 0 | 2 | 29 | 2 | 2 | 0 | 0 | 2 | 56 | 0 |

| 0 | 0 | 1 | 0 | 3 | 4 | 1 | 0 | 1 | 0 | 30 | 0 | 2 | 0 | 1 | 0 | 57 | 1 |

| 0 | 0 | 1 | 1 | 4 | 1 | 1 | 0 | 1 | 1 | 31 | 1 | 2 | 0 | 1 | 1 | 58 | 0 |

| 0 | 0 | 1 | 2 | 5 | 2 | 1 | 0 | 1 | 2 | 32 | 1 | 2 | 0 | 1 | 2 | 59 | 2 |

| 0 | 0 | 2 | 0 | 6 | 1 | 1 | 0 | 2 | 0 | 33 | 1 | 2 | 0 | 2 | 0 | 60 | 0 |

| 0 | 0 | 2 | 1 | 7 | 0 | 1 | 0 | 2 | 1 | 34 | 0 | 2 | 0 | 2 | 1 | 61 | 0 |

| 0 | 0 | 2 | 2 | 8 | 1 | 1 | 0 | 2 | 2 | 35 | 0 | 2 | 0 | 2 | 2 | 62 | 0 |

| 0 | 1 | 0 | 0 | 9 | 0 | 1 | 0 | 0 | 0 | 36 | 1 | 2 | 0 | 0 | 0 | 63 | 0 |

| 0 | 1 | 0 | 1 | 10 | 1 | 1 | 1 | 0 | 1 | 37 | 1 | 2 | 1 | 0 | 1 | 64 | 0 |

| 0 | 1 | 0 | 2 | 11 | 1 | 1 | 1 | 0 | 2 | 38 | 1 | 2 | 1 | 0 | 2 | 65 | 0 |

| 0 | 1 | 1 | 0 | 12 | 1 | 1 | 1 | 1 | 0 | 39 | 0 | 2 | 1 | 1 | 0 | 66 | 0 |

| 0 | 1 | 1 | 1 | 13 | 0 | 1 | 1 | 1 | 1 | 40 | 1 | 2 | 1 | 1 | 1 | 67 | 1 |

| 0 | 1 | 1 | 2 | 14 | 0 | 1 | 1 | 1 | 2 | 41 | 0 | 2 | 1 | 1 | 2 | 68 | 1 |

| 0 | 1 | 2 | 0 | 15 | 0 | 1 | 1 | 2 | 0 | 42 | 1 | 2 | 1 | 2 | 0 | 69 | 0 |

| 0 | 1 | 2 | 1 | 16 | 4 | 1 | 1 | 2 | 1 | 43 | 0 | 2 | 1 | 2 | 1 | 70 | 0 |

| 0 | 1 | 2 | 2 | 17 | 0 | 1 | 1 | 2 | 2 | 44 | 0 | 2 | 1 | 2 | 2 | 71 | 3 |

| 0 | 2 | 0 | 0 | 18 | 4 | 1 | 2 | 0 | 0 | 45 | 3 | 2 | 2 | 0 | 0 | 72 | 0 |

| 0 | 2 | 0 | 1 | 19 | 2 | 1 | 2 | 0 | 1 | 46 | 0 | 2 | 2 | 0 | 1 | 73 | 4 |

| 0 | 2 | 0 | 2 | 20 | 2 | 1 | 2 | 0 | 2 | 47 | 1 | 2 | 2 | 0 | 2 | 74 | 3 |

| 0 | 2 | 1 | 0 | 21 | 1 | 1 | 2 | 1 | 0 | 48 | 1 | 2 | 2 | 1 | 0 | 75 | 2 |

| 0 | 2 | 1 | 1 | 22 | 0 | 1 | 2 | 1 | 1 | 49 | 2 | 2 | 2 | 1 | 1 | 76 | 2 |

| 0 | 2 | 1 | 2 | 23 | 3 | 1 | 2 | 1 | 2 | 50 | 2 | 2 | 2 | 1 | 2 | 77 | 0 |

| 0 | 2 | 2 | 0 | 24 | 0 | 1 | 2 | 2 | 0 | 51 | 0 | 2 | 2 | 2 | 0 | 78 | 2 |

| 0 | 2 | 2 | 1 | 25 | 0 | 1 | 2 | 2 | 1 | 52 | 0 | 2 | 2 | 2 | 1 | 79 | 1 |

| 0 | 2 | 2 | 2 | 26 | 1 | 1 | 2 | 2 | 2 | 53 | 1 | 2 | 2 | 2 | 2 | 80 | 0 |

| TC | P(0) | P(1) | NS | TC | P(0) | P(1) | NS | TC | P(0) | P(1) | NS |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 0.5276 | 0.4724 | 0 | 27 | 0.6147 | 0.3853 | 0 | 54 | 0.4168 | 0.5832 | 1 |

| 1 | 0.5333 | 0.4667 | 0 | 28 | 0.4170 | 0.5830 | 1 | 55 | 0.5012 | 0.4988 | 0 |

| 2 | 0.4901 | 0.5099 | 1 | 29 | 0.6326 | 0.3674 | 0 | 56 | 0.5302 | 0.4698 | 0 |

| 3 | 0.2961 | 0.7039 | 1 | 30 | 0.4889 | 0.5111 | 1 | 57 | 0.5467 | 0.4533 | 0 |

| 4 | 0.4321 | 0.5679 | 1 | 31 | 0.4176 | 0.5824 | 1 | 58 | 0.5061 | 0.4939 | 0 |

| 5 | 0.6300 | 0.3700 | 0 | 32 | 0.4469 | 0.5531 | 1 | 59 | 0.4039 | 0.5961 | 1 |

| 6 | 0.4463 | 0.5537 | 1 | 33 | 0.5505 | 0.4495 | 0 | 60 | 0.5024 | 0.4976 | 0 |

| 7 | 0.4754 | 0.5246 | 1 | 34 | 0.5240 | 0.4760 | 0 | 61 | 0.4613 | 0.5387 | 1 |

| 8 | 0.4397 | 0.5603 | 1 | 35 | 0.4731 | 0.5269 | 1 | 62 | 0.4837 | 0.5163 | 1 |

| 9 | 0.5012 | 0.4988 | 0 | 36 | 0.4299 | 0.5701 | 1 | 63 | 0.5106 | 0.4894 | 0 |

| 10 | 0.5796 | 0.4204 | 0 | 37 | 0.5880 | 0.4120 | 0 | 64 | 0.5440 | 0.4560 | 0 |

| 11 | 0.4117 | 0.5883 | 1 | 38 | 0.5806 | 0.4194 | 0 | 65 | 0.5343 | 0.4657 | 0 |

| 12 | 0.5842 | 0.4158 | 0 | 39 | 0.4698 | 0.5302 | 1 | 66 | 0.4918 | 0.5082 | 1 |

| 13 | 0.5457 | 0.4543 | 0 | 40 | 0.4119 | 0.5881 | 1 | 67 | 0.4521 | 0.5479 | 1 |

| 14 | 0.5364 | 0.4636 | 0 | 41 | 0.5193 | 0.4807 | 0 | 68 | 0.5841 | 0.4159 | 0 |

| 15 | 0.5243 | 0.4757 | 0 | 42 | 0.4539 | 0.5461 | 1 | 69 | 0.5211 | 0.4789 | 0 |

| 16 | 0.7224 | 0.2776 | 0 | 43 | 0.4871 | 0.5129 | 1 | 70 | 0.4783 | 0.5217 | 1 |

| 17 | 0.5050 | 0.4950 | 0 | 44 | 0.4953 | 0.5047 | 1 | 71 | 0.6651 | 0.3349 | 0 |

| 18 | 0.7235 | 0.2765 | 0 | 45 | 0.3502 | 0.6498 | 1 | 72 | 0.4561 | 0.5439 | 1 |

| 19 | 0.3963 | 0.6037 | 1 | 46 | 0.4688 | 0.5312 | 1 | 73 | 0.6998 | 0.3002 | 0 |

| 20 | 0.6019 | 0.3981 | 0 | 47 | 0.5802 | 0.4198 | 0 | 74 | 0.6531 | 0.3469 | 0 |

| 21 | 0.4508 | 0.5492 | 1 | 48 | 0.4432 | 0.5568 | 1 | 75 | 0.6163 | 0.3837 | 0 |

| 22 | 0.5286 | 0.4714 | 0 | 49 | 0.3927 | 0.6073 | 1 | 76 | 0.5956 | 0.4044 | 0 |

| 23 | 0.6598 | 0.3402 | 0 | 50 | 0.6199 | 0.3801 | 0 | 77 | 0.5022 | 0.4978 | 0 |

| 24 | 0.4770 | 0.5230 | 1 | 51 | 0.5357 | 0.4643 | 0 | 78 | 0.6148 | 0.3852 | 0 |

| 25 | 0.5417 | 0.4583 | 0 | 52 | 0.4830 | 0.5170 | 1 | 79 | 0.4368 | 0.5632 | 1 |

| 26 | 0.4398 | 0.5602 | 1 | 53 | 0.4464 | 0.5536 | 1 | 80 | 0.5065 | 0.4935 | 0 |

| Divide by [Decimal Number] | Multiply by [Hexadecimal Number] | Right Shift for [Binary Digits] |

|---|---|---|

| 3 | 0AAAAAAAB | 1 |

| 5 | 0CCCCCCCD | 2 |

| 7 | 049249249 | 1 |

| 9 | 038E38E39 | 1 |

| 11 | 0BA2E8BA3 | 3 |

| 13 | 04EC4EC4F | 2 |

| 15 | 088888889 | 3 |

| Operation Type | State-of-the-Art Range Decoder | |||

|---|---|---|---|---|

| Multiply | 2 | 0 | 1 | 3 |

| Divide | 2 | 1 | 1 | 1 |

| Operation Type | State-of-the-Art Range Decoder | |||

|---|---|---|---|---|

| Multiply | 2 | 0 | 1 | 3 |

| Divide | 1 | 0 | 0 | 0 |

| 1-D Inverse DWT 5/3 Filter @ 85 °C Unrestricted Frequency | Convolution [27,28,29,30,31,32] | Lifting [33,34,35,36,37,38] | Proposed |

|---|---|---|---|

| Total logic elements | 234 | 120 | 120 |

| Total registers | 139 | 72 | 48 |

| Critical path delay [ns] | 5.4 | 8.2 | 5 |

| Max frequency [MHz] | 197.7 | 128 | 212 |

| Total power dissipation [mW] @ 80MHz | 132.4 | 134.4 | 130.9 |

| Architecture | On-Chip Memory Capacity | Off-Chip Memory Capacity |

|---|---|---|

| Non-separable [37] | 0 | |

| SIMD [37] | 0 | |

| Direct [38] | 0 | |

| Systolic-parallel [38] | 0 | |

| [28] | ||

| [40] | 0 | |

| [36] | 0 | |

| RA [39] | 0 | |

| FA [41] | ||

| PA [41] | 0 | |

| [42] | 0 | |

| [43] | 0 | |

| [44] | 0 | |

| [45] | ||

| [46] | ||

| [46] | 0 | |

| [47,48] | 0 | |

| Proposed | 0 |

| Parameter | Value |

|---|---|

| Number of logic elements | 77,127 |

| Memory size | 1,884,207 bits |

| Number of multipliers | 12 |

| Maximum operating frequency at 85 °C | 114.71 MHz |

| Architecture | Frame Size/ Tile Size | Memory Size [kbits] | Maximum Operating Frequency [MHz] |

|---|---|---|---|

| [1] | 160 × 120 | n/a | 24.15 |

| [2] | 512 × 512 | 1424 | 89.9 |

| [3] | 704 × 576 | 594 | 105.6 |

| [4] | 1920 × 1080 | 433,357 | 42.8 |

| [5] | 512 × 512 | 1602 | 116.9 |

| [6] | 2048 × 1080 | 2710 | n/a |

| [7] | 1920 × 1080 | 6192 | n/a |

| [8] | 1920 × 1080 | 5182 | 180 |

| [9] | 1920 × 1080 | 3277 | 110 |

| [10] 3 × 3 NoC | 320 × 200 | 1842 | n/a |

| [10] 2 × 2 NoC | 320 × 200 | 1125 | n/a |

| Proposed | 1920 × 1080 | 1840 | 114.71 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Savić, G.; Prokin, M.; Rajović, V.; Prokin, D. Digital Image Decoder for Efficient Hardware Implementation. Sensors 2022, 22, 9393. https://doi.org/10.3390/s22239393

Savić G, Prokin M, Rajović V, Prokin D. Digital Image Decoder for Efficient Hardware Implementation. Sensors. 2022; 22(23):9393. https://doi.org/10.3390/s22239393

Chicago/Turabian StyleSavić, Goran, Milan Prokin, Vladimir Rajović, and Dragana Prokin. 2022. "Digital Image Decoder for Efficient Hardware Implementation" Sensors 22, no. 23: 9393. https://doi.org/10.3390/s22239393

APA StyleSavić, G., Prokin, M., Rajović, V., & Prokin, D. (2022). Digital Image Decoder for Efficient Hardware Implementation. Sensors, 22(23), 9393. https://doi.org/10.3390/s22239393