Low Power CMOS-Based Hall Sensor with Simple Structure Using Double-Sampling Delta-Sigma ADC

Abstract

1. Introduction

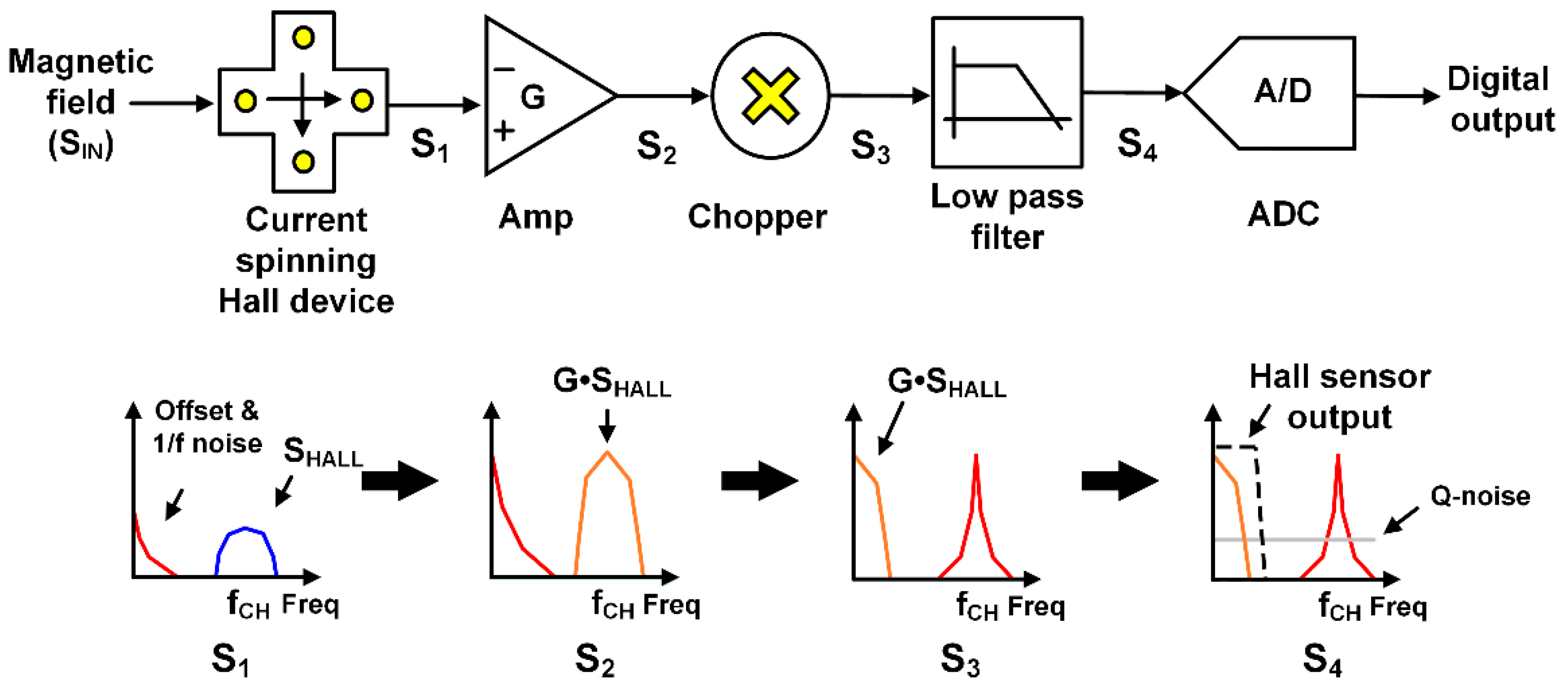

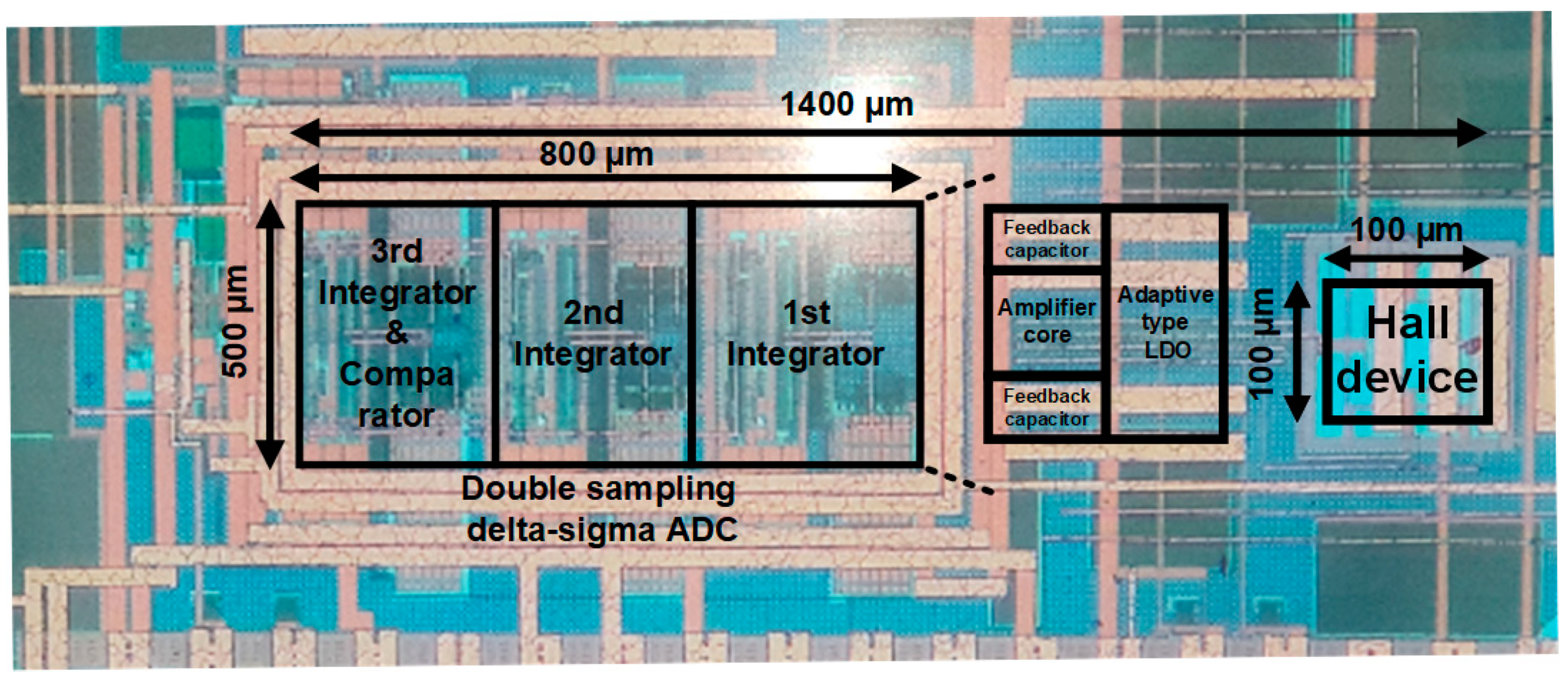

2. Proposed Hall Sensor Architecture

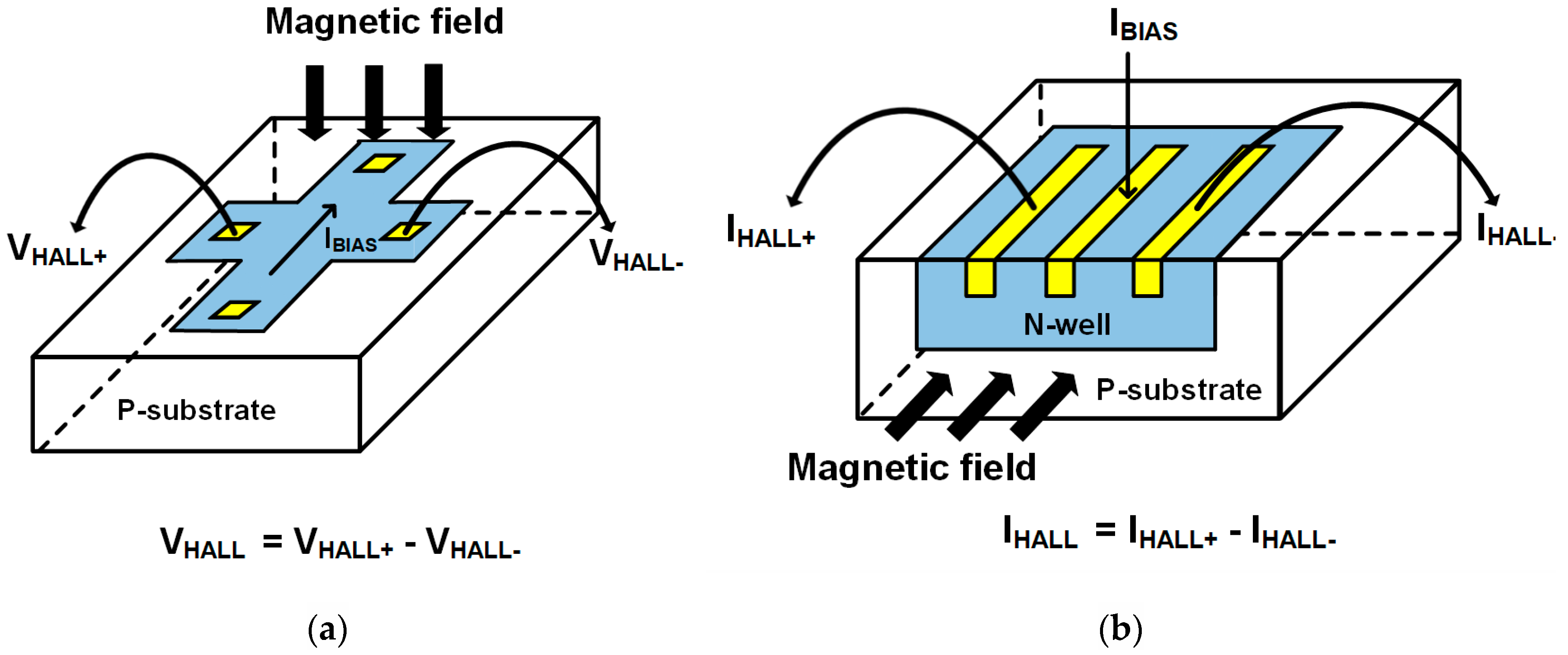

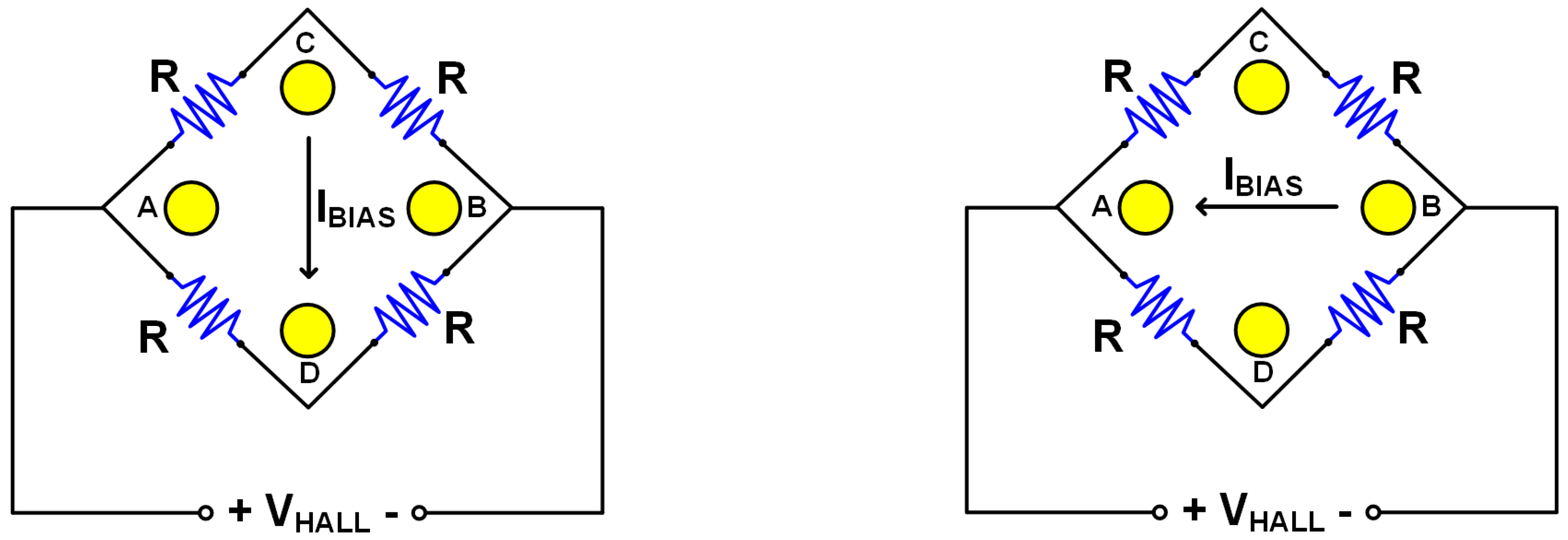

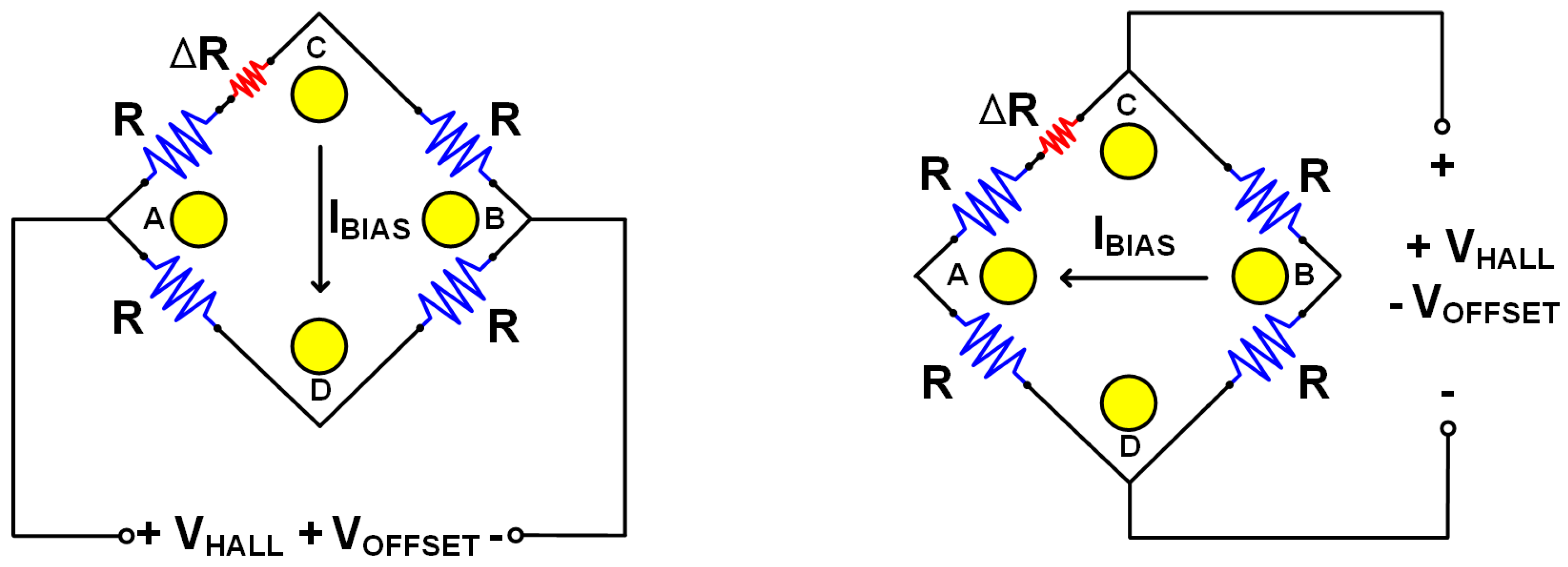

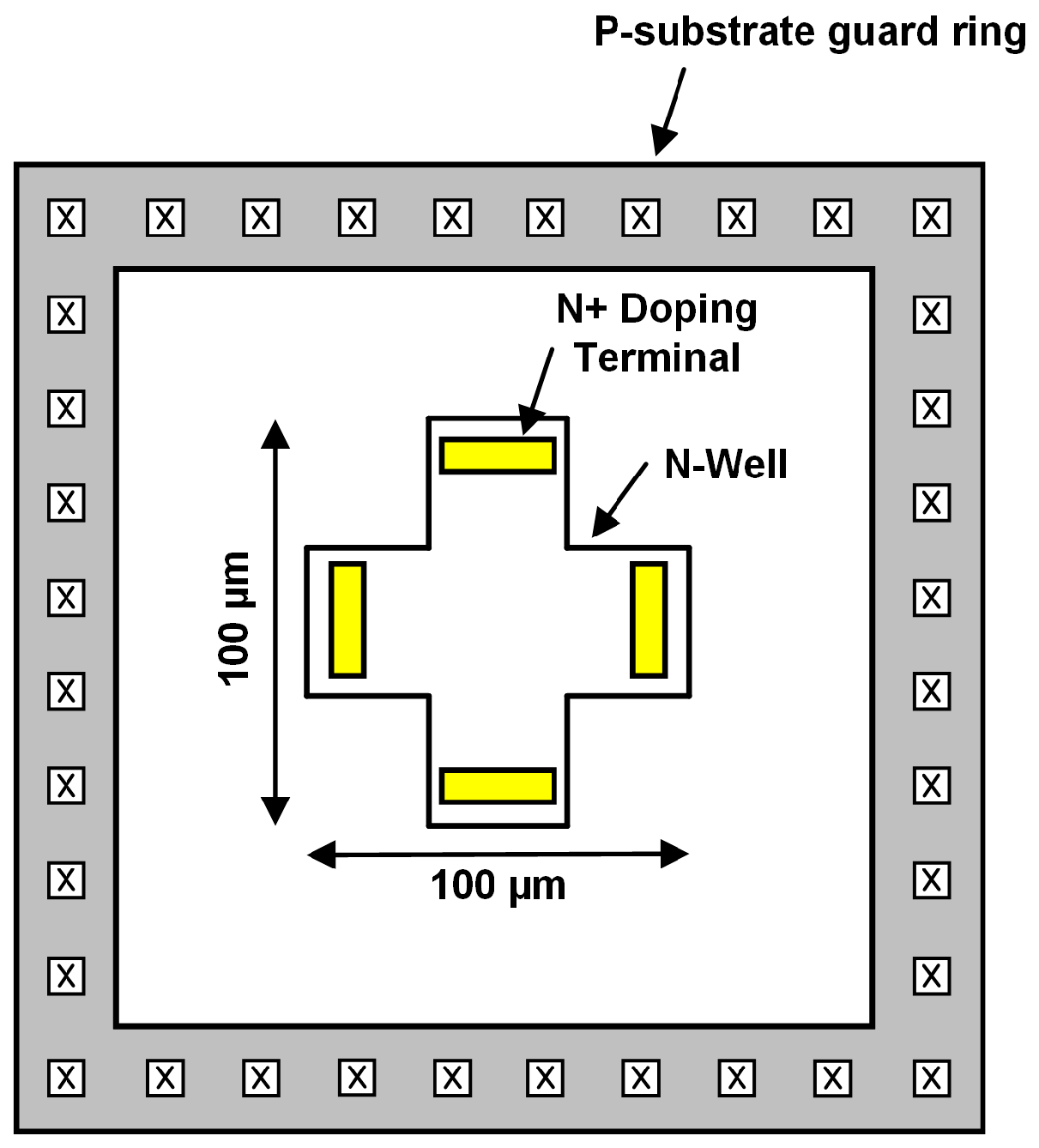

2.1. Hall Device Structure and Current Spinning

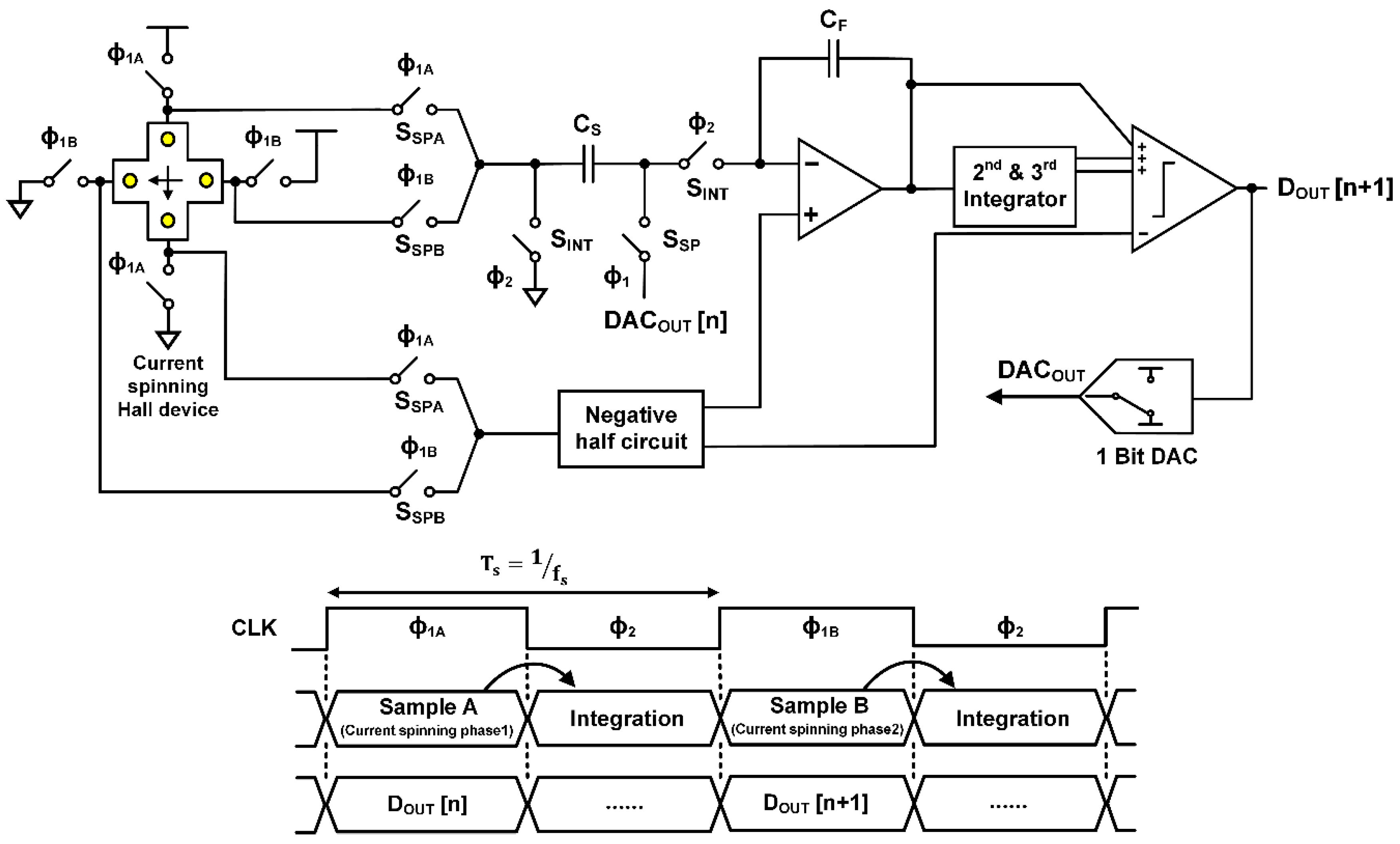

2.2. Directly Connected Hall Device and High-Resolution Discrete-Time Delta-Sigma ADC

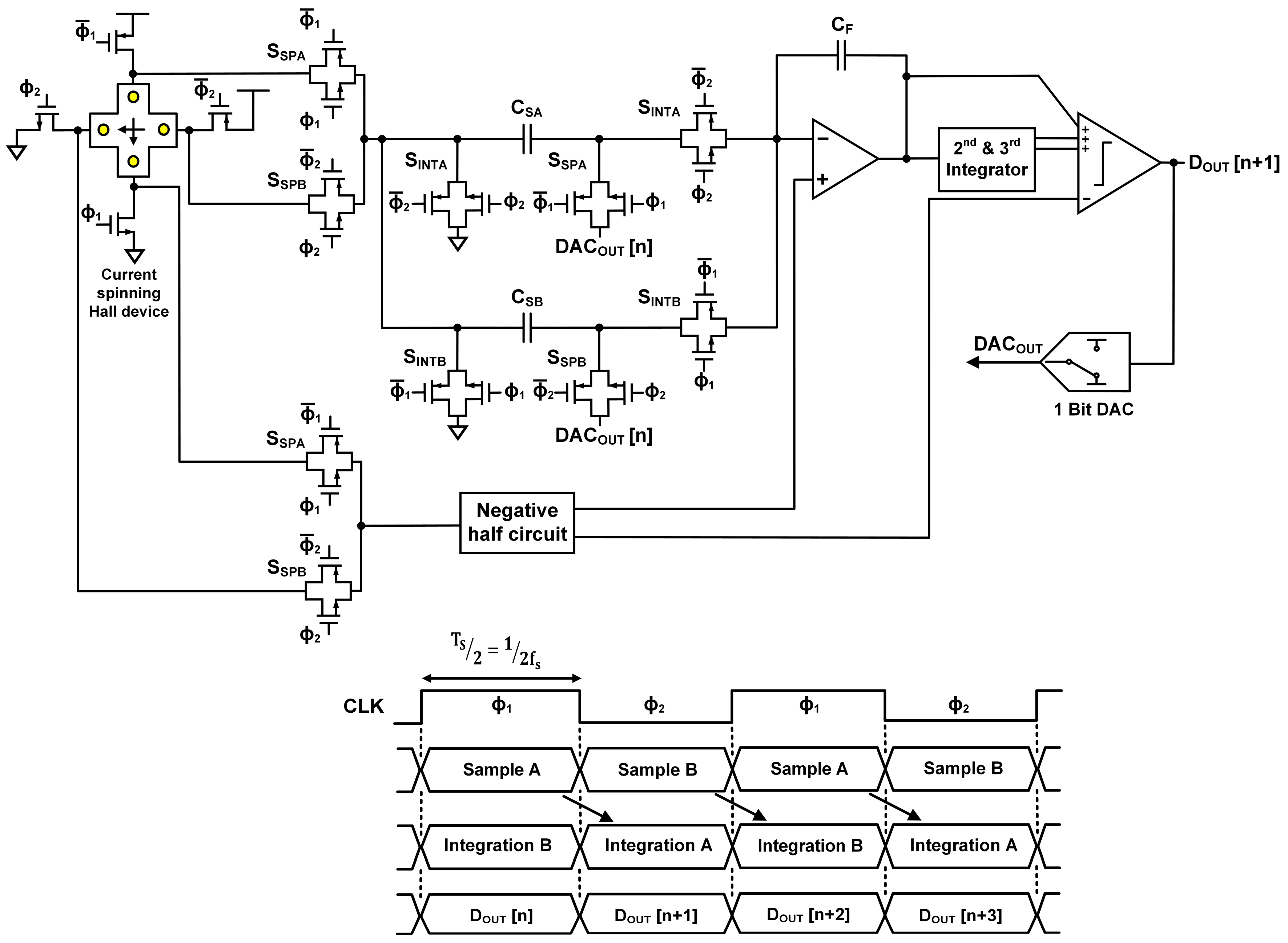

2.3. Double Sampling Delta-Sigma ADC

3. Circuit Implementation

3.1. Cross-Sectional Horizontal Hall Device

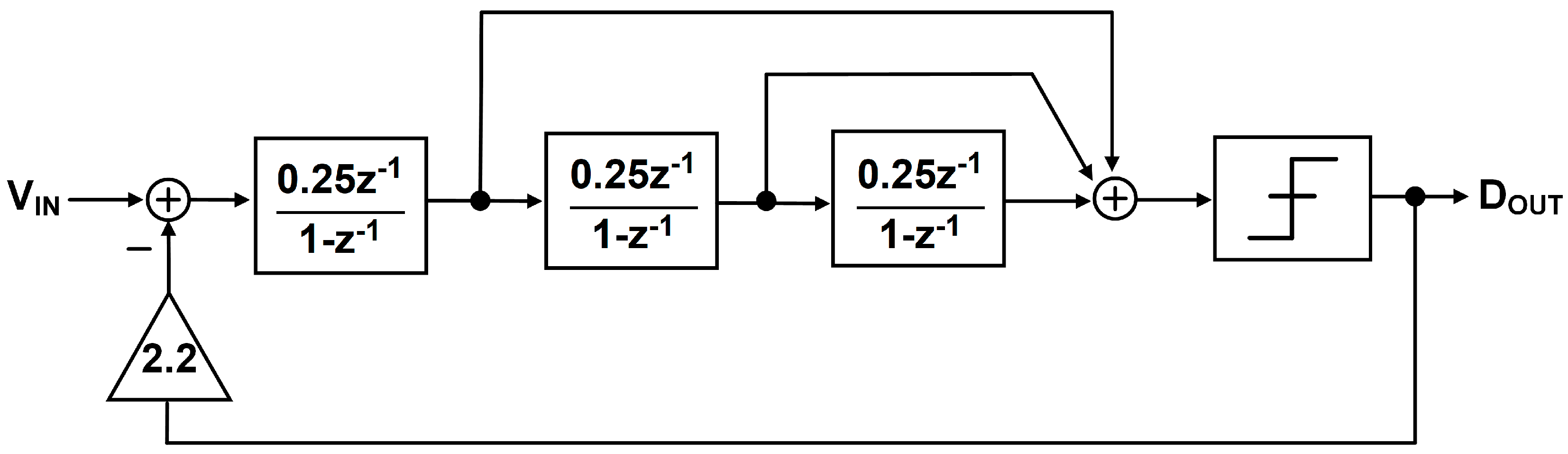

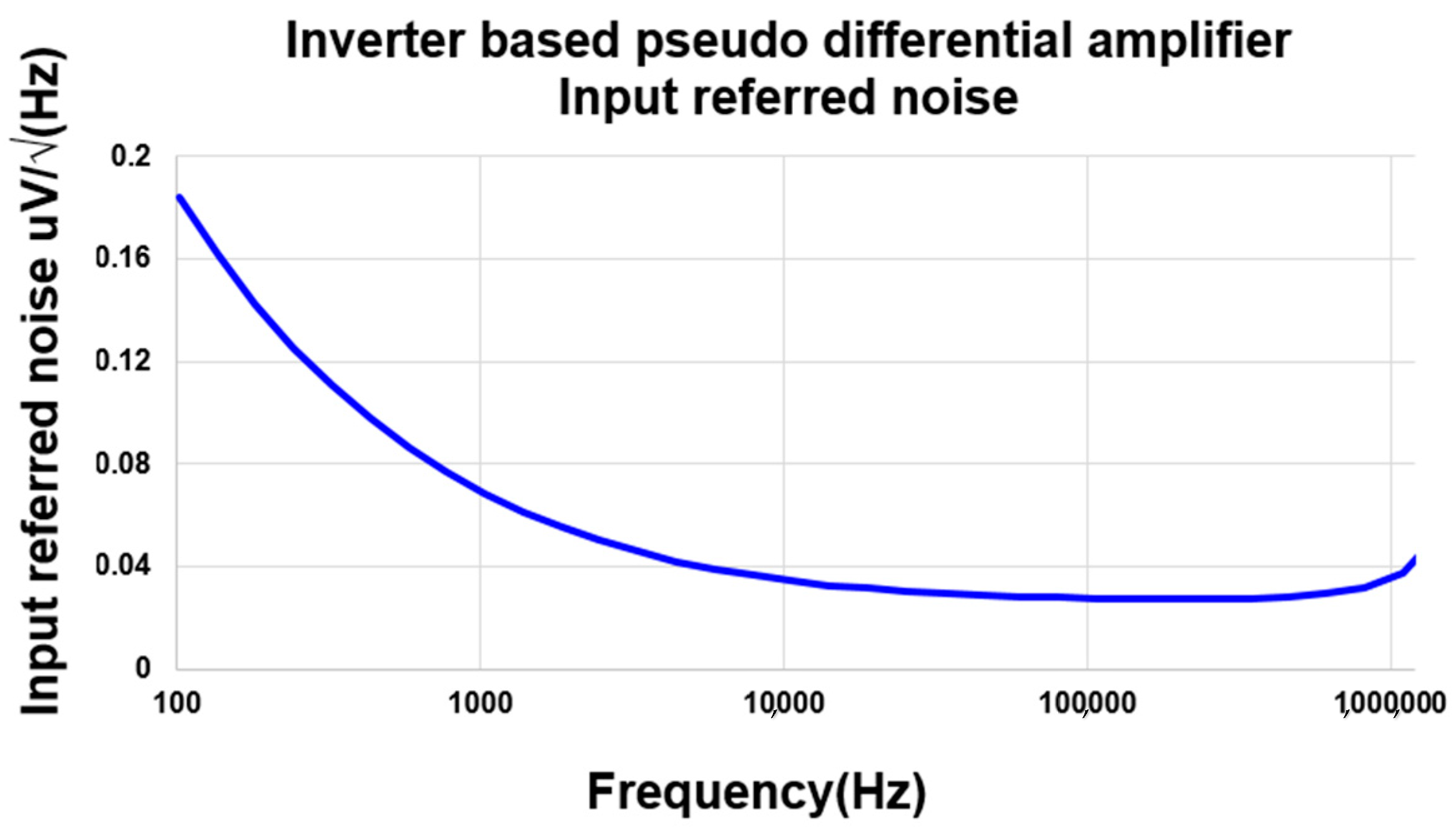

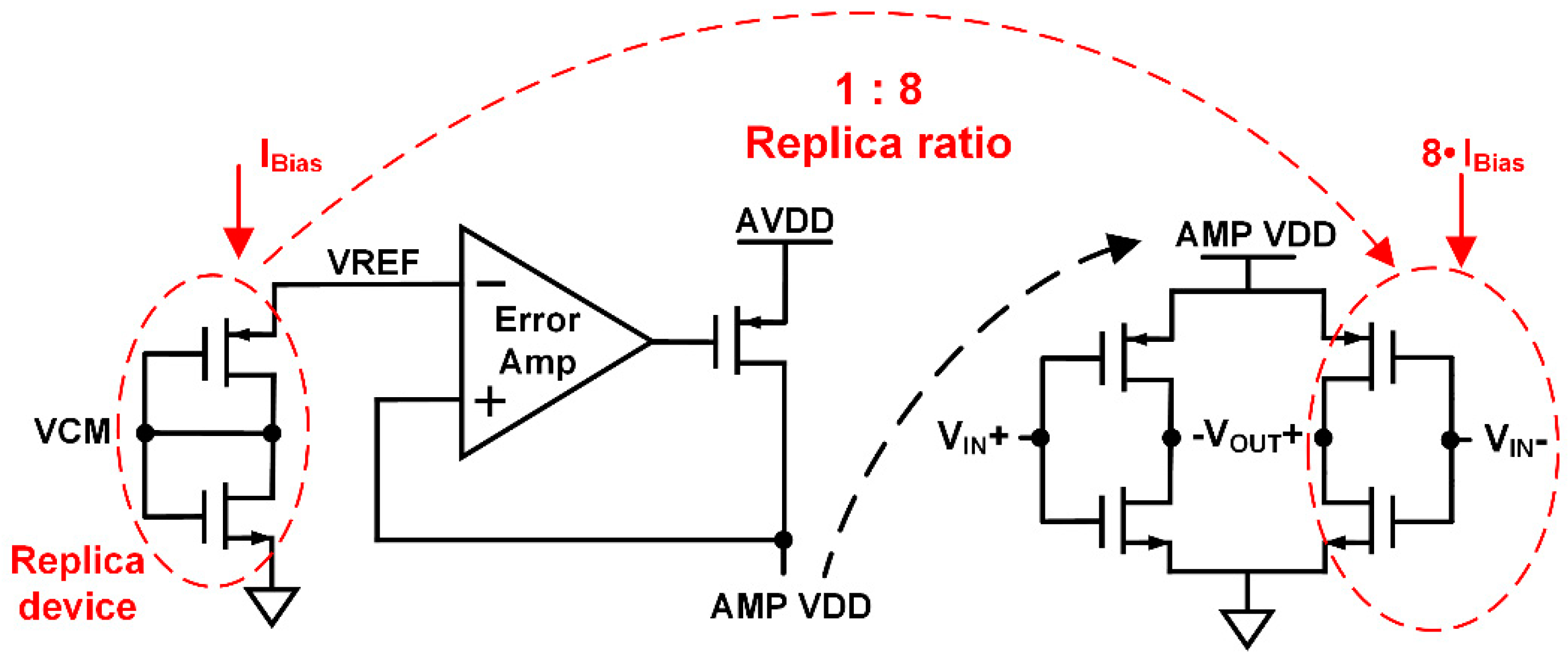

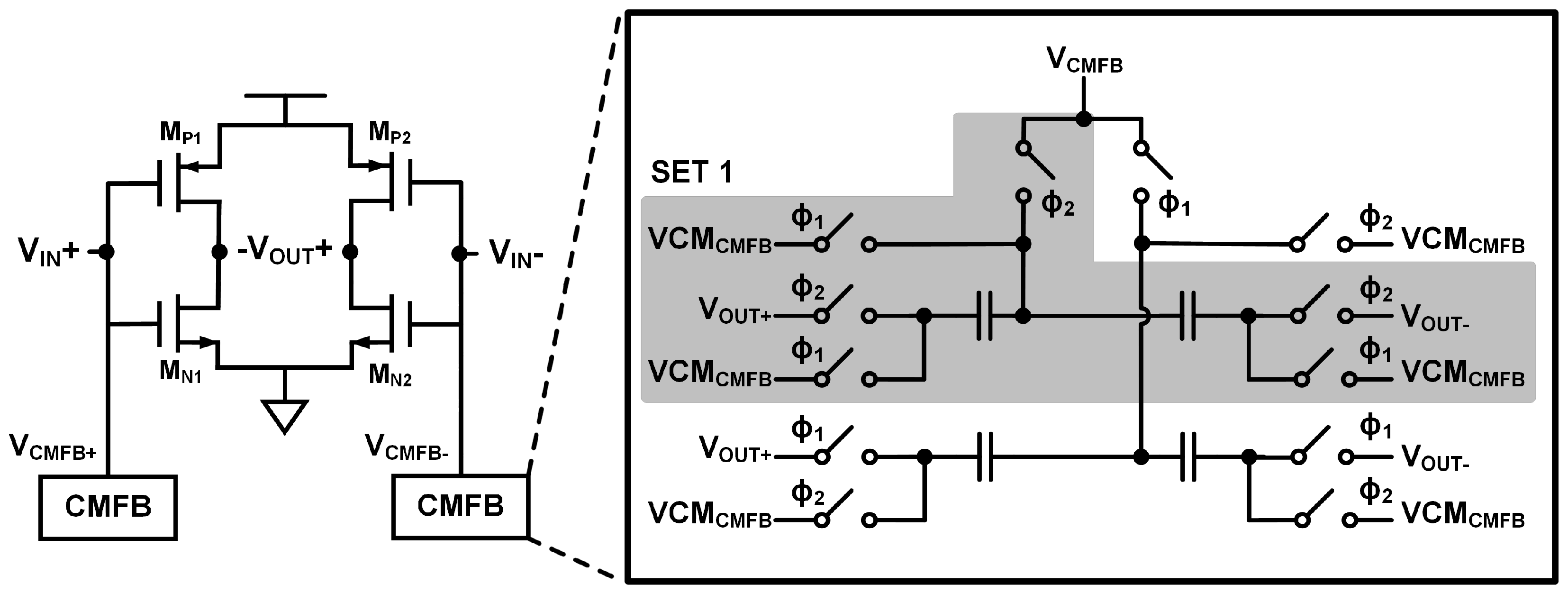

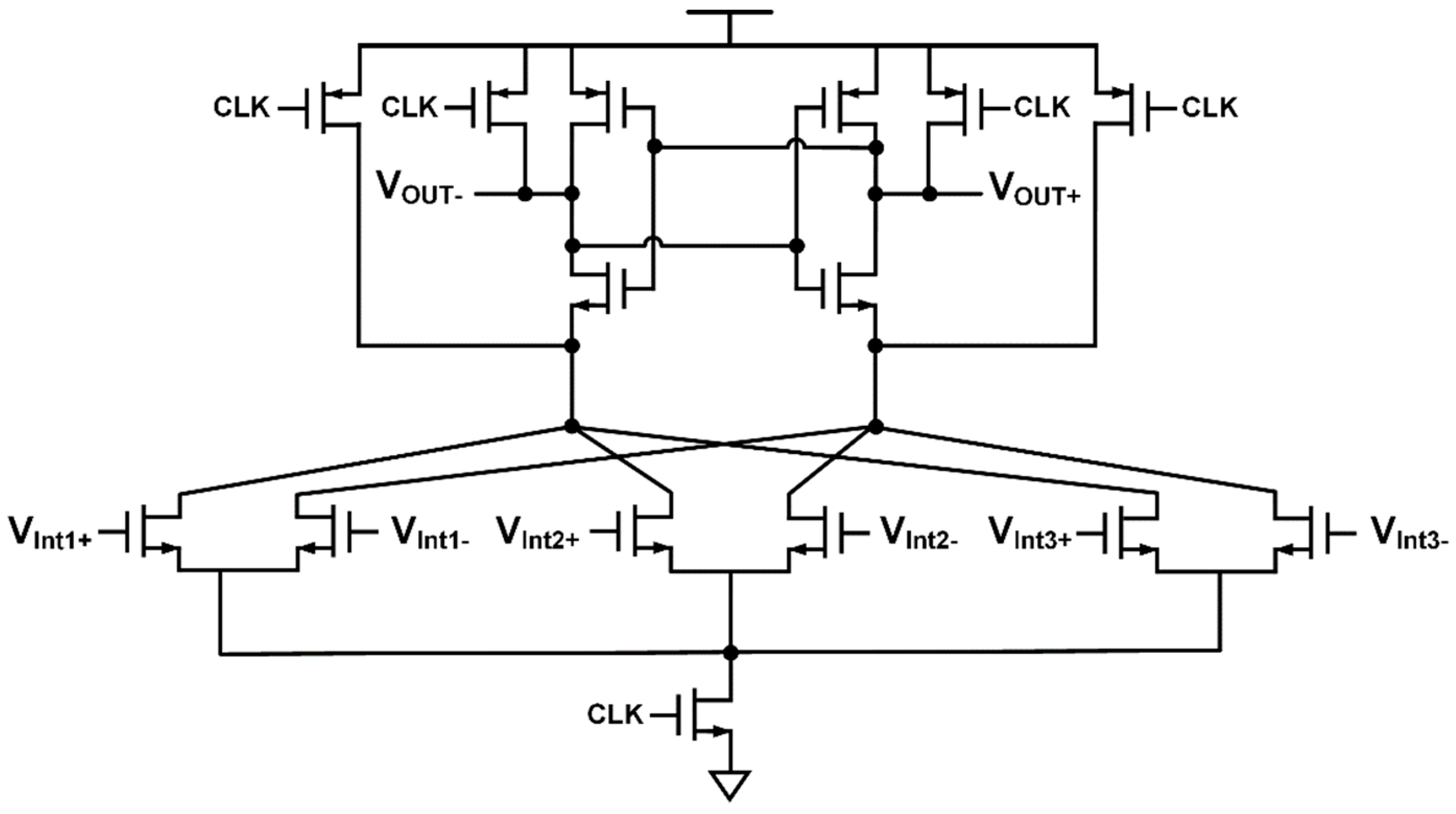

3.2. 3rd-Order Discrete-Time Delta-Sigma ADC

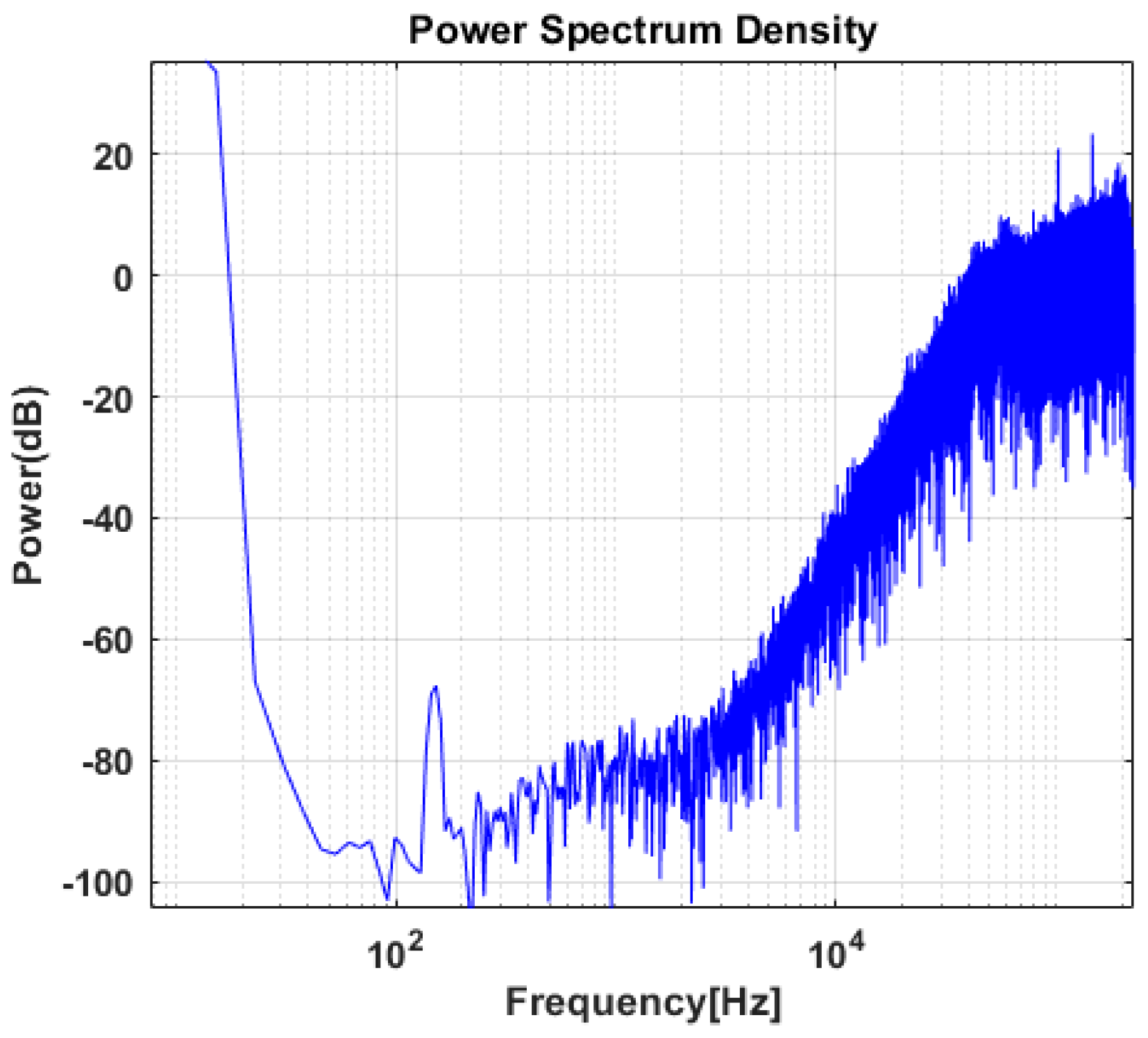

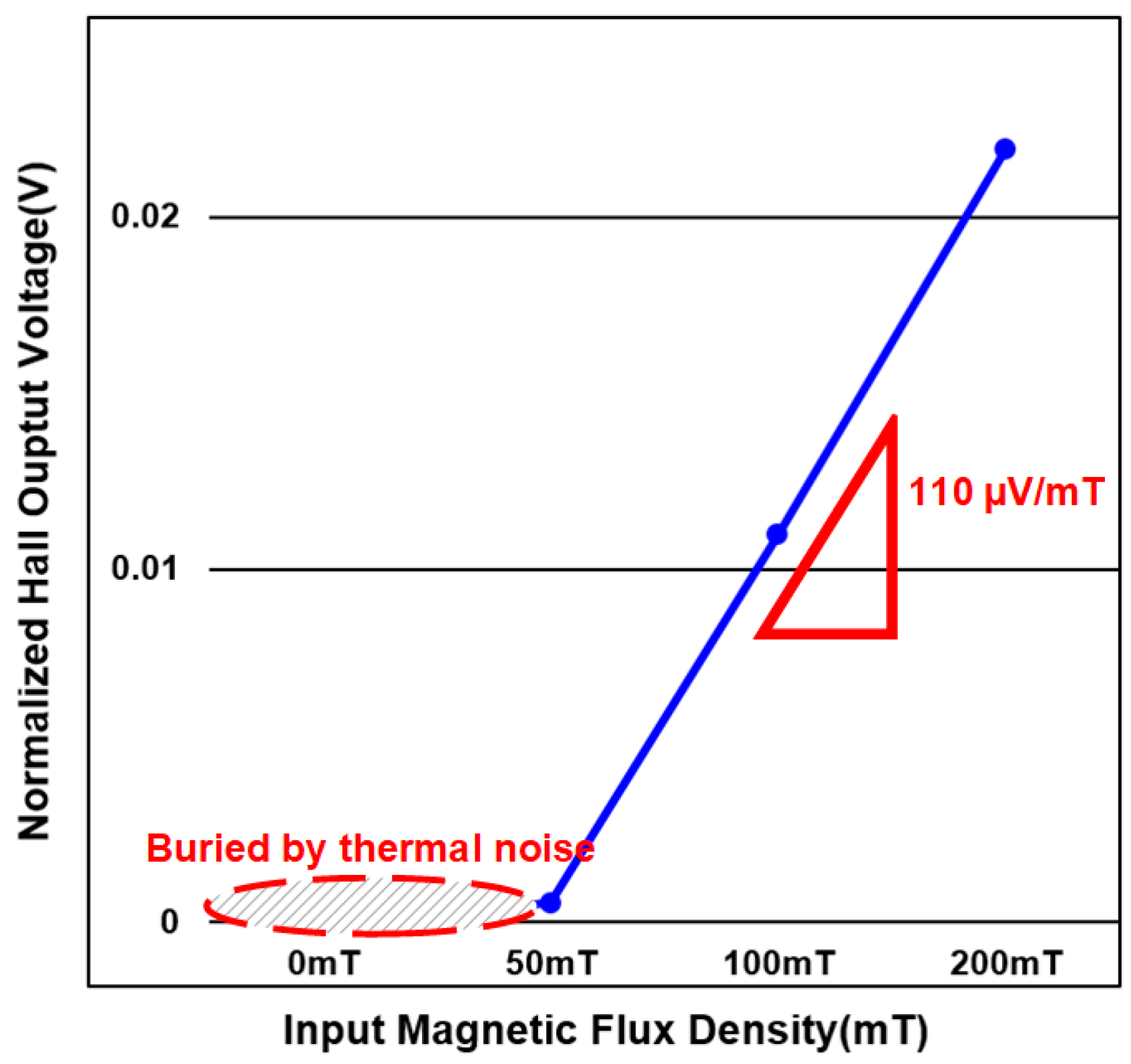

4. Results

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Ajbl, A.; Pastre, M.; Kayal, M. A Fully Integrated Hall Sensor Microsystem for Contactless Current Measurement. IEEE Sens. J. 2013, 13, 2271–2278. [Google Scholar] [CrossRef]

- Huber, S.; Leten, W.; Ackermann, M.; Schott, C.; Paul, O. A Fully Integrated Analog Compensation for the Piezo-Hall Effect in a CMOS Single-Chip Hall Sensor Microsystem. IEEE Sens. J. 2014, 15, 2924–2933. [Google Scholar] [CrossRef]

- Randjelovic, Z.B.; Kayal, M.; Popovic, R.; Blanchard, H. Highly sensitive Hall magnetic sensor microsystem in CMOS technology. IEEE J. Solid State Circuits 2002, 37, 151–159. [Google Scholar] [CrossRef]

- Bellekom, S. CMOS versus bipolar Hall plates regarding offset correction. Sens. Actuators 1999, 76, 178–182. [Google Scholar] [CrossRef]

- Oh, S.; Jang, B.; Chae, H. Sensitivity Enhancement of a Vertical-Type CMOS Hall Device for a Magnetic Sensor. J. Electromagn. Eng. Sci. 2018, 18, 35–40. [Google Scholar] [CrossRef]

- Ramirez, J.; Fruett, F. Offset reduction in a multiple-terminal Hall plate using current spinning. In Proceedings of the IEEE IberoAmerican Congress on Sensors, Bogota, Columbia, 15–18 October 2014. [Google Scholar]

- Oh, S.; Hwang, D.; Chae, H. 4-Contact Structure of Vertical-Type CMOS Hall Device for 3-D Magnetic Sensor. IEICE Electron. Express 2019, 16, 1–10. [Google Scholar] [CrossRef]

- Bilotti, A.; Monreal, G.; Vig, R. Monolithic Magnetic Hall Sensor Using Dynamic Quadrature Offset Cancellation. IEEE J. Solid State Circuits 1997, 32, 829–836. [Google Scholar] [CrossRef]

- Min, Y.; Kwon, C.; Kim, H.; Kim, C.; Kim, S. A CMOS Magnetic Hall Sensor Using a Switched Biasing Amplifier. IEEE Sens. J. 2012, 12, 1195–1196. [Google Scholar] [CrossRef]

- Andrew, T. A 3µV-Offset Operational Amplifier with 20n V/√Hz Input Noise PSD at DC Employing both Chopping and Autozeroing. In Proceedings of the IEEE International Solid-State Circuits Conference. Digest of Technical Papers, San Francisco, CA, USA, 7–11 August 2002. [Google Scholar]

- Enz, C.; Temes, G. Circuit techniques for reducing the effects of op-amp imperfections: Autozeroing, correlated double sampling, and chopper stabilization. Proc. IEEE 1996, 84, 1584–1614. [Google Scholar] [CrossRef]

- Yang, W.; Ran, F. CMOS Chopper Amplifier for Monolithic Magnetic Hall Sensor. In Proceedings of the International Conference on ASIC, Guilin, China, 22–25 October 2007. [Google Scholar]

- Lee, C.; Chien, C. Design and Fabrication of Micro-Hall-Effect Sensors. In Proceedings of the International Conference on Sensing Technology, Limerick, Ireland, 4–6 December 2018. [Google Scholar]

- Ronis, N.; Garcia-Inza, M. Design and characterization of Hall plates in 0.5um CMOS process. In Proceedings of the Argentine Conference of Micro-Nanoelectronics, Technology and Applications, Neuquen, Argentina, 4–5 August 2016. [Google Scholar]

- Choi, Y.; Roh, H.; Nam, H.; Roh, J. 99-dB High-performance Delta-sigma Modulator for 20-kHz Bandwidth. In Proceedings of the IEEE International Symposium on Electronic Design, Test and Application, Hong Kong, China, 23–25 January 2008. [Google Scholar]

- Rabii, S.; Wooley, B. A 1.8V Digital-Audio Sigma-Delta Modulator in 0.8um CMOS. IEEE J. Solid State Circuits 1997, 32, 783–796. [Google Scholar] [CrossRef]

- Roh, J.; Byun, S.; Choi, Y.; Roh, H.; Kim, Y.; Kwon, J. A 0.9-V 60-uW 1-Bit Fourth-Order Delta-Sigma Modulator with 83-dB Dynamic Range. IEEE J. Solid State Circuits 2008, 43, 361–370. [Google Scholar] [CrossRef]

- Kim, M.; Ahn, G.; Hanumolu, P.; Lee, S.; Kim, S.; You, S.; Temes, G.; Moon, U. A 0.9V 92dB Double-Sampled Switched-RC Delta-Sigma Audio ADC. IEEE J. Solid State Circuits 2008, 43, 1195–1206. [Google Scholar] [CrossRef]

- Yue, M.; Wu, D.; Wang, Z. Data Compression for Image Sensor Arrays Using a 15-bit Two-Step Sigma-Delta ADC. IEEE Sens. J. 2014, 14, 2989–2998. [Google Scholar]

- Wu, D.; Gao, C.; Liu, H.; Xie, N. A Low Power Double-Sampling Extended Counting ADC With Class-AB OTA for Sensor Arrays. IEEE Trans. Circuits Syst. I Regul. Pap. 2015, 62, 29–38. [Google Scholar] [CrossRef]

- Su, P.; Chiueh, H. The Design of Low-Power CIFF Structure Second-Order Sigma-Delta Modulator. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems, Cancun, Mexico, 2–5 August 2009. [Google Scholar]

- Chae, Y.; Han, G. Low Voltage, Low Power, Inverter-Based Switched-Capacitor Delta-Sigma Modulator. IEEE J. Solid State Circuits 2009, 42, 458–472. [Google Scholar] [CrossRef]

- Suadet, A.; Kasemsuwan, V. A CMOS inverter-based class-AB pseudo differential amplifier for HF applications. In Proceedings of the IEEE International Conference of Electron Devices and Solid-State Circuits, Hong Kong, China, 15–17 December 2010. [Google Scholar]

- Su, C.; Lin, P.; Lu, H. An Inverter Based 2-MHz 42-uW ΔΣ ADC with 20-KHz Bandwidth and 66dB Dynamic Range. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Hangzhou, China, 13–15 November 2006. [Google Scholar]

- Grasso, A.; Pennisi, S. High-Performance CMOS Pseudo-Differential Amplifier. In Proceedings of the IEEE International Symposium on Circuits and Systems, Kobe, Japan, 23–26 May 2005. [Google Scholar]

- Basu, J.; Mandal, P. Effect of Switched-Capacitor CMFB on the Gain of Fully Differential Op-Amp for Design of Integrators. In Proceedings of the IEEE International Symposium on Circuits and Systems, Florence, Italy, 27–30 May 2018. [Google Scholar]

- Liu, C.; Chang, S.; Huang, G.; Lin, Y. A 10-bit 50-MS/s SAR ADC with a Monotonic Capacitor Switching Procedure. IEEE J. Solid State Circuits 2010, 45, 731–740. [Google Scholar] [CrossRef]

- van der Meer, J.C.; Riedijk, F.R.; van Kampen, E.; Makinwa, K.A.A.; Huijsing, J.H. A fully integrated CMOS Hall sensor with a 3.65μT 3σ offset for compass applications. In Proceedings of the IEEE International Digest of Technical Papers. Solid-State Circuits Conference, San Francisco, CA, USA, 10 February 2005. [Google Scholar]

- Huang, H.; Wang, D.; Xu, Y. A Monolithic CMOS Magnetic Hall Sensor with High Sensitivity and Linearity Characteristics. Sensors 2015, 15, 27359–27373. [Google Scholar] [CrossRef] [PubMed]

| Parameter | [28] | [29] | This Work |

|---|---|---|---|

| Technology | CMOS 0.5 µm | CMOS 0.8 µm | CMOS 0.18 µm |

| Supply Voltage | 5 V | 5 V | 2.2 V |

| Power Consumption | 21 mW | 20 mW | 4.9 mW |

| Measurement Range | ±10.8 mT | ±175 mT | ±150 mT |

| Offset | 3.65 µT | 0.48 mT | 16 µT |

| Linearity | N/A | >99% | >99% |

| Area | 2.9 mm2 | 1 mm2 | 0.7 mm2 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Lee, J.; Oh, Y.; Oh, S.; Chae, H. Low Power CMOS-Based Hall Sensor with Simple Structure Using Double-Sampling Delta-Sigma ADC. Sensors 2020, 20, 5285. https://doi.org/10.3390/s20185285

Lee J, Oh Y, Oh S, Chae H. Low Power CMOS-Based Hall Sensor with Simple Structure Using Double-Sampling Delta-Sigma ADC. Sensors. 2020; 20(18):5285. https://doi.org/10.3390/s20185285

Chicago/Turabian StyleLee, Juyong, Younggyun Oh, Sein Oh, and Hyungil Chae. 2020. "Low Power CMOS-Based Hall Sensor with Simple Structure Using Double-Sampling Delta-Sigma ADC" Sensors 20, no. 18: 5285. https://doi.org/10.3390/s20185285

APA StyleLee, J., Oh, Y., Oh, S., & Chae, H. (2020). Low Power CMOS-Based Hall Sensor with Simple Structure Using Double-Sampling Delta-Sigma ADC. Sensors, 20(18), 5285. https://doi.org/10.3390/s20185285