Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for SpaceFibre Applications †

Abstract

1. Introduction

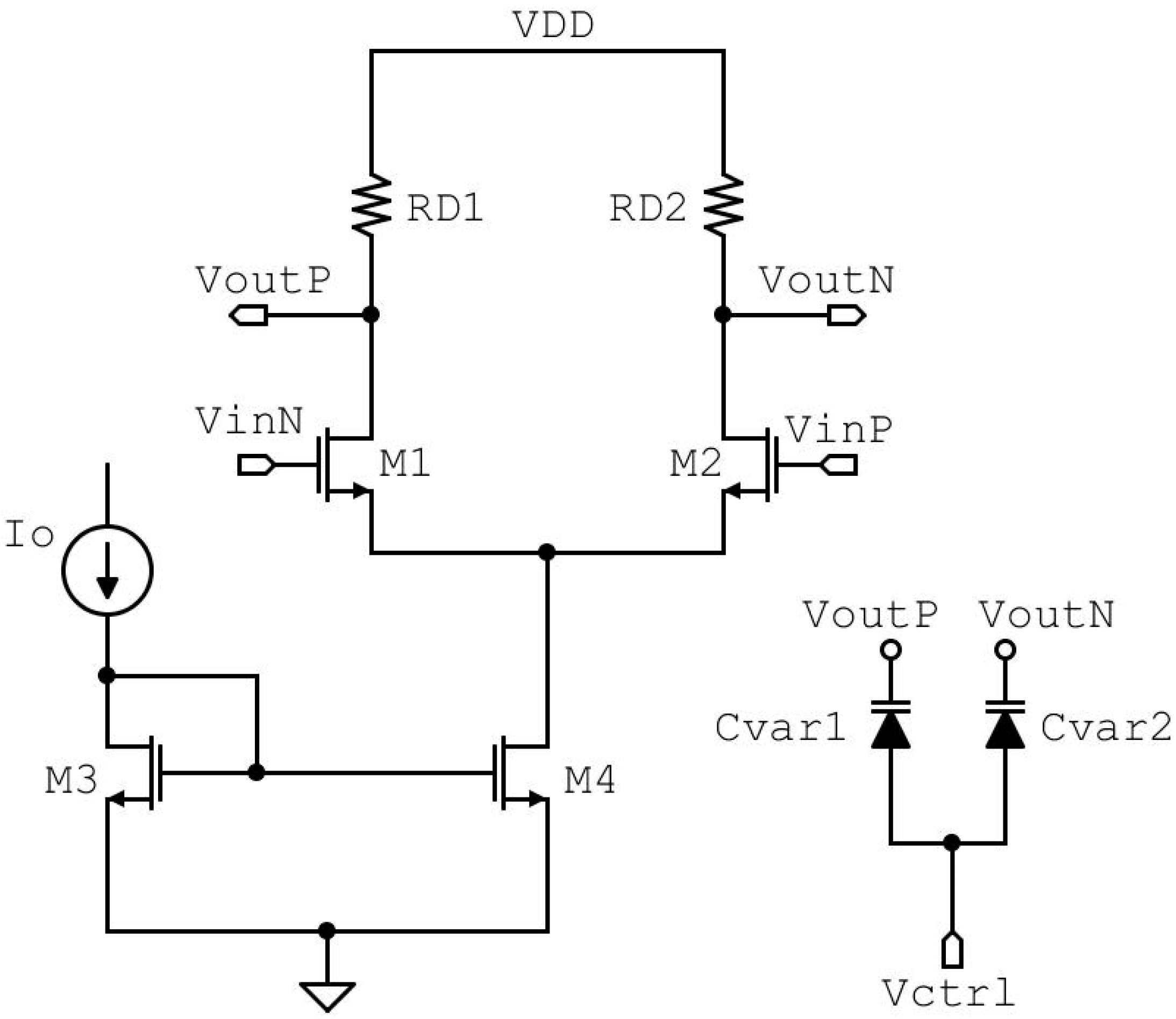

2. Ring Oscillator Based on a Cascade of Three Current Mode Logic (CML) Buffer

2.1. Ring Oscillator Schematic Design

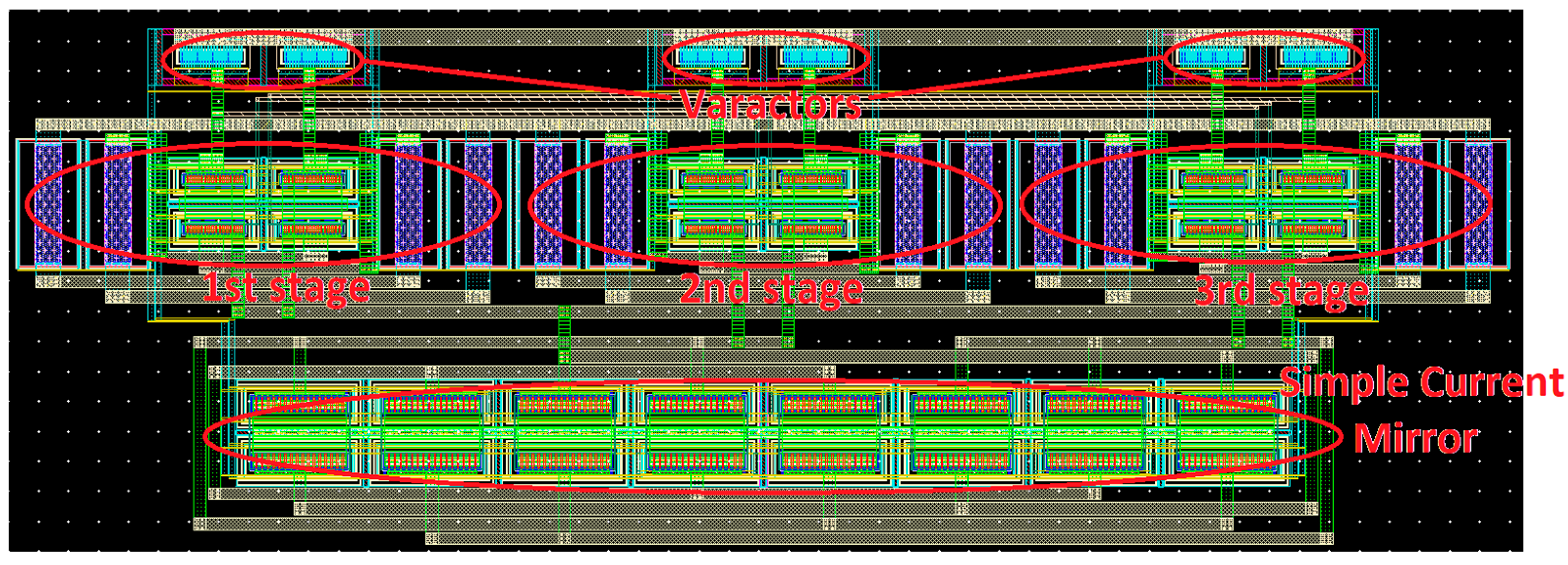

2.2. Ring Oscillator Layout Design

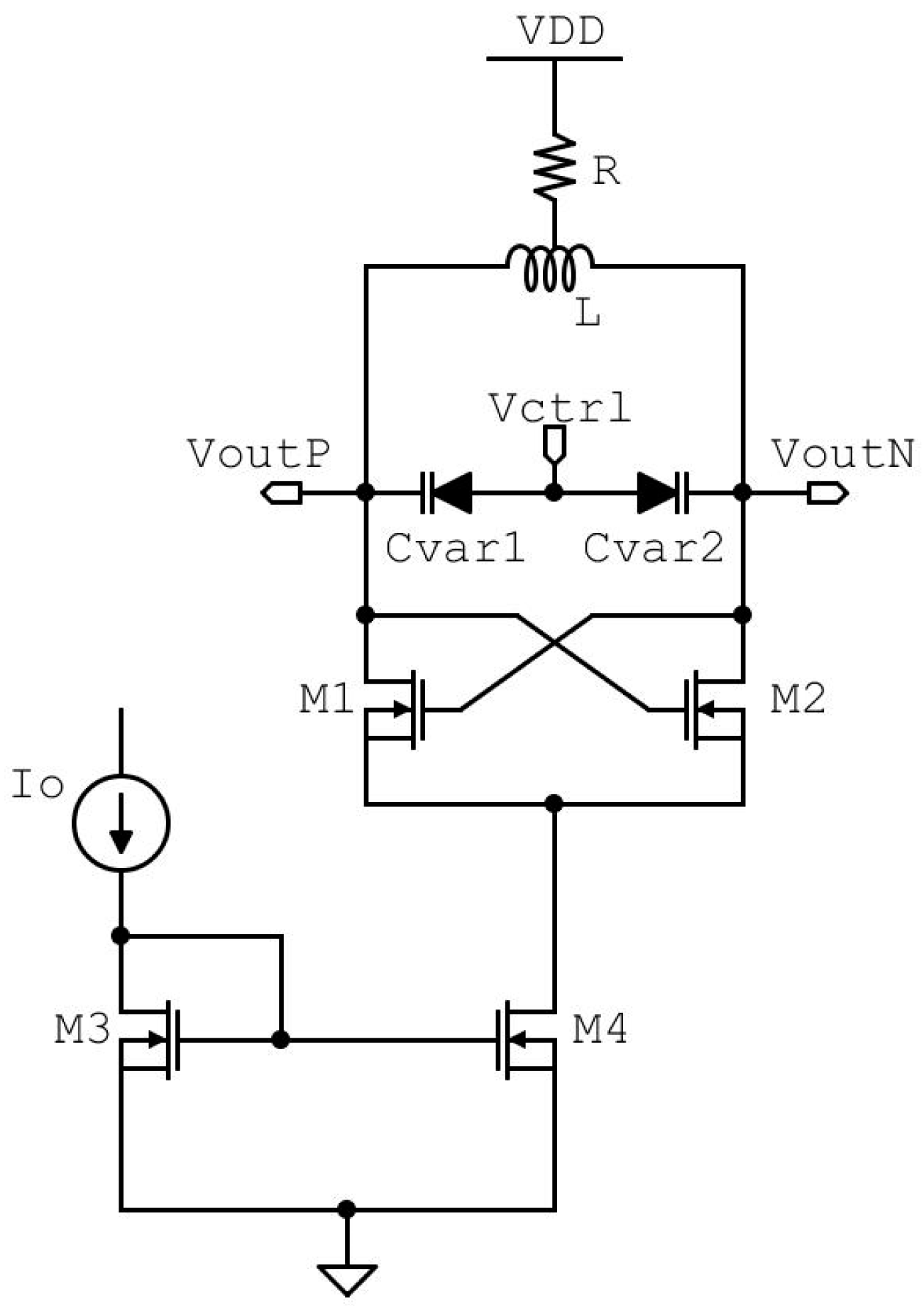

3. LC-Tank Oscillator

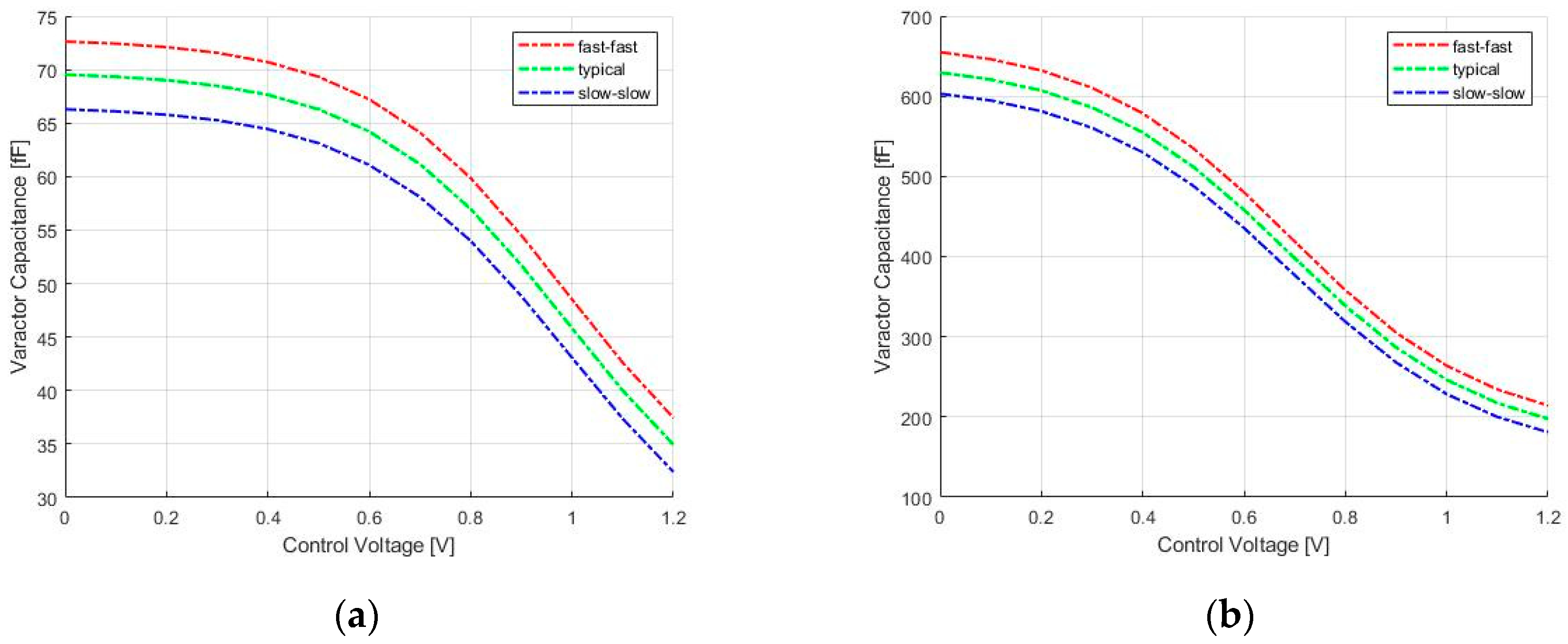

3.1. LC-Tank Schematic Design

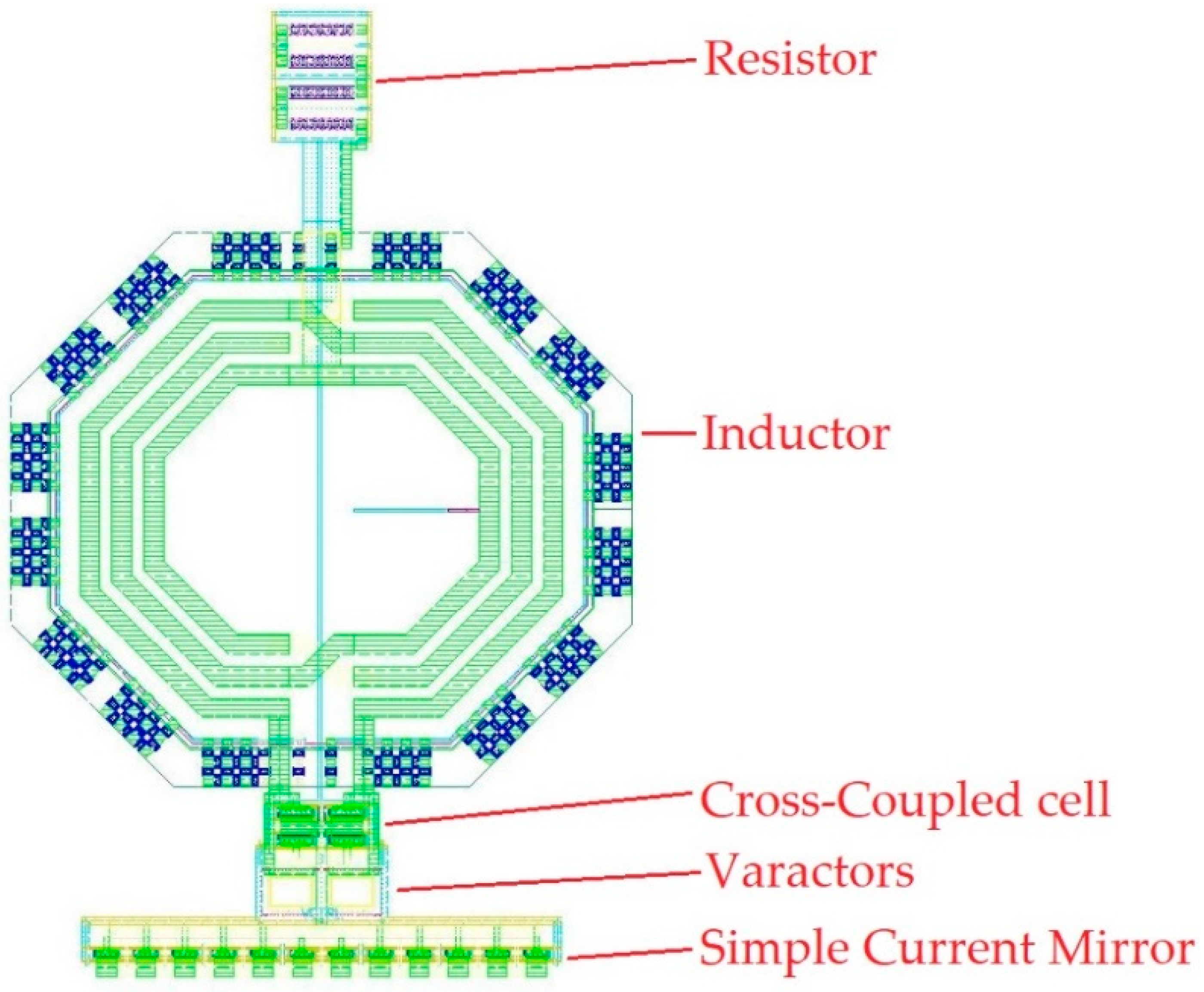

3.2. LC-Tank Layout Design

4. Simulations Results

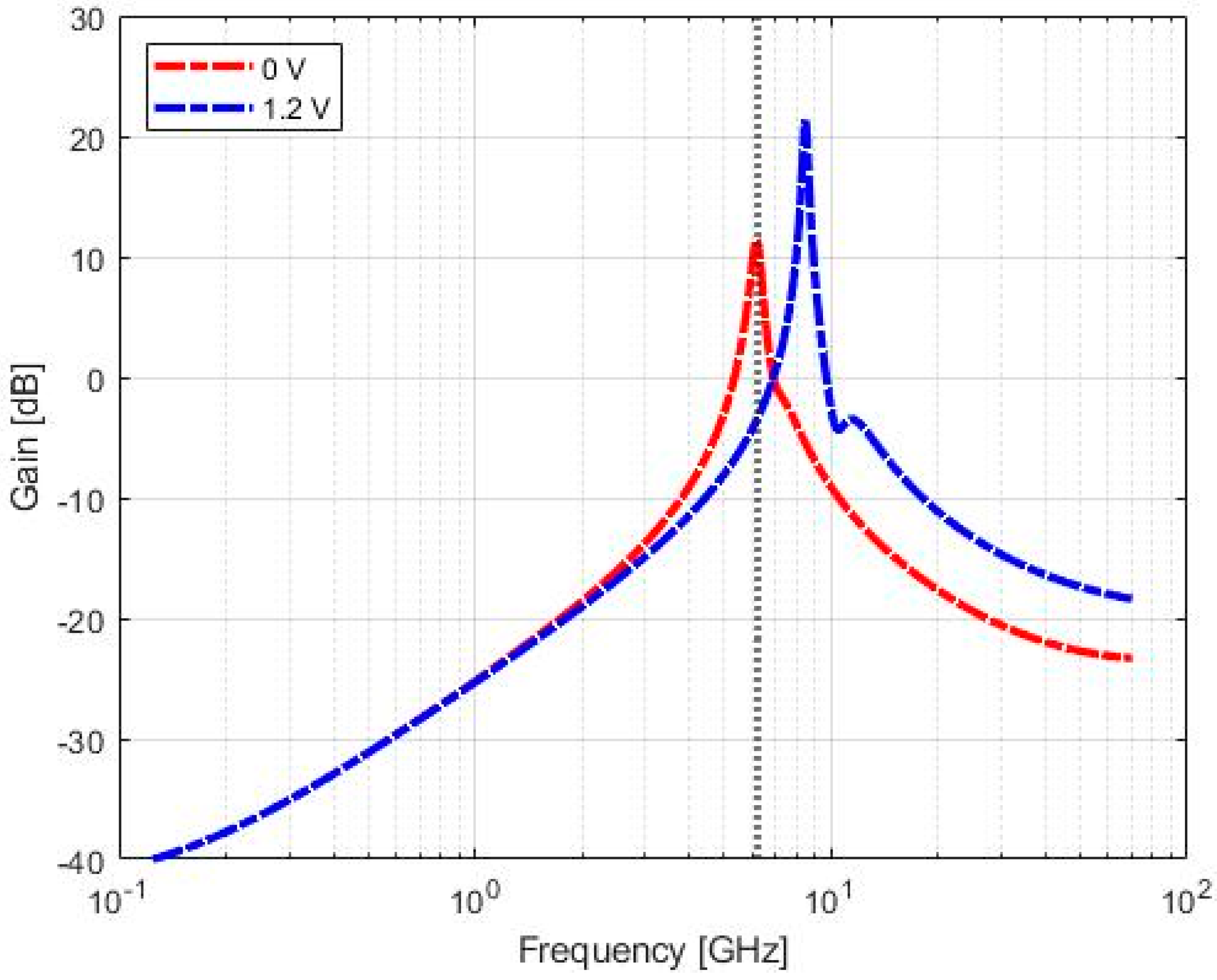

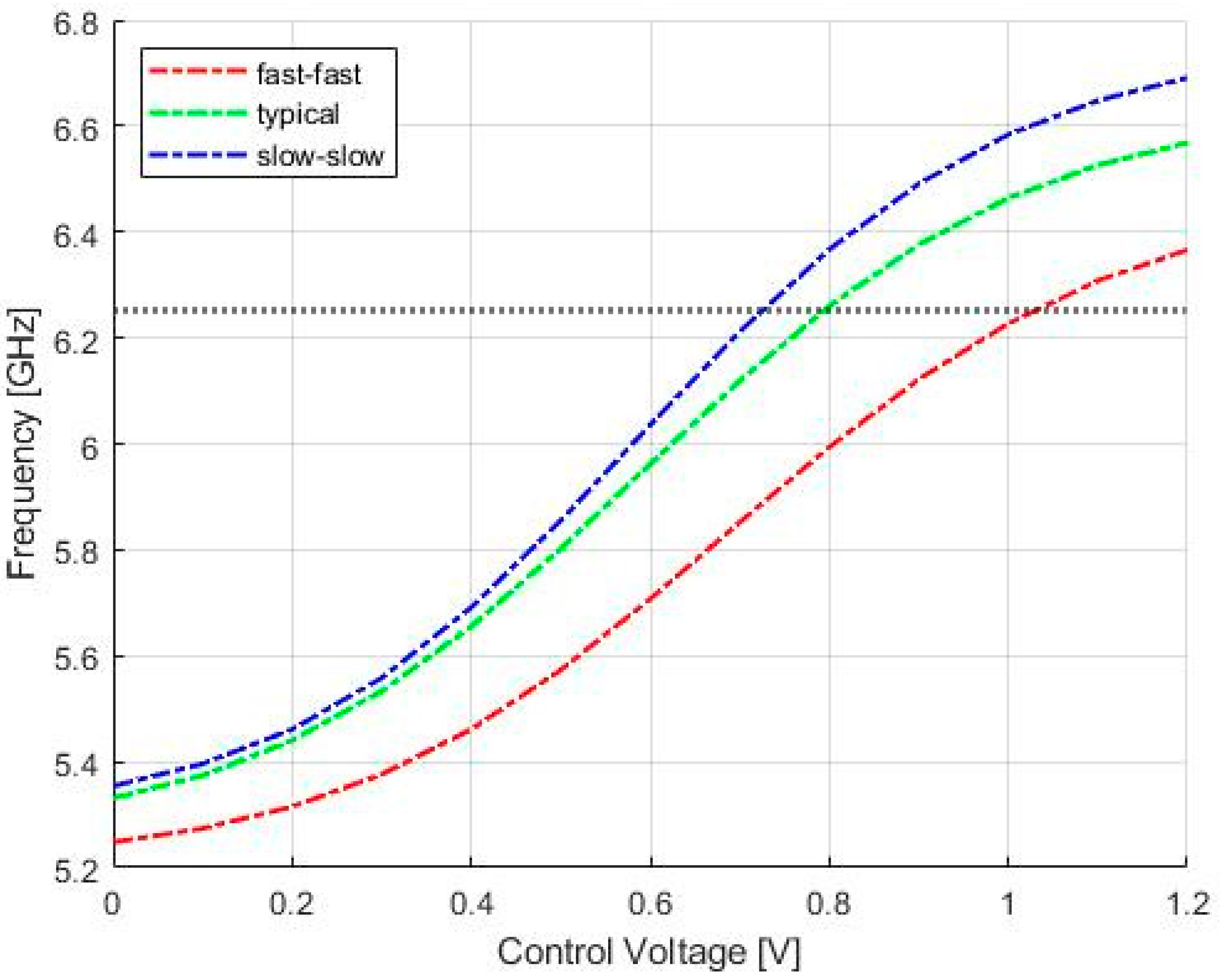

4.1. Design Simulations

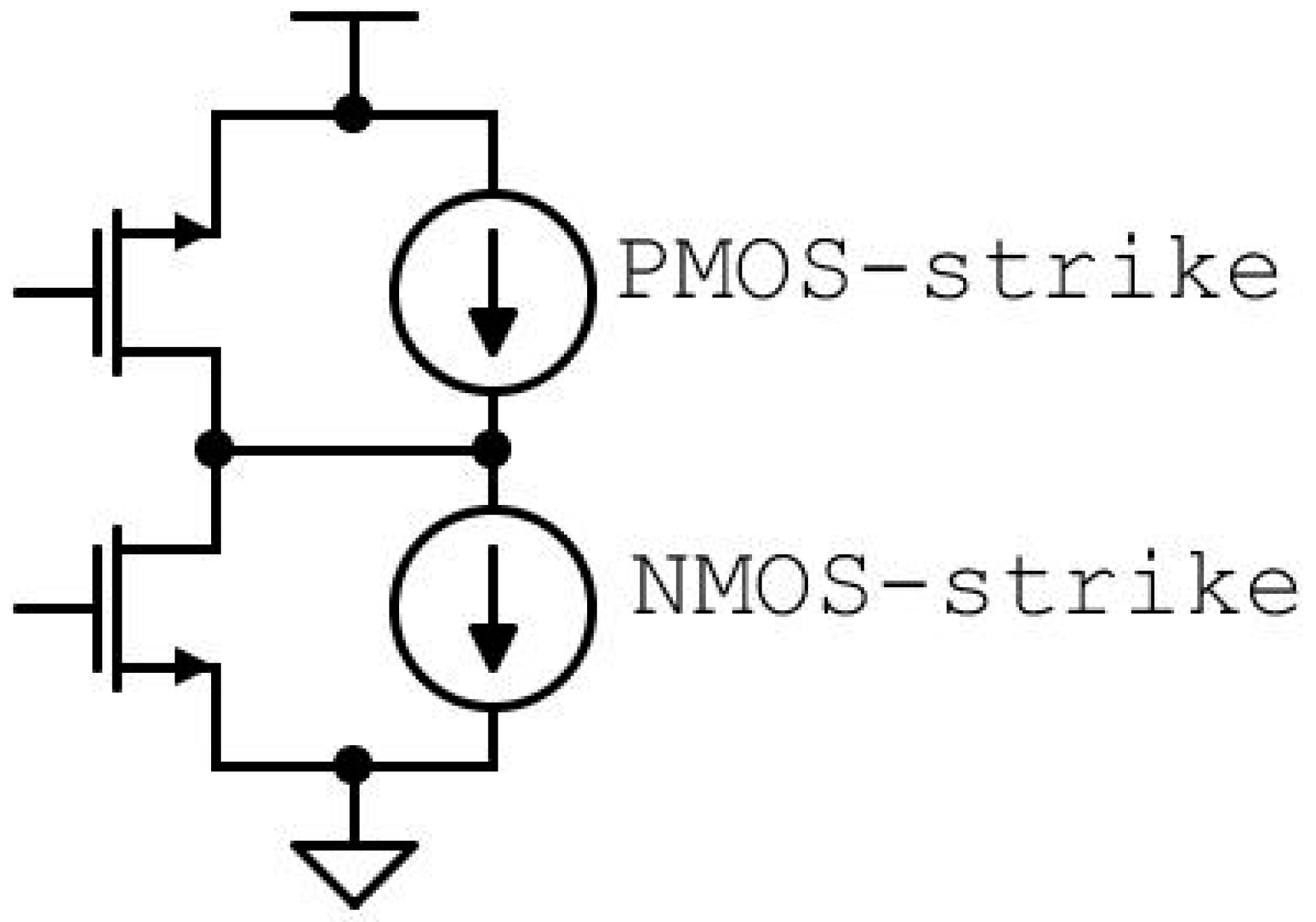

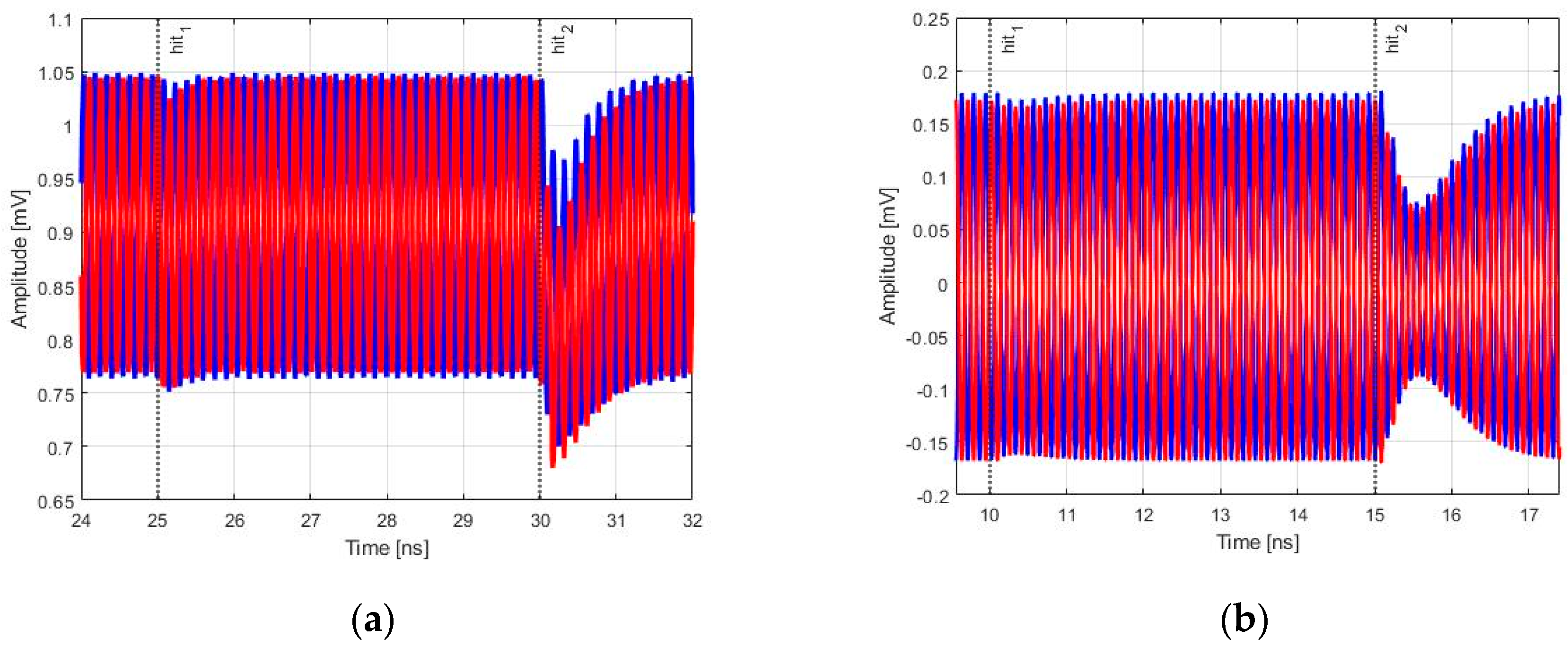

4.2. Single Event Effect Simulations

5. Comparison vs. the State-of-the-Art

6. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Xie, L.; Wei, L. Research on Vehicle Detection in High Resolution Satellite Images. In Proceedings of the IEEE Fourth Global Congress on Intelligent Systems, Hong Kong, China, 3–4 December 2013. [Google Scholar]

- European Space Agency for the members of ECSS. ECSS E-ST-50-11C, Space Engineering, SpaceFibre-Very High-Speed Serial Link; European Cooperation for Space Standardization: Noordwijk, The Netherlands, 2019. [Google Scholar]

- Parkers, S.; Ferrer, A. SpaceFibre Specification Draft K1; University of Dundee: Dundee, UK, 2017. [Google Scholar]

- Ciarpi, G.; Magazzù, G.; Palla, F.; Saponara, S. Design of Radiation-Hard MZM drivers. In Proceedings of the 20th Italian National Conference on Photonic Technologies, Lecce, Italy, 23–25 May 2018; Volume 26, pp. 1–4. [Google Scholar]

- Menouni, M.; Barbero, M.; Bompard, F.; Bonacini, S.; Fougeron, D.; Gaglione, R.; Rozanov, A.; Valerio, P.; Wang, A. 1-Grad total dose evaluation of 65 nm CMOS technology for the HL-LHC upgrades. In Proceedings of the Topical Workshop on Electronics for Particle Physics, Aix en Provence, France, 22–26 September 2014; pp. 22–26. [Google Scholar]

- Ciarpi, G.; Saponara, S.; Magazzù, G.; Palla, F. Radiation Hardness by Design techniques for 1 Grad TID Rad-Hard System in 65 nm standard CMOS technologies. In Proceedings of the International Conference on Application in Electronics Pervading Industry, Environment and Society, Pisa, Italy, 11–13 September 2019; Springer LNEE: Cham, Switzerland; Volume 627, pp. 269–276.

- Palla, F.; Ciarpi, G.; Magazzù, G.; Saponara, S. Design of a high radiation-hard driver for Mach–Zehnder Modulators based high-speed links for hadron collider applications. Nucl. Instrum. Methods Phys. Res. Sect. A 2019, 936, 303–304. [Google Scholar] [CrossRef]

- Ciarpi, G.; Magazzù, G.; Palla, F.; Saponara, S. Design, Implementation, and Experimental Verification of 5 Gbps, 800 Mrad TID and SEU-Tolerant Optical Modulators Drivers. IEEE Trans. Circuits Syst. I Regul. Pap. 2020, 67, 829–838. [Google Scholar] [CrossRef]

- Malou, F.; Gasiot, G.; Chevallier, R.; Dugoujon, L.; Roche, P. TID and SEE Characterization of Rad-Hardened 1.2GHz PLL IP from New ST CMOS 65nm Space Technology. In Proceedings of the 2014 IEEE Radiation Effects Data Workshop (REDW), Paris, France, 14–18 July 2014; pp. 1–8. [Google Scholar]

- Prinzie, J.; Christiansen, J.; Moreira, P.; Steyaert, M.; Leroux, P. Comparison of a 65 nm CMOS Ring- and LC-Oscillator Based PLL in Terms of TID and SEU Sensitivity. IEEE Trans. Nucl. Sci. 2017, 64, 245–252. [Google Scholar] [CrossRef]

- Monda, D.; Ciarpi, G.; Mangraviti, G.; Berti, L.; Saponara, S. Analysis and Comparison of Ring and LC-tank Oscillators for 65 nm Integration of Rad-Hard VCO for SpaceFibre Applications. In Applications in Electronics Pervading Industry, Environment and Society; Springer LNEE: Berlin/Heidelberg, Germany, 2020; Volume 627, pp. 25–32. [Google Scholar]

- Voinigescu, S. High-Frequency Integrated Circuits; Cambridge University Press: Cambridge, UK, 2013. [Google Scholar]

- Bae, W.; Ju, H.; Park, K.; Cho, S.; Jeong, D. A 7.6 mW, 214-fs RMS jitter 10-GHz phase-locked loop for 40-Gb/s serial link transmitter based on two-stage ring oscillator in 65-nm CMOS. In Proceedings of the 2015 IEEE Asian Solid-State Circuits Conference (A-SSCC), Xiamen, China, 9–11 November 2015; pp. 1–4. [Google Scholar]

- Razavi, B. Design of Integrated Circuits for Optical Communications; McGraw-Hill: New York, NY, USA, 2002. [Google Scholar]

- Hajimiri, A.; Limotyrakis, S.; Lee, T.H. Jitter and phase noise in ring oscillators. IEEE J. Solid-State Circuits 1999, 34, 790–804. [Google Scholar] [CrossRef]

- Heydari, P. Design and Analysis of Low-Voltage Current-Mode Logic Buffers. In Proceedings of the Fourth International Symposium on Quality Electronic Design, San Jose, CA, USA, 24–26 March 2003. [Google Scholar]

- Tlelo-Cautle, E.; Castañeda-Aviña, P.; Trejo-Guerra, R.; Carbajal-Gómez, V. Design of a Wide-Band Voltage-Controlled Ring Oscillator Implemented in 180 nm CMOS Technology. Electronics 2019, 8, 1156. [Google Scholar] [CrossRef]

- Gupta, K.; Pandey, N.; Gupta, M. Model and Design of Improved Current Mode Logic Gates: Differential and Single-Ended; Springer Nature: Berlin/Heidelberg, Germany, 2019. [Google Scholar]

- Snoeys, W.; Faccio, F.; Burns, M.; Campbell, M.; Cantatore, E.; Carrer, N.; Casagrande, L.; Cavagnoli, A.; Dachs, C.; Di Liberto, S.; et al. Layout techniques to enhance the radiation tolerance of standard CMOS technologies demonstrated on a pixel detector readout chip. Nucl. Instrum. Methods Phys. Res. Sect. A Accel. Spectrum. Detect. Assoc. Equip. 2000, 439, 349–360. [Google Scholar] [CrossRef]

- Camplani, A.; Shojaii, S.; Shrimali, H.; Stabile, A.; Liberali, V. CMOS IC radiation hardeningby design. Facta Univ. Ser. Electron. Energ. 2014, 27, 251–258. [Google Scholar] [CrossRef]

- Zhang, Z.; Chen, L.; Djahanshahi, H. A SEE Insensitive CML Voltage Controlled Oscillator in 65nm CMOS. In Proceedings of the 2018 IEEE Canadian Conference on Electrical & Computer Engineering, Quebec City, QC, Canada, 13–16 May 2018; pp. 1–4. [Google Scholar]

- Andreani, P.; Mattisson, S. On the use of MOS varactors in RF VCOs. IEEE J. Solid-State Circuits 2000, 35, 905–910. [Google Scholar] [CrossRef]

- Farahabadi, P.M.; Miar-Naimi, H.; Ebrahimzadeh, A. Closed-Form Analytical Equations for Amplitude and Frequency of High-Frequency CMOS Ring Oscillators. IEEE Trans. Circuits Syst. I Regul. Pap. 2009, 56, 2669–2677. [Google Scholar] [CrossRef]

- Cadence® Design Systems, Virtuoso®. Available online: https://www.cadence.com/en_US/home/tools/custom-ic-analog-rf-design/circuit-design/virtuoso-analog-design-environment.html (accessed on 28 June 2020).

- Razavi, B. A Study of Phase Noise in CMOS Oscillators. IEEE J. Solid-State Circuits 1996, 31, 331–343. [Google Scholar] [CrossRef]

- Razavi, B. RF Microelectronics; Prentice Hall: Upper Saddle River, NJ, USA, 1998; Volume 1. [Google Scholar]

- Land, D.V.; Levick, A.P.; Hand, J.W. The use of the Allan deviation for the measurement of the noise and drift performance of microwave radiometers. Meas. Sci. Technol. 2007, 18, 1917–1928. [Google Scholar] [CrossRef]

- Galton, I.; Weltin-Wu, C. Understanding Phase Error and Jitter: Definitions, Implications, Simulations, and Measurement. IEEE Trans. Circuits Syst. I Regul. Pap. 2019, 66, 1–19. [Google Scholar] [CrossRef]

- Rathore, P.; Nakhate, S. Development of Radiation Hardened by Design (RHBD) of NAND gate to mitigate the effects of single event transients (SET). In Proceedings of the IEEE 1st International Conference on Power Electronics, Intelligent Control and Energy Systems (ICPEICES), Delhi, India, 4–6 July 2016; pp. 1–6. [Google Scholar]

- Bailey, S.; Keller, B.; Der-Khachadourian, G. Project UPSET: Understanding and Protecting Against Single Event Transients. Available online: https://people.eecs.berkeley.edu/~stevo.bailey/documents/upset_final.pdf (accessed on 28 June 2020).

- Wirth, G.I.; Vieira, M.G.; Neto, H.E.; Kastensmidth, F.L. Modeling the sensitivity of CMOS circuits to radiation induced single event transients. Microelectron. Reliab. 2008, 48, 29–36. [Google Scholar] [CrossRef]

- Díez-Acereda, V.; Khemchandani, S.L.; Pino, J.D.; Mateos-Angulo, S. RHBD Techniques to Mitigate SEU and SET in CMOS Frequency Synthesizers. Electronics 2019, 8, 690. [Google Scholar] [CrossRef]

- Prinzie, J.; Smedt, V.D. Single Event Transients in CMOS Ring Oscillators. Electronics 2019, 8, 618. [Google Scholar] [CrossRef]

- Prinzie, J.; Christiansen, J.; Moreira, P.; Steyaert, M.; Leroux, P. A 2.56-GHz SEU Radiation Hard LCLC-Tank VCO for High-Speed Communication Links in 65-nm CMOS Technology. IEEE Trans. Nucl. Sci. 2018, 65, 407–412. [Google Scholar] [CrossRef]

- Yen, C.; Nasrollahpour, M.; Hamedi-Hagh, S. Low-power and high-frequency ring oscillator design in 65nm CMOS technology. In Proceedings of the IEEE 12th International Conference on ASIC, Guiyang, China, 25–28 October 2017; pp. 533–536. [Google Scholar]

- Kashani, M.H.; Molavi, R.; Mirabbasi, S. A 2.3-mW 26.3-GHz Gm-Boosted Differential Colpitts VCO with 20% Tuning Range in 65-nm CMOS. IEEE Trans. Microw. Theory Tech. 2019, 67, 1556–1565. [Google Scholar] [CrossRef]

| Oscillator | Technology Corners | Frequency Variations | Standard Deviation σ (Hz) |

|---|---|---|---|

| RO | slow-slow | 31.46% | 0.63 |

| typical | 28.34% | 0.89 | |

| fast-fast | 15.72% | 3.34 | |

| LC | slow-slow | 9.01% | 99.69 |

| typical | 9.07% | 578.5 | |

| fast-fast | 7.04% | 132.2 |

| Oscillator | Hit | Control Voltage | Clock Cycles | Frequency Variations | Amplitude Variations |

|---|---|---|---|---|---|

| RO | hit1 | 0 | 6 | 0.61% | −1.65% |

| VDD | 3 | 0.27% | −2.93% | ||

| hit2 | 0 | 9 | 1.53% | −15.38% | |

| VDD | 9 | 3.12% | −16.27% | ||

| LC | hit1 | 0 | 6 | 0.11% | 1.55% |

| VDD | 13 | 0.46% | 3.17% | ||

| hit2 | 0 | 15 | 1.24% | 43.80% | |

| VDD | 24 | 2.45% | 57.49% |

| Ref. | Frequency (GHz) | Power Consumption (mW) | SEE Tolerant | Architecture | Area (mm2) |

|---|---|---|---|---|---|

| [9] | 0.2–1.2 | n.a. | tested | Ring | n.a. |

| [10] | 2.2–3.2 | 6 | tested | Ring and LC | n.a. |

| [34] | 2.25–2.88 | 1.8 | tested | LC tank | n.a. |

| [35] | 3.7–6.5 | 2 | no | Ring | 0.011 |

| [36] | 23.8–29.1 | 2.3 | no | Colpitts | 0.221 |

| This work | 6.20–6.75 | 18 | simulated | Ring | 0.021 |

| This work | 5.35–6.55 | <3 | simulated | LC tank | 0.061 |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Monda, D.; Ciarpi, G.; Saponara, S. Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for SpaceFibre Applications. Sensors 2020, 20, 4612. https://doi.org/10.3390/s20164612

Monda D, Ciarpi G, Saponara S. Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for SpaceFibre Applications. Sensors. 2020; 20(16):4612. https://doi.org/10.3390/s20164612

Chicago/Turabian StyleMonda, Danilo, Gabriele Ciarpi, and Sergio Saponara. 2020. "Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for SpaceFibre Applications" Sensors 20, no. 16: 4612. https://doi.org/10.3390/s20164612

APA StyleMonda, D., Ciarpi, G., & Saponara, S. (2020). Analysis and Comparison of Rad-Hard Ring and LC-Tank Controlled Oscillators in 65 nm for SpaceFibre Applications. Sensors, 20(16), 4612. https://doi.org/10.3390/s20164612