An X-band Bi-Directional Transmit/Receive Module for a Phased Array System in 65-nm CMOS

Abstract

:1. Introduction

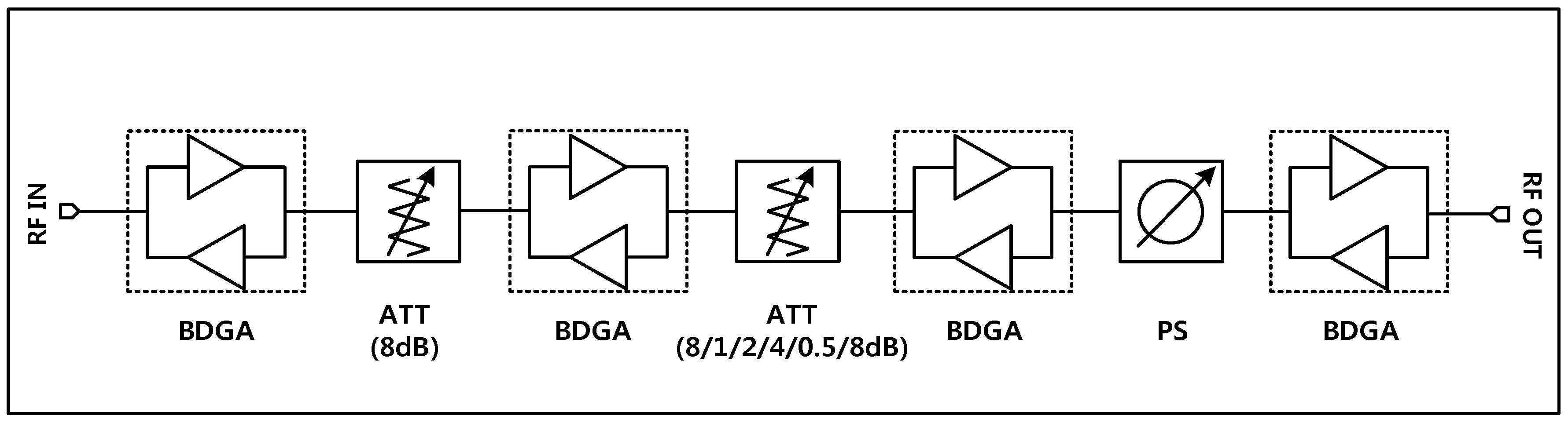

2. The Design of the X-band TRM

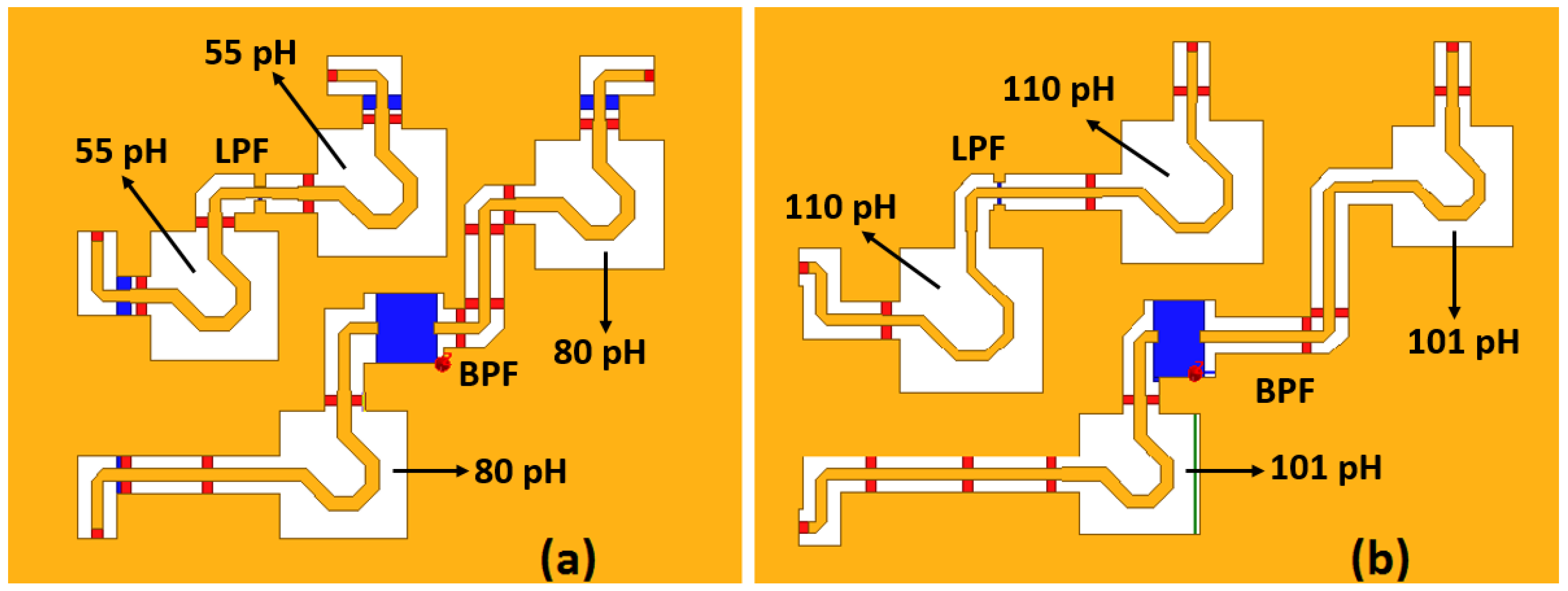

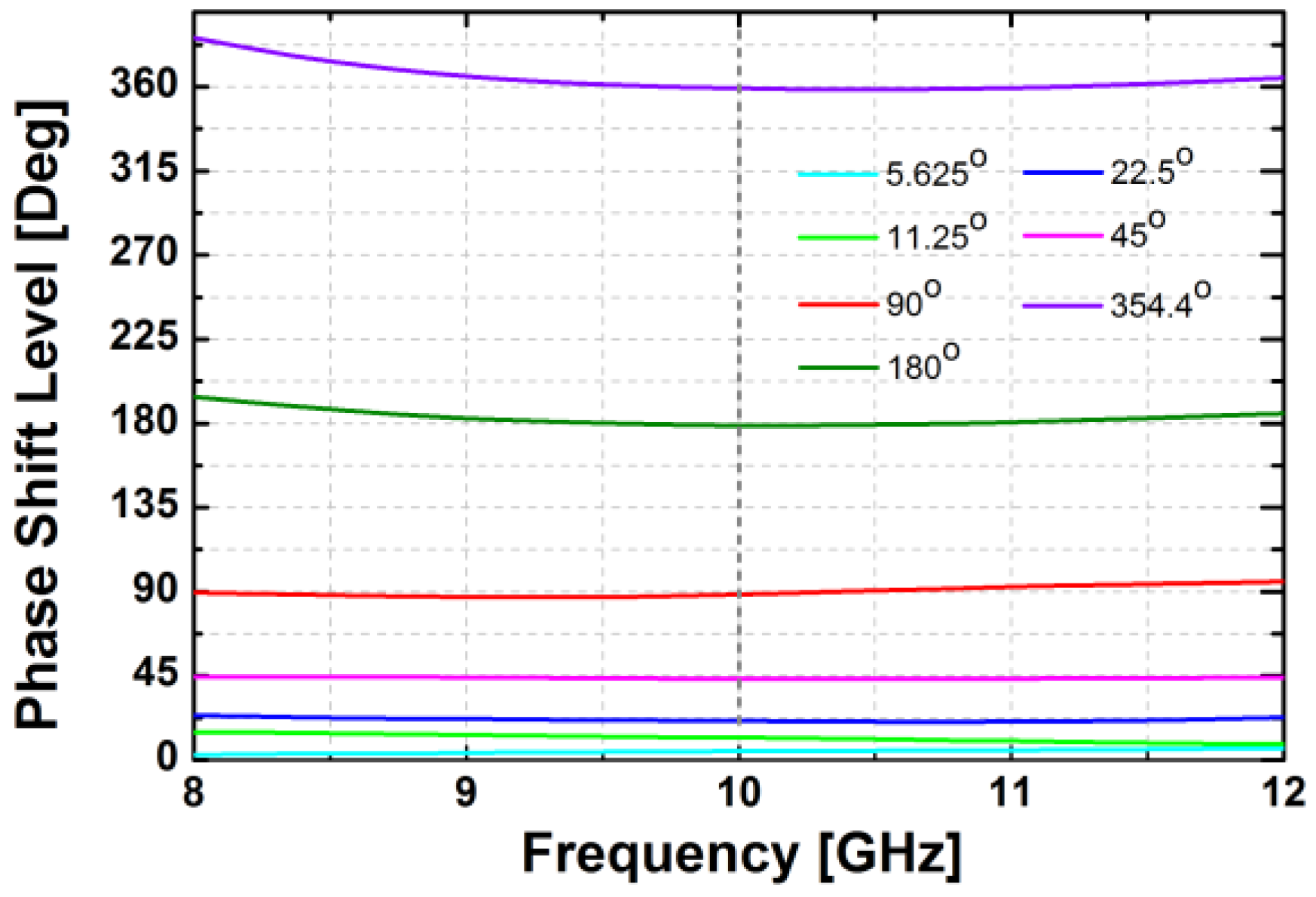

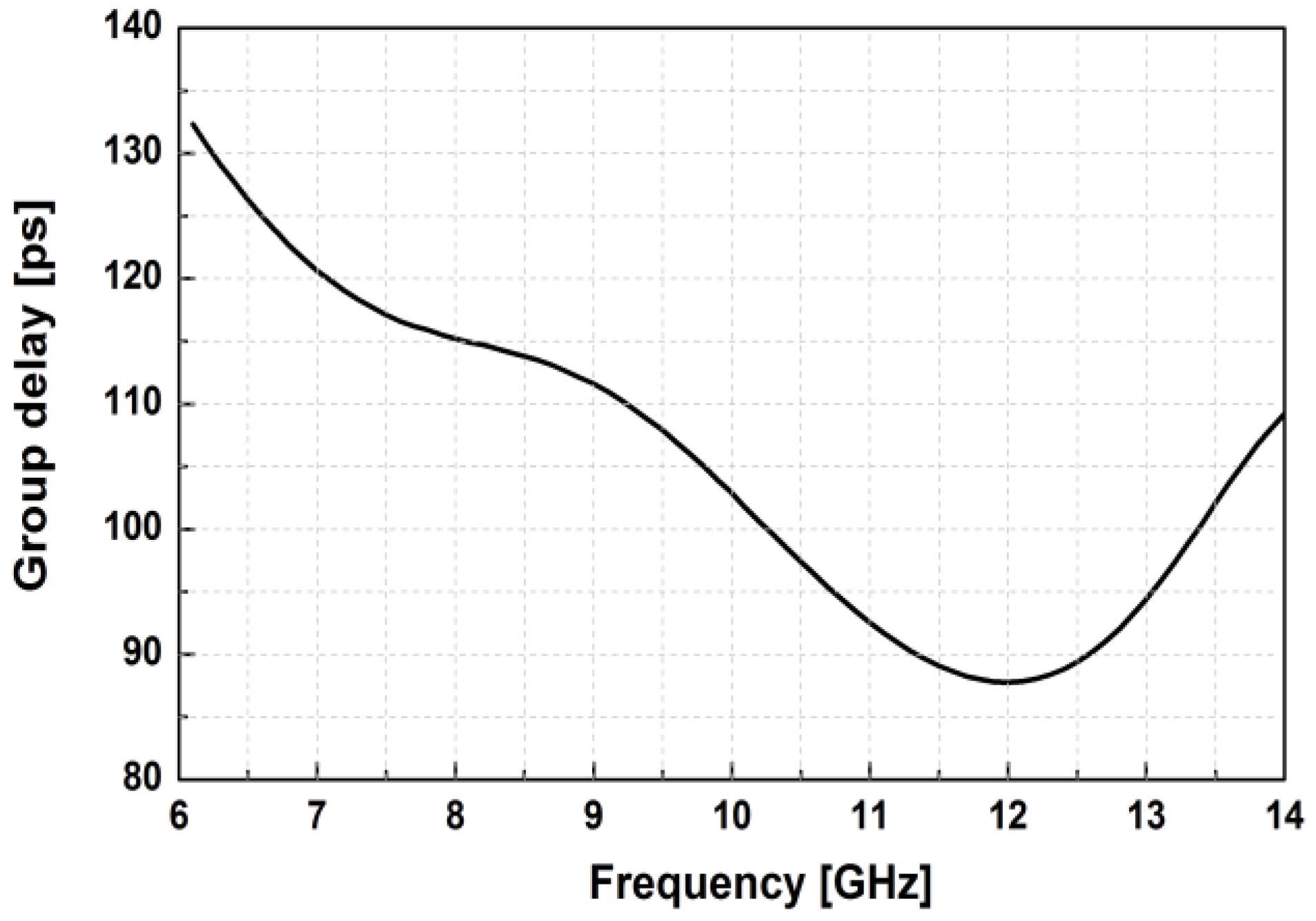

2.1. The 6-Bit Phase Shifter

2.1.1. The phase Shifting Elements

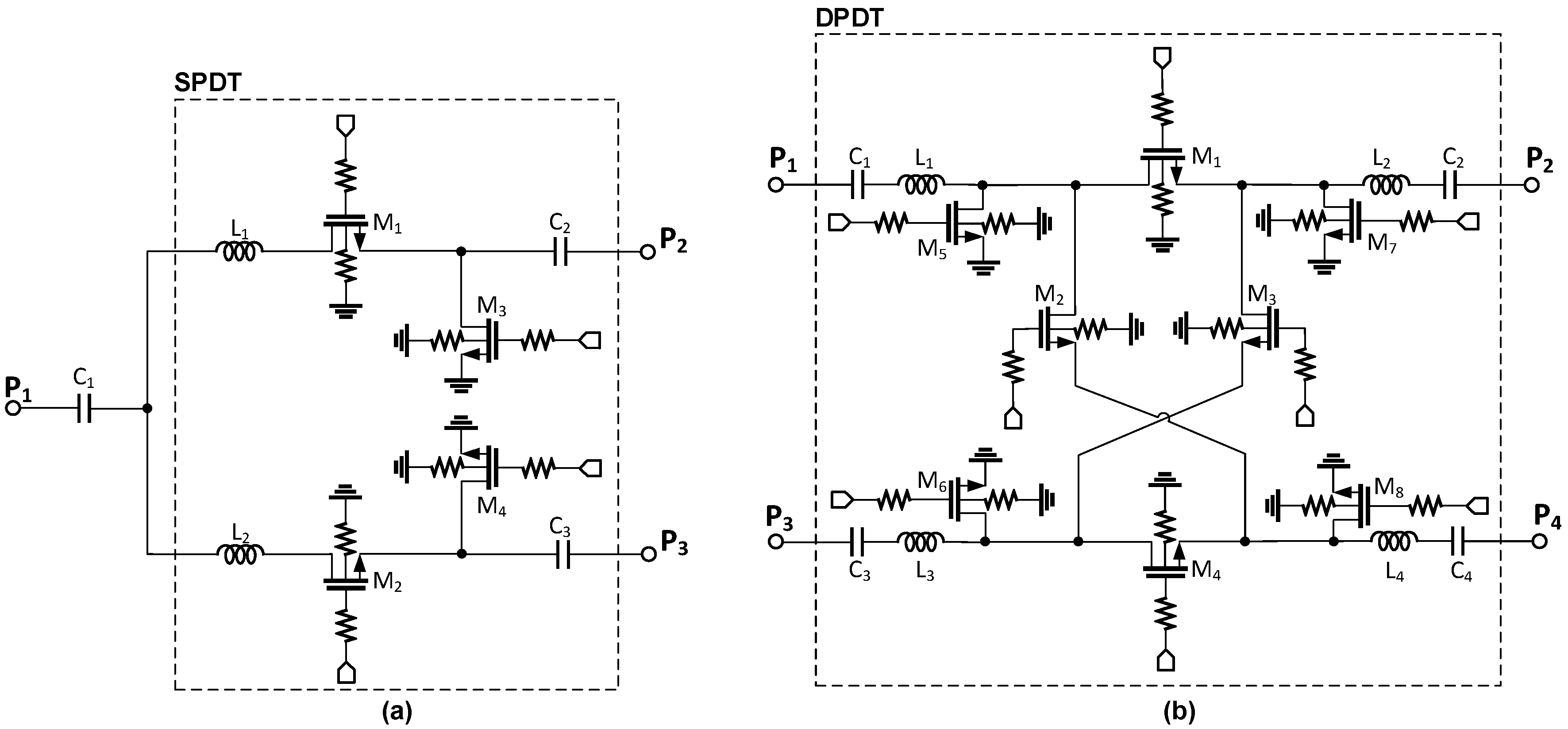

2.1.2. The SPDT and DPDT Switches

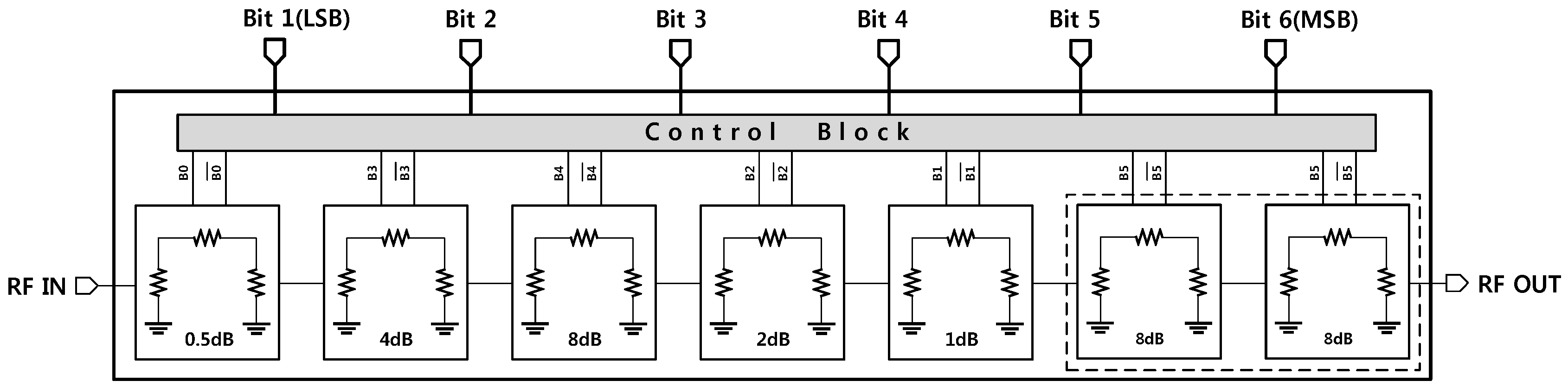

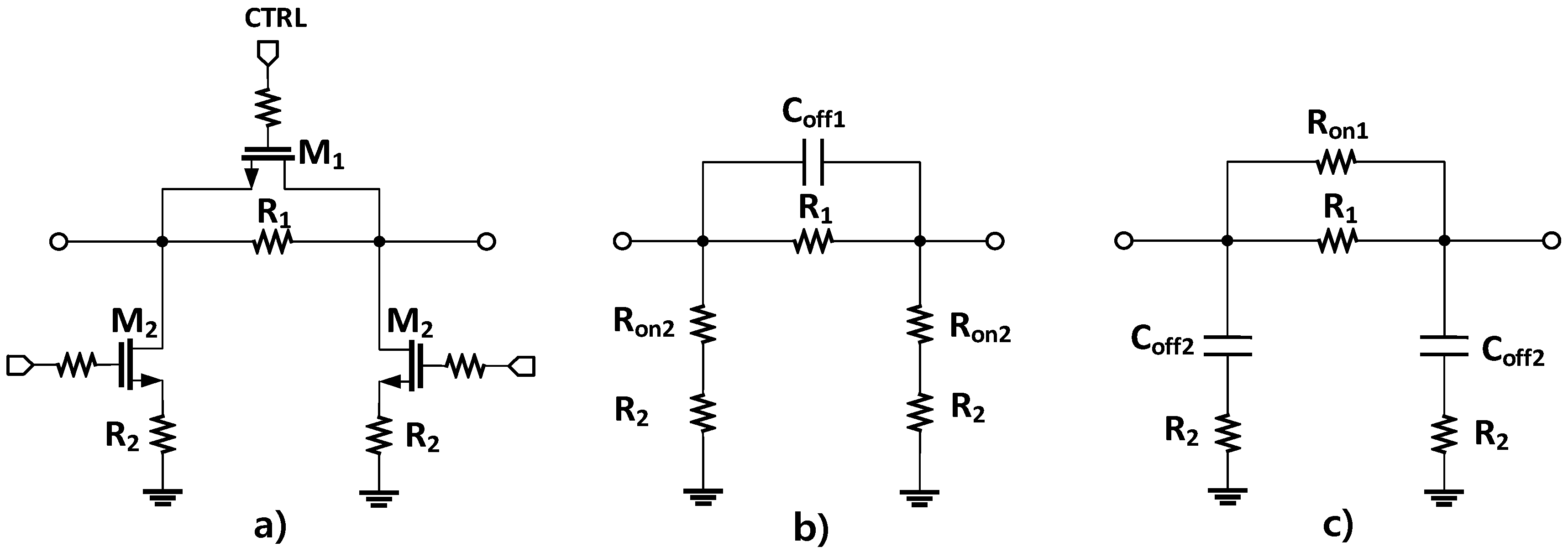

2.2. The Attenuator

2.3. The Bi-Directional Gain Amplifier (BDGA)

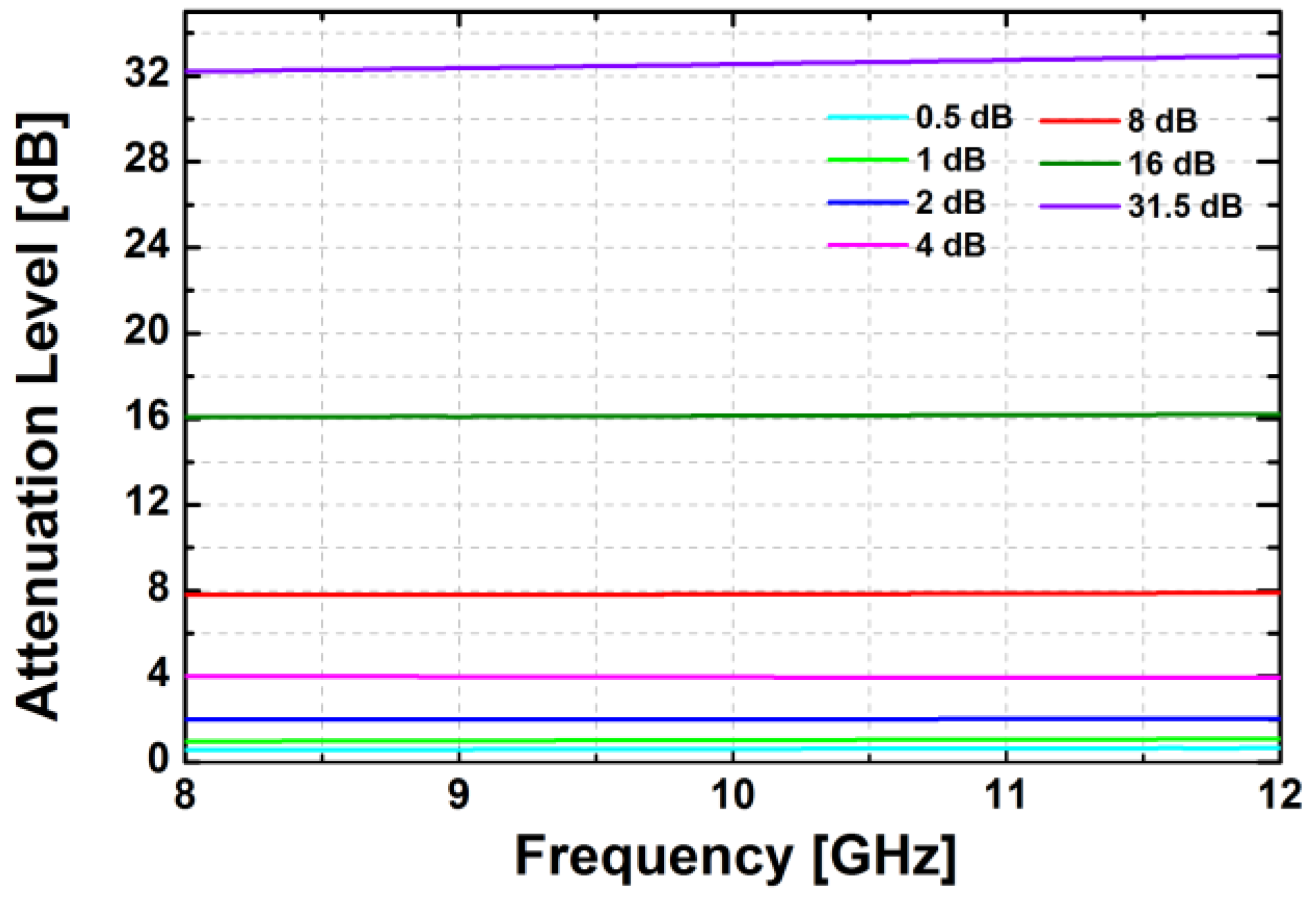

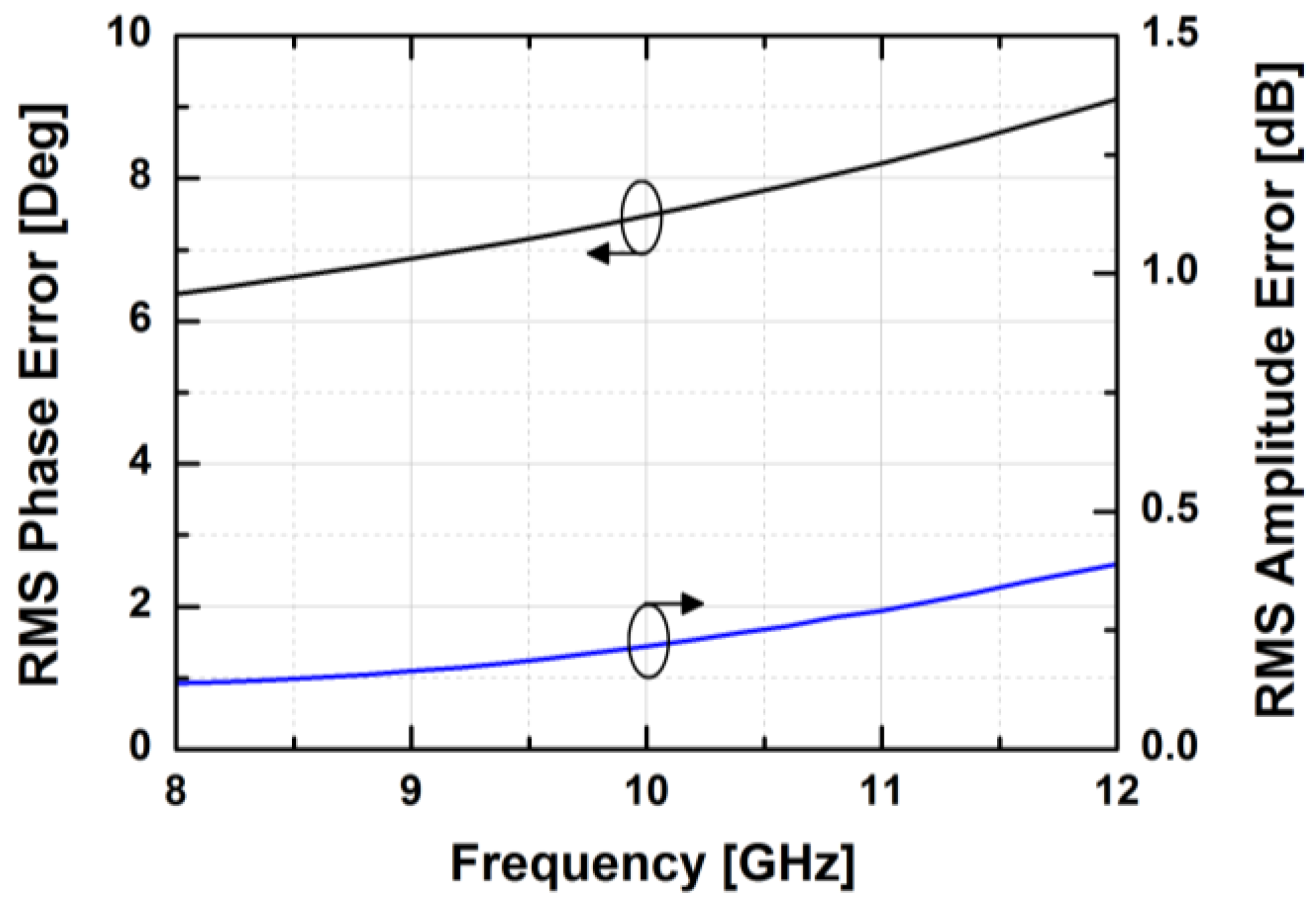

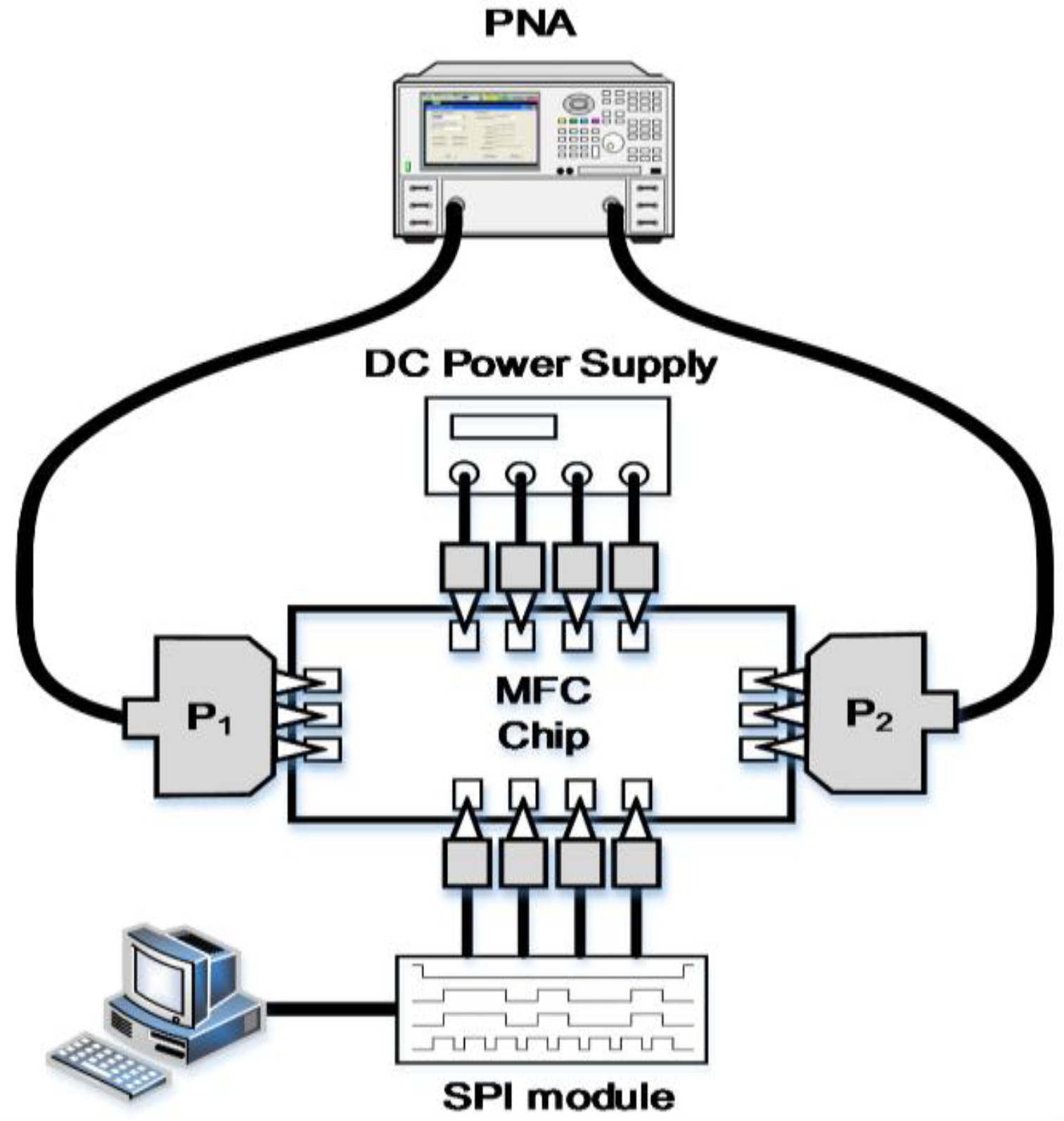

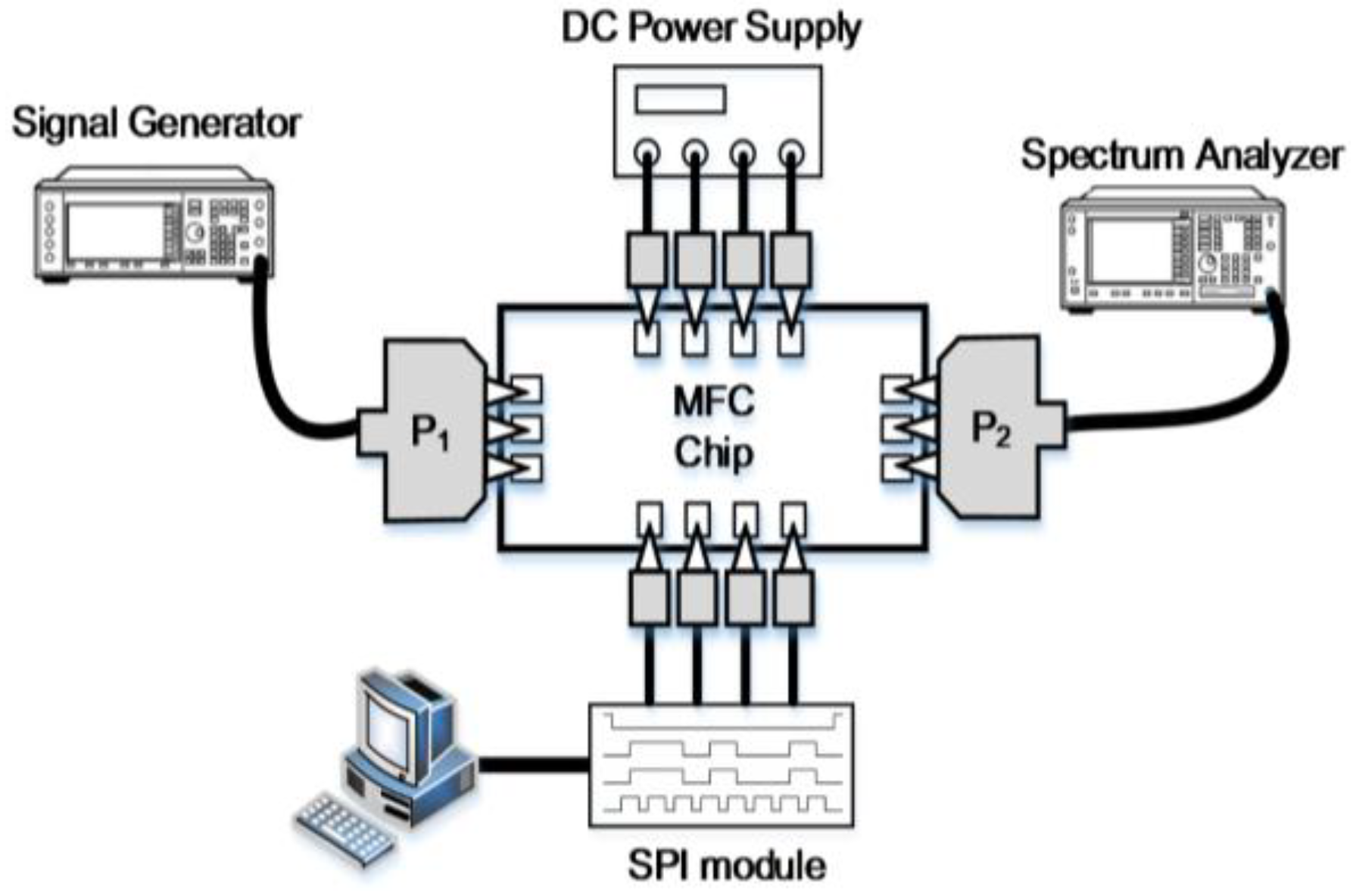

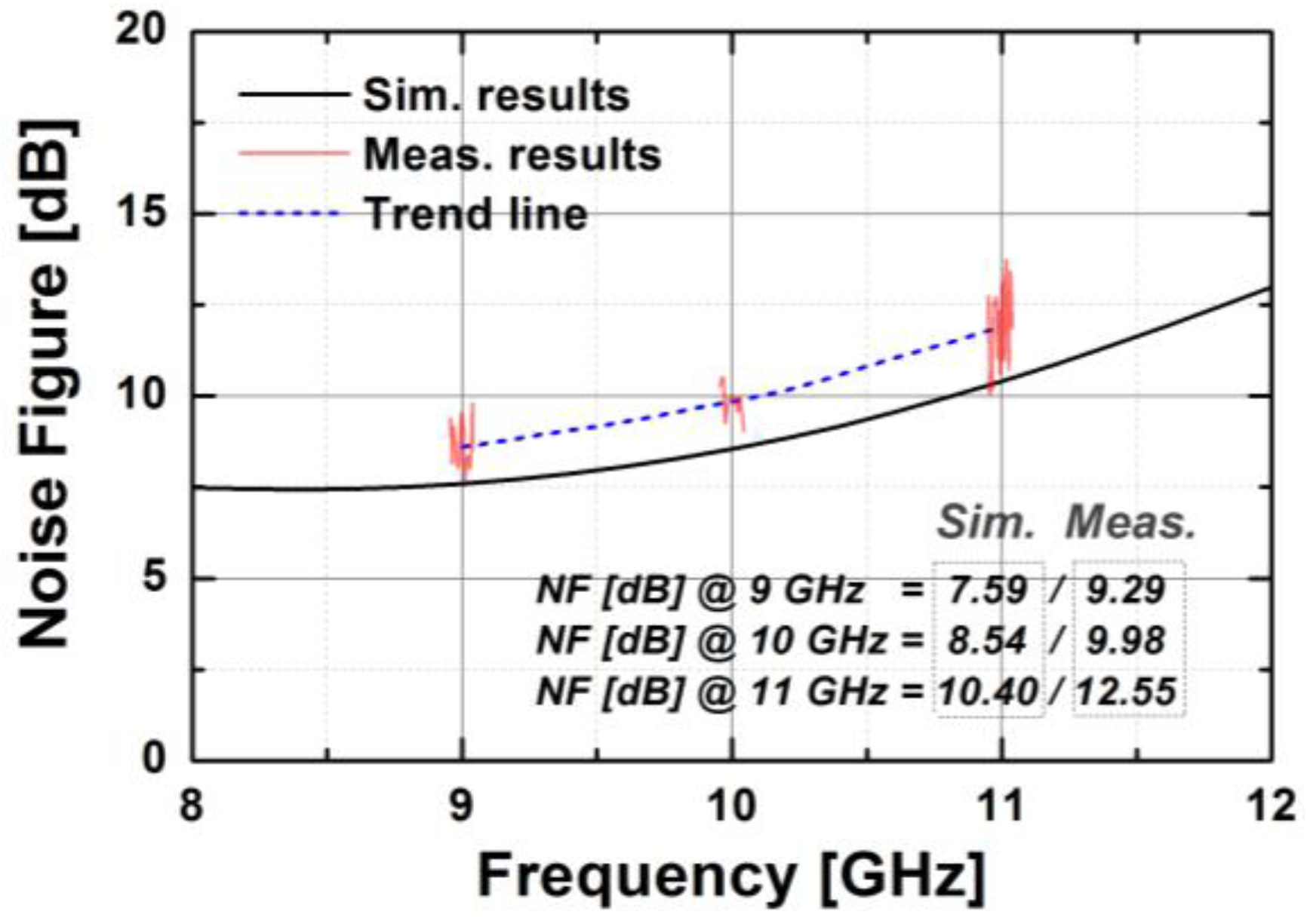

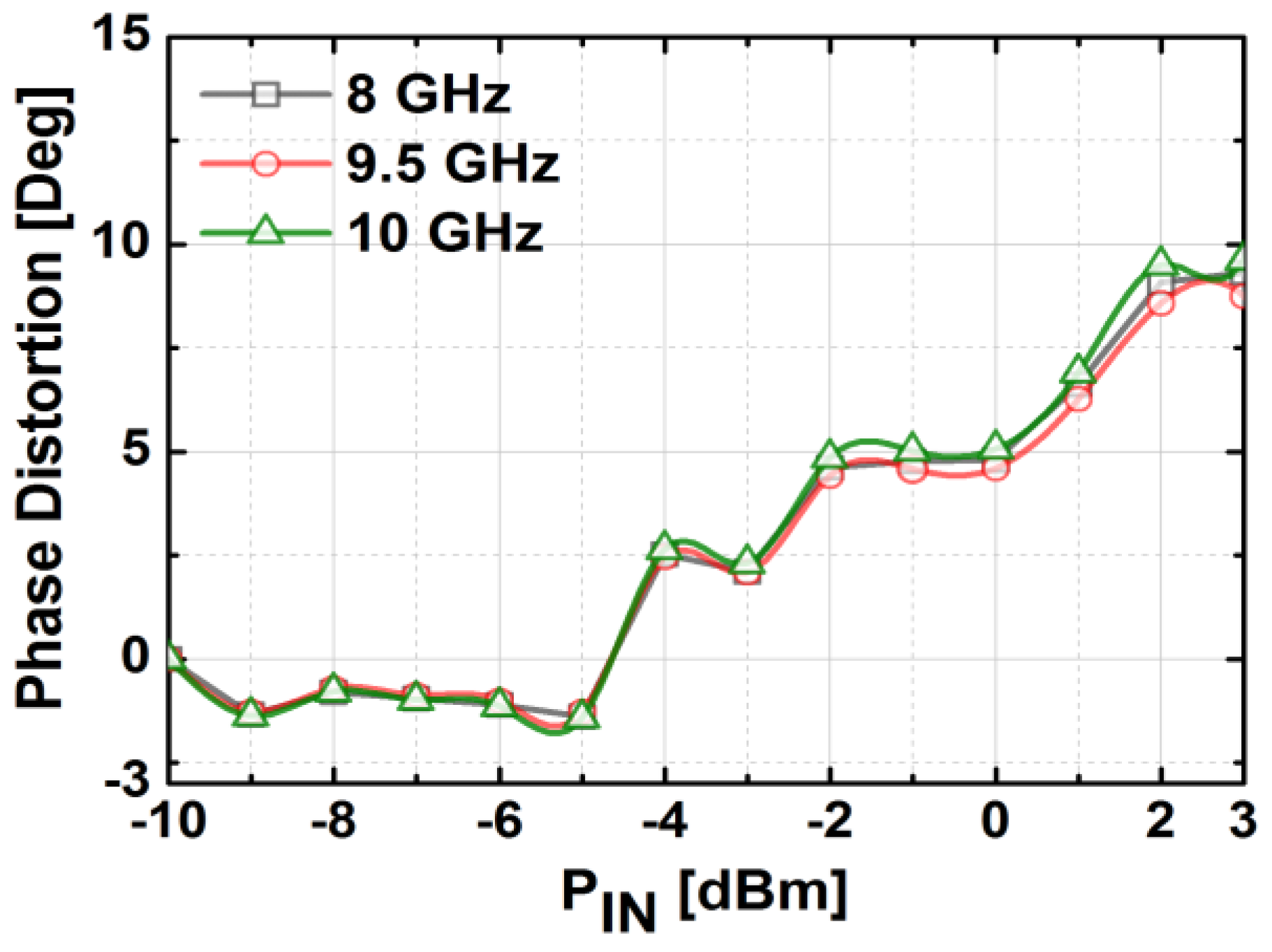

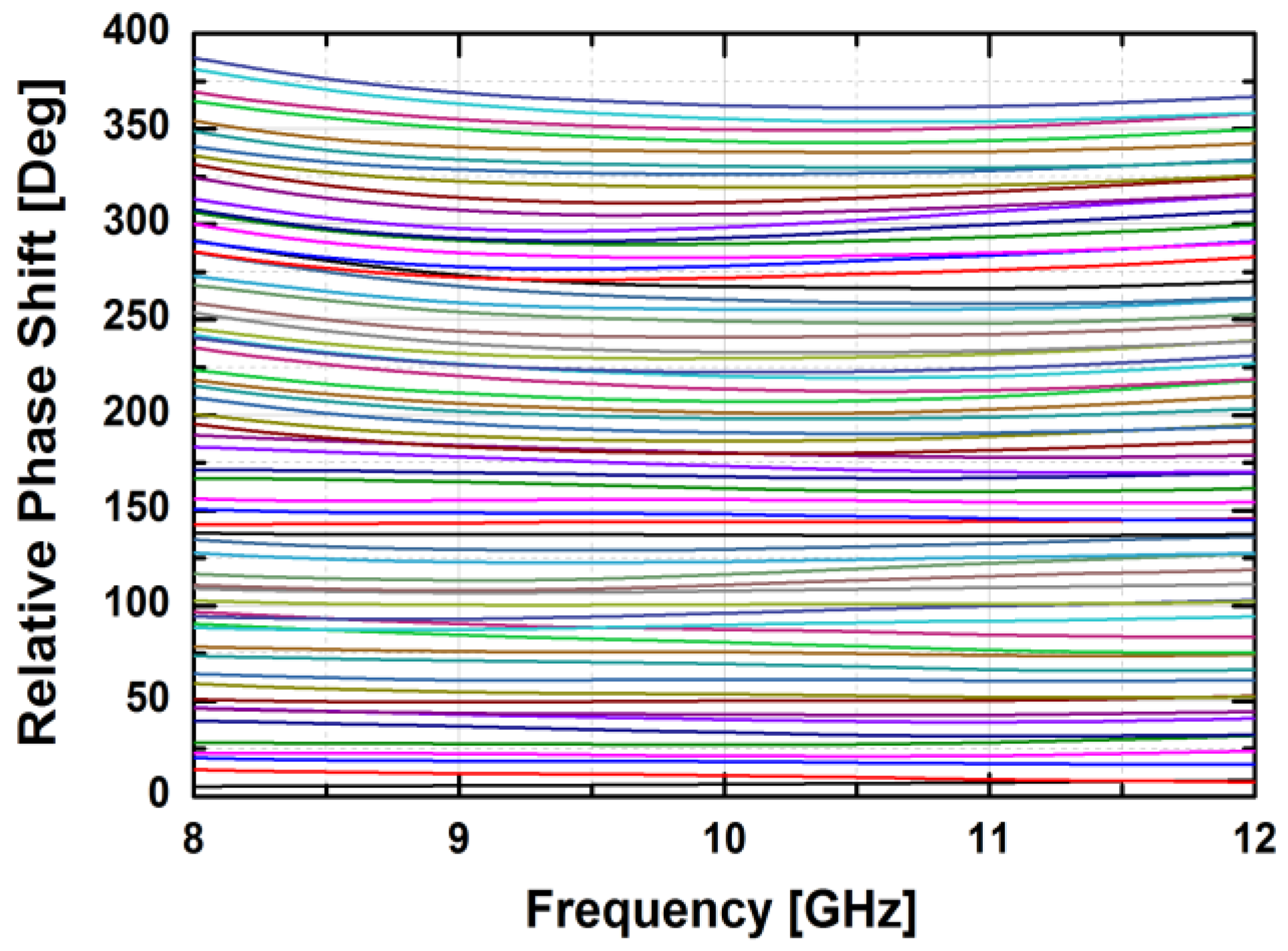

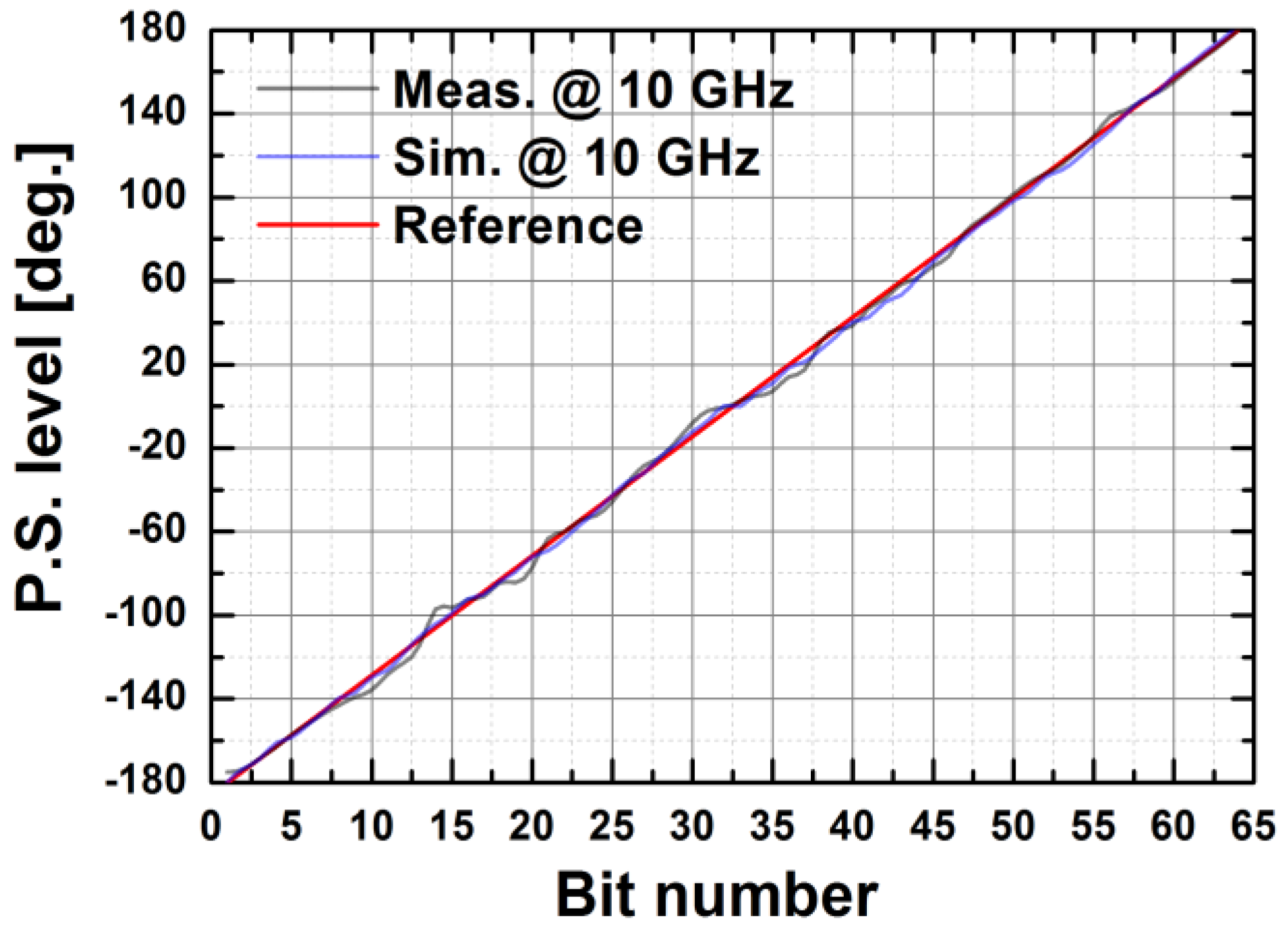

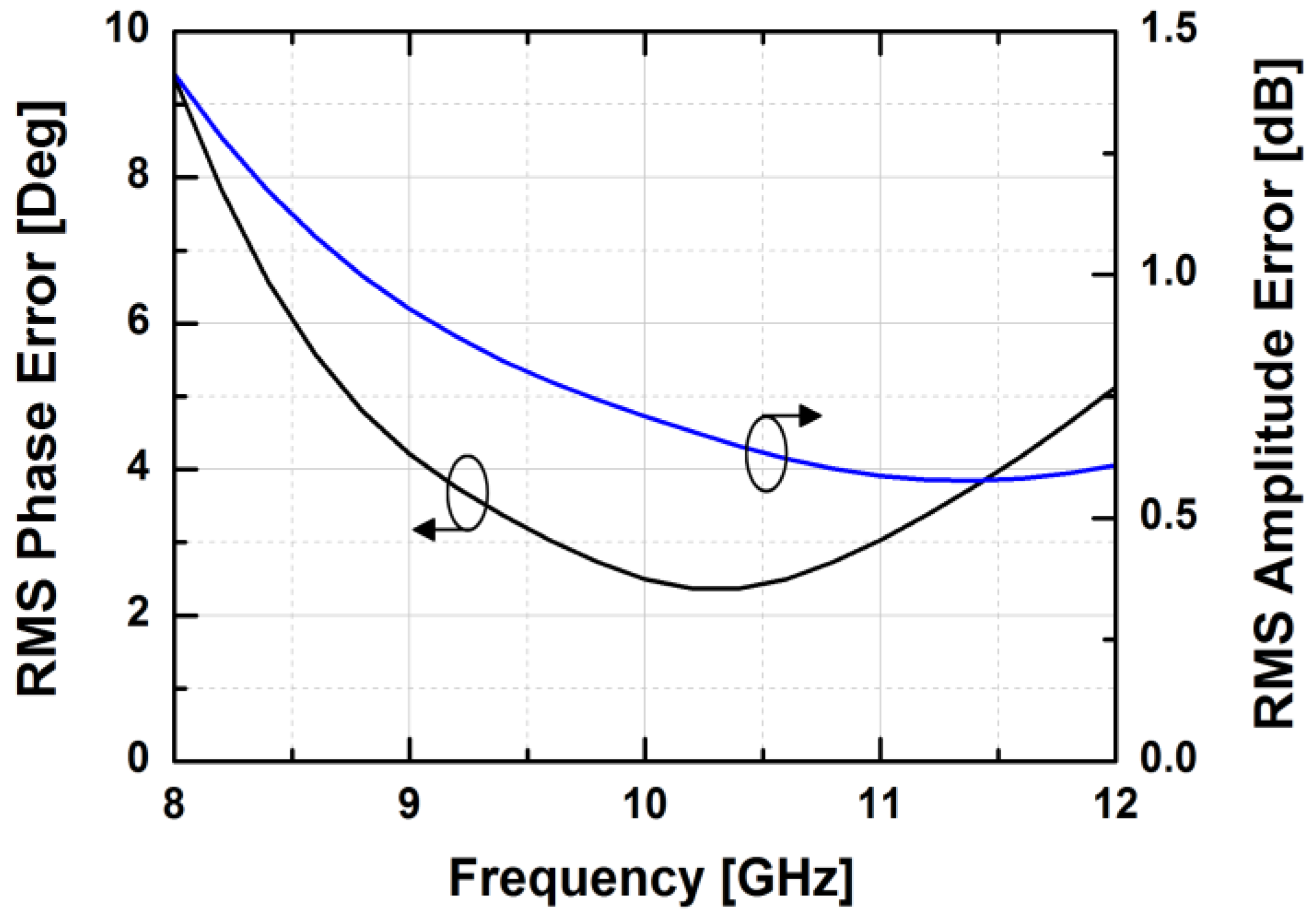

3. Measurement Results

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Forecast International. AESA, Other Developments Drive Radar Production. Available online: http://www.defense-aerospace.com/article-view/release/99241/aesa,-other-developments-drive-radar-production.html (accessed on 28 May 2018).

- Schuh, P.; Sledzik, H.; Reber, R.; Widmer, K.; Fleckenstein, A.; Schweizer, B.; Oppermann, M. T/R module technologies today and future trends. In Proceedings of the 40th European Microwave Conference, Paris, France, 28–30 September 2010; IEEE: Piscataway, NJ, USA, 2010; pp. 1540–1543. [Google Scholar]

- Brookner, E. Active phase arrays and digital beamforming: amazing breakthroughs and future trends. In Proceedings of the 2008 IEEE Radar Conference (IRSI-2007), Rome, Italy, 26–30 May 2008. [Google Scholar]

- XZ1002-BD. 8.5–11.0 GHz GaAs MMIC Core Chip. M/A-COM Tech Asia. Available online: https://www.digchip.com/datasheets/3262797-8-5-11-0-ghz-gaas-mmic-core.html (accessed on 28 May 2018).

- Product Datasheet: CGY2170YUH: C Band High Gain Low Noise Amplifier. OMMIC: Limeil-Brévannes, France. Available online: www.ommic.fr/file/download/CGY2178UH_DS_130910.pdf (accessed on 28 May 2018).

- Min, B.; Rebeiz, G.M. A 10–50 GHz CMOS distributed step attenuator with low loss and low phase imbalance. IEEE J. Solid-State Circuits 2007, 42, 2547–2554. [Google Scholar] [CrossRef]

- Rebeiz, G. Highly dense microwave and millimeter wave phased array T/R modules using CMOS and SiGe RFICs. In Proceedings of the IEEE 12th Annual Wireless Microwave Technology Conference, Clearwater Beach, FL, USA, 18–19 April 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 1–5. [Google Scholar]

- Dinc, T.; Zihir, S.; Gurbuz, Y. SiGe building blocks for on-chip X-band T/R modules. In Proceedings of the IEEE 12th Topical Meetings on Silicon Monolithic Integrated Circuits in RF Systems (SiRF), Santa Clara, CA, USA, 16–18 January 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 57–60. [Google Scholar]

- Jeong, J.C.; Yom, I.B. X-band high power SiGe BiCMOS multifunction chip for active phased array radars. Electron. Lett. 2011, 47, 618–619. [Google Scholar] [CrossRef]

- Patterson, C.E.; Cressler, J.D. A lightweight organic X-band active receiving phased array with integrated SiGe amplifiers and phase shifters. IEEE Trans. Antennas Propag. 2011, 59, 100–109. [Google Scholar] [CrossRef]

- Carosi, D.; Bettidi, A.; Nanni, A. A mixed-signal X-band SiGe multi-function control MMIC for phased array radar applications. In Proceedings of the 39th European Microwave Conference, Rome, Italy, 29 September–1 October 2009; pp. 240–243. [Google Scholar]

- Yeo, S.K.; Chun, J.H.; Kwon, Y.S. A 3-D X-band T/R module package with an anodized aluminum multilayer substrate for phased array radar applications. IEEE Trans. Adv. Packag. 2010, 33, 883–891. [Google Scholar] [CrossRef]

- He, J.; Fengman, L.; Dongkai, S. Design and implementation of a 700–2600 MHz RF SiP module for micro base station. Microsyst. Technol. 2015, 20, 2295–2300. [Google Scholar] [CrossRef]

- Carlofelice, A.D.; Paulis, F.D.; Fina, A.; Marcantonio, D.U.; Orlandi, A.; Tognolatti, P. Compact and reliable T/R module prototype for advance space active electronically steerable antenna in 3-D LTCC technology. IEEE Trans. Microw. Theory Tech. 2018, 66, 2746–2756. [Google Scholar] [CrossRef]

- Tian, G.; Li, J.; Hou, F. Design and implementation of a compact 3-D stacked RF front-end module for micro base station. IEEE Trans. Compon. Packag. Manuf. Technol. 2018. [CrossRef]

- Bettidi, A.; Carosi, D.; Cetronio, A.; Corsaro, F.; Costrini, C.; Lanzieri, C.; Marescialli, L. X-band transmit/receive module MMIC chipset on emerging GaN and SiGe technologies. In Proceedings of the IEEE Phased Array Systems and Technology Symposium Digest, Waltham, MA, USA, 12–15 October 2010; IEEE: Piscataway, NJ, USA, 2010; pp. 250–255. [Google Scholar]

- Kang, D.W.; Kim, J.G.; Min, B.W.; Rebeiz, G.M. Single and four-element Ka-band transmit/receive phased-array silicon RFICs with 5-bit amplitude and phase control. IEEE Trans. Microw. Theory Tech. 2009, 57, 3534–3543. [Google Scholar] [CrossRef]

- Ku, B.H.; Kang, D.W.; Hong, S.C. CMOS integrated circuits for X-band phased array systems. In Proceedings of the IEEE 54th International Midwest Symposium on Circuits and Systems (MWSCAS), Seoul, Korea, 7–10 August 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 1–5. [Google Scholar]

- Cho, M.K.; Yoon, S.H.; Sim, S.H.; Jeon, L.; Kim, J.G. CMOS-based bi-directional T/R chipsets for phased array antenna. In Proceedings of the IEEE MTT-S International Microwave Symposium Digest (MTT), Montreal, QC, Canada, 17–22 June 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 1–3. [Google Scholar]

- Han, J.H.; Kim, J.H.; Park, J.S.; Kim, J.G. A 28 GHz four channel T/R chipset in 65 nm CMOS technology. In Proceedings of the IEEE 5th Asia-Pacific Conference on Antennas and Propagation (APCAP), Kaohsiung, Taiwan, 26–29 July 2016; IEEE: Piscataway, NJ, USA, 2016; pp. 203–204. [Google Scholar]

- Lo, W.K.; Chan, W.S.; Li, C.W.; Leung, C.K. Self-phase equalised bidirectional distributed amplifier. Electron. Lett. 2007, 43, 626–627. [Google Scholar] [CrossRef]

- Yang, J.M.; Lai, R.; Chung, Y.H.; Nishimoto, M.; Battung, M.; Lee, W.; Kagiwada, R. Compact Ka-band bi-directional amplifier for low-cost electronic scanning array antenna. IEEE Solid-State Circuits 2004, 39, 1716–1719. [Google Scholar] [CrossRef]

- Min, B.W.; Rebeiz, G.M. Ka-band low-loss and high-isolation switch design in 0.13 m CMOS. IEEE Trans. Microw. Theory Tech. 2008, 56, 1364–1371. [Google Scholar]

- Dinc, T.; Zihir, S.; Gurbuz, Y. CMOS SPDT T/R switch for X-band, on-chip radar applications. Electron. Lett. 2010, 46, 1382–1384. [Google Scholar] [CrossRef]

- Huang, F.J.; Kenneth, O. A 0.5-µm CMOS T/R switch for 900-MHz wireless applications. IEEE J. Solid-State Circuits 2001, 36, 486–492. [Google Scholar] [CrossRef]

- Kidwai, A.A.; Fu, C.T.; Jensen, J.C.; Taylor, S.S. A fully integrated ultra-low insertion loss T/R switch for 802.11b/g/n application in 90 nm CMOS process. IEEE J. Solid-State Circuits 2009, 44, 1352–1360. [Google Scholar] [CrossRef]

- Li, Z.; Yoon, H.; Huang, F.J. 5.8-GHz CMOS T/R switches with high and low substrate resistances in a 0.18-µm CMOS process. IEEE Microw. Wirel. Compon. Lett. 2003, 13, 1–3. [Google Scholar]

- Yeh, M.C.; Tsai, Z.M.; Liu, R.C.; Lin, K.Y.; Chang, Y.T.; Wang, H. Design and analysis for a miniature CMOS SPDT switch using body-floating technique to improve power performance. IEEE Trans. Microw. Theory Tech. 2006, 54, 31–39. [Google Scholar]

- Li, Q.; Zhang, Y.P.; Yeo, K.S.; Lim, W.M. 16.6- and 28-GHz fully integrated CMOS RF switches with improved body floating. IEEE Trans. Microw. Theory Tech. 2008, 56, 339–345. [Google Scholar] [CrossRef]

- Stefano, T.; Thomas, B.; Stefan, B.; Andreas, D.; Peter, K. Electronically steered cognitive weather radar—A technology perspective. In Proceedings of the 2017 IEEE Radar Conference, Seattle, WA, USA, 8–12 May 2017; pp. 563–566. [Google Scholar]

| Filter | L Element | C Element | |

|---|---|---|---|

| HP | T-type | ||

| π-type | |||

| LP | T-type | ||

| π-type |

| Unit Cell | HP Filter | LP Filter | ||

|---|---|---|---|---|

| L (pH) | C (fF) | L (pH) | C (fF) | |

| 11.25 | 80 | 1000 | 55 | 53 |

| 22.5 | 101 | 624 | 110 | 86 |

| 45 | 231 | 336 | 224 | 168 |

| 90 | 1125 | 790 | 330 | 228 |

| 180 | 796 | 272 | 796 | 336 |

| Device | SPDT | Device | DPDT |

|---|---|---|---|

| M1, M2 | 130 μm/0.06 μm (nf = 26, m = 2) | M1~M4 | 130 μm/0.06 μm (nf = 26, m = 2) |

| M3, M4 | 20 μm/0.06 μm (nf = 20) | M5~M8 | 20 μm/0.06 μm (nf = 20) |

| L1, L2 | 610 pH | L1~L4 | 510 pH |

| C1~C3 | 3.2 pF | C1~C4 | 3.2 pF |

| Att. Unit | M1 | M2 | R1 (Ω) | R2 (Ω) |

|---|---|---|---|---|

| 0.5 dB | 40 μm/0.06 μm | 4 μm/0.06 μm | 6.7 | 9.12 k |

| 1 dB | 40 μm/0.06 μm | 4 μm/0.06 μm | 15.2 | 3.04 k |

| 2 dB | 40 μm/0.06 μm | 4 μm/0.06 μm | 21.7 | 372.4 |

| 4 dB | 40 μm/0.06 μm | 4 μm/0.06 μm | 31.1 | 82.50 |

| 8 dB | 40 μm/0.06 μm | 4 μm/0.06 μm | 78.5 | 33.5 |

| 8 dB (16 dB) | 40 μm/0.06 μm | 4 μm/0.06 μm | 81.3 | 33.5 |

| [7] | [11] | [17] | This Work | |

|---|---|---|---|---|

| Technology | SiGe BiCMOS | SiGe BiCMOS | CMOS 0.18 μm | CMOS 65 nm |

| Frequency range (GHz) | 8–11 | 8–11 | 8.5–10 | 8–10.5 |

| Phase shifter range/step (deg) | 360/11.25 | 360/11.25 | 360/5.625 | 360/5.625 |

| Attenuator range/step (dB) | 31/1 | 15.5/0.5 | 31.5/0.5 | 31.5/0.5 |

| Insertion gain (dB) | 20 | 17 | 12 | 3.7 |

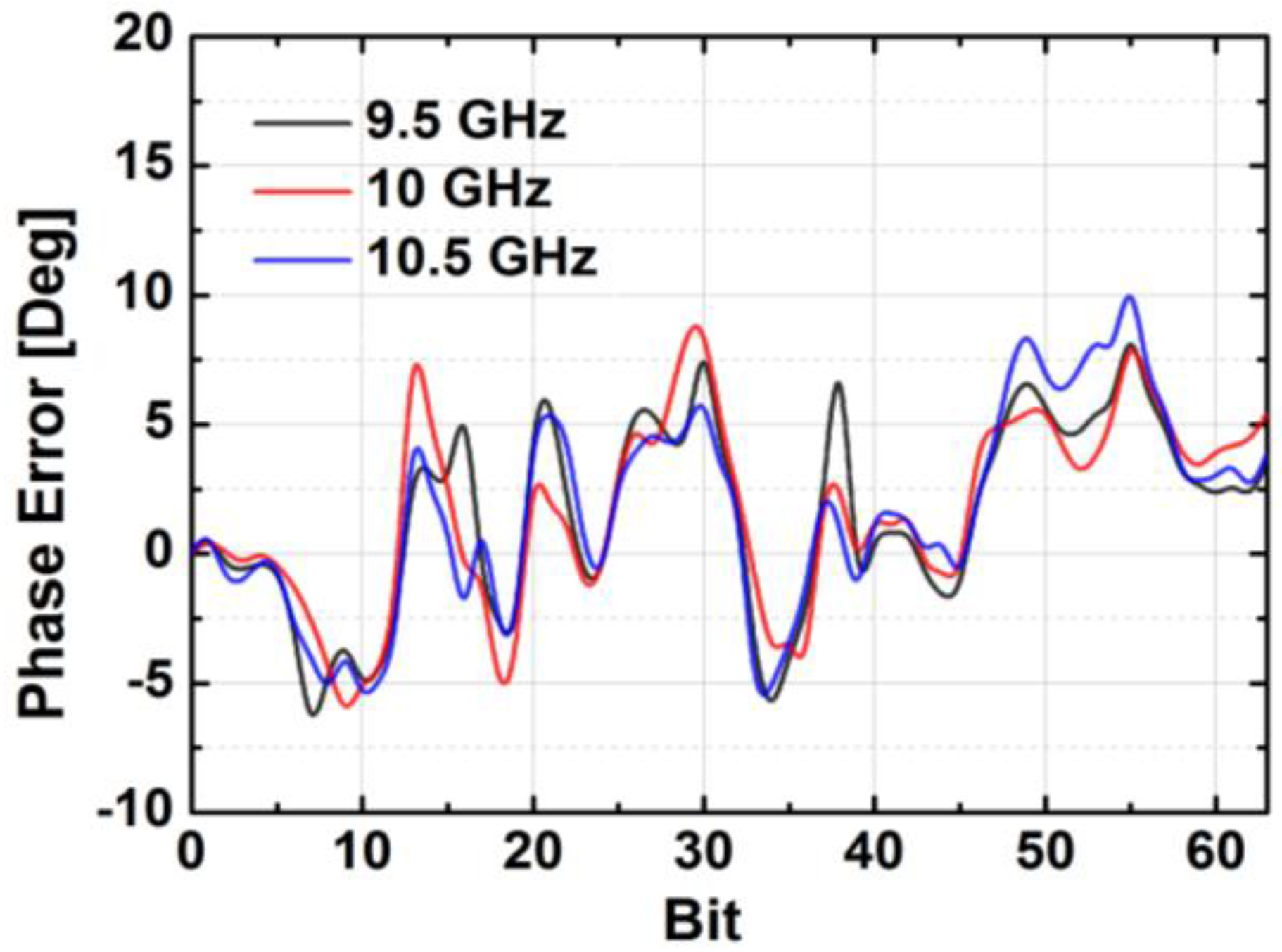

| RMS phase error (deg) | 6 | 6 | 2 | 4 |

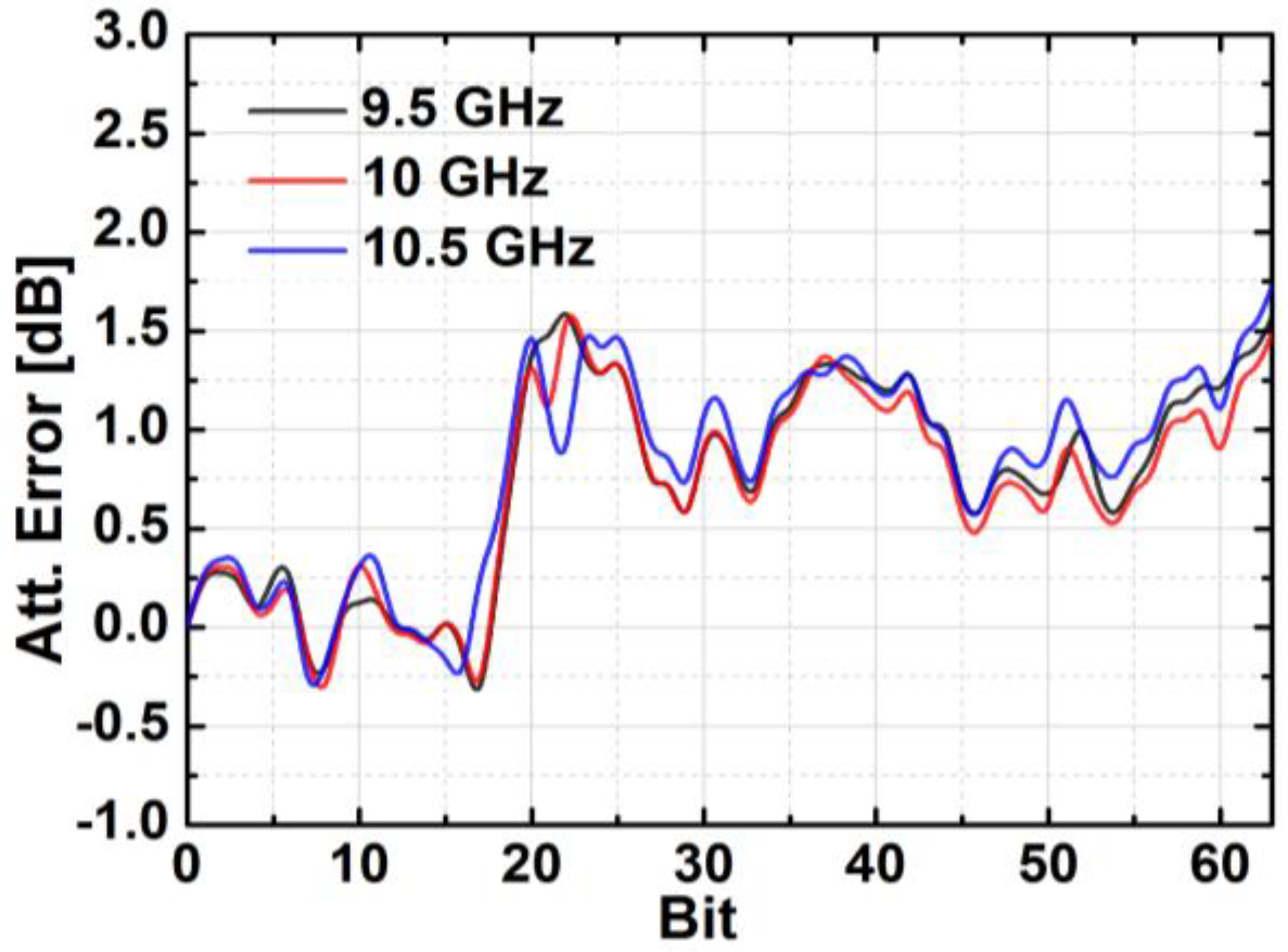

| RMS amplitude error (dB) | 1.5 | 1 | 0.25 | 0.5 |

| OP1dB (dBm) | 18 | 12 | 11 | 5.1 |

| NF | 9 | 9 | 8.5 | 10 |

| Power consumption (Watt) | 1.5 | 0.8 | 0.67 | 0.17 |

| Chip size (mm2) | 3.5 × 2.4 | 3.9 × 4.1 | 4.4 × 2.9 | 3.92 × 2.44 |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Nguyen, V.-V.; Nam, H.; Choe, Y.J.; Lee, B.-H.; Park, J.-D. An X-band Bi-Directional Transmit/Receive Module for a Phased Array System in 65-nm CMOS. Sensors 2018, 18, 2569. https://doi.org/10.3390/s18082569

Nguyen V-V, Nam H, Choe YJ, Lee B-H, Park J-D. An X-band Bi-Directional Transmit/Receive Module for a Phased Array System in 65-nm CMOS. Sensors. 2018; 18(8):2569. https://doi.org/10.3390/s18082569

Chicago/Turabian StyleNguyen, Van-Viet, Hyohyun Nam, Young Joe Choe, Bok-Hyung Lee, and Jung-Dong Park. 2018. "An X-band Bi-Directional Transmit/Receive Module for a Phased Array System in 65-nm CMOS" Sensors 18, no. 8: 2569. https://doi.org/10.3390/s18082569

APA StyleNguyen, V.-V., Nam, H., Choe, Y. J., Lee, B.-H., & Park, J.-D. (2018). An X-band Bi-Directional Transmit/Receive Module for a Phased Array System in 65-nm CMOS. Sensors, 18(8), 2569. https://doi.org/10.3390/s18082569