An Area-Efficient and Programmable 4 × 25-to-28.9 Gb/s Optical Receiver with DCOC in 0.13 µm SiGe BiCMOS

Abstract

1. Introduction

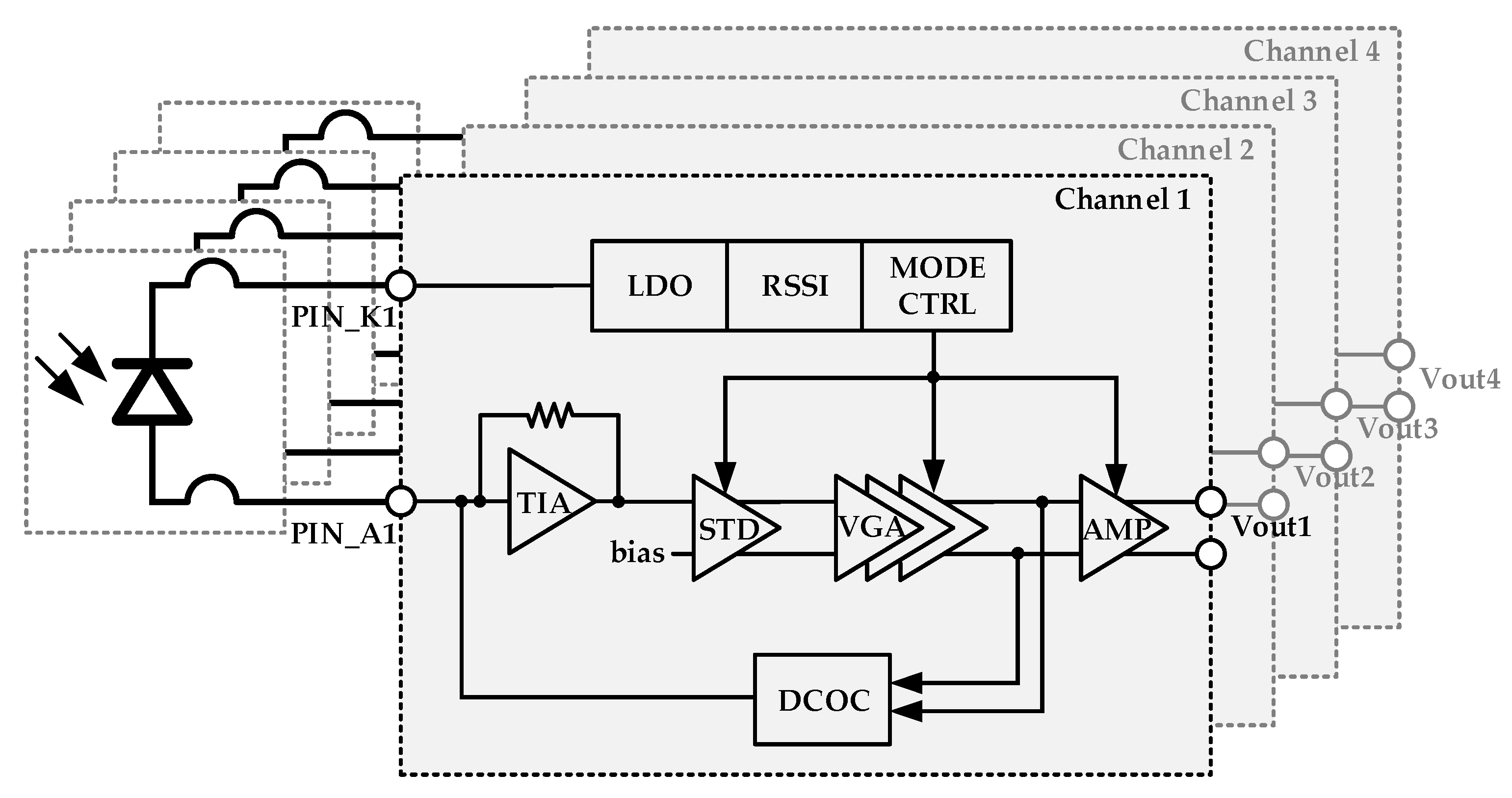

2. Architecture Design

3. Circuit Design

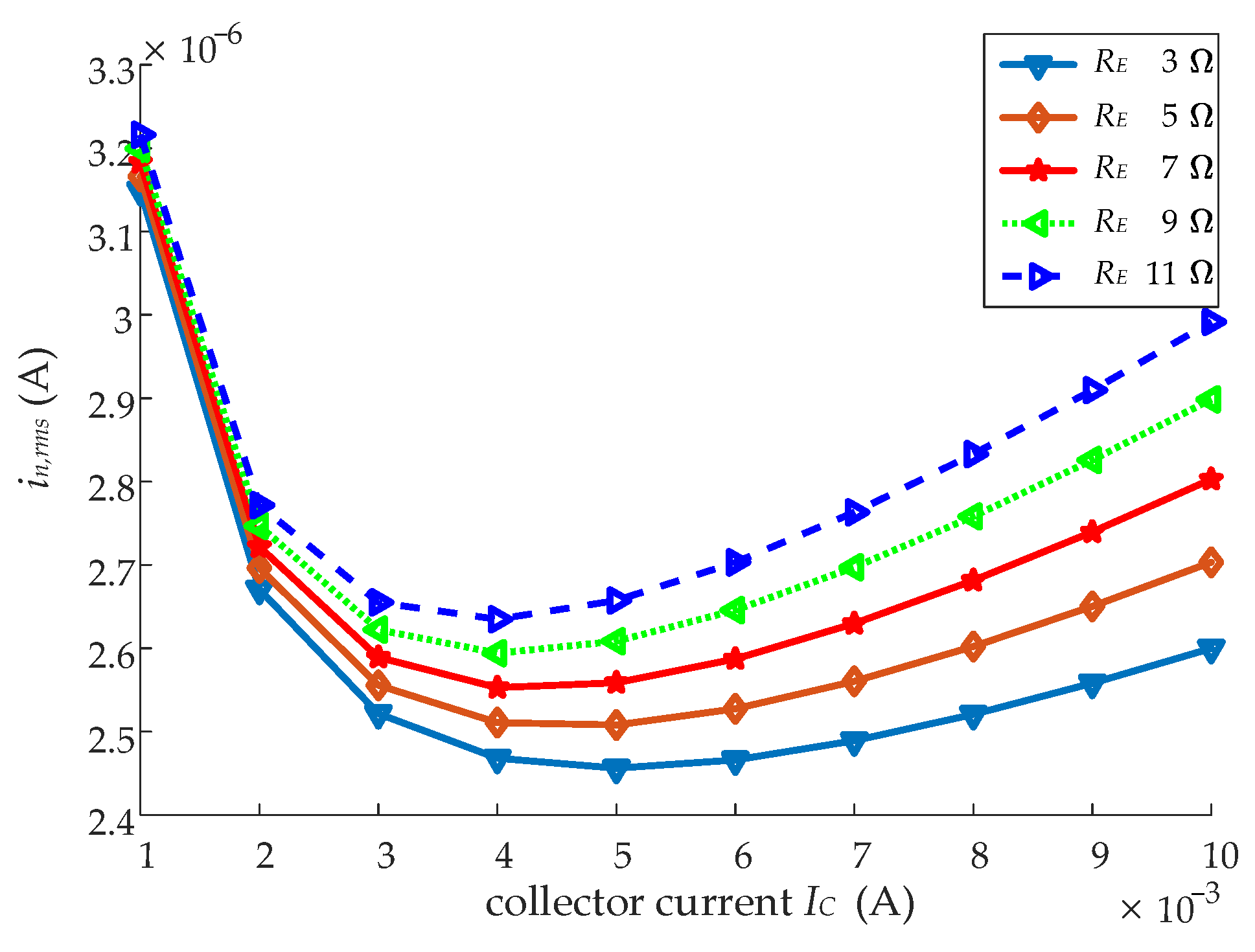

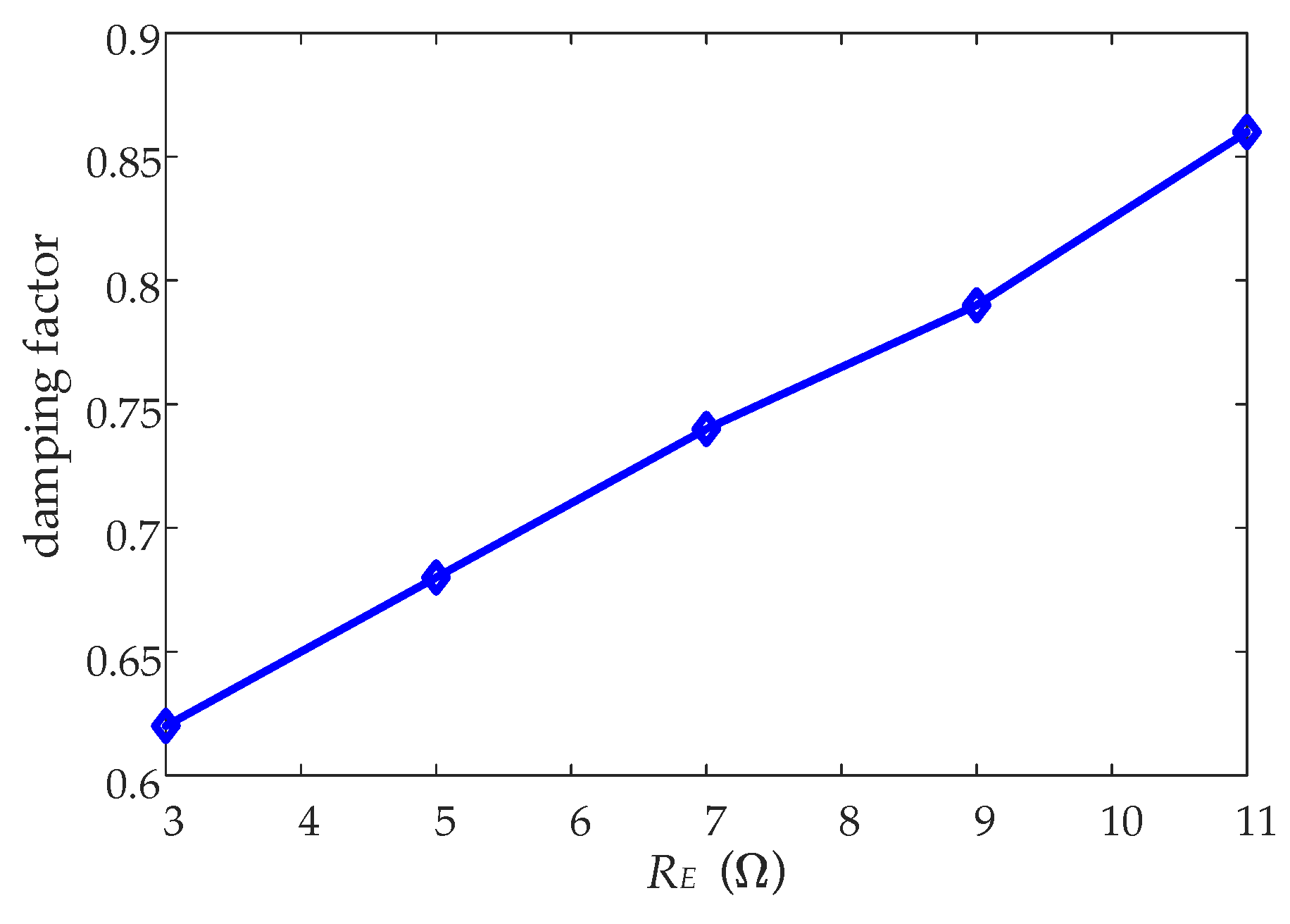

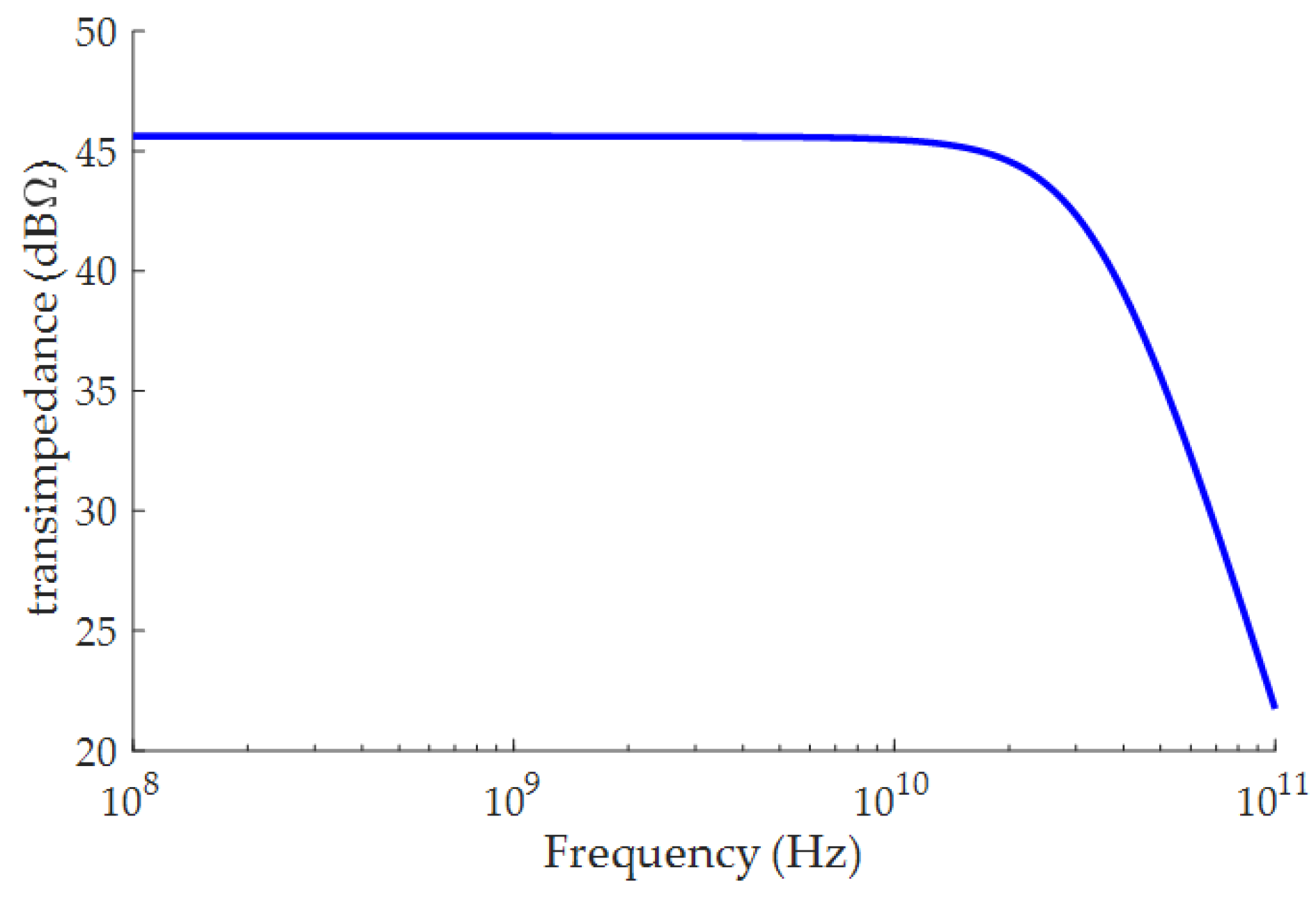

3.1. Transimpedance Amplifier

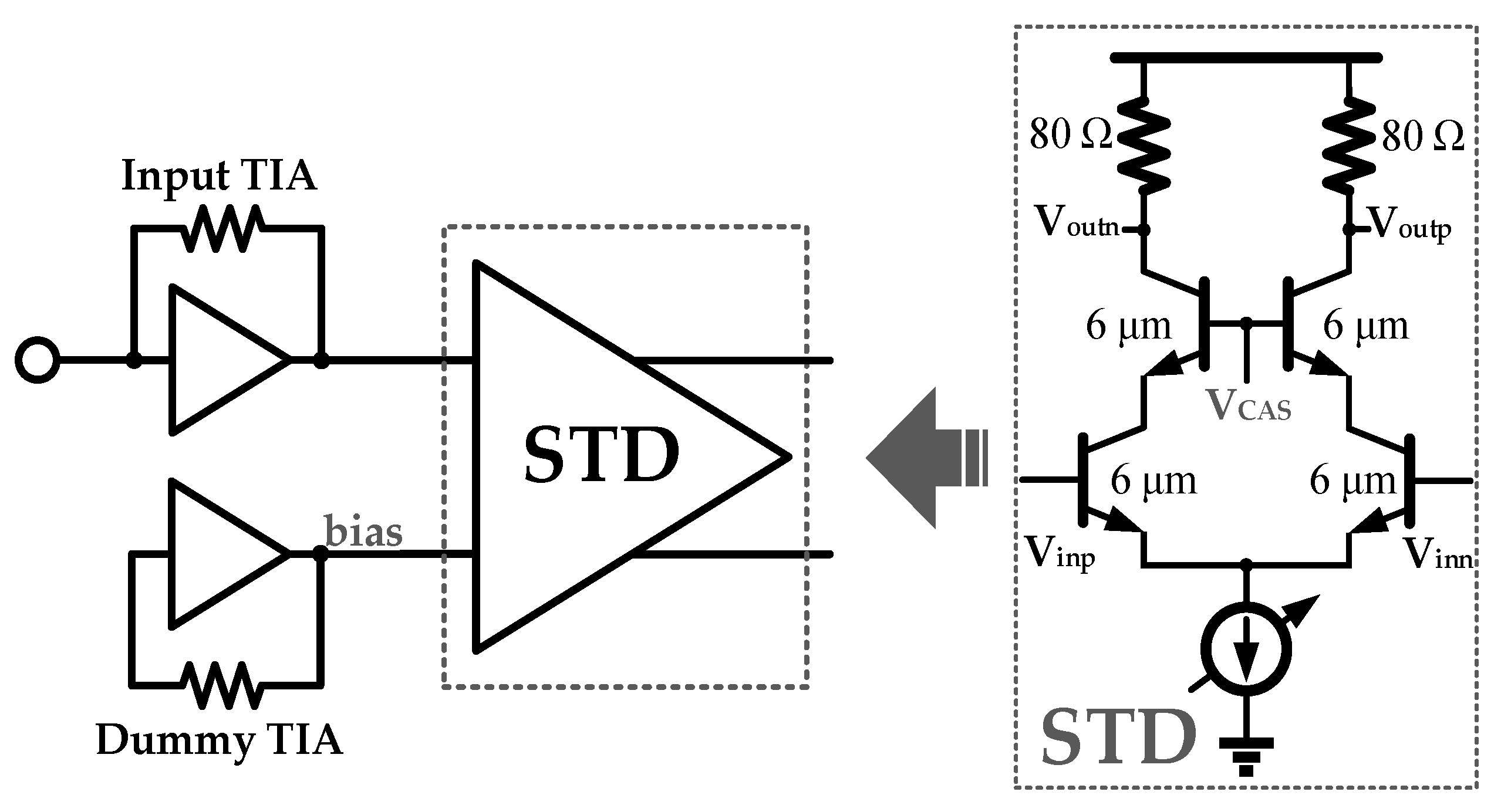

3.2. Single-Ended–Differential Amplifier

3.3. Variable-Gain Amplifiers

3.4. Output Amplifier

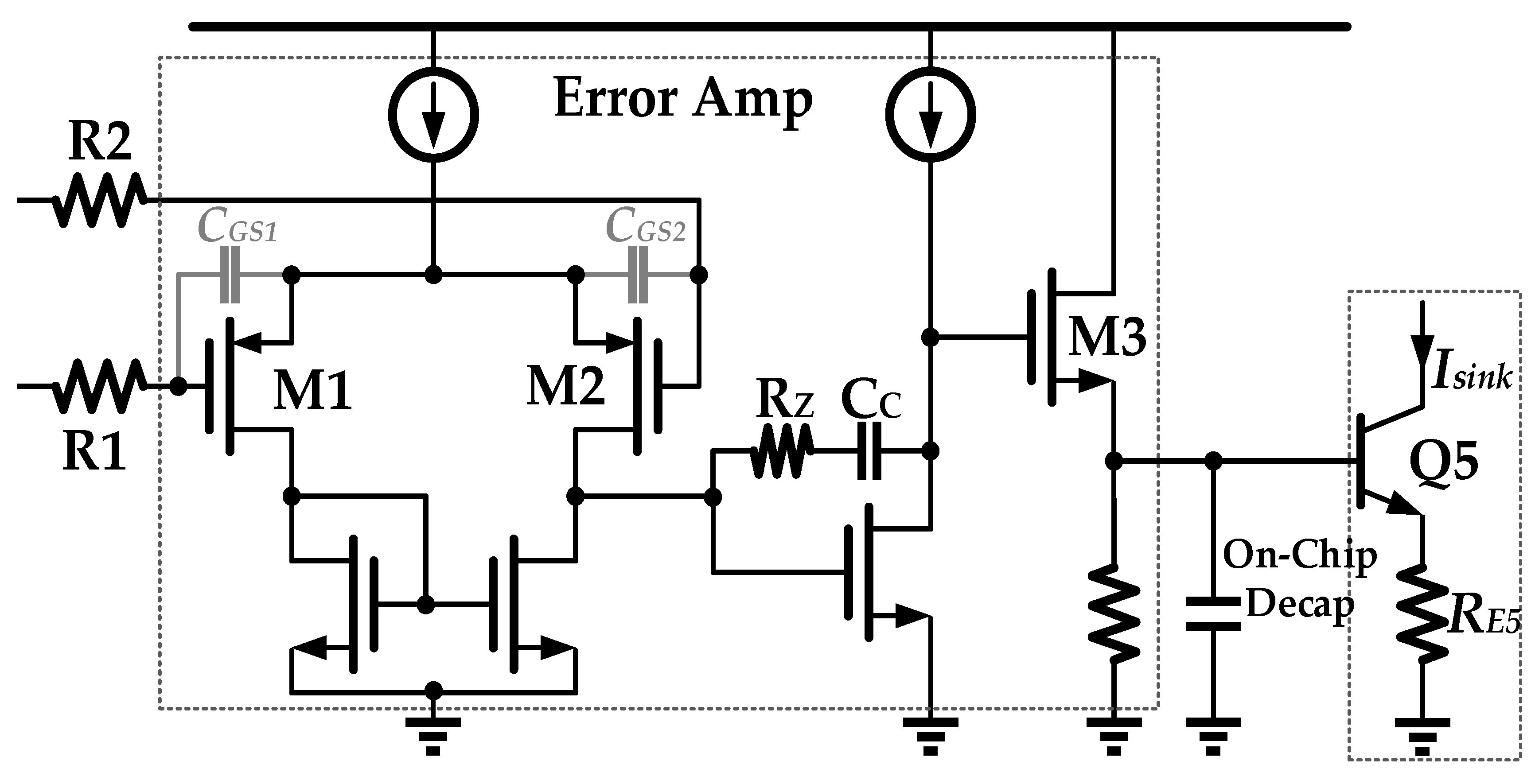

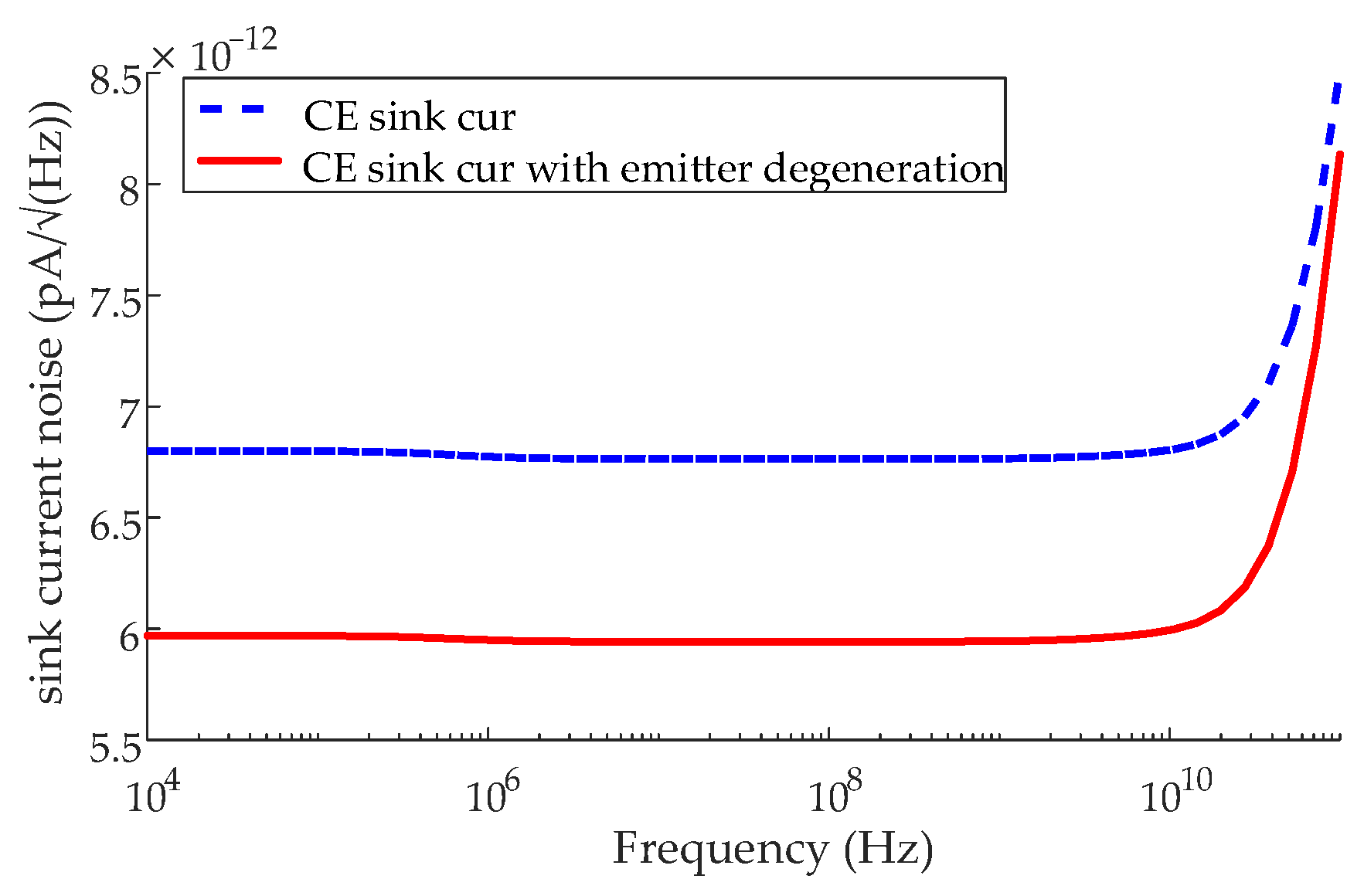

3.5. DC Offset Cancellation Loop

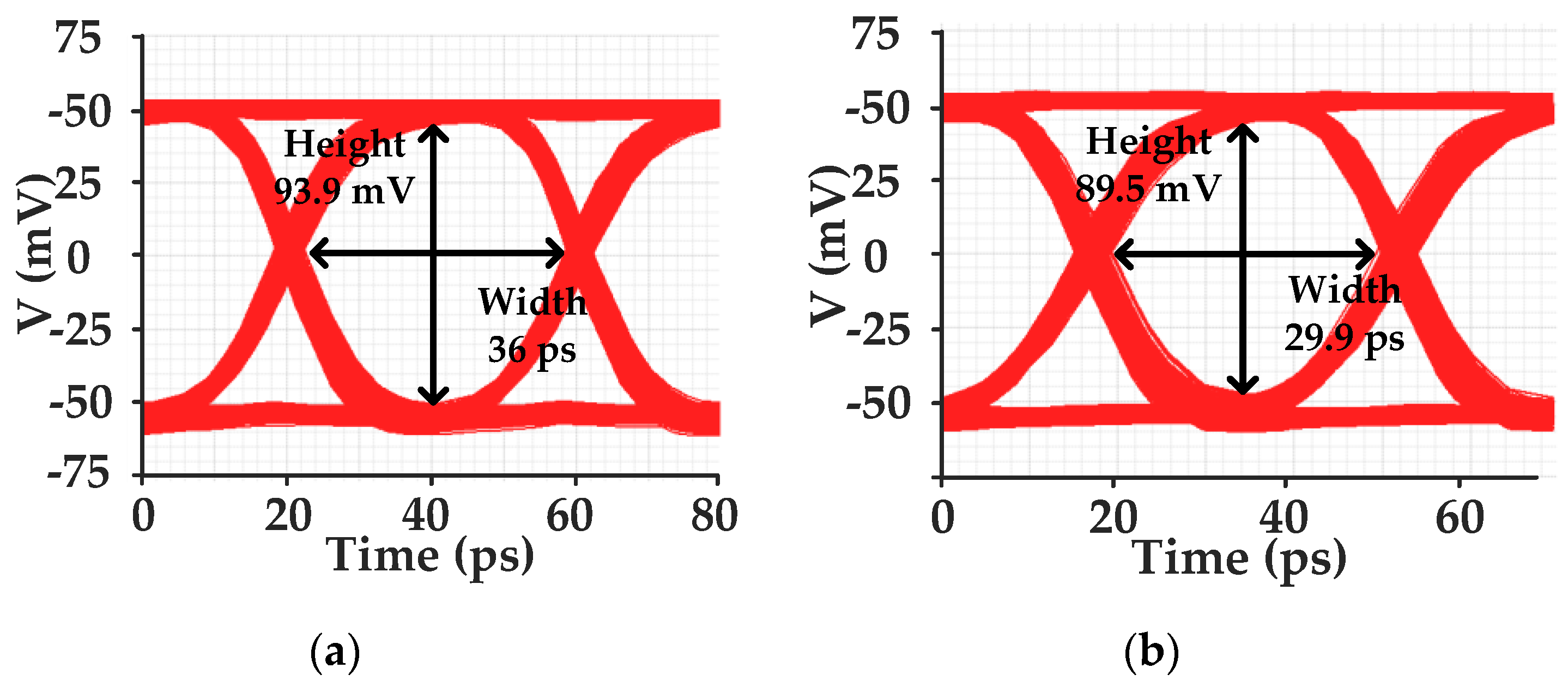

4. Measurement Results, Analysis, and Discussion

5. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Greshishchev, Y.; Schvan, P. A 60 dB gain 55 dB dynamic range 10 Gb/s broadband SiGe HBT limiting amplifier. In Proceedings of the 1999 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 17 February 1999; pp. 382–383. [Google Scholar]

- Shibasaki, T.; Tsunoda, Y.; Oku, H.; Ide, S.; Mori, T.; Koyanagi, Y. 4 × 25 Gb/s retimer ICs for optical links in 0.13 μm SiGe BiCMOS. In Proceedings of the 2015 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 22–26 February 2015; pp. 1–3. [Google Scholar]

- Knochenhauer, C.; Hauptmann, S.; Scheytt, J.C.; Ellinger, F. A Jitter-Optimized Differential 40-Gbit/s Transimpedance Amplifier in SiGe BiCMOS. IEEE Trans. Microw. Theory Tech. 2010, 58, 2538–2548. [Google Scholar] [CrossRef]

- Moeneclaey, B.; Verbrugghe, J.; Blache, F.; Goix, B.; Lanteri, D.; Duval, B.; Achouche, M.; Bauwelinck, J.; Yin, X. A 40-Gb/s Transimpedance Amplifier for Optical Links. IEEE Photonics Technol. Lett. 2015, 27, 1375–1378. [Google Scholar] [CrossRef]

- Schild, A.; Rein, H.; Mullrich, J.; Altenhain, L.; Blank, J.; Schrodinger, K. High-gain SiGe transimpedance amplifier array for a 12 × 10 Gb/s parallel optical-fiber link. IEEE J. Solid-State Circuits 2003, 38, 4–12. [Google Scholar] [CrossRef]

- Park, S.M. Four-channel SiGe transimpedance amplifier array for parallel optical interconnects. In Proceedings of the 2004 IEEE International Symposium on Circuits and Systems (ISCAS), Vancouver, BC, Canada, 23–26 May 2004. [Google Scholar]

- Park, S.M.; Toumazou, C.; Papavassiliou, C. A high-speed four-channel integrated optical receiver array using SiGe HBT technology. In Proceedings of the 2000 IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, 28–31 May 2000; pp. 433–436. [Google Scholar]

- Weiner, J.S.; Leven, A.; Houtsma, V.; Baeyens, Y.; Chen, Y.; Paschke, P.; Yang, Y.; Frackoviak, J.; Sung, W.; Tate, A.; et al. SiGe differential transimpedance amplifier with 50-GHz bandwidth. IEEE J. Solid-State Circuits 2003, 38, 1512–1517. [Google Scholar] [CrossRef]

- Li, D.; Zhang, Z.; Xie, Y.; Liu, M.; Yang, Q.; Geng, L. A 25 Gb/s low-noise optical receiver in 0.13 μm SiGe BiCMOS. In Proceedings of the 2016 IEEE International Conference on Electronics, Circuits and Systems (ICECS), Monte Carlo, Monaco, 11–14 December 2016; pp. 576–579. [Google Scholar]

- Kalogerakis, G.; Moran, T.; Nguyen, T.; Denoyer, G. A quad 25 Gb/s 270 mW TIA in 0.13 Mm BiCMOS with <0.15 dB crosstalk penalty. In Proceedings of the 2013 IEEE International Solid-State Circuits Conference Digest of Technical Papers, San Francisco, CA, USA, 17–21 February 2013; pp. 116–117. [Google Scholar]

- Proesel, J.; Schow, C.; Rylyakov, A. 25 Gb/s 3.6 pJ/b and 15 Gb/s 1.37 pJ/b VCSEL-based optical links in 90 nm CMOS. In Proceedings of the 2012 IEEE International Solid-State Circuits Conference, San Francisco, CA, USA, 19–23 February 2012; pp. 418–420. [Google Scholar]

- Kokolov, A.A.; Konkin, D.A.; Koryakovtsev, A.S.; Sheyerman, F.I.; Babak, L.I. Microwave Photonic ICs for 25 Gb/s Optical Link Based on SiGe BiCMOS Technology. Symmetry 2019, 11, 1453. [Google Scholar] [CrossRef]

- Shahramian, S.; Dehlaghi, B.; Liang, J.; Bespalko, R.; Dunwell, D.; Bailey, J.; Wang, B.; Sharif-Bakhtiar, A.; O’Farrell, M.; Tang, K.; et al. 30.5 A 1.41pJ/b 56Gb/s PAM-4 Wireline Receiver Employing Enhanced Pattern Utilization CDR and Genetic Adaptation Algorithms in 7nm CMOS. In Proceedings of the 2019 IEEE International Solid- State Circuits Conference, San Francisco, CA, USA, 17–21 February 2019; pp. 482–484. [Google Scholar]

- Mathew, M.; Hart, B.L.; Hayatleh, K. Design of a low-current shunt-feedback transimpedance amplifier with inherent loop-stability. Analog Integr. Circuits Sign. Proces. 2019, 99, 539–545. [Google Scholar] [CrossRef]

- Li, C.; Palermo, S. A Low-Power 26-GHz Transformer-Based Regulated Cascode SiGe BiCMOS Transimpedance Amplifier. IEEE J. Solid-State Circuits 2013, 48, 1264–1275. [Google Scholar] [CrossRef]

- Säckinger, E. Broadband Circuits for Optical Fiber Communication, 1st ed.; Agere Systems: Allentown, PA, USA, 2002; p. 119. [Google Scholar]

- Xuan, Z.; Ding, R.; Liu, Y.; Baehr-Jones, T.; Hochberg, M.; Aflatouni, F. A Low-Power Hybrid-Integrated 40-Gb/s Optical Receiver in Silicon. IEEE Trans. Microwave Theory Tech. 2018, 66, 589–595. [Google Scholar] [CrossRef]

- Alexander, S.B. Optical Communication Receiver Design, 1st ed.; The International Society for Optical Engineering: Bellingham, WA, USA, 1997; pp. 173–182. [Google Scholar]

- Takemoto, T.; Matsuoka, Y.; Yamashita, H.; Lee, Y.; Akita, F.; Arimoto, H.; Kokubo, M.; Ido, T. A 50.6-Gb/s 7.8-mW/Gb/s −7.4-dBm sensitivity optical receiver based on 0.18-µm SiGe BiCMOS technology. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar]

- Sedighi, B.; Scheytt, J.C. Low-Power SiGe BiCMOS Transimpedance Amplifier for 25-GBaud Optical Links. IEEE Trans. Circuits Syst. Express Briefs 2012, 59, 461–465. [Google Scholar] [CrossRef]

- Razavi, B. Design of Integrated Circuits for Optical Communications, 2nd ed.; John Wiley & Sons: Hoboken, NJ, USA, 2012; p. 24. [Google Scholar]

- Li, D.; Minoia, G.; Repossi, M.; Baldi, D.; Temporiti, E.; Mazzanti, A.; Svelto, F. A low-noise design technique for high-speed CMOS optical receivers. IEEE J. Solid-State Circuits 2014, 49, 1437–1447. [Google Scholar] [CrossRef]

- Säckinger, E. Analysis and Design of Transimpedance Amplifiers for Optical Receivers, 1st ed.; John Wiley & Sons: Hoboken, NJ, USA, 2018; pp. 191–197. [Google Scholar]

- El-Diwany, M.H.; Roulston, D.J.; Chamberlain, S.G. Design of low-noise bipolar transimpedance preamplifiers for optical receiver. In IEE Proceedings G - Electronic Circuits and Systems; IET: London, UK, 1981; Volume 128, pp. 299–306. [Google Scholar] [CrossRef]

- Gray, P.R.; Hurst, P.J.; Lewis, S.H.; Meyer, R.G. Analysis and Design of Analog Integrated Circuits, 5th ed.; John Wiley & Sons: Hoboken, NJ, USA, 2001. [Google Scholar]

- Palmisano, G.; Pennisi, S. CMOS single-input differential-output amplifier cells. In IEE Proceedings-Circuits, Devices and Systems; IET: London, UK, 2003; Volume 150, pp. 194–198. [Google Scholar] [CrossRef]

- Kumar, T.B.; Ma, K.; Yeo, K.S. A 4 GHz 60 dB variable gain amplifier with tunable DC offset cancellation in 65 nm CMOS. IEEE Microw. Wirel. Compon. Lett. 2014, 25, 37–39. [Google Scholar] [CrossRef]

- Zheng, Y.; Yan, J.; Xu, Y.P. A CMOS VGA With DC Offset Cancellation for Direct-Conversion Receivers. IEEE Trans. Circuits Syst. Regul. Pap. 2009, 56, 103–113. [Google Scholar] [CrossRef]

- Takemoto, T.; Yuki, F.; Yamashita, H.; Lee, Y.; Saito, T.; Tsuji, S.; Nishimura, S. A Compact 4 × 25-Gb/s 3.0 mW/Gb/s CMOS-Based Optical Receiver for Board-to-Board Interconnects. J. Light. Technol. 2010, 28, 3343–3350. [Google Scholar] [CrossRef]

| 25 Gb/s | 28.9 Gb/s | |

|---|---|---|

| Eye height (mV) | 154.2 | 114.8 |

| Eye width (UI) | 0.65 | 0.65 |

| Eye one level (mV) | 126.7 | 116.8 |

| Eye zero level (mV) | −129.0 | −119.5 |

| Crossing (%) | 51.2 | 51.8 |

| Reference | This Work | [10] | [11] | [12] | [29] |

|---|---|---|---|---|---|

| Data rate (Gb/s) | 25–28.9 (4 ch) | 25 (4 ch) | 25 | 25 | 25 (4 ch) |

| Technology | 0.13 μm SiGe BiCMOS | 0.13 μm SiGe BiCMOS | 90 nm CMOS | 0.25 μm SiGe BiCMOS | 65 nm CMOS |

| Transimpedance (dBΩ) | 62.8–77.5 * | 76 | 78.3 | 62.9 | 69.8 |

| Minimum input current (μApp) | 110 | 89 | 219 | N/A | 285 |

| Power supply (V) | 3.3 | 3.3 | 1.2 | 3.3/2.5 | 1.8/1.0 |

| DC power (mW) | 84.97/123.7 ** | 67.5 | 44.4 | 160 | 74 |

| Area (mm2) | 0.54 *** | 1.23*** | 0.81 | 1.24 | 0.4 *** |

© 2020 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Xu, H.; Liu, J.; Wang, Z.; Zhou, M.; Mo, J.; Yu, F. An Area-Efficient and Programmable 4 × 25-to-28.9 Gb/s Optical Receiver with DCOC in 0.13 µm SiGe BiCMOS. Electronics 2020, 9, 1032. https://doi.org/10.3390/electronics9061032

Xu H, Liu J, Wang Z, Zhou M, Mo J, Yu F. An Area-Efficient and Programmable 4 × 25-to-28.9 Gb/s Optical Receiver with DCOC in 0.13 µm SiGe BiCMOS. Electronics. 2020; 9(6):1032. https://doi.org/10.3390/electronics9061032

Chicago/Turabian StyleXu, Haojie, Jiarui Liu, Zhiyu Wang, Min Zhou, Jiongjiong Mo, and Faxin Yu. 2020. "An Area-Efficient and Programmable 4 × 25-to-28.9 Gb/s Optical Receiver with DCOC in 0.13 µm SiGe BiCMOS" Electronics 9, no. 6: 1032. https://doi.org/10.3390/electronics9061032

APA StyleXu, H., Liu, J., Wang, Z., Zhou, M., Mo, J., & Yu, F. (2020). An Area-Efficient and Programmable 4 × 25-to-28.9 Gb/s Optical Receiver with DCOC in 0.13 µm SiGe BiCMOS. Electronics, 9(6), 1032. https://doi.org/10.3390/electronics9061032