Single-Event Upset Characterization of a Shift Register in 16 nm FinFET Technology

Abstract

1. Introduction

- Single-Event Latchup (SEL): It happens in CMOS technology where ionizing radiation can activate parasitic bipolar transistors that are structurally intrinsic to this technology. Excessive current flow can permanently damage the device [8].

- Single-Event Gate Rupture (SEGR): A phenomenon that is particularly critical in devices with thin oxide and it is due to a high-energy particle that can create a localized electric field strong enough to break down the gate oxide of a MOSFET, leading to permanent transistor failure [9].

- Single-Event Burnout (SEB): This occurs in power devices, such as silicon carbide (SiC) devices, when a particle strike induces a high-current condition, potentially destroying the device due to thermal runaway [10].

- Single-Event Upset (SEU): Occurs when a single ionizing particle impacts a logical node, such as a memory cell, a register, or a latch, causing a logic state change and leading to data corruption. The ‘critical charge’ () defines the threshold charge that a circuit node can tolerate without a change in logic state, serving as a key measure of the impact of an SEU [3,4,11].

- Single-Event Transient (SET): Temporary voltage glitch induced in combinational logic circuits. If this glitch propagates and is latched into a sequential element (e.g., a flip-flop), it may result in an SEU [3].

- Multiple-Cell Upset (MCU): Occurs when a single radiation event simultaneously affects multiple adjacent memory cells, potentially causing correlated errors that are harder to correct. They are also called Multiple-Bit Upset (MBU) when the affected cells correspond to the bits from the same logical word in the memory [12].

- Rad-Hard By Process (RHBP): consists of the modification of some integrated circuit (IC) manufacturing steps, such as doping levels or layer thicknesses, so that they make the transistor radiation-tolerant. The drawback is a significant increase in the costs due to the custom modification in the production steps [14]. Additionally, radiation hardness can be improved by physical shields which prevent particles from reaching the IC. While effective, this method is expensive and requires a substantially large area on the silicon and/or of the whole system [15,16].

- Rad-Hard By Design (RHBD): involves the use of special add-on circuits to minimize the possibility of SEU. It is the most widely used method, and its implementation can be off-chip through dedicated software approaches or on-chip using specific circuit structures. Most common techniques are the Triple Modular Redundancy (TMR) that analyze the results of multiple redundant outputs, and the Quatro latch that uses redundant reinforced feedback architectures [3,17,18,19,20]. Moreover, it is possible to enhance the radiation hardness of transistors by using specific layout techniques such as squared gates, guard rings, and triple wells [21].

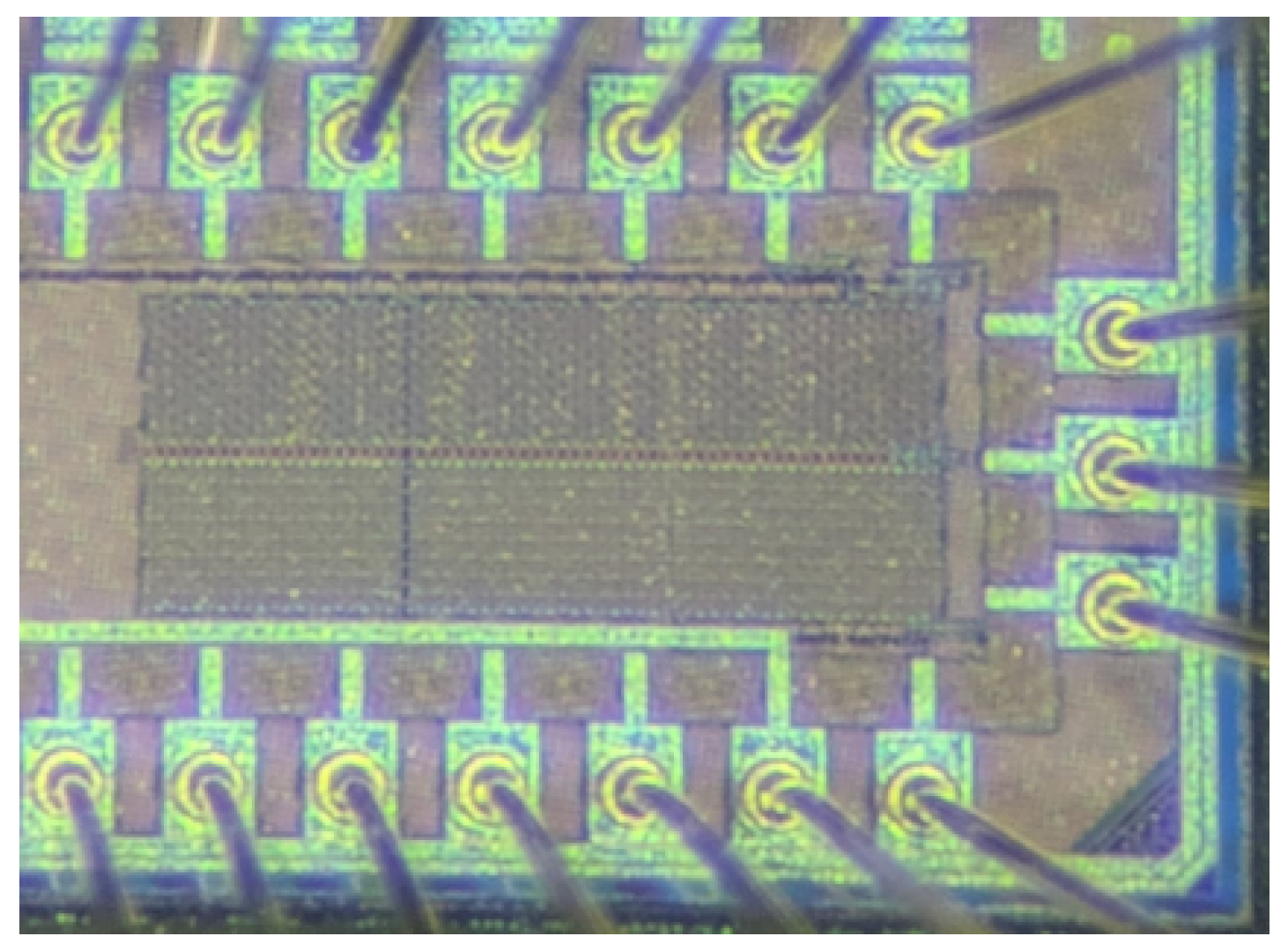

2. Proposed Design

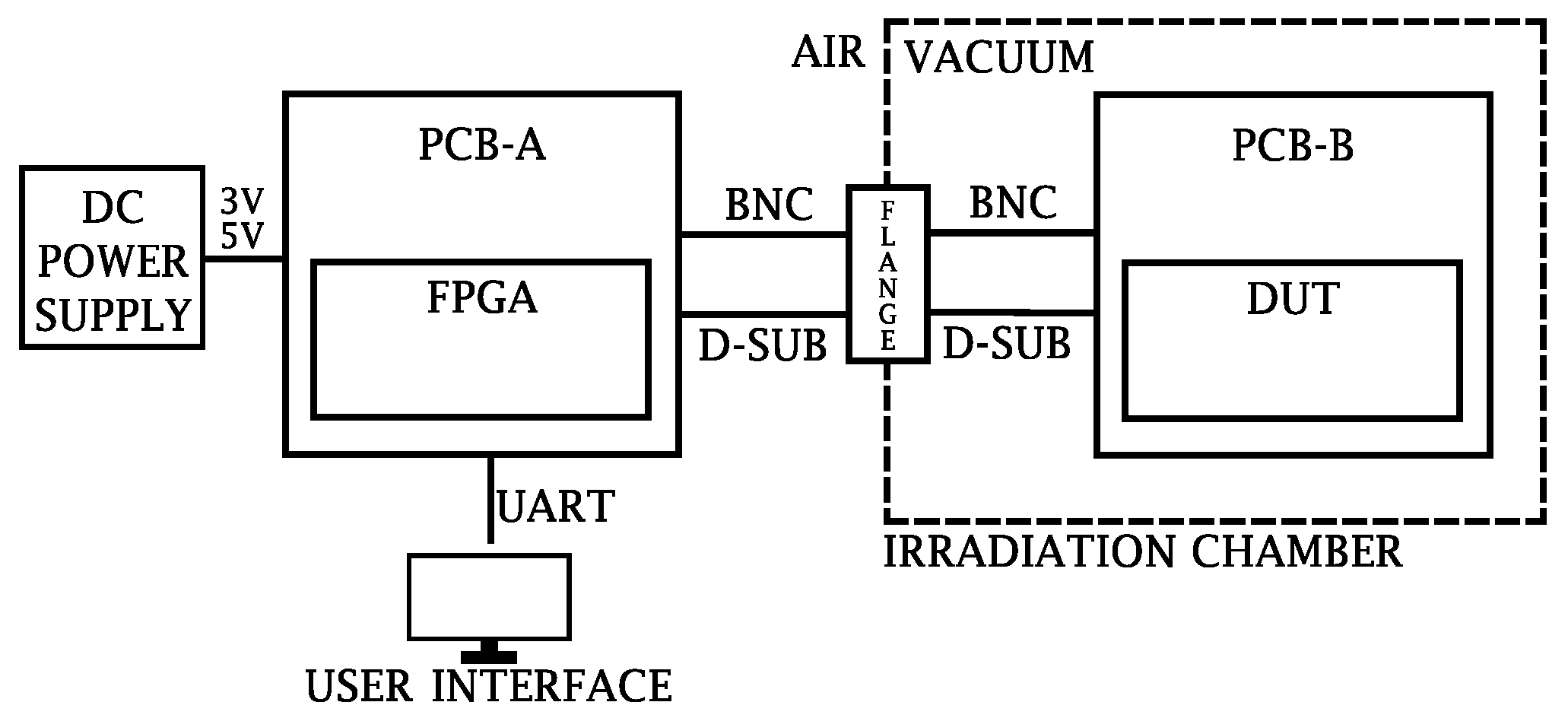

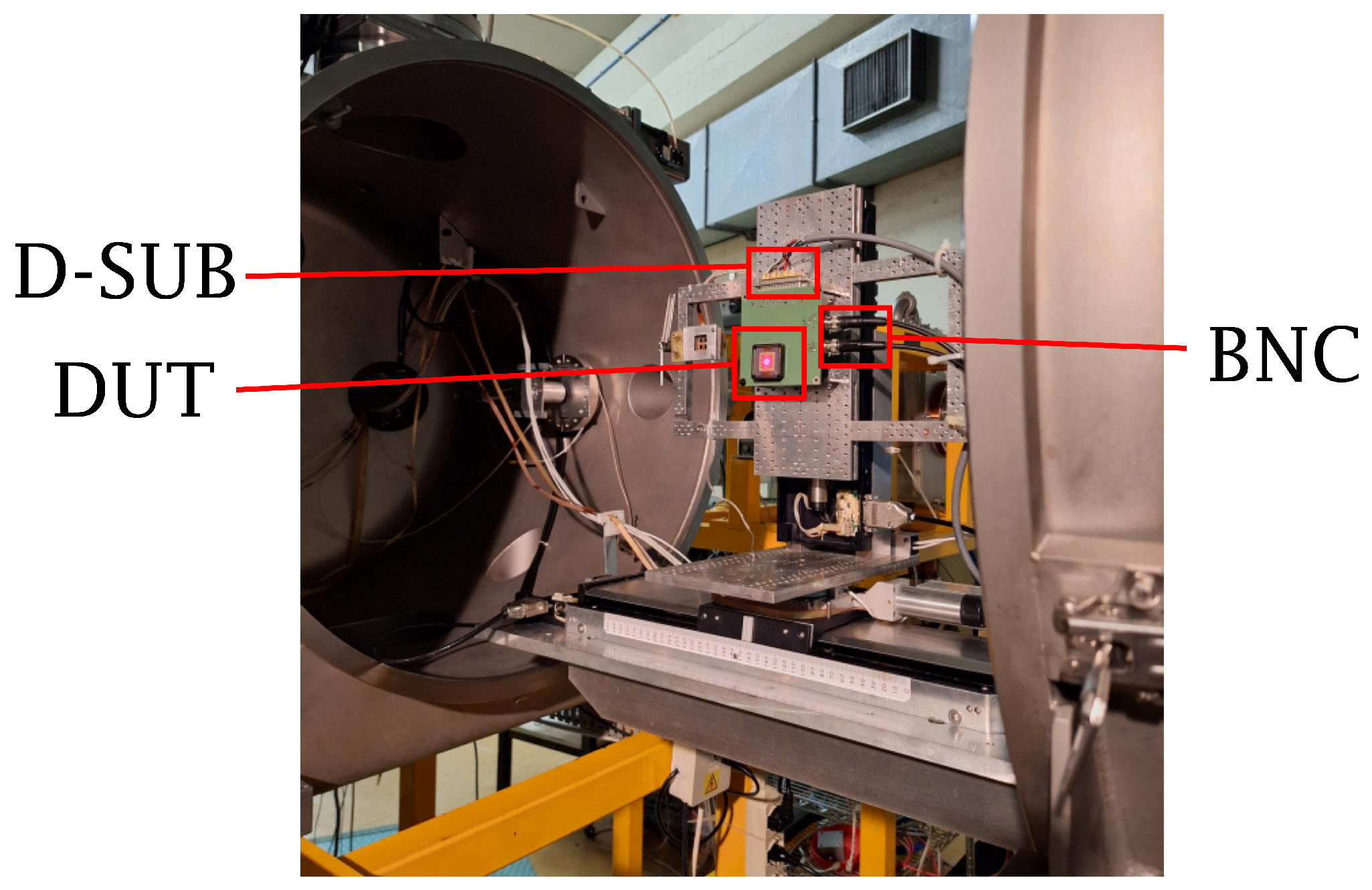

3. SEU Measurement Setup

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Stassinopoulos, E.; Raymond, J. The space radiation environment for electronics. Proc. IEEE 1988, 76, 1423–1442. [Google Scholar] [CrossRef]

- Whitmore, J.; Rivetta, C.; Shenai, A.; Elias, J.E.; Holm, S.; Baumbaugh, A.E.; Knickerbocker, K.; Zimmerman, T.; Ronzhin, A.; Yarema, R.J.; et al. Radiation validation for the CMS HCAL front-end electronics. In Proceedings of the 8th Workshop on Electronics for LHC Experiments, Colmar, France, 9–13 September 2002; pp. 433–438. [Google Scholar] [CrossRef]

- de Aguiar, Y.Q.; Wrobel, F.; Autran, J.-L.; Alía, R.G. Single-Event Effects, from Space to Accelerator Environments: Analysis, Prediction and Hardening by Design; Springer: Berlin/Heidelberg, Germany, 2025. [Google Scholar] [CrossRef]

- Bettini, A. Introduction to Elementary Particle Physics; Cambridge University Press: Cambridge, UK, 2008. [Google Scholar]

- Schwank, J.R.; Shaneyfelt, M.R.; Fleetwood, D.M.; Felix, J.A.; Dodd, P.E.; Paillet, P.; Ferlet-Cavrois, V. Radiation Effects in MOS Oxides. IEEE Trans. Nucl. Sci. 2008, 55, 1833–1853. [Google Scholar] [CrossRef]

- Calligaro, C.; Gatti, U. Rad-Hard Semiconductor Memories; River Publisher: Gistrup, Denmark, 2018. [Google Scholar]

- Dodd, P.E.; Massengill, L.W. Basic mechanisms and modeling of single-event upset in digital microelectronics. IEEE Trans. Nucl. Sci. 2003, 50, 583–602. [Google Scholar] [CrossRef]

- Guagliardo, S.; Wrobel, F.; Aguiar, Y.Q.; Autran, J.-L.; Leroux, P.; Saigné, F.; Pouget, V.; Touboul, A.D. Single-Event Latchup sensitivity: Temperature effects and the role of the collected charge. Microelectron. Reliab. 2021, 119, 114087. [Google Scholar] [CrossRef]

- Silvestri, M.; Gerardin, S.; Paccagnella, A.; Ghidini, G. Gate Rupture in Ultra-Thin Gate Oxides Irradiated With Heavy Ions. IEEE Trans. Nucl. Sci. 2009, 56, 1964–1970. [Google Scholar] [CrossRef]

- Witulski, A.F.; Ball, D.R.; Galloway, K.F.; Javanainen, A.; Lauenstein, J.-M.; Sternberg, A.L.; Schrimpf, R.D. Single-Event Burnout Mechanisms in SiC Power MOSFETs. IEEE Trans. Nucl. Sci. 2018, 65, 1951–1955. [Google Scholar] [CrossRef]

- Wang, F.; Agrawal, V.D. Single Event Upset: An Embedded Tutorial. In Proceedings of the 21st International Conference on VLSI Design (VLSID 2008), Hyderabad, India, 4–8 January 2008; pp. 429–434. [Google Scholar] [CrossRef]

- Borghello, G.; Ceresa, D.; Pejašinović, R.; Diaz, F.P.; Bergamin, G.; Kloukinas, K. Single Event Effects Characterization of a Commercial 28 nm CMOS Technology. In Proceedings of the TWEPP 2018 Topical Workshop on Electronics for Particle Physics, Geremeas, Italy, 1–6 October 2023; Available online: https://indico.cern.ch/event/1255624/contributions/5443894/ (accessed on 1 December 2024).

- European Cooperation for Space Standardization (ECSS) Report. Engineering Techniques for Radiation Effects Mitigation in ASICs and FPGAs Handbook—ECSS-E-HB-20-40A. Available online: https://ecss.nl/home/ecss-e-hb-20-40a-engineering-techniques-for-radiation-effects-mitigation-in-asics-and-fpgas-handbook/ (accessed on 1 December 2024).

- Gonzalez-Velo, Y.; Mahmud, A.; Chen, W.; Taggart, J.L.; Barnaby, H.J.; Kozicki, M.N.; Ailavajhala, M.; Holbert, K.E.; Mitkova, M. Radiation Hardening by Process of CBRAM Resistance Switching Cells. IEEE Trans. Nucl. Sci. 2016, 63, 2145–2151. [Google Scholar] [CrossRef]

- Millward, D.; Strobel, D. The effectiveness of Rad-Pak ICs for space-radiation hardening. In Proceedings of the 40th Conference Proceedings on Electronic Components and Technology, Las Vegas, NV, USA, 20–23 May 1990; Volume 2, pp. 913–916. [Google Scholar] [CrossRef]

- Tang, L.; Wan, C.; Sun, X.; Zhang, M.; Ye, W. Research on Anti-Radiation Hardening Technology of Packaging. In Proceedings of the 2022 23rd International Conference on Electronic Packaging Technology (ICEPT), Dalian, China, 10–13 August 2022; pp. 1–4. [Google Scholar] [CrossRef]

- Dang, L.D.T.; Kang, M.; Kim, J.; Chang, I.-J. Studying the Variation Effects of Radiation Hardened Quatro SRAM Bit-Cell. IEEE Trans. Nucl. Sci. 2016, 63, 2399–2401. [Google Scholar] [CrossRef]

- Chong, K.-S.; Lwin, N.K.Z.; Shu, W.; Chang, J.S. Radiation-Hardened-by-Design (RHBD) Digital Design Approaches: A Case Study on an 8051 Microcontroller. In Proceedings of the 2020 IEEE International Symposium on Circuits and Systems (ISCAS), Seville, Spain, 10–21 October 2020; pp. 1–5. [Google Scholar] [CrossRef]

- Nicolaidis, M. Design for soft error mitigation. IEEE Trans. Device Mater. Reliab. 2005, 5, 405–418. [Google Scholar] [CrossRef]

- Li, Y.-Q.; Wang, H.-B.; Liu, R.; Chen, L.; Nofal, I.; Shi, S.-T.; He, A.-L.; Guo, G.; Baeg, S.H.; Wen, S.-J.; et al. A Quatro-Based 65-nm Flip-Flop Circuit for Soft-Error Resilience. IEEE Trans. Nucl. Sci. 2017, 64, 1554–1561. [Google Scholar] [CrossRef]

- Wang, H.; Dai, X.; Ibrahim, Y.M.Y.; Sun, H.; Nofal, I.; Cai, L.; Guo, G.; Shen, Z.; Chen, L. A Layout-Based Rad-Hard DICE Flip-Flop Design. J. Electron. Test. 2019, 35, 111–117. [Google Scholar] [CrossRef]

- Nsengiyumva, P.; Ball, D.R.; Kauppila, J.S.; Tam, N.; McCurdy, M.; Holman, W.T.; Alles, M.L.; Bhuva, B.L.; Massengill, L.W. A Comparison of the SEU Response of Planar and FinFET D Flip-Flops at Advanced Technology Nodes. IEEE Trans. Nucl. Sci. 2016, 63, 266–272. [Google Scholar] [CrossRef]

- Shida, W.; Min, T.; Hongwei, Z.; Bo, M.; Yi, S. Evaluation of Single-Event Upset in FinFET Device. In Proceedings of the 2023 5th International Conference on Radiation Effects of Electronic Devices (ICREED), Kunming, China, 24–27 May 2023; pp. 1–7. [Google Scholar] [CrossRef]

- Chi, Y.; Wu, Z.; Huang, P.; Sun, Q.; Liang, B.; Zhao, Z. Characterization of single-event transients induced by high LET heavy ions in 16 nm bulk FinFET inverter chains. Microelectron. Reliab. 2022, 130, 114490. [Google Scholar] [CrossRef]

- Danilov, I.A.; Gorbunov, M.S.; Antonov, A.A. SET Tolerance of 65 nm CMOS Majority Voters: A Comparative Study. IEEE Trans. Nucl. Sci. 2014, 61, 1597–1602. [Google Scholar] [CrossRef]

- Wyss, J.; Bisello, D.; Pantano, D. SIRAD: An irradiation facility at the LNL Tandem accelerator for radiation damage studies on semiconductor detectors and electronic devices and systems. Nucl. Instruments Methods Phys. Res. Sect. A Accel. Spectrometers Detect. Assoc. Equip. 2001, 462, 426–434. [Google Scholar] [CrossRef]

- Silvestrin, L. Characterization of Electronic Circuits with the SIRAD IEEM: Developments and First Results. Ph.D. Thesis, Physics, University of Padua, Padua, Italy, 2011. Available online: https://www.research.unipd.it/handle/11577/3421637 (accessed on 1 December 2024).

- Ziegler, J.F. SRIM-2003. Nucl. Instruments Methods Phys. Res. Sect. B Beam Interact. Mater. Atoms. 2004, 219–220, 1027–1036. [Google Scholar] [CrossRef]

- Nsengiyumva, P.; Massengill, L.W.; Alles, M.L.; Bhuva, B.L.; Ball, D.R.; Kauppila, J.S.; Haeffner, T.D.; Holman, W.T.; Reed, R.A. Analysis of Bulk FinFET Structural Effects on Single-Event Cross Sections. IEEE Trans. Nucl. Sci. 2017, 64, 441–448. [Google Scholar] [CrossRef]

- Mattiazzo, S.; Bonaldo, S.; Matteis, M.D.; Fary, F.; Pipino, A.; Resta, F.; Baschirotto, A. 28 nm High-k Bulk Digital Circuit Performance (SEU) After Heavy Ion Exposure. In TWEPP 2018 Topical Workshop on Electronics for Particle Physics. 2018. Available online: https://indico.cern.ch/event/697988/contributions/3055934/ (accessed on 1 December 2024).

- Sun, Q.; Guo, Y.; Liang, B.; Tao, M.; Chi, Y.; Huang, P.; Wu, Z.; Luo, D.; Chen, J. Higher NMOS Single Event Transient Susceptibility Compared to PMOS in Sub-20nm Bulk FinFET. IEEE Electron. Device Lett. 2023, 44, 1712–1715. [Google Scholar] [CrossRef]

- Yoshida, K.; Nakajima, R.; Sugitani, S.; Ito, T.; Furuta, J.; Kobayashi, K. SEU Sensitivity of PMOS and NMOS Transistors in a 65 nm Bulk Process by α-Particle Irradiation. In Proceedings of the 2023 International Conference on IC Design and Technology (ICICDT), Tokyo, Japan, 25–28 September 2023; pp. 72–75. [Google Scholar] [CrossRef]

| Ion Source | Energy [MeV] | LET | Range [µm] |

|---|---|---|---|

| 16 | 108 | 3.16 | 107 |

| 28 | 157 | 8.9 | 61 |

| 58 | 220 | 30.68 | 37 |

| 107 | 266 | 58.4 | 29 |

| Ion Source | Tilt Angle | LET | Range [µm] |

|---|---|---|---|

| 58 | 0° | 29.36 | 37 |

| 58 | 30° | 33.9 | 32 |

| 28 | 0° | 8.7 | 59.32 |

| 28 | 45° | 12.31 | 41.9 |

| Ion Source | Tilt Angle | LET

| Data | Config. | Fluence | Nr. of SEU a | Cross- Section per Bit [cm2] |

|---|---|---|---|---|---|---|---|

| 28 | 0° | 8.7 | 1 | TMR | 2.00 | 0 | 0 |

| 28 | 45° | 12.31 | 1 | TMR | 3.71 | 0 | 0 |

| 58 | 0° | 29.36 | 1 | TMR | 9.84 | 21 | 1.42 |

| 58 | 30° | 33.9 | 1 | TMR | 5.44 | 16 | 1.96 |

| 58 | 0° | 29.36 | 0 | TMR | 5.51 | 0 | 0 |

| 28 | 45° | 12.31 | 1 | Standard | 8.73 | 0 | 0 |

| 58 | 0° | 29.36 | 1 | Standard | 5.53 | 10 | 1.21 |

| 58 | 30° | 33.9 | 1 | Standard | 6.03 | 9 | 1.17 |

| 58 | 0° | 29.36 | 0 | Standard | 1.35 | 0 | 0 |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

D’Aniello, F.; Tettamanti, M.; Shah, S.A.A.; Mattiazzo, S.; Bonaldo, S.; Vadalà, V.; Baschirotto, A. Single-Event Upset Characterization of a Shift Register in 16 nm FinFET Technology. Electronics 2025, 14, 1421. https://doi.org/10.3390/electronics14071421

D’Aniello F, Tettamanti M, Shah SAA, Mattiazzo S, Bonaldo S, Vadalà V, Baschirotto A. Single-Event Upset Characterization of a Shift Register in 16 nm FinFET Technology. Electronics. 2025; 14(7):1421. https://doi.org/10.3390/electronics14071421

Chicago/Turabian StyleD’Aniello, Federico, Marcello Tettamanti, Syed Adeel Ali Shah, Serena Mattiazzo, Stefano Bonaldo, Valeria Vadalà, and Andrea Baschirotto. 2025. "Single-Event Upset Characterization of a Shift Register in 16 nm FinFET Technology" Electronics 14, no. 7: 1421. https://doi.org/10.3390/electronics14071421

APA StyleD’Aniello, F., Tettamanti, M., Shah, S. A. A., Mattiazzo, S., Bonaldo, S., Vadalà, V., & Baschirotto, A. (2025). Single-Event Upset Characterization of a Shift Register in 16 nm FinFET Technology. Electronics, 14(7), 1421. https://doi.org/10.3390/electronics14071421