Hybrid Radio-Frequency-Energy- and Solar-Energy-Harvesting-Integrated Circuit for Internet of Things and Low-Power Applications

Abstract

1. Introduction

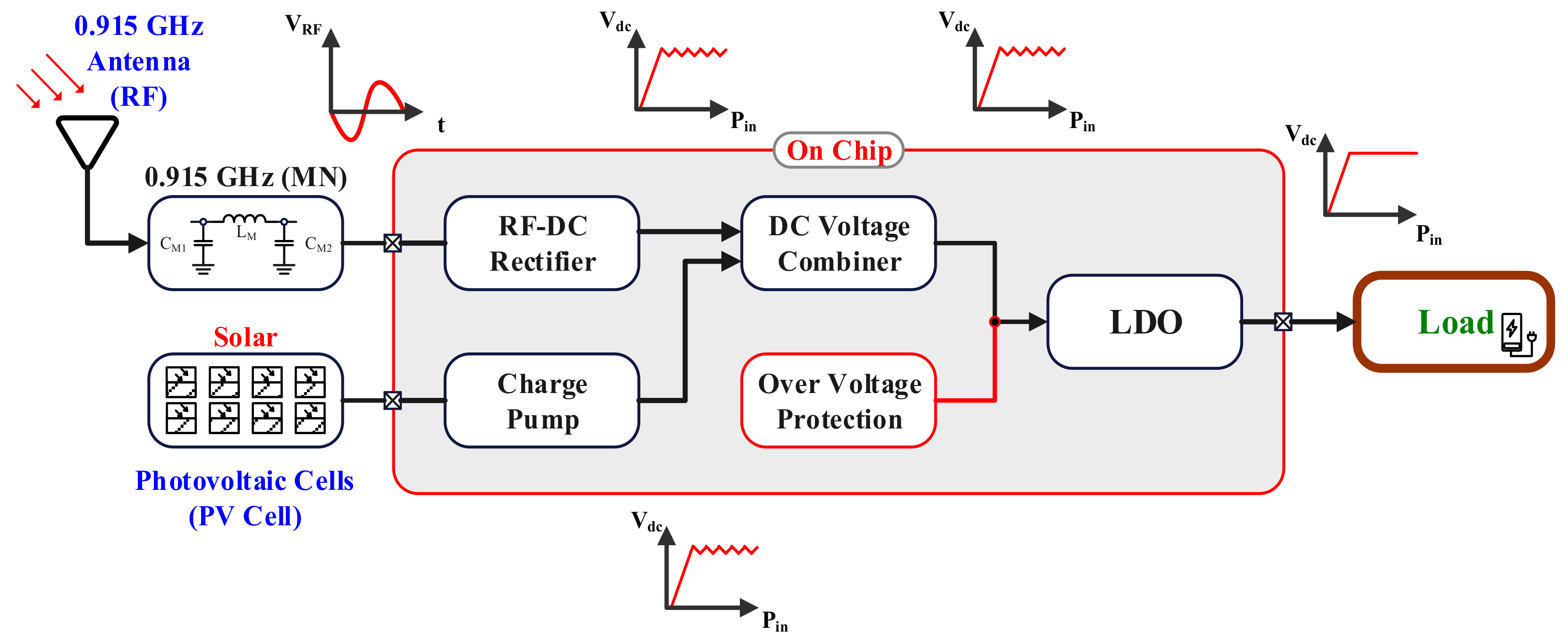

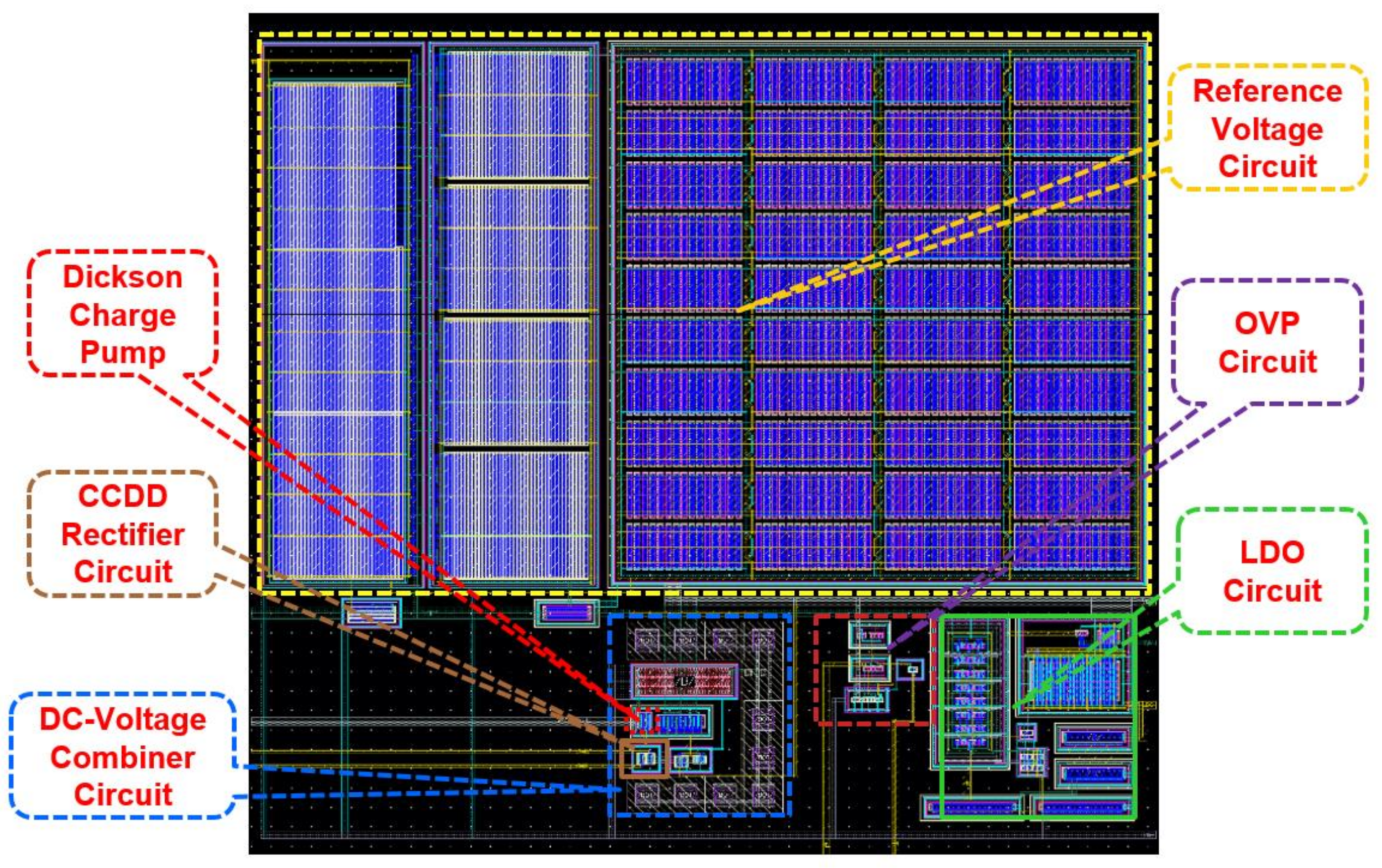

2. Circuit Implementation of Hybrid Energy-Harvesting System

2.1. Balun’s Function

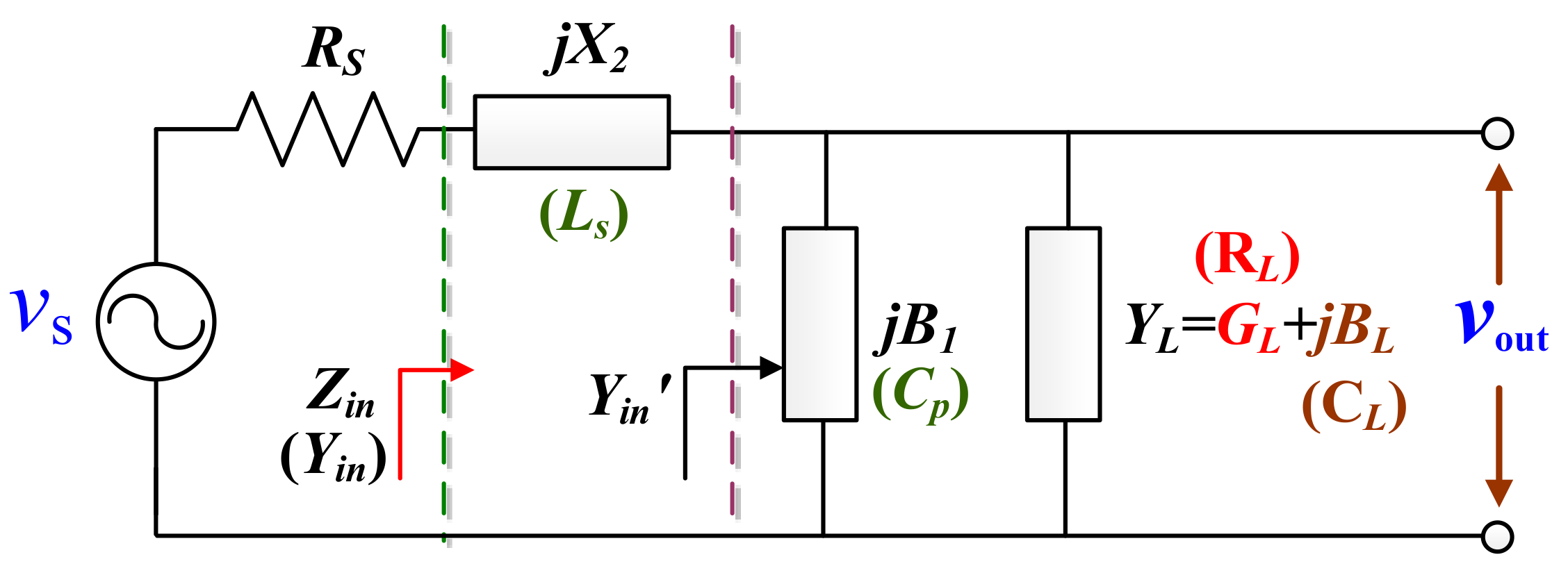

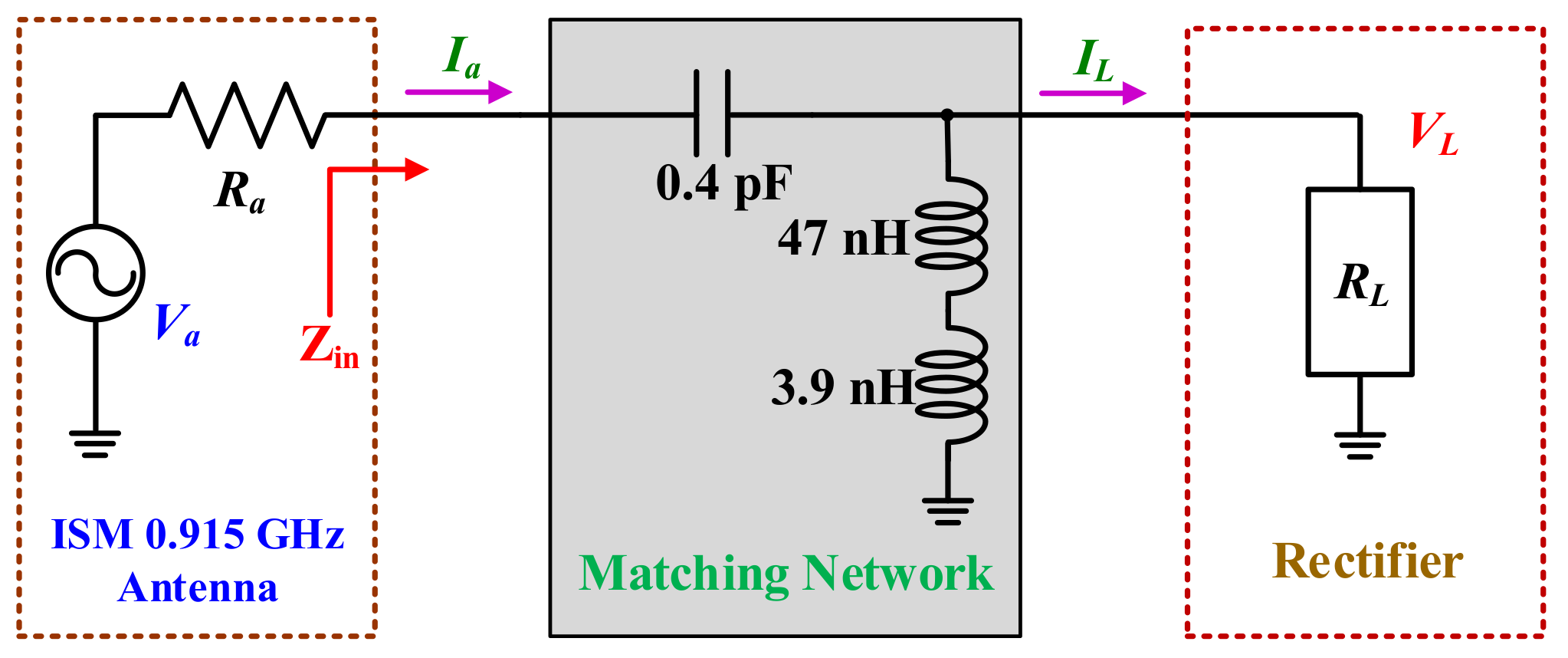

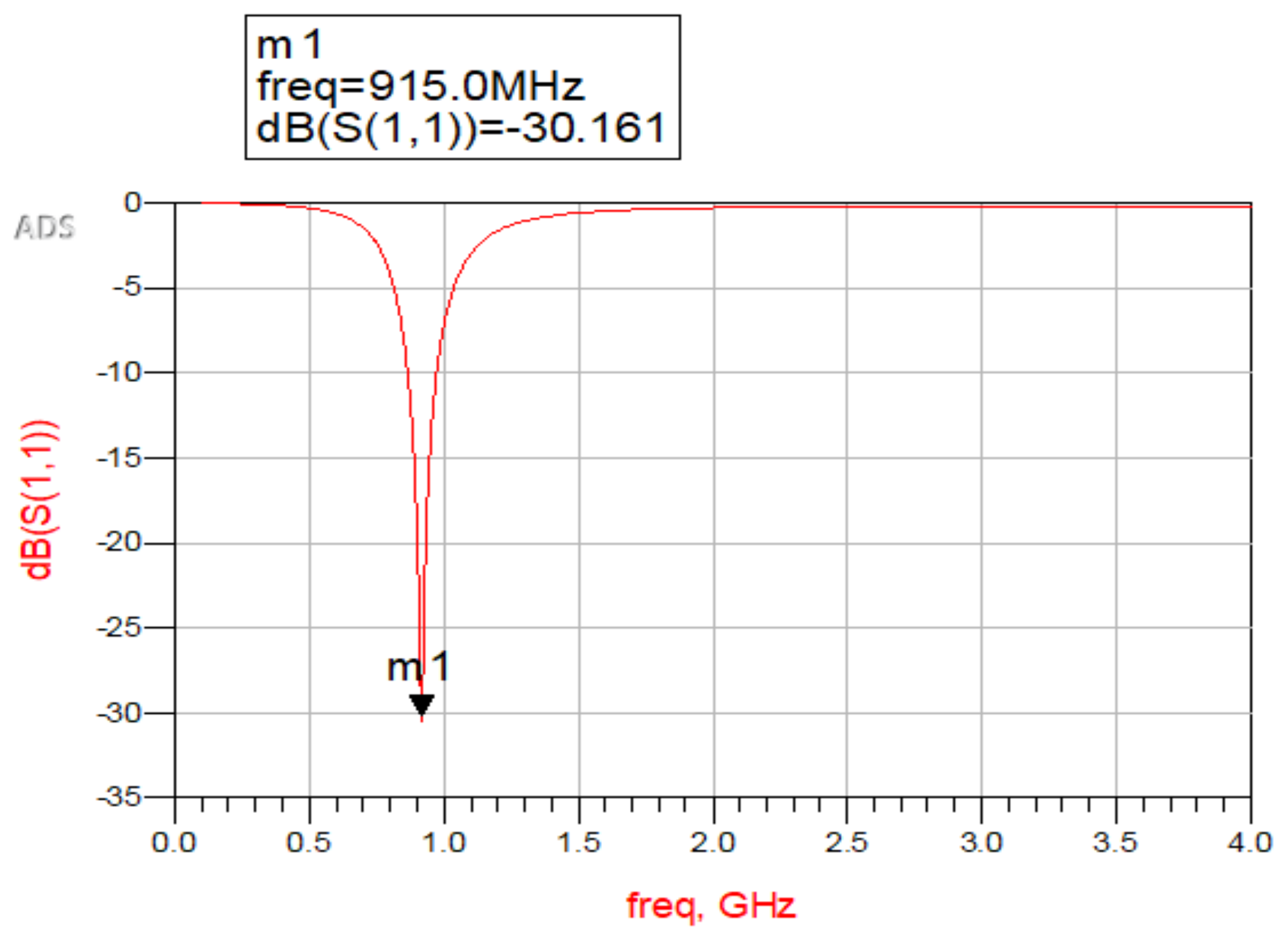

2.2. Matching Network

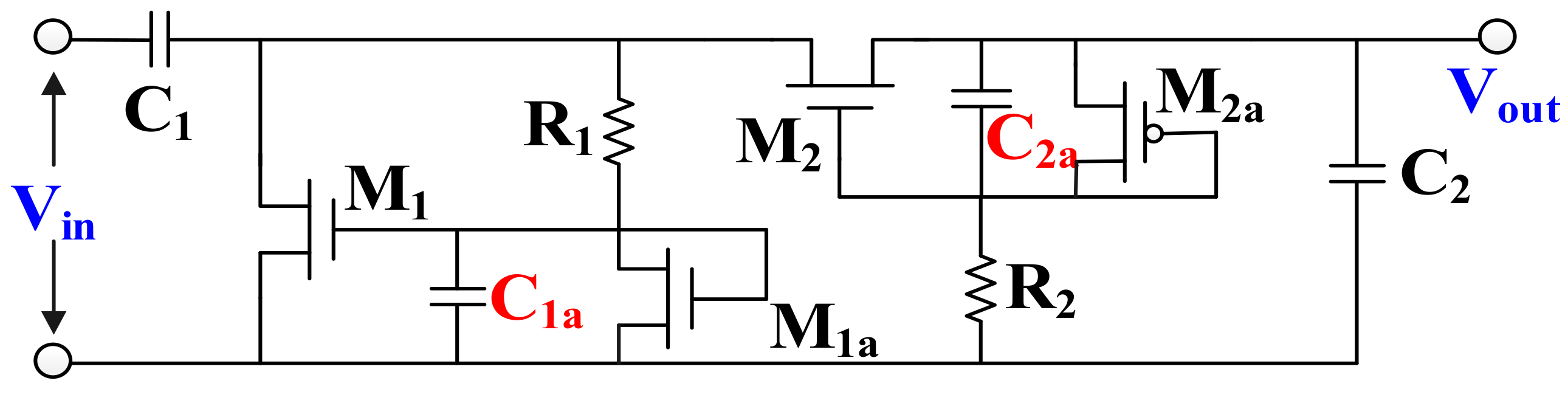

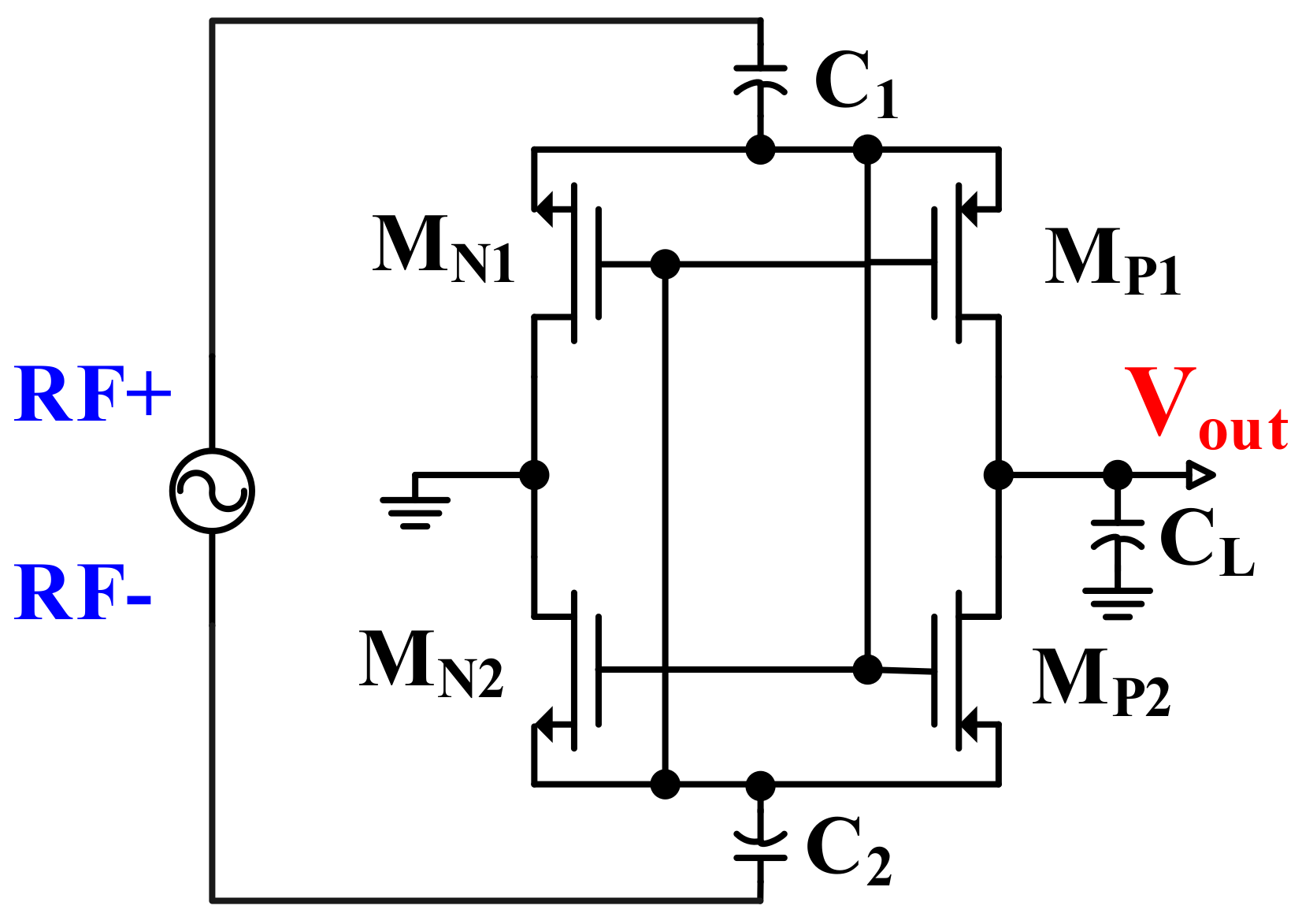

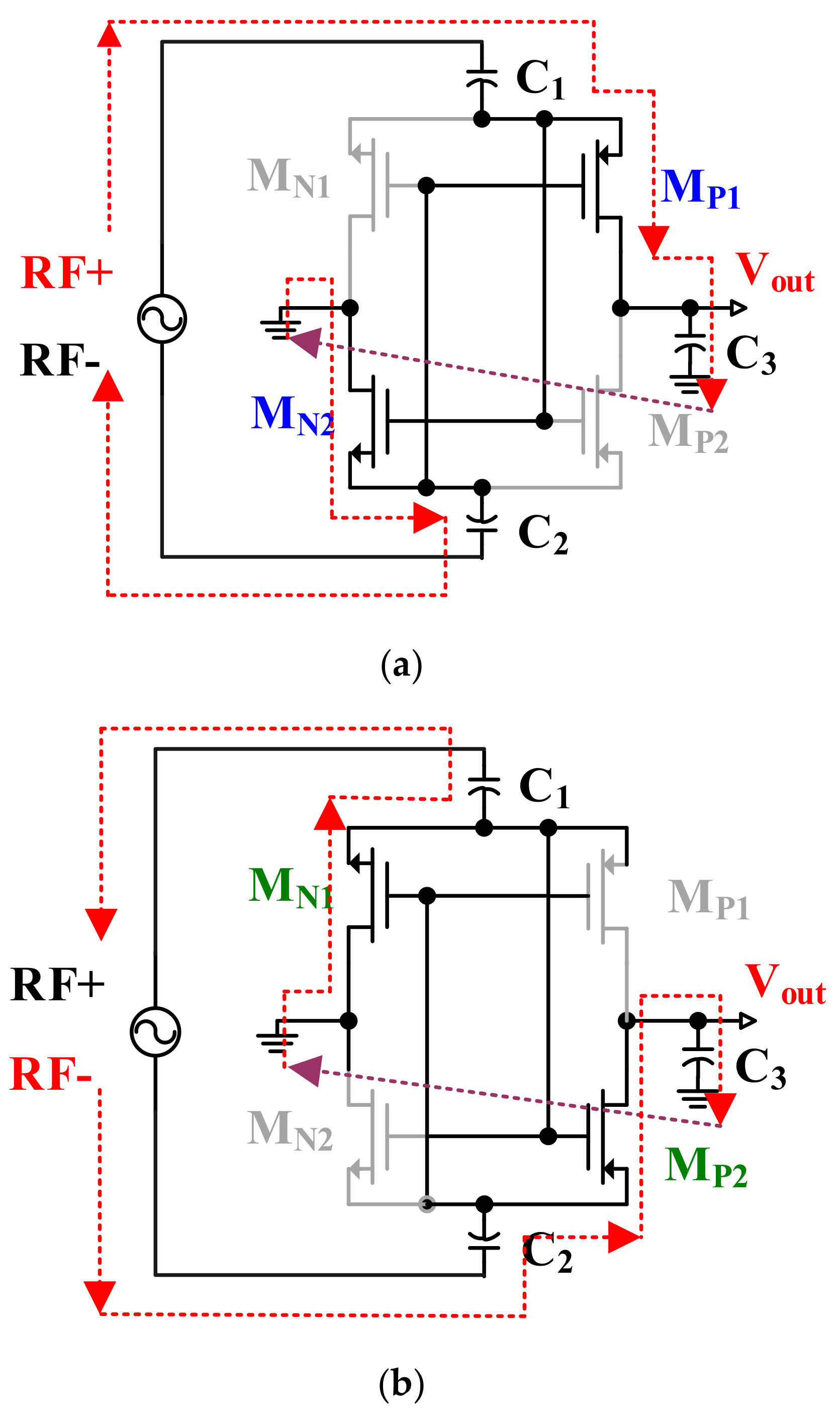

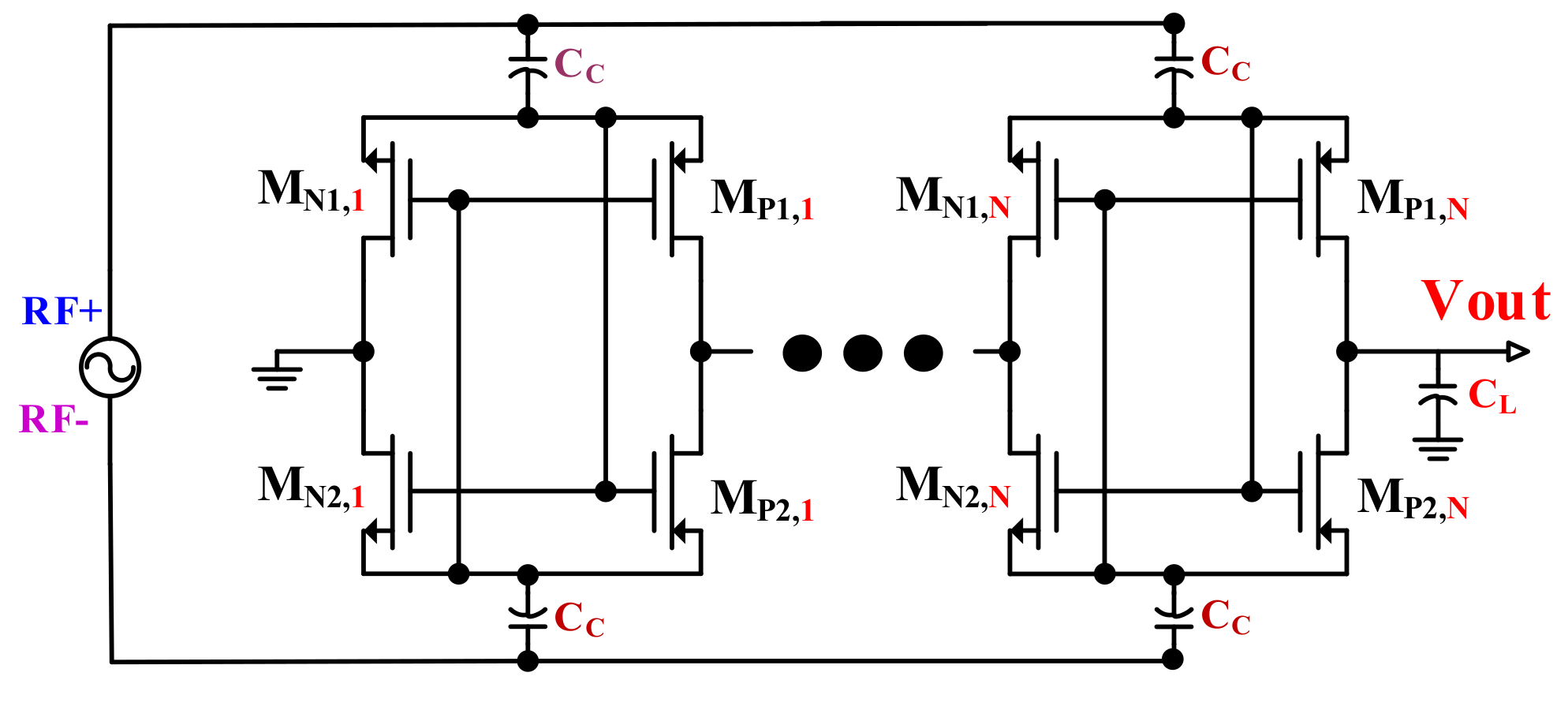

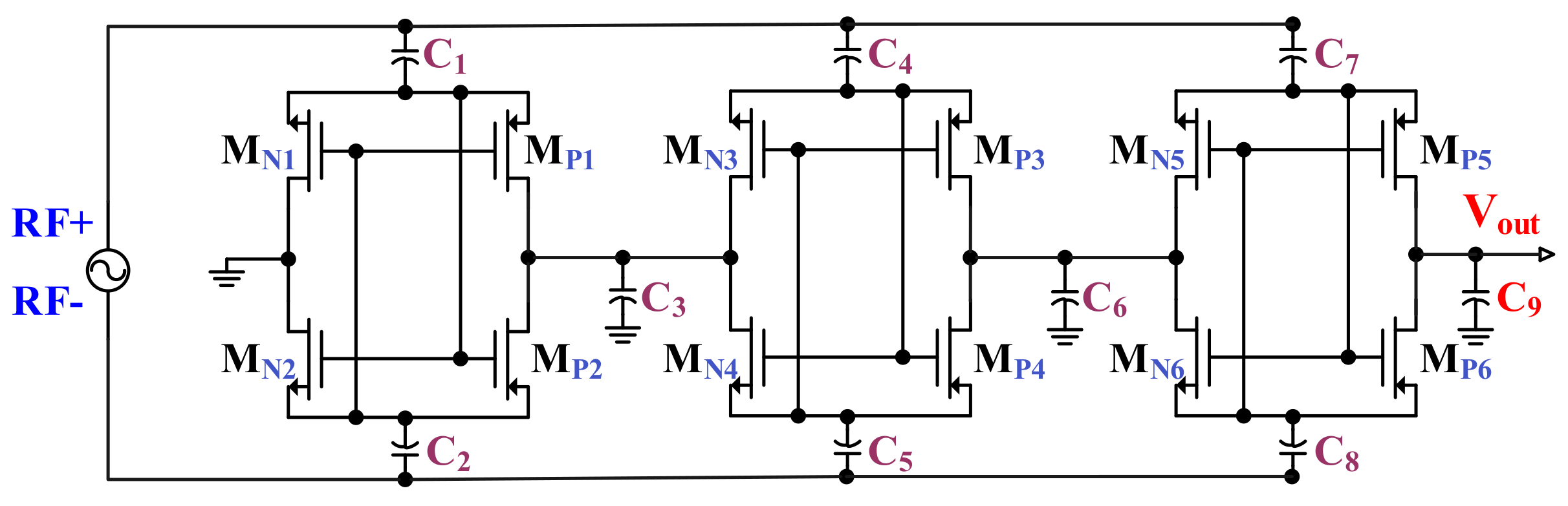

2.3. RF-DC Bridge Rectifier

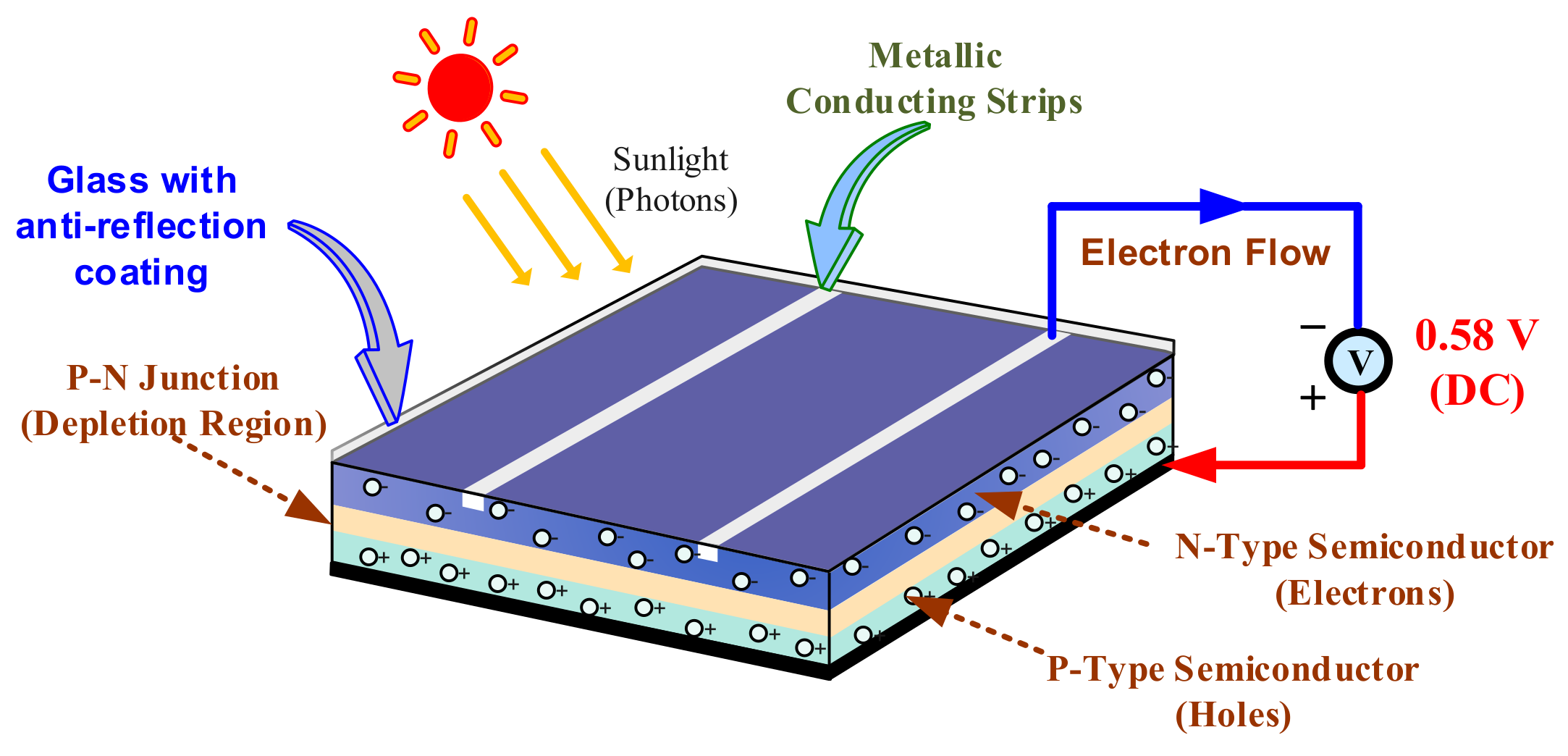

2.4. Solar Energy (PV Cell)

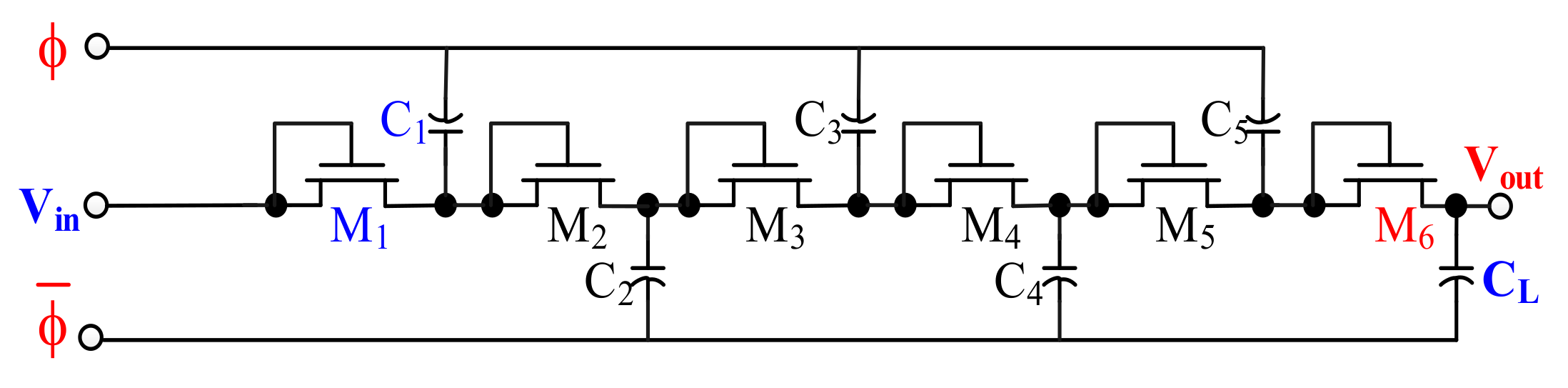

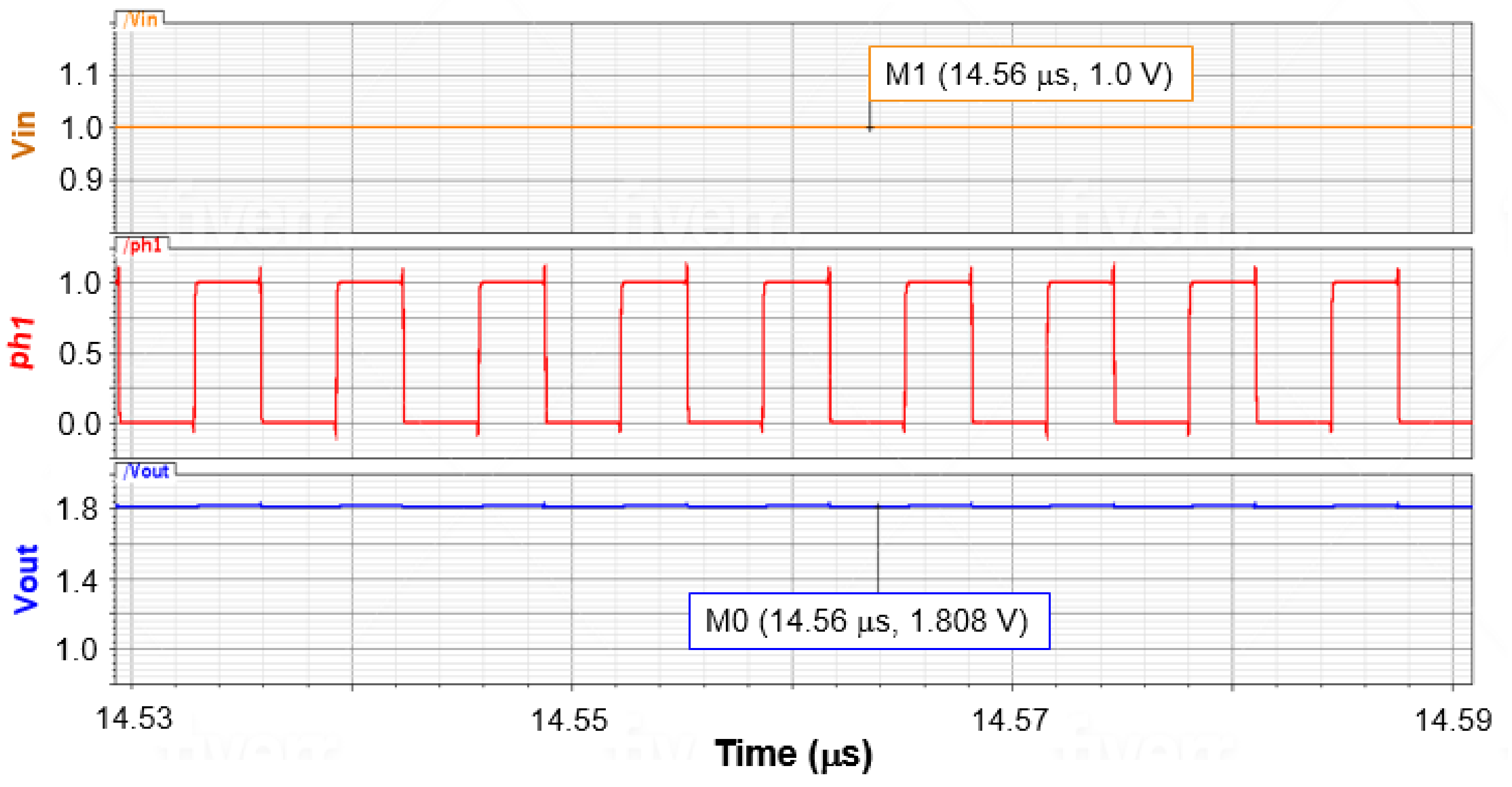

2.5. Dickson Charge Pump

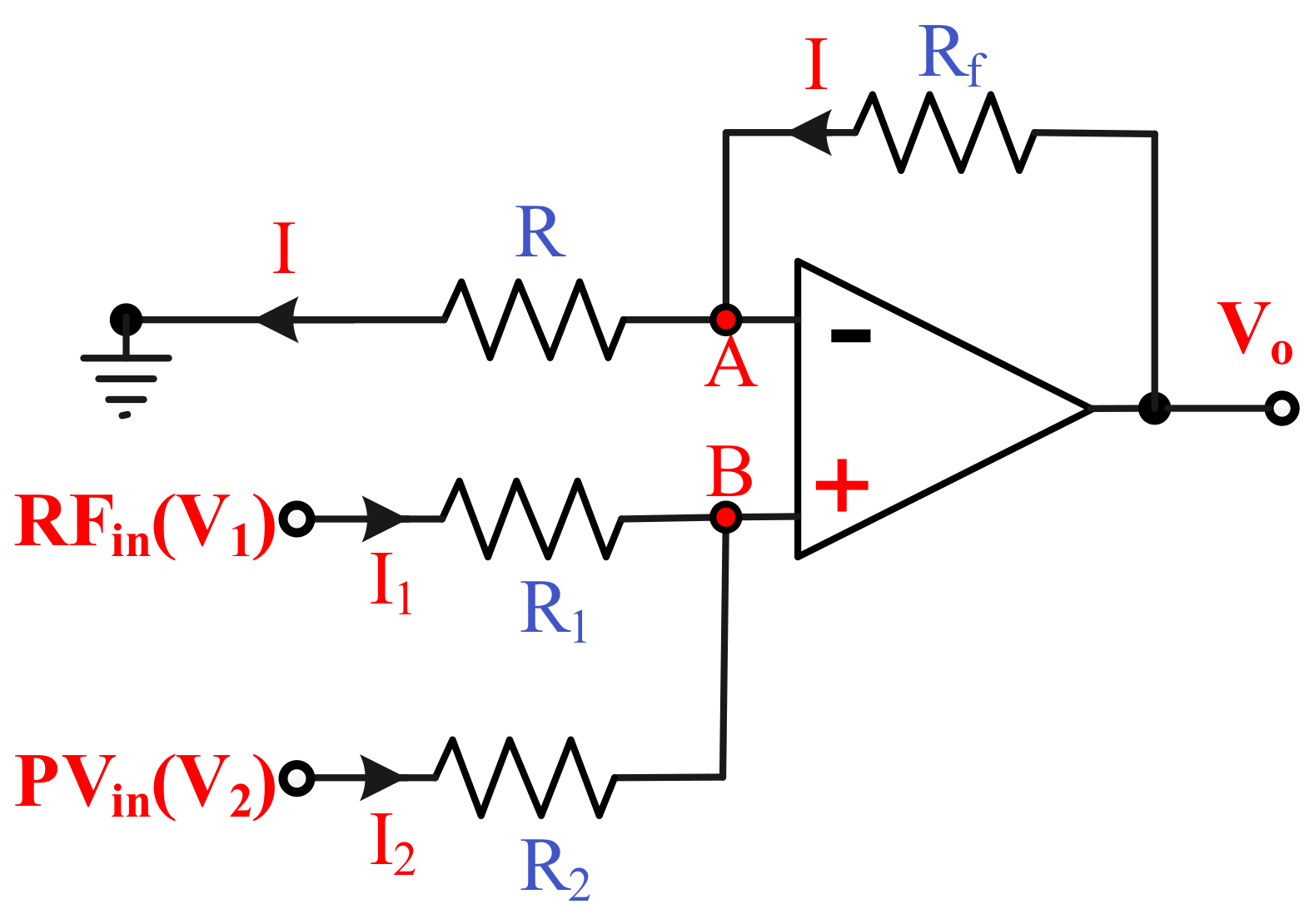

2.6. DC Voltage Combiner

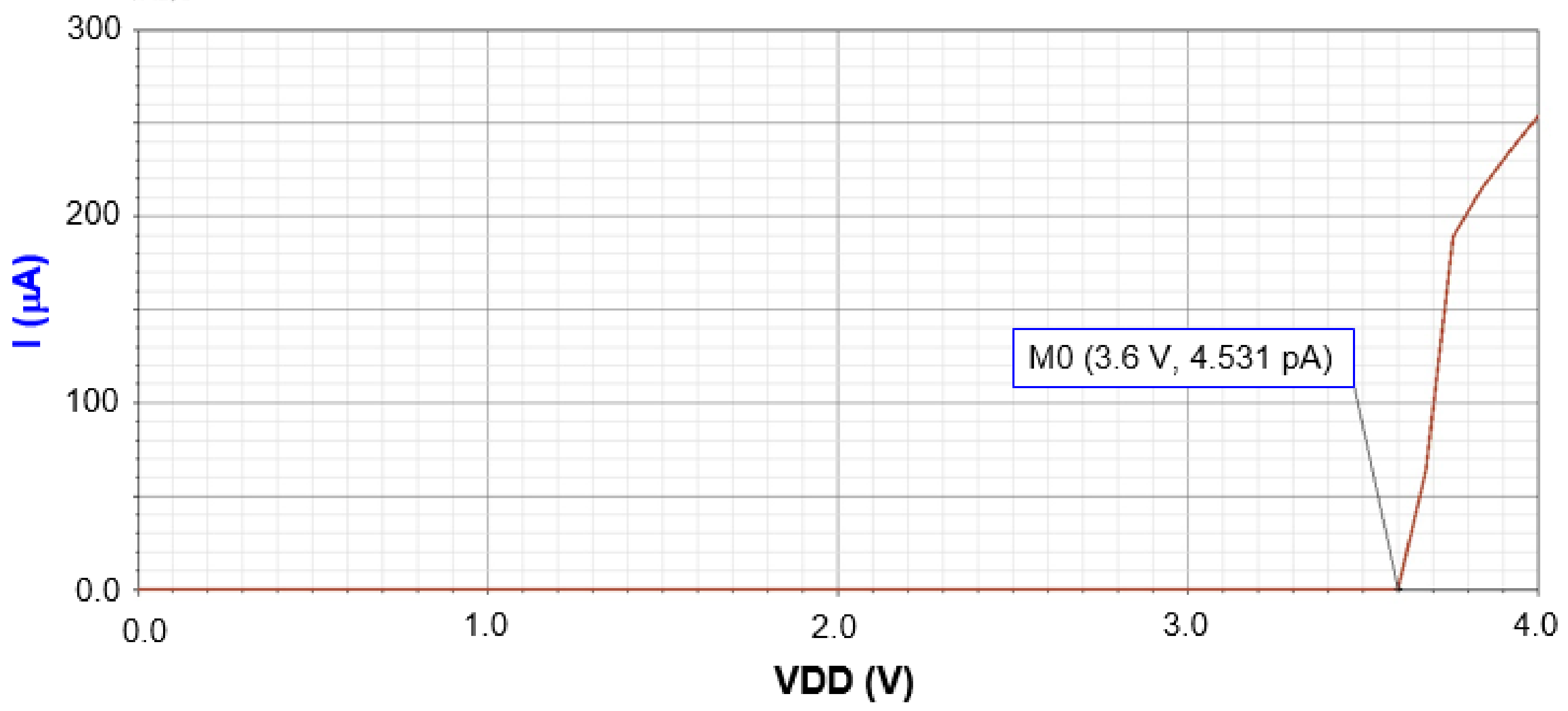

2.7. Overvoltage Protection (OVP) Circuit

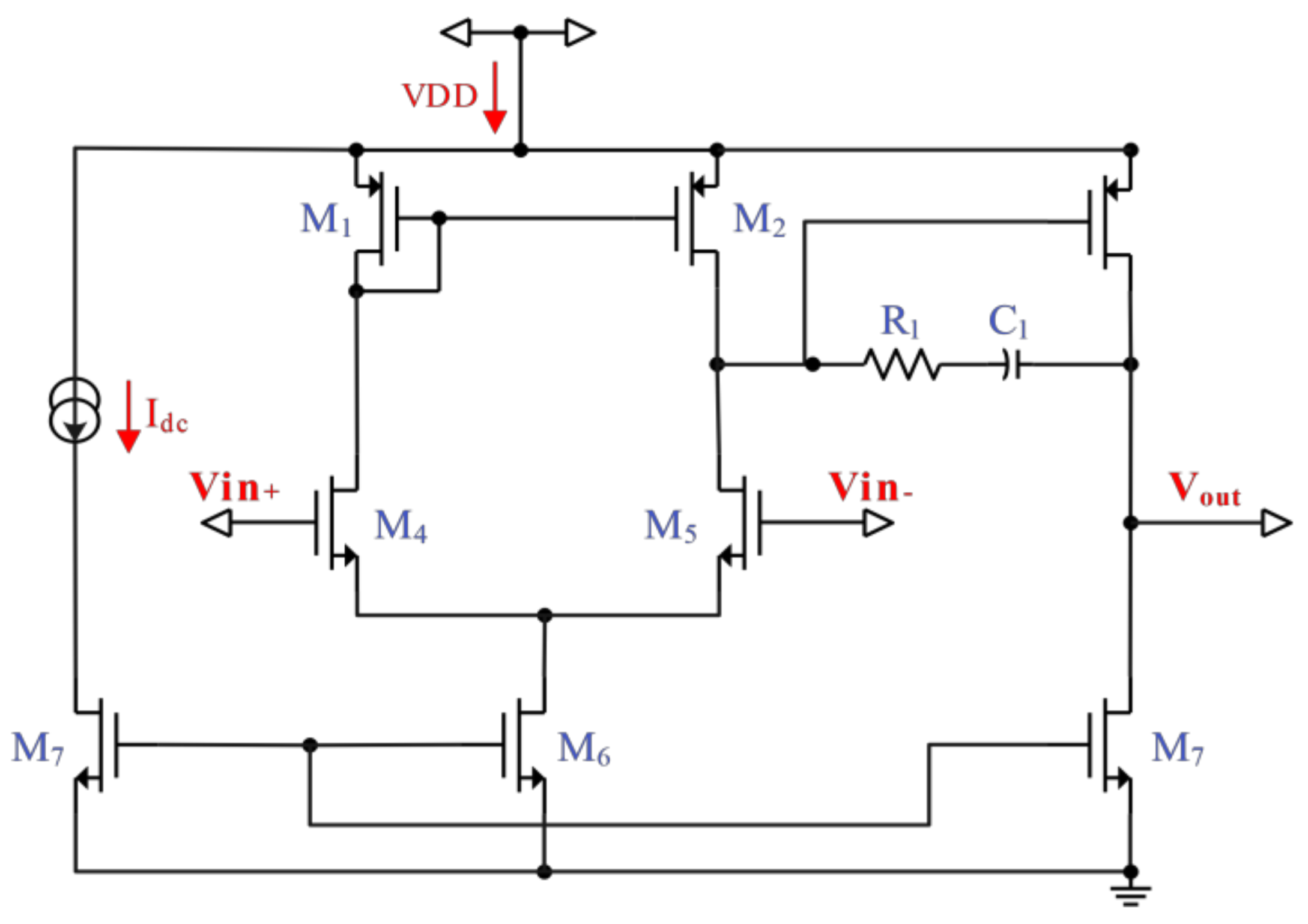

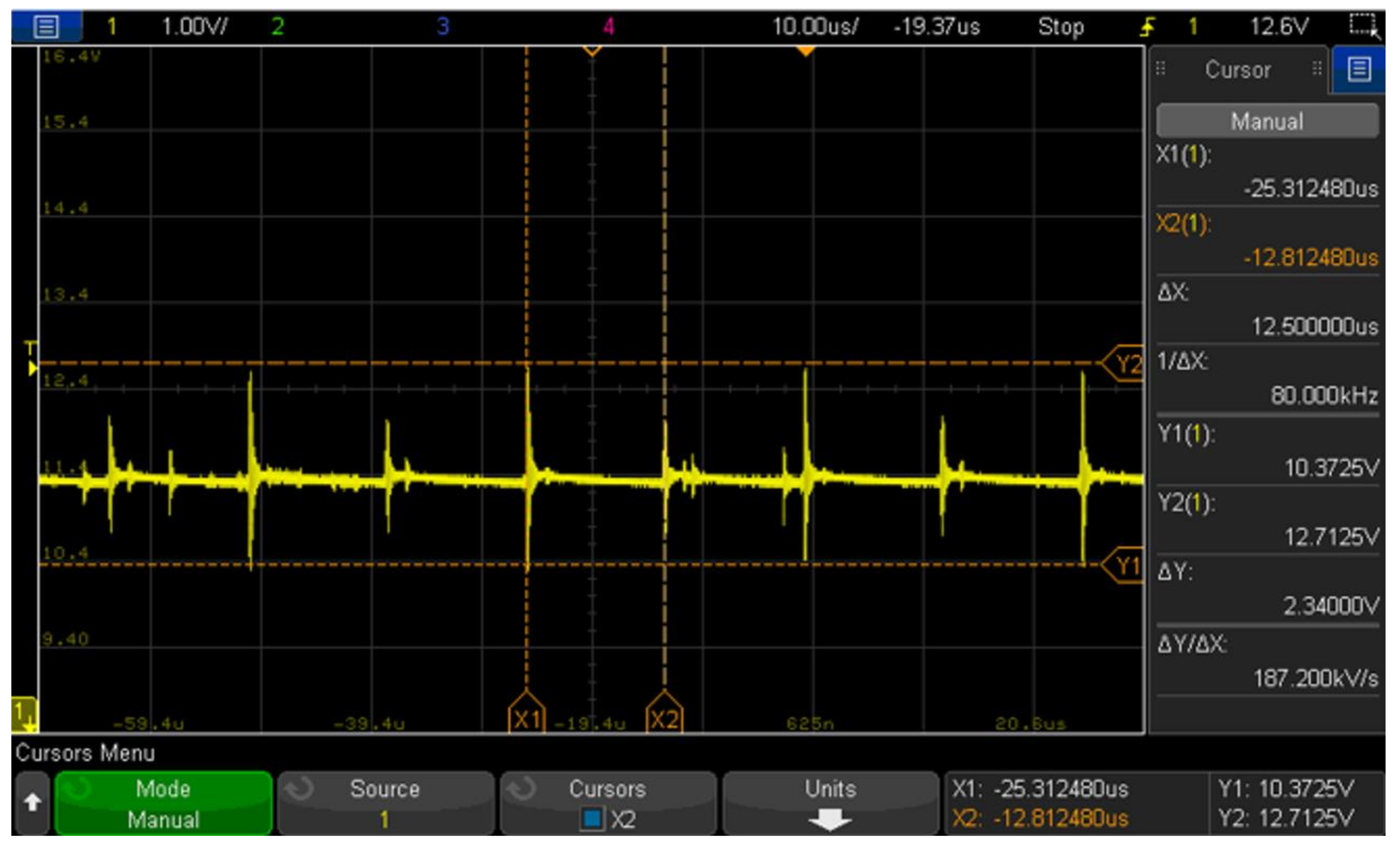

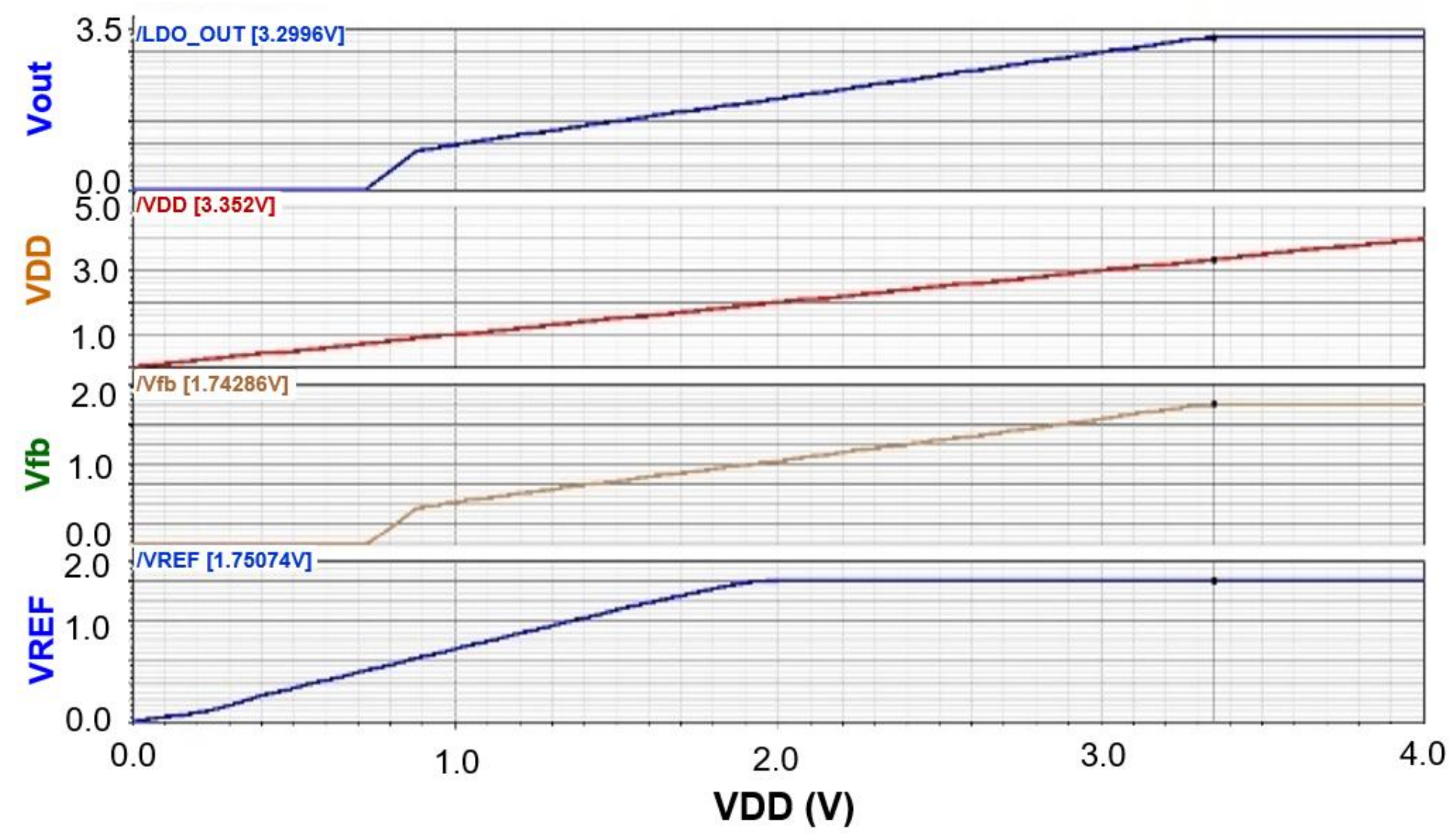

2.8. Low-Dropout Linear Voltage Regulator

3. Simulation Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Shafique, M.T.; Kamran, H.; Arshad, H.; Khattak, H.A. Home energy monitoring system using wireless sensor network. In Proceedings of the 14th International Conference Emerging Technologies (ICET), Islamabad, Pakistan, 21–22 November 2018; pp. 1–6. [Google Scholar]

- Xu, P.; Flandre, D.; Bol, D. Analysis, modeling, and design of a 2.45-GHz RF energy harvester for SWIPT IoT smart sensors. IEEE J. Solid-State Circuits 2019, 54, 2717–2729. [Google Scholar] [CrossRef]

- Chen, P.Y.; Chen, B.Y.; Chang, C.H.; Cheng, J.Y.; Chen, S.S.; Yang, M.M.; Hu, W.W. An RF-DC converter IC for power charging application. In Proceedings of the International Conference Engineering Technologies and Applications (IET-ICETA), Changhua, Taiwan, 14–16 October 2022; pp. 1–2. [Google Scholar]

- Sung, G.M.; Chou, H.Y.; Chen, Z.W. Radio frequency energy harvesting IC for ISM-915 MHz and 2.45 GHz wireless transmitter. In Proceedings of the IEEE International Future Energy Electronics Conference (IFEEC), Taipei, Taiwan, 16–19 November 2021; pp. 1–5. [Google Scholar]

- Lin, S.H.; Kuo, C.Y.; Lu, S.Y.; Liao, Y.T. A high-efficiency power management IC with power-aware multi-path rectifier for wide-range RF energy harvesting. In Proceedings of the IEEE MTT-S International Microwave Symposium (IMS), Honololu, HI, USA, 4–9 June 2017; pp. 303–306. [Google Scholar]

- Seong, D.; Jang, K.; Hwang, W.; Jeon, H.; Choi, J. Radio-frequency energy-harvesting IC with DC-DC converter. In Proceedings of the International SoC Design Conference (ISOCC), Jeju, Republic of Korea, 23–26 October 2016; pp. 339–340. [Google Scholar]

- Adami, S.E.; Vollaire, C.; Allard, B.; Costa, F.; Haboubi, W.; Cirio, L. Ultra-low power autonomous power management system with effective impedance matching for RF energy harvesting. In Proceedings of the 8th International Conference on Integrated Power Electronics Systems, Nuremberg, Germany, 25–27 February 2014; pp. 1–6. [Google Scholar]

- Chang, C.L.; Lee, T.C. An thermoelectric and RF multi-source energy harvesting system. In Proceedings of the 2nd International Conference on Intelligent Green Building and Smart Grid, Prague, Czech Republic, 27–29 June 2016; pp. 1–5. [Google Scholar]

- Saini, G.; Somappa, L.; Baghini, M.S. A 500-nW-to-1-mW input power inductive boost converter with MPPT for RF energy harvesting system. IEEE J. Emerg. Sel. Top. Power Electron. 2021, 9, 5261–5271. [Google Scholar] [CrossRef]

- Atsushi, S.; Koji, K.; Takashi, I. Differential-drive CMOS rectifier for UHF RFIDs with 66% PCE at −12 dBm input. In Proceedings of the IEEE Asian Solid-State Circuits Conference (ASSCC), Fukuoka, Japan, 3–5 November 2008; pp. 105–108. [Google Scholar]

- Hamza, M.; Rehman, M.U.; Riaz, A.; Maqsood, Z.; Khan, W.T. Hybrid dual band radio frequency and solar energy harvesting system for making battery-less sensing nodes. In Proceedings of the IEEE Radio and Wireless Symposium (RWS), San Diego, CA, USA, 17–22 January 2021; pp. 116–118. [Google Scholar]

- Jadhav, S.B.; Lambor, S.M. Hybrid solar and radio frequency (RF) energy harvesting. In Proceedings of the IEEE International Conference Power, Control, Signals and Instrumentation Engineering (ICPCSI), Chennai, India, 21–22 September 2017; pp. 1975–1980. [Google Scholar]

- Farooq, A.; Gray, M.; Bao, X.; Wu, X. Hybrid RF-solar energy harvesting for IoT. In Proceedings of the 34th Irish Signals and Systems Conference (ISSC), Dublin, Ireland, 13–14 June 2023; pp. 1–5. [Google Scholar]

- Yu, B.Y.; Wang, Z.H.; Ju, L.; Zhang, C.; Liu, Z.G.; Tao, L.; Lu, W.B. Flexible and wearable hybrid RF and solar energy harvesting system. IEEE Trans. Antennas Propag. 2022, 70, 2223–2233. [Google Scholar] [CrossRef]

- Shi, Y.; Nan, Y.H. Hybrid power harvesting from ambient radiofrequency and solar energy. IEEE Antennas Wirel. Propag. Lett. 2022, 21, 2382–2386. [Google Scholar] [CrossRef]

- Williams, J.M.; Gao, F.; Qian, Y.; Song, C.; Khanna, R.; Liu, H. Solar and RF energy harvesting design model for sustainable wireless sensor tags. In Proceedings of the IEEE Topical Conference Wireless Sensors and Sensor Networks (WiSNeT), San Antonio, TX, USA, 26–29 January 2020; pp. 1–4. [Google Scholar]

- Sung, G.M.; Chung, C.K.; Lai, Y.J.; Syu, J.Y. Small-area radiofrequency energy harvesting integrated circuits for powering wireless sensor networks. Sensors 2019, 19, 1754. [Google Scholar] [CrossRef] [PubMed]

- Hashemi, S.; Sawan, M.; Savaria, Y. A novel low-drop CMOS active rectifier for RF-powered devices: Experimental result. Microelectron. J. 2009, 40, 1547–1554. [Google Scholar] [CrossRef]

- Umeda, T.; Yoshida, H.; Sekine, S.; Fujita, Y.; Suzuki, T.; Otaka, S. A 950-MHz rectifier circuit for sensor network tags with 10-m distance. IEEE J. Solid-State Circuit 2006, 41, 35–41. [Google Scholar] [CrossRef]

- Nakamoto, H.; Yamazaki, D.; Yamanmoto, T.; Kurata, H.; Yamada, S.; Miksida, K.; Ninomiya, T.; Ohkawa, T.; Masui, S.; Gotoh, K. A passive RFID RF identification CMOS tag IC using ferroelectric RAM in 0.35-μm technology. IEEE J. Solid-State Circuit 2007, 42, 101–110. [Google Scholar] [CrossRef]

- Koji, K.; Ito, T. High-efficiency CMOS rectifier circuit with self-Vth-cancellation and power regulator functions for UHF RFIDs. In Proceedings of the IEEE Asian Solid-State Circuits Conference, Jeju, Republic of Korea, 12–14 November 2007; pp. 119–122. [Google Scholar]

- Yi, J.; Ki, W.H.; Tsui, C.Y. Analysis and design strategy of UHF micro-power CMOS rectifiers for micro-sensor and RFID applications. IEEE Trans. Circuits Syst. I Regul. Pap. 2007, 54, 153–166. [Google Scholar] [CrossRef]

- Boyle, G. Renewable Energy: Power for a Sustainable Future, 2nd ed.; Oxford University Press: Oxford, UK, 2004. [Google Scholar]

- Javier, C.; Pindado, S.; Manuel, C.D. Explicit expressions for solar panel equivalent circuit parameters based on analytical formulation and the Lambert W-function. Energies 2014, 7, 4098–4115. [Google Scholar] [CrossRef]

- Ambrosio, R.; Alba, R.T.; Guerrero-C, J.F.; Gonzalez, V.; Limon, A.; Moreno, M. Energy harvesting combining three different sources for low power applications. In Proceedings of the International Conference on Electrical Engineering, Computing Science and Automatic Control (CCE), Mexico City, Mexico, 28–30 October 2015; pp. 1–6. [Google Scholar]

- Johns, D.; Martin, K. Analog Integrated Circuit Design; John Wiley & Sons, Inc.: New York, NY, USA, 1997. [Google Scholar]

- Sun, M.; Ranasinghe, D.; Said, F.; Al-Sarawi, S.F. RF energy harvester with peak power conversion efficiency tracking. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), Jeju, Republic of Korea, 25–28 October 2016; pp. 107–110. [Google Scholar]

- Lai, W.C.; Jang, S.L.; Huang, C.Y.; Juang, M.H. Fully-integrated CMOS DC-DC boost converter. In Proceedings of the IEEE Asia Power and Energy Engineering Conference (APEEC), Chengdu, China, 29–31 March 2019; pp. 84–88. [Google Scholar]

- Chong, G.; Ramiah, H.; Yin, J.; Rajendran, L.; Wong, W.R.; Mark, P.I.; Martins, R.P. CMOS cross-coupled differential-drive rectifier in subthreshold operation for ambient RF energy harvesting-model and analysis. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 1942–1946. [Google Scholar] [CrossRef]

- Hegde, C.; Moham, A.; Mondal, S.; Paily, R.P. A wide dynamic range differential drive CMOS rectifier for μwatts RF energy harvesting systems. In Proceedings of the 38th International Conference on VLSI Design and 23rd International Conference on Embedded Systems (VLSID), Bangalore, India, 4–8 January 2025; pp. 175–179. [Google Scholar]

- Diangco, M.M.C.; Gerasta, O.J.L. Multiple-input energy harvesting DC adder combiner for Internet of Things (IoT) wireless sensor nodes (WSN) applications in 65nm CMOS technology. In Proceedings of the IEEE 11th International Conference on Humanoid, Nanotechnology, Information Technology, Communication and Control, Environment, and Management (HNICEM), Laoag, Philippines, 29 November–1 December 2019; pp. 1–6. [Google Scholar]

- Acut, R.V.P.; Hora, J.A.; Gerasta, O.J.L.; Zhu, X.; Dutkiewicz, E. PV-TEG-WiFi multiple sources design energy harvesting system for WSN application. In Proceedings of the IEEE International Circuits and Systems Symposium (ICSyS), Kuantan, Malaysia, 18–19 September 2019; pp. 1–5. [Google Scholar]

- Laganà, F.; Bibbò, L.; Calcagno, S.; Carlo, D.D.; Pullano, S.A.; Pratticò, D.; Angiulli, G. Smart electronic device-based monitoring of SAR and temperature variations in indoor human tissue interaction. Appl. Sci. 2025, 15, 2439. [Google Scholar] [CrossRef]

| Reference (Year) | [28] (2019) | [29] (2019) | [30] (2025) | [31] (2019) | [32] (2021) | This Work |

|---|---|---|---|---|---|---|

| Technology | 180 nm | 180 nm | 65 nm | 65 nm | 65 nm | 180 nm |

| Harvesting sources | RF | RF | RF | PV + RF + TEG | PV + TEG + WiFi | RF + Solar |

| RF frequency (MHz) | 2300 | 900 | 953 | - | 2400 | 915 |

| Input power range (dBm) | −20~+15 | −20~+0 | −25~0 | - | 0.5 V | −5~+20 |

| Rectifier topology | 2-stage CCR | 3-, 4-, and 7-stage CCDDR | Fully self-biased | 2-stage CCCP | CCCP | 3-stage CCDDR |

| Peak PCE (rectifier) | 7.6% | 42.3% | 60.5% | 41.9% (RF) 76.1% (DC Adder) | 69.0% (Combiner) | 41.6% (RF) 78% (Solar) |

| RF output voltage (V) | 0.6/1.7 | 1.3 | 1.4 | 0.5 | 0.92 | 1.8 |

| Solar output voltage (V) | - | - | - | 0.5 | 6.30 | 1.8 |

| Hybrid harvester (V) | - | - | - | 1.0 | - | 3.2996 |

| Chip area (mm2) | 1.109 | - | - | 0.086 | - | 0.050625 |

| Remarks | Poor | Average | Good | Good | Excellent | Good |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Sung, G.-M.; Chen, S.-H.; Choppa, V.; Yu, C.-P. Hybrid Radio-Frequency-Energy- and Solar-Energy-Harvesting-Integrated Circuit for Internet of Things and Low-Power Applications. Electronics 2025, 14, 2192. https://doi.org/10.3390/electronics14112192

Sung G-M, Chen S-H, Choppa V, Yu C-P. Hybrid Radio-Frequency-Energy- and Solar-Energy-Harvesting-Integrated Circuit for Internet of Things and Low-Power Applications. Electronics. 2025; 14(11):2192. https://doi.org/10.3390/electronics14112192

Chicago/Turabian StyleSung, Guo-Ming, Shih-Hao Chen, Venkatesh Choppa, and Chih-Ping Yu. 2025. "Hybrid Radio-Frequency-Energy- and Solar-Energy-Harvesting-Integrated Circuit for Internet of Things and Low-Power Applications" Electronics 14, no. 11: 2192. https://doi.org/10.3390/electronics14112192

APA StyleSung, G.-M., Chen, S.-H., Choppa, V., & Yu, C.-P. (2025). Hybrid Radio-Frequency-Energy- and Solar-Energy-Harvesting-Integrated Circuit for Internet of Things and Low-Power Applications. Electronics, 14(11), 2192. https://doi.org/10.3390/electronics14112192