Die-Level Thinning for Flip-Chip Integration on Flexible Substrates

Abstract

:1. Introduction

1.1. Flexible CMOS Sensors with Die-Level Post-Processing

1.2. Flip chip Integration of the Thinned Chips

2. Materials and Methods

2.1. Die-Level Thinning

Bumping-Thinning Sequence

2.2. Chip on Board Integration via Wire Bonding

2.3. Flip-Chip Integration

2.3.1. Thermosonic Bonding

2.3.2. ACP Bonding

3. Results and Discussion

3.1. Silicon IDE-Sensors

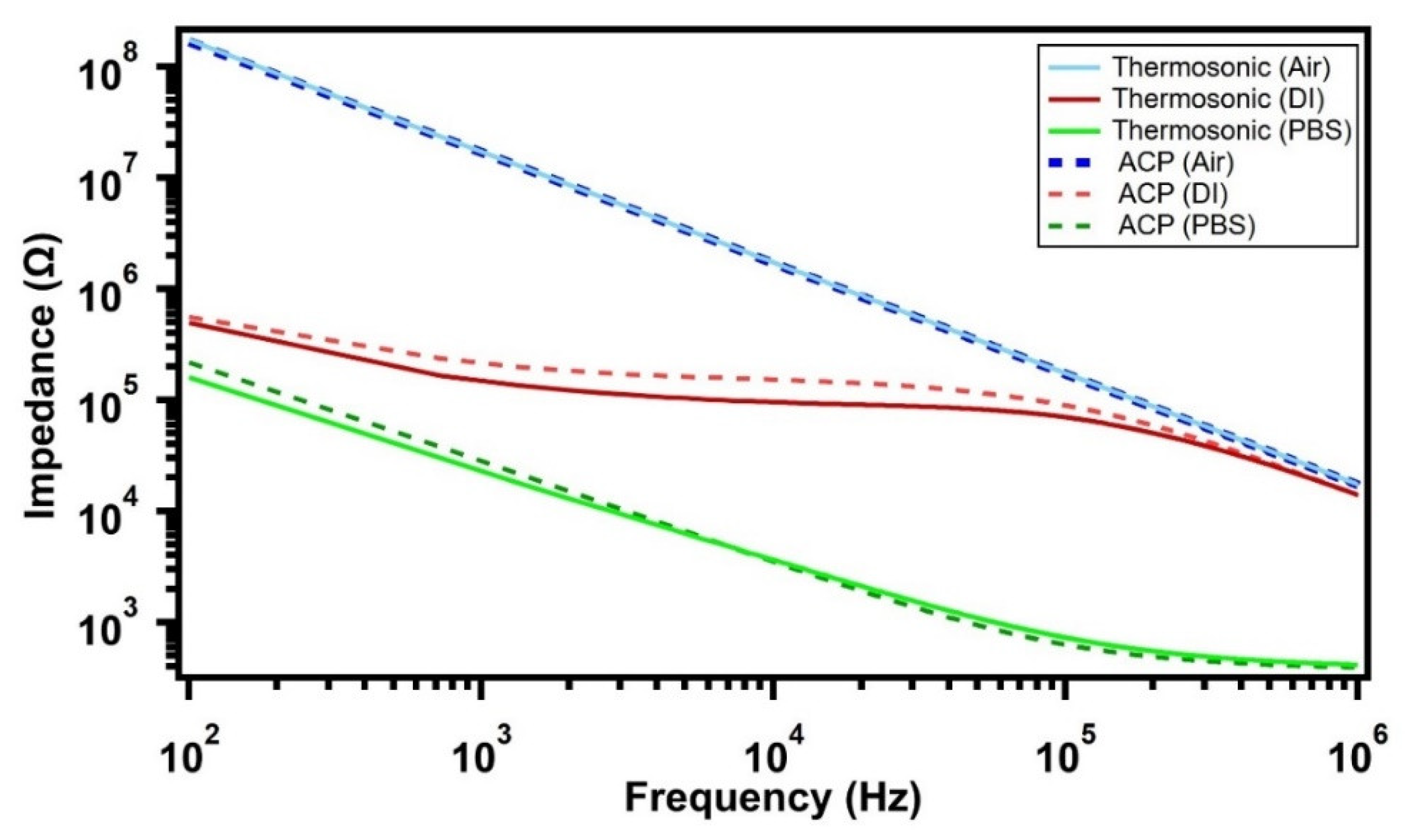

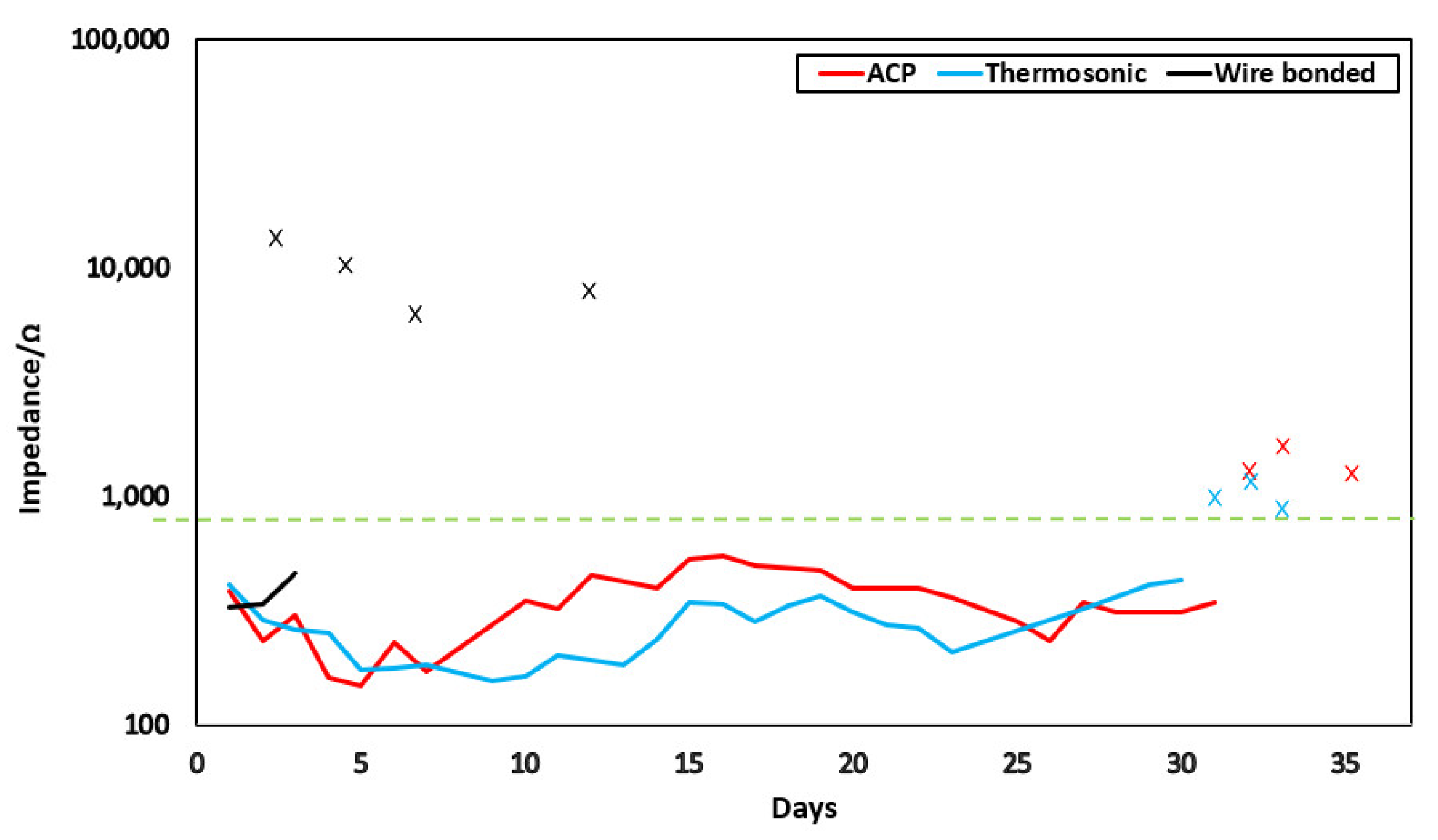

3.2. Impedance Analysis

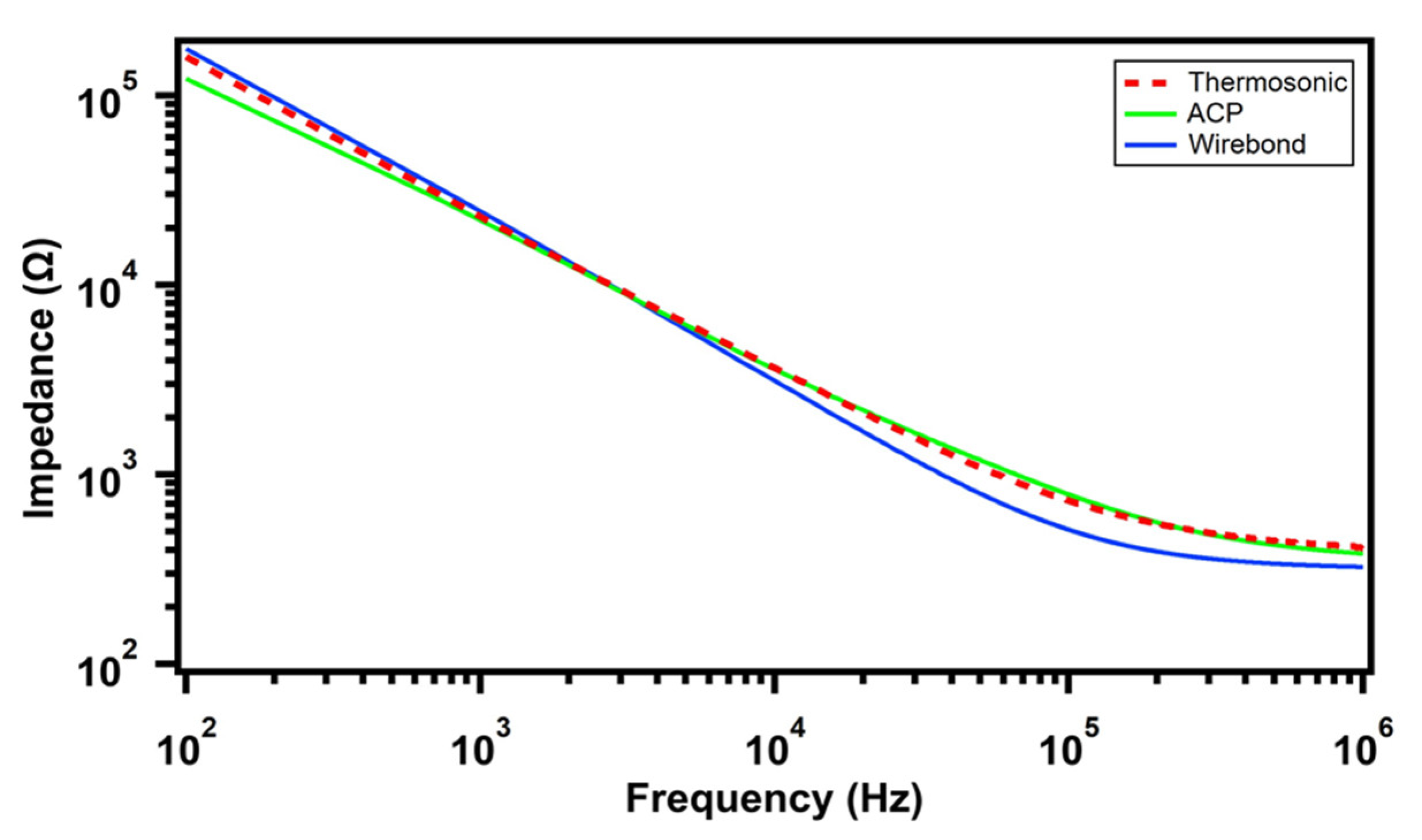

3.3. Comparison to the Wire-Bonded Sensors

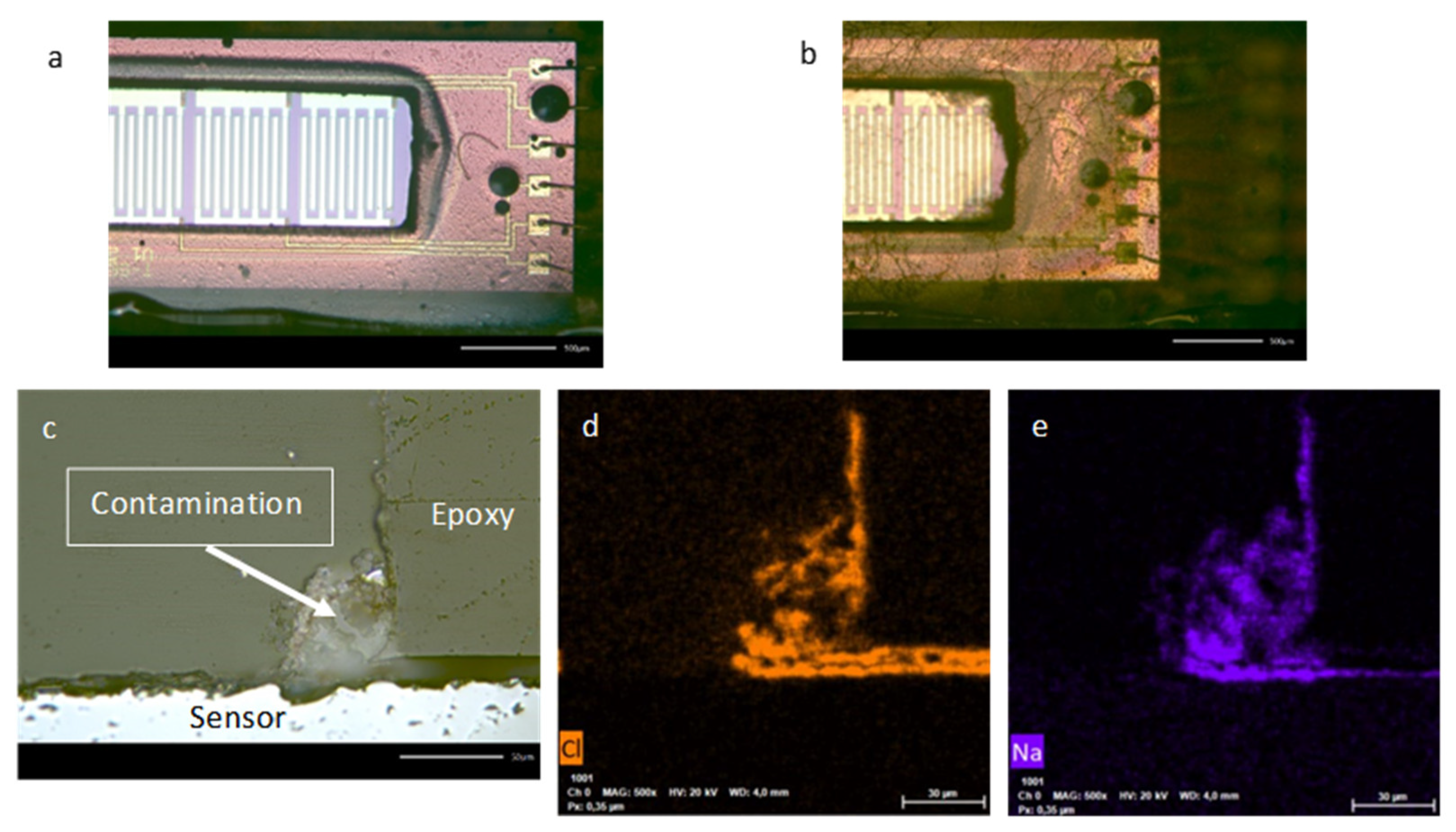

3.4. CMOS Chips

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Rodrigues, D.; Barbosa, A.I.; Rebelo, R.; Kwon, I.K.; Reis, R.L.; Correlo, V.M. Skin-Integrated Wearable Systems and Implantable Biosensors: A Comprehensive Review. Biosensors 2020, 10, 79. [Google Scholar] [CrossRef]

- Dinis, H.; Mendes, P.M. Recent Advances on Implantable Wireless Sensor Networks. In Wireless Sensor Networks—Insights and Innovations; IntechOpen: London, UK, 2017. [Google Scholar]

- Perumal, V.; Hashim, U. Advances in biosensors: Principle, architecture and applications. J. Appl. Biomed. 2014, 12, 1–15. [Google Scholar] [CrossRef]

- Sekitani, T.; Zschieschang, U.; Klauk, H.; Someya, T. Flexible organic transistors and circuits with extreme bending stability. Nat. Mater. 2010, 9, 1015–1022. [Google Scholar] [CrossRef] [PubMed]

- Zulqarnain, M.; Stanzione, S.; Rathinavel, G.; Smout, S.; Willegems, M.; Myny, K.; Cantatore, E. A flexible ECG patch compatible with NFC RF communication. npj Flex. Electron. 2020, 4, 13. [Google Scholar] [CrossRef]

- Malik, M.H.; Grosso, G.; Zangl, H.; Binder, A.; Roshanghias, A. Flip Chip integration of ultra-thinned dies in low-cost flexible printed electronics; the effects of die thickness, encapsulation and conductive adhesives. Microelectron. Reliab. 2021, 123, 114204. [Google Scholar] [CrossRef]

- Hussain, M.M.; El-Atab, N. (Eds.) Handbook of Flexible and Stretchable Electronics; CRC Press: Boca Raton, FL, USA, 2019. [Google Scholar]

- Ma, S.; Kumaresan, Y.; Dahiya, A.S.; Dahiya, R. Ultra-Thin Chips with Printed Interconnects on Flexible Foils. Adv. Electron. Mater. 2021, 2021, 2101029. [Google Scholar] [CrossRef]

- Tsiamis, A.; Li, Y. Comparison of Conventional and Maskless Lithographic Techniques for More than Moore ost-processing of Foundry CMOS Chips. J. Microelectromech. Syst. 2021, 29, 1245–1252. [Google Scholar] [CrossRef]

- Wu, M.-C.; Lin, R.-B.; Tsai, S.-C. Chip placement in a reticle for multiple-project wafer fabrication. ACM Trans. Des. Autom. Electron. Syst. 2008, 13, 1–21. [Google Scholar] [CrossRef]

- Pina, C.A. MOSIS: IC prototyping and low volume production service. In Proceedings of the 2001 International Conference on Microelectronic Systems Education, Las Vegas, NV, USA, 17–18 June 2001; pp. 4–5. [Google Scholar]

- Giagka, V.; Saeidi, N.; Demosthenous, A.; Donaldson, N. Controlled silicon IC thinning on individual die level for active implant integration using a purely mechanical process. In Proceedings of the Electronic Components and Technology Conference, Orlando, FL, USA, 27–30 May 2014. [Google Scholar]

- Miller, L.F. Controlled Collapse Reflow Chip Joining. IBM J. Res. Dev. 1969, 13, 239–250. [Google Scholar] [CrossRef]

- Lau, J.H. Flip Chip Technologies; McGraw-Hill: New York, NY, USA, 1996. [Google Scholar]

- Harman, G.G. Wire Bonding in Microelectronics Materials, Processes, Reliability and Yield; McGraw-Hill: New York, NY, USA, 1997. [Google Scholar]

- Fretz, M. Flip Chip Bonding Technologies for Hybrid Integration. Ph.D. Thesis, Universität Neuenburg, Neuenburg, Germany, 2009. [Google Scholar]

- Roshanghias, A.; Rodrigues, A.; Schwarz, S.; Steiger-Thirsfeld, A. Thermosonic direct Cu pillar bonding for 3D die stacking. SN Appl. Sci. 2020, 2, 1091. [Google Scholar] [CrossRef]

- Pang, C.H.; Sham, M.L.; Hung, K.Y. Investigation. In Proceedings of the 5th Electronics Packaging Technology Conference (EPTC 2003), Singapore, 12 December 2003. [Google Scholar]

- Wang, F.-L.; Han, L. Ultrasonic Effects in the Thermosonic Flip Chip Bonding Process. IEEE Trans. Compon. Packag. Manuf. Technol. 2013, 3, 336–341. [Google Scholar] [CrossRef]

- Kang, S.Y.; Williams, P.M.; McLaren, T.S.; Lee, Y.C. Studies of thermosonic bonding for flip-chip assembly. Mater. Chem. Phys. 1995, 42, 31–37. [Google Scholar] [CrossRef]

- Luk, C.F.; Chan, Y.C.; Hung, K.C. Development of gold to gold interconnection flip chip bonding for chip on suspension assemblies. Microelectron. Reliab. 2002, 42, 381–389. [Google Scholar] [CrossRef]

- Nakano, K.; Fujimoto, N.; Tanaka, M.; Asai, A. Development of the Ultrasonic Flip Chip Bonding Technology for Yaw Rate Sensors. Denso Tech. Rev. 2016, 21, 150–155. [Google Scholar]

- McLaren, T.S.; Kang, S.Y.; Zhang, W.; Ju, T.-H.; Lee, Y.-C. Thermosonic bonding of an optical transceiver based on an 8/spl times/8 vertical cavity surface emitting laser array. IEEE Trans. Compon. Packag. Manuf. Technol. Part B 1997, 20, 152–160. [Google Scholar] [CrossRef]

- Liu, J.; Tolvgard, A.; Malmodin, J.; Lai, Z. A reliable and environmentally friendly packaging technology-flip-chip joining using anisotropically conductive adhesive. IEEE Trans. Compon. Packag. Technol. 1999, 22, 186–190. [Google Scholar] [CrossRef]

- Yoon, D.-J.; Malik, M.H.; Yan, P.; Paik, K.-W.; Roshanghias, A. ACF bonding technology for paper- and PET-based disposable flexible hybrid electronics. J. Mater. Sci. Mater. Electron. 2021, 32, 2283–2292. [Google Scholar] [CrossRef]

- Li, Y.G.; Lu, D.; Wong, C.P. Electrical Conductive Adhesives with Nanotechnologies, 1st ed.; Springer: New York, NY, USA, 2010. [Google Scholar]

- Lin, C.M.; Chen, D.C.; Liu, Y.C. Investigation on fracture and conductivity of flex-on-film flexible bonding using anisotropic conductive film considering repeated bending. Microsyst. Technol. 2018, 25, 3017–3025. [Google Scholar] [CrossRef]

- Nah, J.-W.; Paik, K.W.; Hwang, T.-K.; Kim, W.-H. A Study on Coining Processes of Solder Bumps on Organic Substrates. IEEE Trans. Electron. Packag. Manuf. 2003, 26, 166–172. [Google Scholar]

- Shirangi, M.H.; Michel, B. Mechanism of Moisture Diffusion, Hygroscopic Swelling, and Adhesion Degradation in Epoxy Molding Compounds. In Moisture Sensitivity of Plastic Packages of IC Devices; Springer: Boston, MA, USA, 2010; pp. 29–69. [Google Scholar]

- Ardebili, H.; Hillman, C.; Natishan, M.A.E.; McCluskey, P.; Peterson, D. A Comparison of the Theory of Moisture Diffusion in Plastic Encapsulated Microelectronics with Moisture Sensor Chip and Weight-Gain Measurements. IEEE Trans. Compon. Packag. Technol. 2002, 25, 132–139. [Google Scholar] [CrossRef] [Green Version]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Malik, M.H.; Tsiamis, A.; Zangl, H.; Binder, A.; Mitra, S.; Roshanghias, A. Die-Level Thinning for Flip-Chip Integration on Flexible Substrates. Electronics 2022, 11, 849. https://doi.org/10.3390/electronics11060849

Malik MH, Tsiamis A, Zangl H, Binder A, Mitra S, Roshanghias A. Die-Level Thinning for Flip-Chip Integration on Flexible Substrates. Electronics. 2022; 11(6):849. https://doi.org/10.3390/electronics11060849

Chicago/Turabian StyleMalik, Muhammad Hassan, Andreas Tsiamis, Hubert Zangl, Alfred Binder, Srinjoy Mitra, and Ali Roshanghias. 2022. "Die-Level Thinning for Flip-Chip Integration on Flexible Substrates" Electronics 11, no. 6: 849. https://doi.org/10.3390/electronics11060849

APA StyleMalik, M. H., Tsiamis, A., Zangl, H., Binder, A., Mitra, S., & Roshanghias, A. (2022). Die-Level Thinning for Flip-Chip Integration on Flexible Substrates. Electronics, 11(6), 849. https://doi.org/10.3390/electronics11060849