Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics

Abstract

:1. Introduction

2. Materials and Methods

3. Result and Discussion

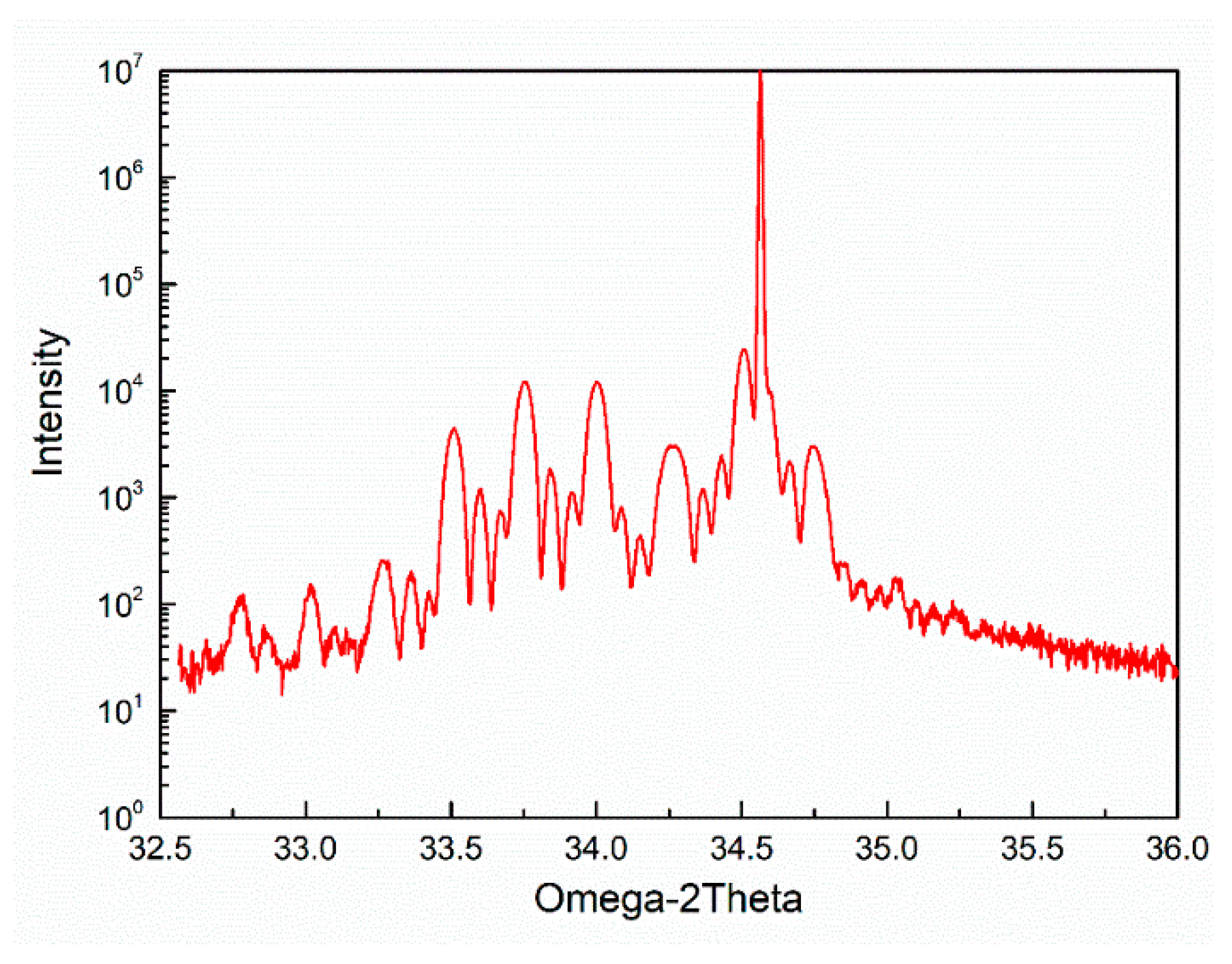

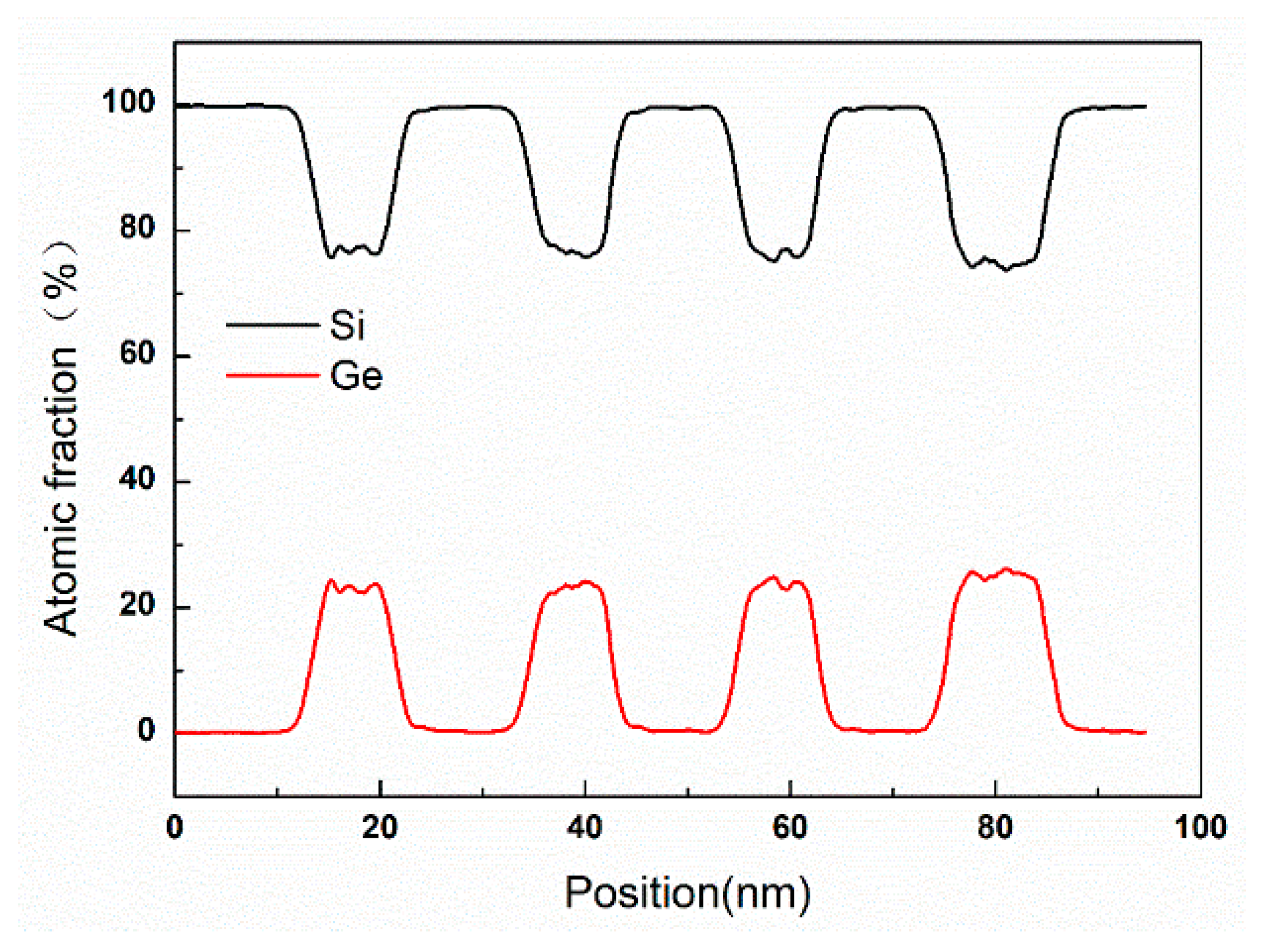

3.1. Epitaxial Growth of Stacked SiGe/Si Multilayer

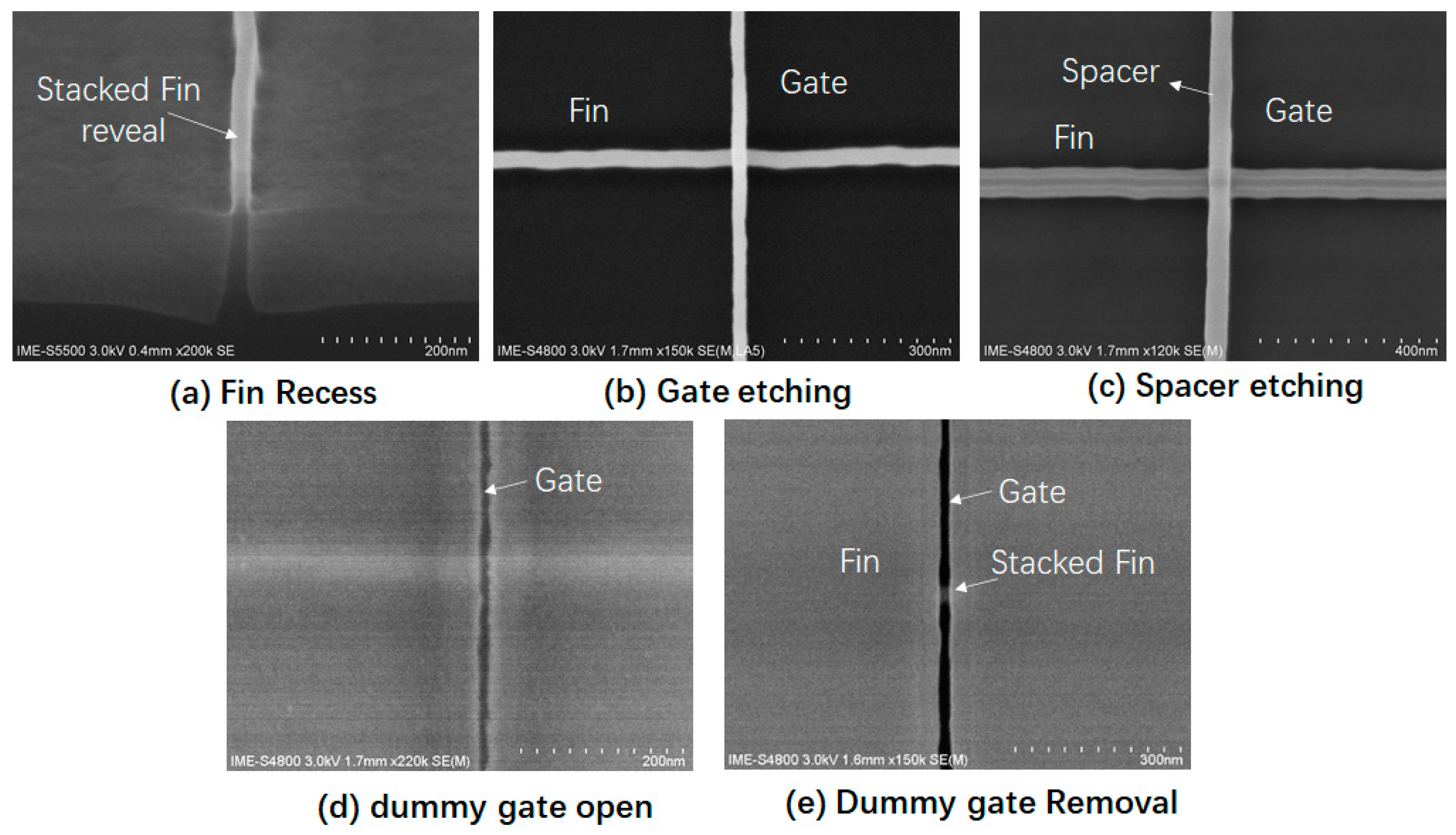

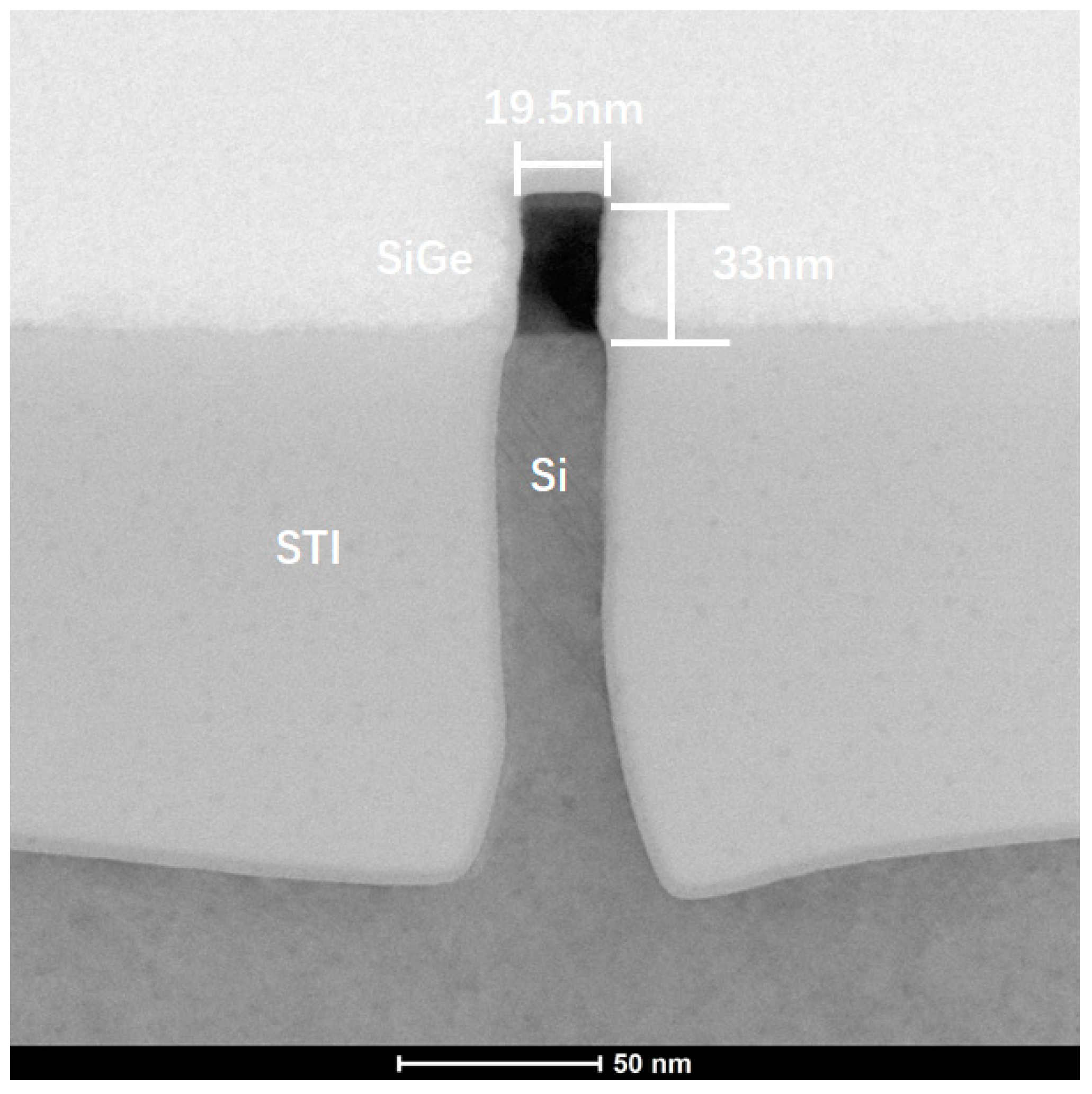

3.2. Stacked SiGe/Si Fin Etching

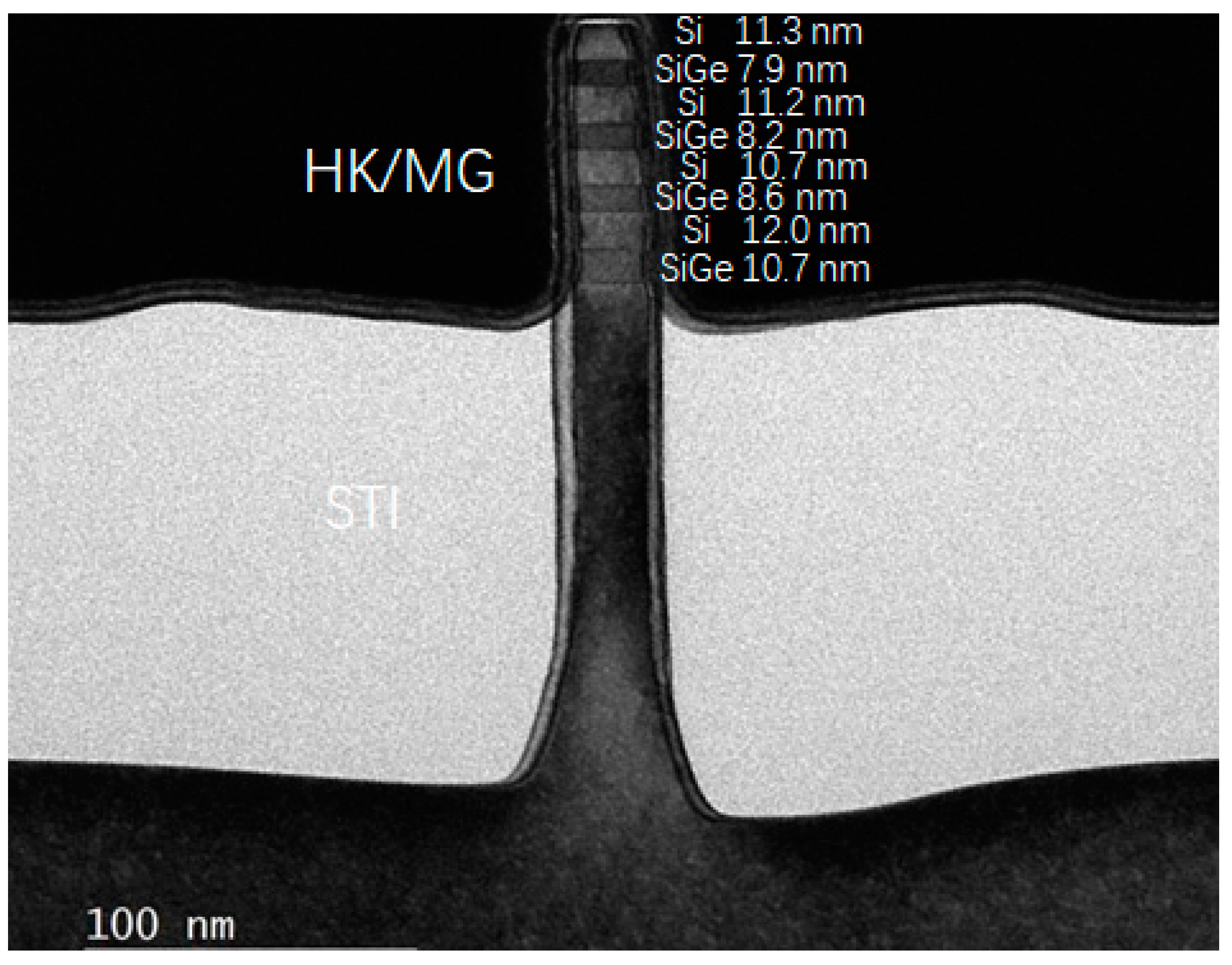

3.3. FinFET Device Fabrication

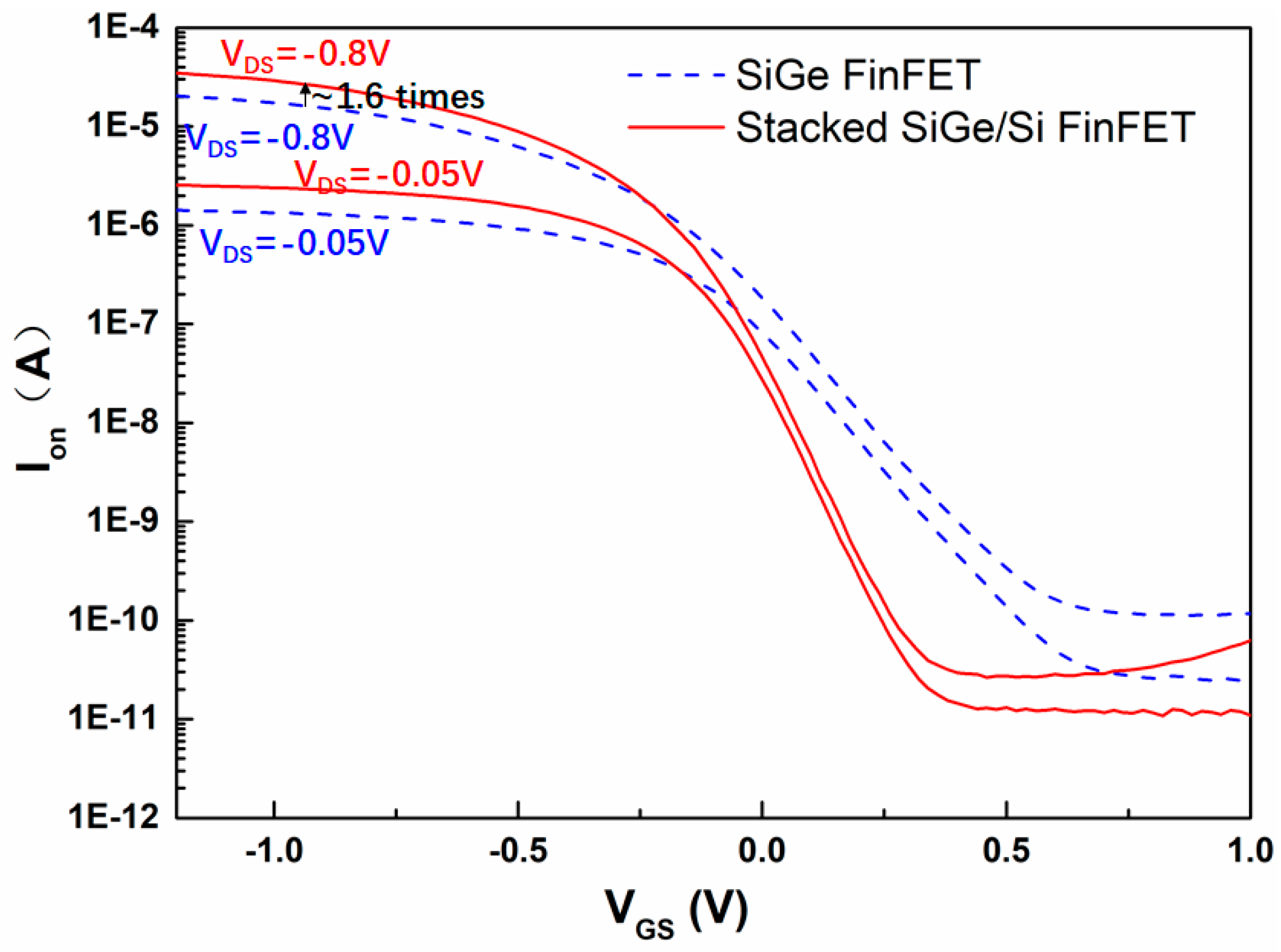

3.4. Electrical Performance

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Yeap, G.; Lin, S.S.; Chen, Y.M.; Shang, H.L.; Wang, P.W.; Lin, H.C.; Peng, Y.C.; Sheu, J.Y.; Wang, M.; Chen, X.; et al. 5 nm CMOS Production Technology Platform featuring full-fledged EUV, and High Mobility Channel FinFETs with densest 0.021 µm2 SRAM cells for Mobile SoC and High Performance Computing Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 36.7.1–36.7.4. [Google Scholar]

- Mertens, H.; Ritzenthaler, R.; Arimura, H.; Franco, J.; Sebaai, F.; Hikavyy, A.; Pawlak, B.; Machkaoutsan, V.; Devriendt, K.; Tsvetanova, D. Si-cap-free SiGe p-channel FinFETs and gate-all-around transistors in a replacement metal gate process: Interface trap density reduction and performance improvement by high-pressure deuterium anneal. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T142–T143. [Google Scholar]

- Witters, L.; Arimura, H.; Sebaai, F.; Hikavyy, A.; Milenin, A.P.; Loo, R.; De Keersgieter, A.; Eneman, G.; Schram, T.; Wostyn, K.; et al. Strained Germanium Gate-All-Around pMOS Device Demonstration Using Selective Wire Release Etch Prior to Replacement Metal Gate Deposition. IEEE Trans. Electron Devices 2017, 64, 4587–4593. [Google Scholar] [CrossRef]

- Franco, J.; Kaczer, B.; Roussel, P.J.; Mitard, J.; Cho, M.; Witters, L.; Grasser, T.; Groeseneken, G. SiGe Channel Technology: Superior Reliability Toward Ultrathin EOT Devices-Part I: NBTI. IEEE Trans. Electron Devices 2013, 60, 396–404. [Google Scholar] [CrossRef]

- Lee, C.H.; Southwick, R.G.; Mochizuki, S.; Li, J.; Miao, X.; Wang, M.; Bao, R.; Ok, I.; Ando, T.; Hashemi, P.; et al. Toward High Performance SiGe Channel CMOS: Design of High Electron Mobility in SiGe nFinFETs Outperforming Si. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 35.1.1–35.1.4. [Google Scholar]

- Zhao, Z.Q.; Li, Y.; Zan, Y.; Li, Y.L.; Li, J.J.; Cheng, X.H.; Wang, G.L.; Liu, H.Y.; Wang, H.X.; Zhang, Q.Z.; et al. Fabrication technique of the Si0.5Ge0.5 Fin for the high mobility channel FinFET device. Semicond. Sci. Technol. 2020, 35, 045015. [Google Scholar] [CrossRef]

- Zhao, Z.Q.; Li, Y.L.; Wang, G.L.; Du, A.Y.; Li, Y.; Zhang, Q.Z.; Xu, G.B.; Zhang, Y.K.; Luo, J.; Li, J.F.; et al. Process optimization of the Si0.7Ge0.3 Fin Formation for the STI first scheme. Semicond. Sci. Technol. 2019, 34, 125008. [Google Scholar] [CrossRef]

- Mochizuki, S.; Colombeau, B.; Zhang, J.; Kung, S.C.; Stolfi, M.; Zhou, H.; Breton, M.; Watanabe, K.; Li, J.; Jagannathan, H.; et al. Structural and Electrical Demonstration of SiGe Cladded Channel for PMOS Stacked Nanosheet Gate-All-Around Devices. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020; pp. 1–2. [Google Scholar]

- Paul, D.J. Si/SiGe heterostructures: From material and physics to devices and circuits. Semicond. Sci. Technol. 2004, 19, R75–R108. [Google Scholar] [CrossRef]

- Arimura, H.; Wostyn, K.; Ragnarsson, L.Å.; Capogreco, E.; Chasin, A.; Conard, T.; Brus, S.; Favia, P.; Franco, J.; Mitard, J.; et al. Ge oxide scavenging and gate stack nitridation for strained Si0.7Ge0.3 pFinFETs enabling 35% higher mobility than Si. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 29.2.1–29.2.4. [Google Scholar]

- Jungwoo, O.; Majhi, P.; Jammy, R.; Joe, R.; Dip, A.; Takuya, S.; Yasushi, A.; Takanobu, K.; Tsunetoshi, A.; Masayuki, T. Additive mobility enhancement and off-state current reduction in SiGe channel pMOSFETs with optimized Si Cap and high-k metal gate stacks. In Proceedings of the 2009 International Symposium on VLSI Technology, Systems, and Applications, Hsinchu, Taiwan, 27–29 April 2009; pp. 22–23. [Google Scholar]

- Zhang, B.; Yu, W.; Zhao, Q.T.; Hartmann, J.; Lupták, R.; Buca, D.; Bourdelle, K.; Wang, X.; Mantl, S. High mobility Si/Si0.5Ge0.5/strained SOI p-MOSFET with HfO2 /TiN gate stack. In Proceedings of the 2010 10th IEEE International Conference on Solid-State and Integrated Circuit Technology, Shanghai, China, 1–4 November 2010; pp. 911–913. [Google Scholar]

- Ando, T.; Hashemi, P.; Bruley, J.; Rozen, J.; Ogawa, Y.; Koswatta, S.; Chan, K.K.; Cartier, E.A.; Mo, R.; Narayanan, V. High Mobility High-Ge-Content SiGe PMOSFETs Using Al2O3/HfO2 Stacks With In-Situ O3 Treatment. IEEE Electron Device Lett. 2017, 38, 303–305. [Google Scholar] [CrossRef]

- Lee, C.H.; Kim, H.; Jamison, P.; Southwick, R.G.; Mochizuki, S.; Watanabe, K.; Bao, R.; Galatage, R.; Guillaumet, S.; Ando, T.; et al. Selective GeOx-scavenging from interfacial layer on Si1−xGex channel for high mobility Si/Si1−xGex CMOS application. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Chang, K.M.; Chen, C.F.; Lai, C.H.; Kuo, P.S.; Chen, Y.M.; Chang, T.Y. Electrical properties of SiGe nanowire following fluorine/nitrogen plasma treatment. Appl. Surf. Sci. 2014, 289, 581–585. [Google Scholar] [CrossRef]

- Li, Y.; Cheng, X.; Zhong, Z.; Zhang, Q.; Wang, G.; Li, Y.; Li, J.; Ma, X.; Wang, X.; Yang, H.; et al. Key Process Technologies for Stacked Double Si0.7Ge0.3 Channel Nanowires Fabrication. ECS J. Solid State Sci. Technol. 2020, 9, 064009. [Google Scholar] [CrossRef]

| Category | Ion (µA) | SS (mV/dec) | Vtsat (V) | Ion/Ioff |

|---|---|---|---|---|

| Conventional SiGe channel FinFET | 13.3 | 149 | 0.38 | 1 × 105 |

| Four-period stacked SiGe/Si channel FinFET | 21.2 | 90 | 0.16 | 1 × 106 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, Y.; Zhao, F.; Cheng, X.; Liu, H.; Zan, Y.; Li, J.; Zhang, Q.; Wu, Z.; Luo, J.; Wang, W. Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics. Nanomaterials 2021, 11, 1689. https://doi.org/10.3390/nano11071689

Li Y, Zhao F, Cheng X, Liu H, Zan Y, Li J, Zhang Q, Wu Z, Luo J, Wang W. Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics. Nanomaterials. 2021; 11(7):1689. https://doi.org/10.3390/nano11071689

Chicago/Turabian StyleLi, Yongliang, Fei Zhao, Xiaohong Cheng, Haoyan Liu, Ying Zan, Junjie Li, Qingzhu Zhang, Zhenhua Wu, Jun Luo, and Wenwu Wang. 2021. "Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics" Nanomaterials 11, no. 7: 1689. https://doi.org/10.3390/nano11071689

APA StyleLi, Y., Zhao, F., Cheng, X., Liu, H., Zan, Y., Li, J., Zhang, Q., Wu, Z., Luo, J., & Wang, W. (2021). Four-Period Vertically Stacked SiGe/Si Channel FinFET Fabrication and Its Electrical Characteristics. Nanomaterials, 11(7), 1689. https://doi.org/10.3390/nano11071689