Abstract

A novel output-capacitorless low-dropout regulator (OCL-LDO) with an embedded slew-rate-enhancement (SRE) circuit is presented in this paper. The SRE circuit adopts a transient current-boost strategy to improve the slew rate at the gate of the power transistor when a large voltage spike at the output is detected. In addition, a feed-forward transconductance cell is introduced to form a push–pull output structure with the power transistor. The simulation results show that the maximum transient output voltage variation is when the load current is stepped from to in with a load capacitance of , and the settling time is . The proposed OCL-LDO consumes a quiescent current of and has a dropout voltage of for the maximum output current of .

1. Introduction

Power management units are popular in system-on-chip (SoC) applications because multiple voltage regulators can be used to individually power system sub-modules [1]. Among the many candidates for on-chip power management, LDO (low dropout regulator) regulators capable of providing accurate and clean supply voltages are considered suitable for SoC applications. Traditional LDOs rely on large off-chip capacitors on the order of at the output to ensure system stability while improving transient response and power supply rejection (PSR) [2,3,4]. For portable systems with SoC architectures, bulky off-chip capacitors are not desirable. This led to the development of LDO regulators without off-chip capacitors at the output [5,6,7].

For portable electronic devices, the low quiescent power consumption of OCL-LDOs is critical for improving power efficiency to extend battery runtime. However, OCL-LDOs trade off power consumption and other performance metrics such as loop stability and dynamic performance [8]. The ability to drive large load currents while achieving low dropout voltage requires a PMOS (positive channel metal oxide semiconductor) transistor with a large size as the power device. Since the gate capacitance of the power transistor is proportional to its width, on the one hand, a low-frequency pole is introduced into the system, which affects the stability of the OCL-LDO, and on the other hand, the time for charging and discharging the gate parasitic capacitance of the power transistor is greatly increased. Especially for applications that require low power consumption, the system faces the problem of reduced bandwidth and slew rate, so improving the transient performance of OCL-LDOs is one of the main design challenges.

Currently, many LDO regulators without large off-chip capacitors have been reported. To cater to the need for the low-power consumption of portable devices in standby mode, some LDOs are designed to operate at currents in the order of [9,10]. LDOs with bias currents struggle to respond quickly to the load transitions because unity-gain bandwidth (UGB) is limited by ultra-low currents. In addition, low power consumption undoubtedly reduces the slew rate at the gate of the power transistor, further deteriorating the transient response. Reference [11] uses an advanced Q-reduction technique to improve UGB, but the proposed LDO requires a compromise on minimum load current, which limits its application in long-standby systems. Although flipped voltage follower (FVF)-based LDO regulators are easy in transient response, the tradeoff is low loop gain [12,13]. Low loop gain tends to induce poor load regulation [14]. Other LDOs designed with a two-stage amplifier structure also suffer from low gain, especially when operating at low supply voltages [15,16,17,18]. In [19,20,21], adaptive biasing techniques are adopted to improve the transient response of the LDO while maintaining low quiescent power consumption at light loads. However, this solution only works when switching from a heavy load to a light load. Dynamic biasing techniques use capacitive coupling to increase the bias current during load switching, so as to improve the transient performance without increasing steady-state power [9]. Unfortunately, RC networks need to occupy chip areas, and more seriously, the SRE circuit may degrade loop stability.

Since it is difficult for portable applications to balance loop stability and transient response performance at low power consumption, a new solution is required to design OCL-LDOs. This paper proposes a dynamic SRE technique to address the above difficulties. This technique achieves transient enhancement by increasing the slew rate at the gate of the power transistor and the output node during the transient instant. The proposed SRE circuit reuses the frequency compensation capacitors and the common gate transistors, which greatly reduces the additional bias current.

The rest of the paper is organized as follows: Section 2 presents the architecture as well as the stability analysis of the proposed OCL-LDO. Section 3 describes the schematic of the proposed circuit and explains the operation of the circuit during load transitions. Section 4 presents the simulation results, discussions, and performance comparisons. Finally, we draw conclusions in Section 5.

2. Proposed Architecture

2.1. Topology

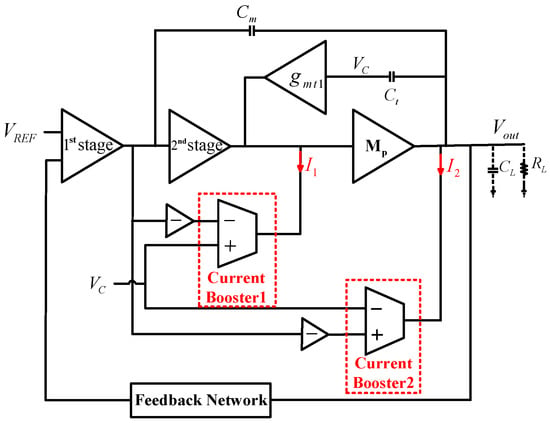

The topology of the proposed OCL-LDO is shown in Figure 1, including an error amplifier as the first stage, a non-inverting amplifier as the second stage, a power transistor as the third stage, a frequency compensation network, a transient-current boosting circuit, and a feedback network, where the compensation network consists of , , and , and the transient-current boosting circuit consists of two current boosters. represents the effective output resistance. The total capacitance at the output is the equivalent output lumped capacitance of the load capacitor in the range of – plus the equivalent parasitic capacitance of the power transistor. The input voltage of the transconductance cell is denoted as . In the proposed architecture, the frequency compensation capacitors and couple the output voltage variation during the load transients and pass it to the current boosters for transient enhancement.

Figure 1.

Conceptual structure of the proposed OCL−LDO regulator.

The transient-current boosting circuit consists of two current boosters, as shown in Figure 1. The output current is quadratically dependent on the booster-cell differential input voltage. Due to the action of the two inverters, the voltages at the positive and negative inputs of the current boosters always change in opposite directions during transients. That is to say, when the voltage at the positive input terminal of booster 1,2 changes by , the voltage at the negative input terminal changes by , then the total input voltage change is . Therefore, even with small bias currents, and are able to be boosted up during load transients, which means that the slew rate at the power transistor gate and the output node can be enhanced.

2.2. Stability Analysis

The stability of the proposed OCL-LDO is achieved by the TCFC compensation technique, which can provide higher current-bandwidth efficiency [22]. Figure 2 shows the equivalent small-signal model of the proposed OCL-LDO, where is defined as the transconductance of each stage, whereas and represent the output resistance and lumped parasitic capacitance, respectively. and compose the non-inverting second stage. is the output resistance of M19, which is a pFET in saturation. is the transconductance of the power transistor Mp. The effective output resistance is defined by , where and is the output resistance of the output stage and load resistance, respectively. models the load capacitance as defined above. The Miller compensation capacitor forms an external feedback loop, and the internal compensation capacitor feeds back the output signal to the gate of the power transistor through the transconductance . In order to improve the transient performance of the system, a feed-forward transconductance stage is introduced in the OCL-LDO, which can form a push–pull structure with the power transistor to further improve the slew rate at the output node.

Figure 2.

Small−signal model of the proposed OCL−LDO regulator.

Both and are given by the equivalent transconductance of the circuit structure shown in Figure 3. is defined as:

can be deduced as follows:

where is the transconductance of M2. In the proposed design, is actually realized by the of M15 and M21, which are two nFETs in saturation, showing large resistance, so . Specifically, , . It can be concluded that , . Compared with and , the contributions of and to the current are insignificant and therefore can be ignored. Thus, the small-signal model in Figure 2 can be simplified as shown in Figure 4.

Figure 3.

Equivalent model of the transconductance cell .

Figure 4.

Simplified small−signal model of Figure 2.

For simplicity, we assume that the DC gain of each stage is large enough, and the compensation capacitance is larger than the parasitic capacitance of the first stage. and are much smaller than the load capacitance , as given by:

It is worth noting that includes the gate parasitic capacitance of the power transistor and is therefore large. The derived small-signal transfer function for the open-loop gain of the OCL-LDO is given by:

and are the low-frequency gain and the dominant pole, respectively, which are given as:

Hence, the gain-bandwidth product can be obtained as:

Since the load current will change, the stability of the proposed LDO should be discussed for different load conditions.

Case I (low output current): In this case, is very large, so that . The non-dominant poles and zeros can be expressed as:

From the above analysis, it can be seen that can cancel each other out. The other two zeros, and , only appear at high frequencies. For a third-order Butterworth frequency response with the damping factor , the stability conditions are given by:

When and are large, Equation (15) is easily satisfied. It can be noticed that is proportional to , so the worst stability of the circuit occurs with no load current and maximum load capacitance. As the load current increases, will undoubtedly be pushed to higher frequencies and the phase margin will increase.

Case II (moderate to maximum output current): In this case, is small, as it is greatly affected by the load current (). The expressions for the zeros, dominant pole, and GBW remain the same. The non-dominant poles change, as given by:

It can be observed that remains the same. Since GBW does not vary with the load current, still holds. With a small , is located at a higher frequency than GBW and has no effect on LDO stability. Hence, the loop stability only depends on the location of . Compared to the case discussed before, even though is smaller, the larger pushes to higher frequencies, thus improving the phase margin. Furthermore, the zero is located slightly beyond the GBW for the enhancement of the phase margin.

In fact, the stability of the circuit is improved with SRE. Specifically, we return to Figure 2 for a detailed analysis of the true equivalent transconductance of the second gain stage. It follows that , where . It can be found that , which means that when the SRE circuit fails and the system is under a light load, and will move closer to the unit gain bandwidth and the stability of the circuit will be slightly worse. At heavy loads, this situation is improved, as is still pushed to high frequencies.

3. Design of the Proposed OCL-LDO Regulator

3.1. Schematic

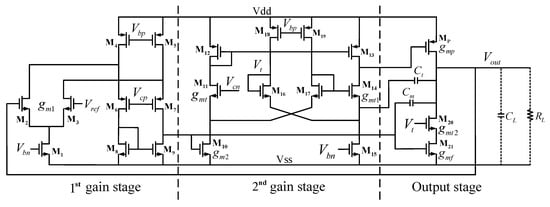

The full schematic of the proposed OCL-LDO is depicted in Figure 5. The first gain stage is realized by a single folded-cascode error amplifier with M1-M9. The differential pair M2 and M3 provides the transconductance . The second stage is a non-inverting amplifier composed by M10–M19. Mp is the power transistor, which together with the feed-forward transconductance module M21 constitutes a push–pull output stage. are capacitors for frequency compensation. and represent the equivalent output resistance and load capacitance, respectively. The transconductances of transistors M11, M14, M20, and M21 are , , , and , respectively. , , , and are the bias voltages provided by the bias circuit. The circuit consumes a total of quiescent current, of which the first, second, and output stages consume 3, 15, and 9, respectively, and the remaining 3 is consumed by the bias circuit.

Figure 5.

Full schematic of the proposed OCL−LDO regulator.

3.2. Overshoot and Undershoot Reduction

The slew rate at the power transistor gate node and output node affects the transient response. As shown in Figure 5, these two nodes correspond to two charging and discharging paths, one is composed of M13 and M14, and the other is composed of , M20, and M21. Therefore, it is important to dynamically increase the current in these two critical paths. This paper uses the coupling effect of and when receiving the load current switching request to sense the change of , and pass it to the two current boosters composed of M14 and M20 to accelerate the charging and discharging of the load capacitor and the gate parasitic capacitance of the power transistor.

When generates a spike in response to an urgent load current request, detects the spike and changes the gate voltage of M14 by − through the inverter formed by M10 and M17, while its source voltage changes due to the coupling effect of . This causes the of M14 to change by −. When undershoots, the current of M14 is boosted and the current of M13 is decreased through the replication of the current mirror formed by M12 and M13. On the one hand, the second stage can therefore withdraw more current to discharge the gate parasitic capacitance of . When overshoots, the circuit operates in the opposite way to quickly charge the gate capacitance of Mp. On the other hand, for the output node, the push–pull output stage formed by M21 and Mp helps to enhance the slew rate. It should be noted that the path formed by M20 and M21 is the primary channel to discharge the extra current when overshoots. Therefore, while reducing the current of Mp, it is more important to increase the current through M20 and M21 to suppress the overshoot of . Fortunately, M20 can do this by pulling a large current in a similar manner to M14. When is regulated back to a steady state, the operation of dynamic current boost is automatically shut down to save energy.

4. Simulation Results and Discussions

The simulated loop gain responses of the proposed regulator at different load current conditions are shown in Figure 6. In the case of , the regulator achieves a minimum phase margin (PM) of and a minimum gain margin (GM) of for the load current range from 0 to . As the load current raises, the PM and GM increase to and . At heavy load conditions, reduces dramatically when Mp enters into the triode region. In this case, the gain of the output stage is reduced, as is the . However, because the proposed regulator has three gain stages, the minimum of is found at . Moreover, the stability of the proposed OCL-LDO for is investigated to conduct the loop gain response in Figure 7. A minimum phase margin (PM) of and a minimum gain margin (GM) of are achieved. Theoretical analysis shows that the system has the worst PM and GM when and . Therefore, for further verification, Monte-Carlo simulations are achieved under the condition of and . As Figure 8a,b illustrate, the average PM and GM achieved by the proposed OCL-LDO are and 11.5 dB, respectively. Meanwhile, Table 1 shows the simulated PM and GM across PVT variations. The results shown in Figure 8 and Table 1 verify that the stability of the proposed OCL-LDO can be guaranteed.

Figure 6.

Simulated open−loop gain at different load currents with .

Figure 7.

Simulated open−loop gain at different load currents with .

Figure 8.

Monte−Carlo simulations when and . (a) PM, (b) GM.

Table 1.

Simulation results over PVT variation for the best, mean, and worst stability cases.

The proposed circuit is able to supply a load current from to with a dropout voltage of for a supply of . The circuit, including the bias circuit, consumes of quiescent current over the specified load current range. The simulated load transient responses under different load capacitor conditions are given in Figure 9. As shown in Figure 9a, when the load current is switched between and with an edge time of 100 ns for the case of , the simulated undershoot and overshoot are and , respectively. On the other hand, the maximum undershoot and overshoot for are and , as shown in Figure 9b. The maximum output voltage variation is about with load step changes of , and it can return to the final state within .

Figure 9.

Simulated load transient response of the proposed OCL−LDO regulator for a load current switched between 0 and with an edge time of . (a) , (b) .

Generally speaking, if the output is connected to a large load capacitor, when the load current changes, the overshoot and undershoot can be effectively reduced because the capacitor charges and discharges the output node. However, as shown in Figure 9, the undershoot with 100 pF is even larger than the case with 0 pF . This is because the pole of the output node is close to the unit gain bandwidth when the LDO is connected to a 100 pF load capacitor. During the transition of the load current, the bias voltage and bias current of the amplifier will deviate greatly. In particular, the voltage across the gate and source of M14 deviates sharply due to the change in the opposite direction, resulting in the nonlinear behavior of the circuit. This deviation causes the pole and zero frequency to change during the load transition, so the circuit has more overshoot in this case. On the other hand, the nonlinear behavior of the circuit leads to the generation of rings in the transient response, as shown in Figure 9b. If the gate voltage of M14 is connected to a fixed bias, and the circuit structure, transistor size, and bias current are kept unchanged, the deviation of the bias current of M14 decreases during the load transition. The rings are improved in this case.

To verify the proposed SRE technique of the OCL-LDO, the transient waveforms of the output voltage are simulated with and without the SRE circuit. For a fair comparison, the only difference is that the gate voltages of the transistors M14 and M20 are biased to a fixed value, while the circuit structure, transistor size, and bias current remain the same. As shown in Figure 10, with the help of the slew-rate-enhancement technique, the undershoot is reduced by more than 45 and the settling time is also improved.

Figure 10.

Simulated load transient response of the proposed OCL−LDO regulator under the cases with and without the SRE, for load currents switched between 0 and with an edge time of . (a) , (b) .

It can be seen from Figure 10 that without SRE, the undershoot of the LDO is much larger than the overshoot. This is because when the circuit is switched from light to heavy loads, the gate voltage of the power transistor cannot be pulled down quickly due to the large parasitic capacitance, so it cannot provide a large current to the output in time. To solve this problem, the designed SRE circuit can provide a larger discharge current for the gate capacitance of the power transistor during load transitions. Therefore, the improvement for the undershoot is significantly better compared to the overshoot. Moreover, without SRE, the output has rings when the circuit steps from heavy to light loads, as shown in Figure 10b. This shows that the SRE circuit is helpful to the stability of the system, which is consistent with the previous stability analysis.

Since the PSR is related to the loop gain at low frequencies, and the large load capacitance bypasses the output ripple to the ground at high frequencies, we present the worst-case PSR in Figure 11. As depicted, the PSR has its best value at low frequencies. Because the proposed LDO has a three-stage gain structure and has an optimized gain-bandwidth product in TCFC compensation, the proposed OCL-LDO is capable of providing a good PSR. In order to more objectively evaluate the performance improvement in the proposed OCL-LDO resulting from the slew-rate-enhancement technique, a comparison with the state-of-the-art work is given in Table 2. A figure-of-merit () for OCL_LDO is adopted to compare the transient performance [23]. Comparisons are also made using a new figure-of-merit () that takes into account the effects of parasitic capacitances under different processes [14]. It is given by:

where is the edge time ratio and defined by:

Figure 11.

PSR simulations of the proposed OCL−LDO regulator for and .

Table 2.

Performance comparison with prior-reported OCL-LDO regulators.

is the minimum channel length associated with the process. The smaller value means a better transient performance metric. The value of the proposed design is second only to that reported in [9]. However, the maximum load capacitance in [9] is only , which limits its application. In [17], the dropout voltage of the LDO is designed to be 150mV. Smaller dropout voltage results in higher power efficiency, but at the expense of a larger power transistor for the same drive capability. This means that the gate parasitic capacitance of the power transistor is larger, so the transient response is significantly worse than that of this paper. With the proposed circuit architecture, the voltage-spike detection scheme, and the SRE technique, the transient performance of the designed OCL-LDO has a greater advantage compared to other designs with the same power.

5. Conclusions

A low-power OCL-LDO regulator with embedded transient enhancement is implemented with a 40nm standard CMOS process. With the proposed transient enhancement technique and circuit architecture, the OCL-LDO can guarantee stability over the full load range of without the limitation of a minimum load current. The dropout voltage is . The simulation results show that the undershoot of the proposed OCL-LDO is significantly improved, and the quiescent power consumption does not increase when the system is heavily loaded. Compared with the prior art, the proposed OCL-LDO regulator achieves a better transient performance indicator and also provides good performance parameters in terms of line regulation, load regulation, and PSR. The above work will be helpful for on-chip applications.

Author Contributions

Conceptualization, S.N. and H.C.; methodology, S.N.; validation, S.N., Z.C., and X.L.; formal analysis, C.H.; investigation, S.N.; resources, S.N.; data curation, Z.C.; writing—original draft preparation, S.N.; writing—review and editing, S.N.; visualization, Q.W.; supervision, C.H.; project administration, S.S.; funding acquisition, Z.S. All authors have read and agreed to the published version of the manuscript.

Funding

This research was funded by the National Natural Science Foundation of China (grant numbers 92164302, 61874129, 91964204, 61904186, 61904189, 61874178), the Strategic Priority Research Program of the Chinese Academy of Sciences (grant number XDB44010200), the Science and Technology Council of Shanghai (grant numbers 17DZ2291300, 19JC1416801, 2050112300), the Youth Innovation Promotion Association CAS under Grant 2022233, and in part by the Shanghai Research and Innovation Functional Program under Grant 17DZ2260900.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

Not applicable.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Buss, D.D. Technology in the Internet age. In Proceedings of the 2002 IEEE International Solid-State Circuits Conference. Digest of Technical Papers (Cat. No.02CH37315), San Francisco, CA, USA, 7 February 2002; pp. 18–21. [Google Scholar]

- Raducan, C.; Neag, M. Slew-rate booster and frequency compensation circuit for automotive LDOs. IEEE Trans. Circuits Syst. I Reg. Pap. 2022, 69, 465–477. [Google Scholar] [CrossRef]

- Ming, X.; Kuang, J.-J.; Liang, H.; Zhang, J.; Qin, Y.; Zhang, Z.-W.; Wang, Z.; Zhang, B. A fast-transient low-dropout regulator with current-efficient super transconductance cell and dynamic reference control. IEEE Trans. Circuits Syst. I Reg. Pap. 2021, 68, 2354–2367. [Google Scholar] [CrossRef]

- Carreon-Bautista, S.; Huang, L.; Sanchez-Sinencio, E. An autonomous energy harvesting power management unit with digital regulation for IoT applications. IEEE J. Solid-State Circuits 2016, 51, 1457–1474. [Google Scholar] [CrossRef]

- Bu, S.; Guo, J.; Leung, K.N. A 200-ps-response-time output-capacitorless low-dropout regulator with unity-gain bandwidth>100 MHz in 130-nm CMOS. IEEE Trans. Power Electron. 2018, 33, 3232–3246. [Google Scholar] [CrossRef]

- Bu, S.; Leung, K.N.; Lu, Y.; Guo, J.; Zheng, Y. A fully integrated low dropout regulator with differentiator-based active zero compensation. IEEE Trans. Circuits Syst. I Reg. Pap. 2018, 65, 3578–3591. [Google Scholar] [CrossRef]

- Milliken, R.J.; Silva-Martinez, J.; Sanchez-Sinencio, E. Full on-chip CMOS low-dropout voltage regulator. IEEE Trans. Circuits Syst. I Reg. Pap. 2007, 54, 1879–1890. [Google Scholar] [CrossRef]

- Chong, S.; Chan, P.K. A 0.9-μA quiescent current output-capacitorless LDO regulator with adaptive power transistors in 65-nm CMOS. IEEE Trans. Circuits Syst. I Reg. Pap. 2013, 60, 1072–1081. [Google Scholar] [CrossRef]

- Huang, Y.; Lu, Y.; Maloberti, F.; Martins, R.P. Nano-ampere low-dropout regulator designs for IoT devices. IEEE Trans. Circuits Syst. I Reg. Papers 2018, 65, 4017–4026. [Google Scholar] [CrossRef]

- Adorni, N.; Stanzione, S.; Boni, A. A 10-mA LDO with 16-nA IQ and operating from 800-mV supply. IEEE J. Solid-State Circuits 2020, 55, 404–413. [Google Scholar] [CrossRef]

- Lau, S.K.; Mok, P.K.T.; Leung, K.N. A low-dropout regulator for SoC with Q-reduction. IEEE J. Solid-State Circuits 2007, 42, 658–664. [Google Scholar] [CrossRef]

- Cai, G.; Lu, Y.; Zhan, C.; Martins, R.P. A fully integrated FVF LDO with enhanced full-spectrum power supply rejection. IEEE Trans. Power Electron. 2021, 36, 4326–4337. [Google Scholar] [CrossRef]

- Huang, M.; Feng, H.; Lu, Y. A fully integrated FVF-based low-dropout regulator with wide load capacitance and current ranges. IEEE Trans. Power Electron. 2019, 34, 11880–11888. [Google Scholar] [CrossRef]

- Hong, S.-W.; Cho, G.-H. High-gain wide-bandwidth capacitor-less low-dropout regulator (LDO) for mobile applications utilizing frequency response of multiple feedback loops. IEEE Trans. Circuits Syst. I Reg. Pap. 2016, 63, 46–57. [Google Scholar] [CrossRef]

- Chen, F.; Lu, Y.; Mok, P.K.T. A fast-transient 500-mA digitally assisted analog LDO with 30-μV/mA load regulation and 0.0073-ps FoM in 65-nm CMOS. IEEE J. Solid-State Circuits 2020, 56, 511–520. [Google Scholar] [CrossRef]

- Tang, J.; Lee, J.; Roh, J. Low-power fast-transient capacitor-less LDO regulator with high slew-rate class-AB amplifier. IEEE Trans. Circuits Syst. II Exp. Briefs 2019, 66, 462–466. [Google Scholar] [CrossRef]

- Li, G.; Qian, H.; Guo, J.; Mo, B.; Lu, Y.; Chen, D. Dual active-feedback frequency compensation for output-capacitorless LDO with transient and stability enhancement in 65-nm CMOS. IEEE Trans. Power Electron. 2020, 35, 415–429. [Google Scholar] [CrossRef]

- Man, T.Y.; Mok, P.K.T.; Chan, M. A high slew-rate push–pull output amplifier for low-quiescent current low-dropout regulators with transient-response improvement. IEEE Trans. Circuits Syst. II Exp. Briefs 2007, 54, 755–759. [Google Scholar] [CrossRef]

- Mandal, D.; Desai, C.; Bakkaloglu, B.; Kiaei, S. Adaptively biased output cap-less NMOS LDO with 19ns settling time. IEEE Trans. Circuits Syst. II Exp. Briefs 2019, 66, 167–171. [Google Scholar] [CrossRef]

- Pereira-Rial, Ó.; López, P.; Carrillo, J.M.; Brea, V.M.; Cabello, D. An 11 mA capacitor-less LDO with 3.08 nA quiescent current and SSF-based adaptive biasing. IEEE Trans. Circuits Syst. II Exp. Briefs 2022, 69, 844–848. [Google Scholar] [CrossRef]

- Ming, X.; Kuang, J.J.; Gong, X.C.; Lin, Z.; Xiong, J.; Qin, Y.; Zhang, B. A fast-transient capacitorless LDO with dual paths active-frequency compensation scheme. IEEE Trans. Power Electron. 2022, 37, 10332–11034. [Google Scholar] [CrossRef]

- Peng, X.; Sansen, W. Transconductance with capacitances feedback compensation for multistage amplifiers. IEEE J. Solid-State Circuits 2005, 40, 1514–1520. [Google Scholar] [CrossRef]

- Guo, J.; Leung, K.N. A 6-μW chip-area-efficient output-capacitorless LDO in 90-nm CMOS technology. IEEE J. Solid-State Circuits 2010, 45, 1896–1905. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2022 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).