Abstract

This paper presents the design results of a 100-channel integrated circuit dedicated to various biomedical experiments requiring both electrical stimulation and recording ability. The main design motivation was to develop an architecture that would comprise not only the recording and stimulation, but would also block allowing to meet different experimental requirements. Therefore, both the controllability and programmability were prime concerns, as well as the main chip parameters uniformity. The recording stage allows one to set their parameters independently from channel to channel, i.e., the frequency bandwidth can be controlled in the (0.3 Hz–1 kHz)–(20 Hz–3 kHz) (slow signal path) or (0.3 Hz–1 kHz)–4.7 kHz (fast signal path) range, while the voltage gain can be set individually either to 43.5 dB or 52 dB. Importantly, thanks to in-pixel circuitry, main system parameters may be controlled individually allowing to mitigate the circuitry components spread, i.e., lower corner frequency can be tuned in the 54 dB range with approximately 5% precision, and the upper corner frequency spread is only 4.2%, while the voltage gain spread is only 0.62%. The current stimulator may also be controlled in the broad range (69 dB) with its current setting precision being no worse than 2.6%. The recording channels’ input-referred noise is equal to 8.5 µVRMS in the 10 Hz–4.7 kHz bandwidth. The single-pixel occupies 0.16 mm2 and consumes 12 µW (recording part) and 22 µW (stimulation blocks).

1. Introduction

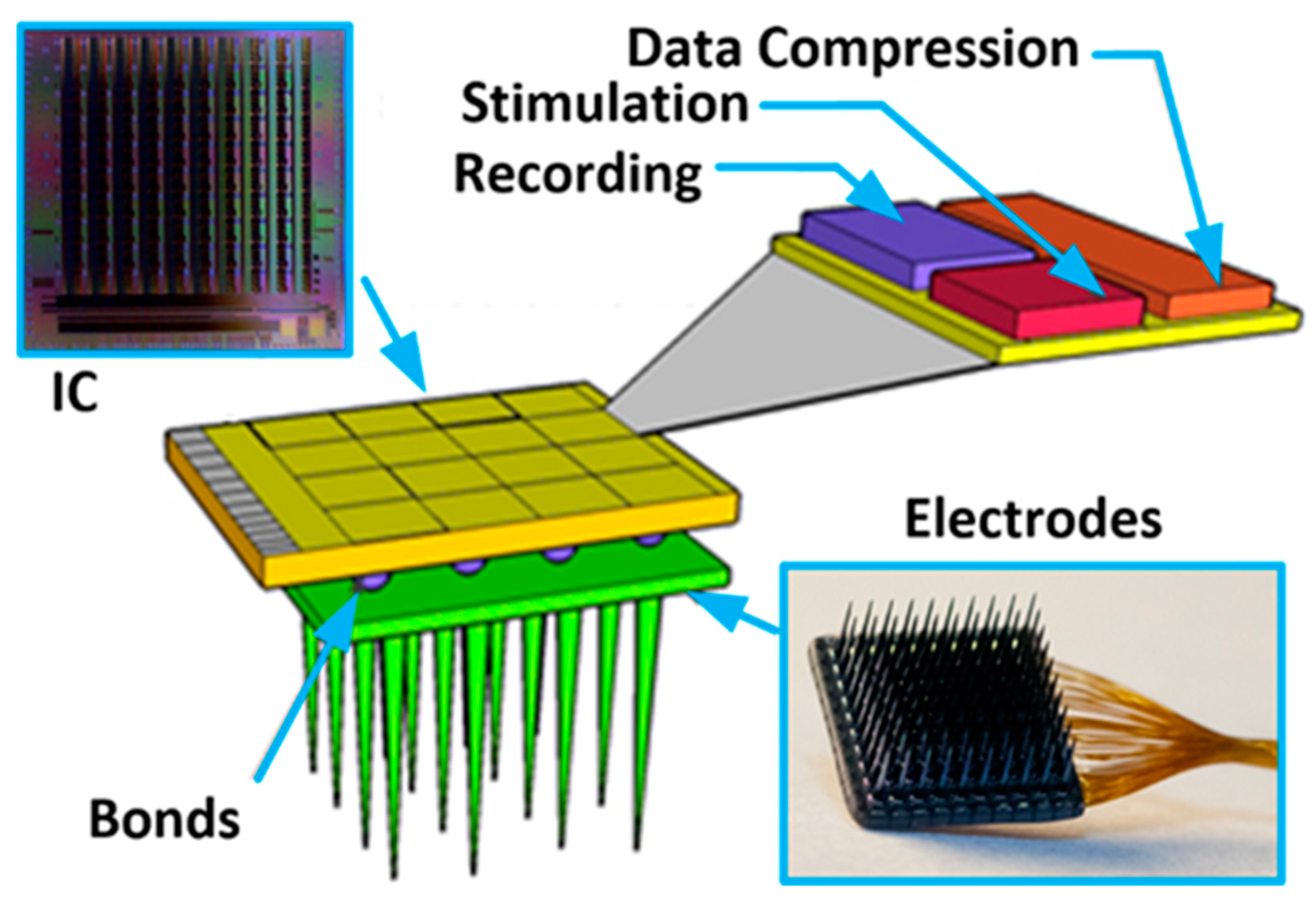

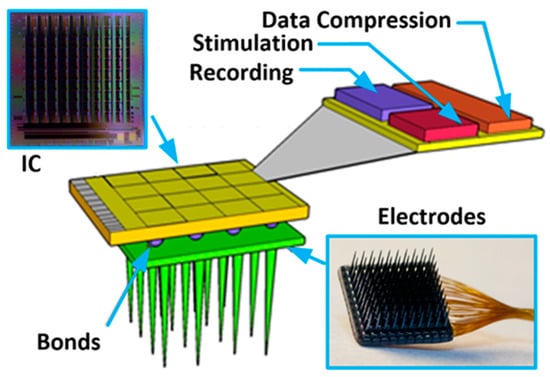

Existing technologies allow building systems comprised of sensors combined with electronics that can be used for different kinds of application (i.e., science, consumer market, military) [1,2]. Whenever such systems need to be very small, have large functionality, low power consumption, battery-less supply, and architecture allowing for multisite signal processing (see Figure 1), modern technologies are the only way to satisfy these requirements. These may be Micro-Electro-Mechanical Systems (MEMS) and Very Large-Scale Integration (VLSI) technologies for sensors and electronics production, respectively [3,4]. One of the contemporary technologies beneficiaries is also biomedicine which deals with experiments exploiting the electrical nature of neural-to-neural communication in living organisms. The main motivation of that experiments is the need for neural coding and processing cognition, finding cures for nervous system-related diseases, or developing prostheses for people with different disabilities [5,6,7,8,9,10,11,12]. These explorations are run as in vitro or in vivo experiments, and are realized with the use of electronic circuits that either record or/and stimulate neural activity. The common denominator for the mentioned experiments is the fact that the more active sites are in a single system (i.e., more inputs/outputs for recording/stimulation), the better the understanding of the observed phenomenon. Moreover, the systems’ spatial resolution is highly important as it allows for individual signal propagation monitoring (this parameter depends on the targeted experiments and can span from a single µm up to a few hundreds of µm). Next, a significant number of experiments require not only recording or stimulating neural activity, but also to have both of these functionalities and, what is more, to record different signal species (i.e., signals that vary in their amplitudes and frequency bandwidth). And finally, considering the in vivo experiments, one needs to also respect requirements regarding the wireless transmission of both energy and data. It becomes clear that a large number of active sites would be a source of a huge amount of data which, especially considering in vivo experiments, may pose a problem of the data bottleneck. Therefore, there is also a need to perform, directly on-chip data processing as much as possible to as to decrease the amount of valuable data, i.e., signal detection and classification, its conversion and data compression, etc. Having all of these in mind, one can see that neurobiologists expect highly functional systems comprising as many active sites as possible with large functionality, meaning that modern submicron or even nanometer technologies adaptation becomes one possible solution. Considering that the area dedicated to the single active site is imposed by a particular experiment, the area of the single conditioning system part needs to be reduced to allow for other functionalities to be implemented. Some solutions partially solve that problem, such as in [13,14,15,16], where the signal is pre-processed by the conditioning block, integrated with the electrode (with the use of the same fabrication process), and is further provided to the rest part of the system (additional conditioning analog circuitry and digital blocks). Moreover, Refs. [17,18] show a solution that mitigates mentioned problem with the use of 3D technology, i.e., the analog and digital parts are separated on individual dies, while their mutual connections are realized with the use of through silicon via (TSV). However, it should be pointed out that whenever the area occupied by the analog blocks becomes smaller, the problem that may negatively affect the whole neurobiological system, i.e., its performance or uniformity, rises [19,20]. Importantly, the parameters spread from channel to channel may introduce uncertainty in measured/generated signals (whether it comes to recording or stimulation) that may not be accepted, especially in experiments based on signal shape or its propagation parameters analysis. As a consequence, one needs to provide solutions to compromise on low area occupation of the analog part and its main parameters uniformity. Moreover, these solutions should not affect other systems’ parameters, such as power consumption or noise performance.

Figure 1.

The conceptual idea of the implantable multichannel system for neurobiological experiments.

This paper aims to provide a possible solution that can be implemented whenever the abovementioned requirements need to be satisfied in the multichannel systems dedicated to different types of biomedical experiments. The proposed solution is a result of the author’s former works [21,22,23,24,25,26]. The paper is organized as follows. Section 2 provides information regarding the 100-channel integrated circuit (IC). Section 3 and Section 4 provide the design description of the recording and stimulating blocks, with an emphasis on their main parameter uniformity. Section 5 consists of the ICs’ parameters measurement results and neurobiological recording results, while Section 6 provides conclusions.

2. IC Architecture

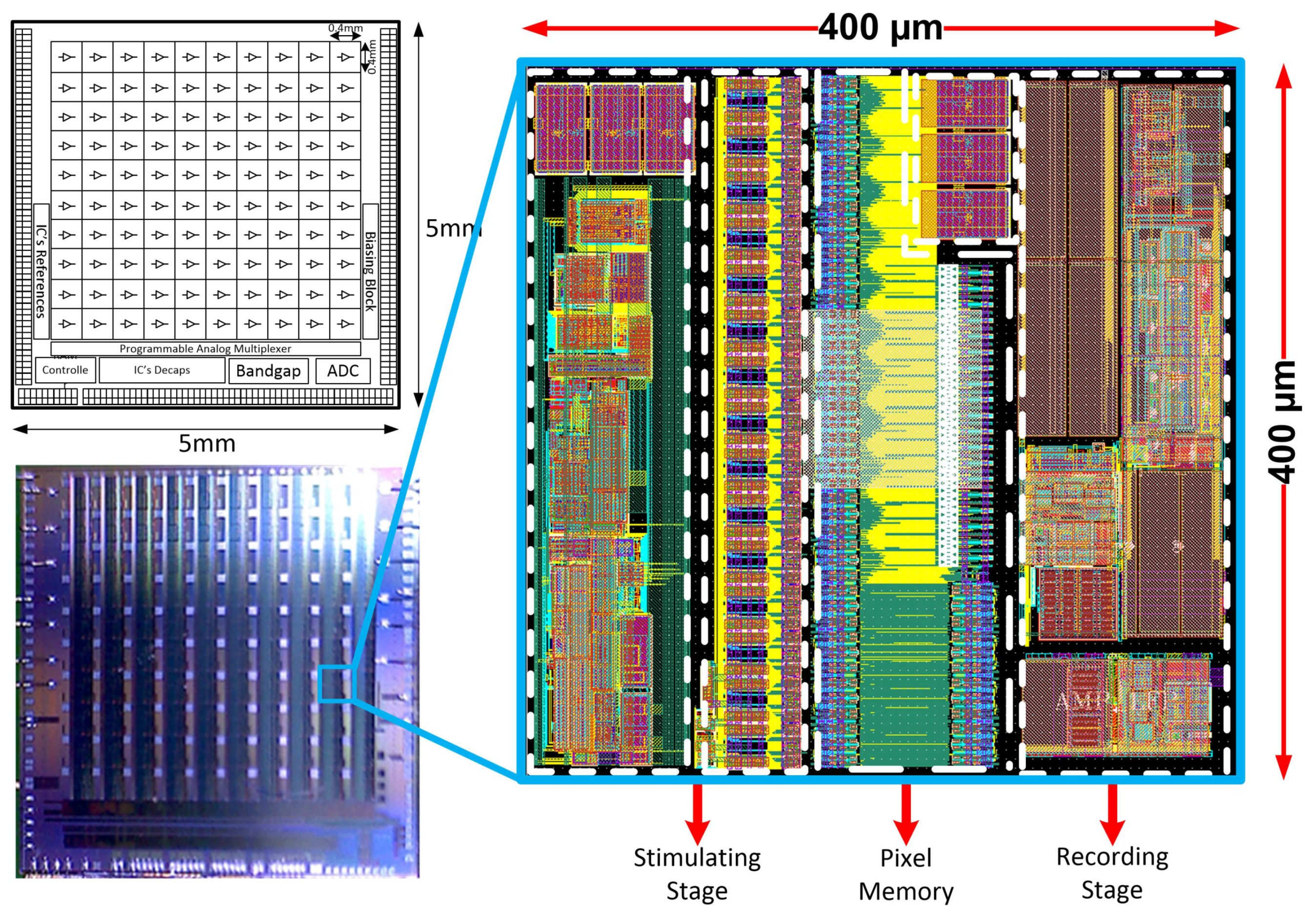

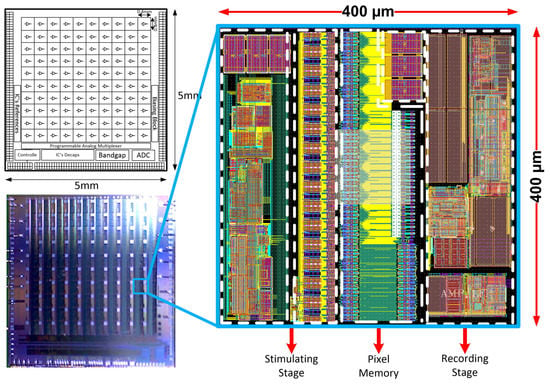

The Neural Recording and Stimulating 100-channel Integrated Circuit (NRS100 IC) is composed of 10 × 10 pixels (each built of recording and stimulation blocks, and 36 × 9-bit memory), Successive Approximation Register (SAR)-based analog to digital converter (ADC), Random-Access Memory (RAM) controller, current/voltage user-controlled references, programmable analog multiplexer, and Low Voltage Differential Signaling (LVDS)- based receivers/transceivers (see Figure 2). The chip occupies an area of 5 × 5 mm2, whereas the single-pixel has a 400 µm pitch to meet 3D electrodes dimensioning (see Figure 1). Based on different biomedical experiments requirements, it was decided that the IC should allow one to record different biomedical signals, i.e., the lower corner frequency (LCF) should be set independently from channel to channel from approximately 1 kHz to below 1 Hz. The upper corner frequency (UCF) should also be independently controlled to allow for signals recording from single Hz up to a few kHz. Additionally, the particular IC’s recording channel should have the ability of its independent voltage gain control. Regarding the stimulation part of the IC, it was decided to provide the user ability to control in broad range stimulation parameters, i.e., stimulating pulses amplitudes, their duration, polarity, and even frequency. Therefore, each pixel has its memory which allows for defining pixel individual 30 stimulation patterns.

Figure 2.

The NRS100 block idea, photograph of the PCB mounted IC, and the single pixels’ layout masks view.

3. Recording Channel

The recording channel is dedicated to performing proper amplification and filtration of weak input biomedical signals to optimally utilize allowable supply voltage and to condition signals for following blocks, such as analog to digital converters. There are many excellent examples of integrated electronics dedicated to biomedical signals recordings [27,28,29,30,31,32,33,34]. These very often utilize additional techniques to overcome problems with noise and power consumption (such as chopping, sigma-delta conversion, ad digital feedback), and promoted results are outstanding. Here, the additional aspect is considered, i.e., main parameter uniformity from channel to channel, ICs’ functionality, and their area occupation that may be important whenever large functionality on a small area is considered [19,20].

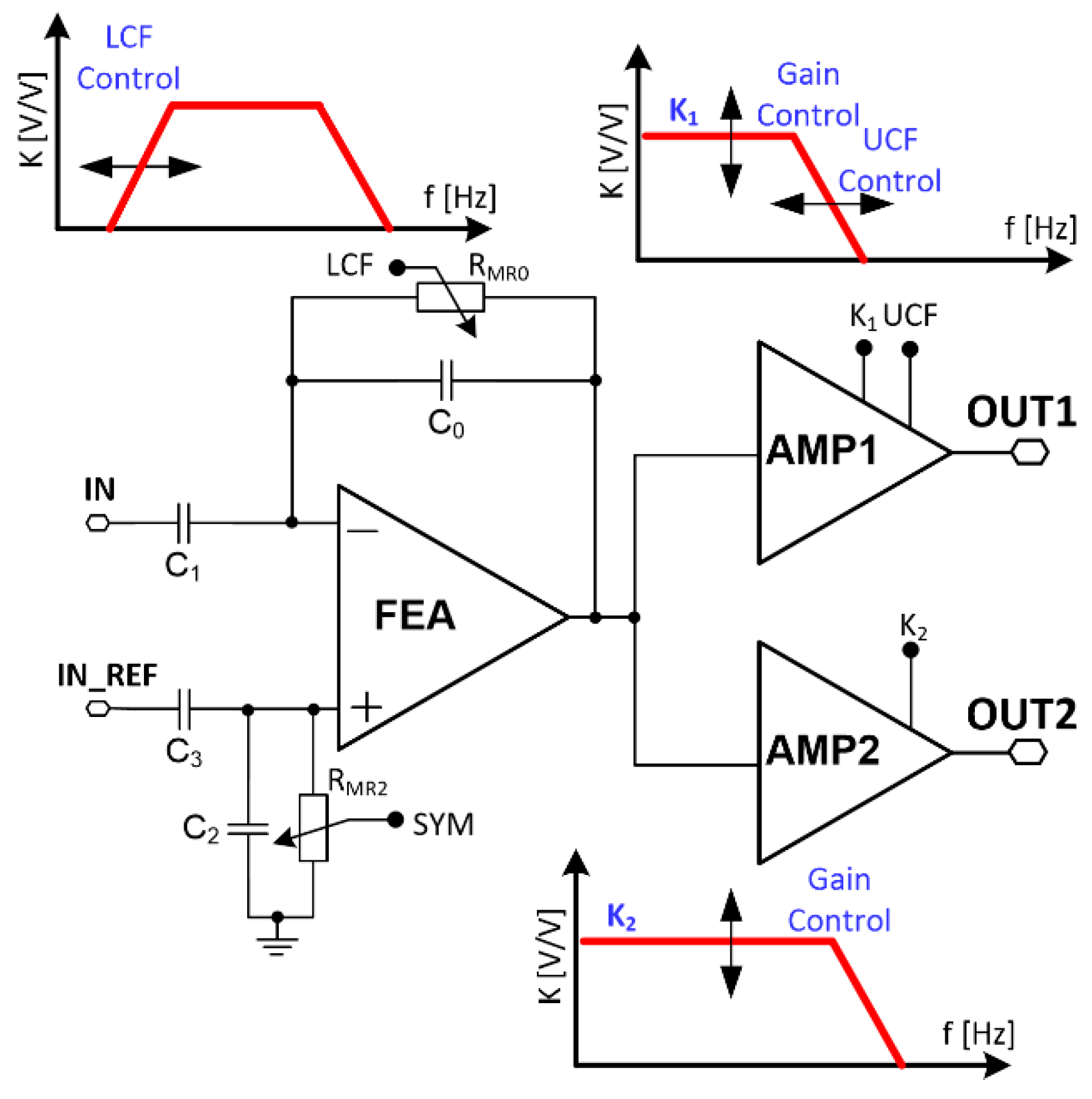

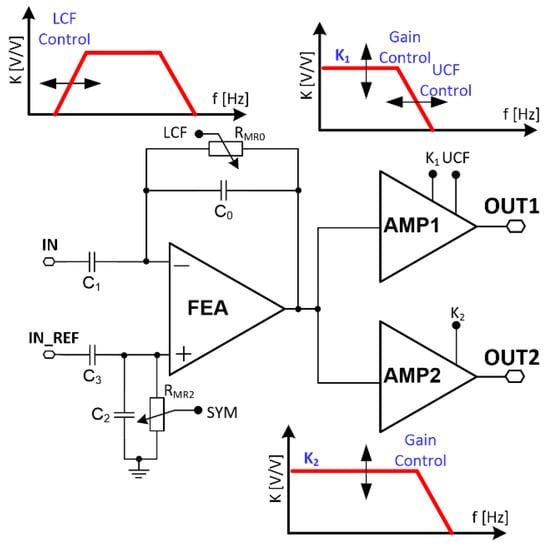

The biomedical signals differ in their amplitudes and frequencies bandwidth (see Table 1), and these parameters need to be taken into account in the complete recording channel design. It can be seen that whenever there is a need to record neurobiological signals with one circuitry, it is necessary to set different voltage gain and filters’ corner frequency. Therefore, a conventional, single path recording channel is not an efficient solution. If, for instance, LFP and AP signals are considered to be recorded simultaneously (see Table 1), it is necessary to set proper ADCs sampling frequency to avoid aliasing, and this results in unnecessarily high sampling frequency for LFP signals. Additionally, as the LFP signals are a few times higher in their amplitudes compared to the AP signals, one needs to set the correct voltage gain setting not to exceed the amplifier’s linear region. As a consequence, the voltage gain may be too small for AP signals, resulting in a higher ADC resolution requirement to properly reconstruct small AP signals. Having all of these in mind, the particular recording channel was divided into two individual conditioning paths, i.e., one for slow and the other for fast signal processing as shown in Figure 3. Both the corner frequencies and voltage gains can be changed in the particular conditioning signal path to address different input signal requirements.

Table 1.

Parameters of the typical biomedical signals [16].

Figure 3.

Recording channels’ schematic idea.

Biomedical signals should be recorded differentially, as they are contaminated by common signals which are usually of much higher amplitudes than the input recorded signals are. Additionally, the front-end amplifier needs to comply with large input DC voltage offsets that are generated on the electrode interface reaching even hundreds of mV.

3.1. Voltage Gain

The recording channels’ mid-band voltage gain K is set by the front-end amplifier and following stages voltage gain, i.e., either the amplifier destined for slow or fast signals defined as K1 and K2, respectively:

In the given project the second amplifying stages are realized with the use of operational amplifiers working with the noninverting configuration. Here, the voltage gains are defined by the high poly-based R1, R2 resistors with the (R1 + R2)/R1 ratio. Finally, the voltage gain spread can be given in the following way:

In the given project the single-pixel was decided to be divided into three equal areas (recording, stimulation, and memory), resulting in an approximately 0.05 mm2 area dedicated to the recording stage. Additionally, bearing in mind that both the recording channel is composed of two amplifying stages and the feedback PMOS transistor forming the RMR0 resistance should be kept in the linear region, the voltage gain was set to 51 v/v. It was performed with the use of 52 unit MIM (metal-insulator-metal) capacitors each of capacitance and area 150 fF and 25.8 × 5.5 µm2, respectively. The C1 is composed of 51 unit capacitors, whereas the unit capacitance spread for a given process is ϬC/C = 0.034%. The area dedicated to the second amplifying stage was 110 × 110 µm2. This resulted in the AMP1 feedback composed of 24 unit resistors of W × L = 0.5 µm × 22 µm producing 50 kΩ unit resistance (R1 = 150 kΩ/300 kΩ, R2 = 900 kΩ), while the AMP2 was built of 44 unit resistances of W × L = 0.5 µm × 5 µm producing 11 kΩ unit resistance (R1 = 22 kΩ/44 kΩ, R2 = 440 kΩ). The single resistors’ spread value ϬR/R depends on the particular resistors’ value, and is equal to ϬR1/R1 = 0.11%, ϬR2/R2 = 0.49% (amplifier AMP2) and ϬR1/R1 = 0.11%, ϬR2/R2 = 0.19% (amplifier AMP1). Taking into account Equation (2), it results in recording channels voltage gain spread equal to 0.53% (fast signals) and 0.29% (slow signals). It can be seen that the voltage gain spread should be expected low, whereas its main spread contribution comes from the second amplifying stage composed of high poly resistors.

3.2. Lower Corner Frequency

The LCF of the recording channel is defined by the RMR0C0 constant that should be in the range from about 10 s down to 250 ms (considering the 0.1 Hz ÷ 1 kHz LCF tuning range). Assuming that the feedback capacitance C0 is equal to 150 fF, it is necessary to set the RMR0 in the range from 1.6 GΩ up to 10.6 TΩ. It can be seen that even for the highest required LCF, the RMR0 resistance still has to have an extremely high value requiring the use of nonpassive components. A natural alternative here is the MOS-based transistor working as a controllable resistor. Regarding MOS transistors’ effective channel resistance, this depends on a transistors’ operating region, i.e., either strong inversion (SI) or weak inversion (WI), and can be given as follows [35]:

where VGS is the transistors’ gate-source dropout voltage, VTH is the transistors’ threshold voltage, n is a subthreshold slope factor, and β = µCOX (µ—represents carriers mobility, COX is the oxide capacitance per transistor channel area), and ϕT represents thermal voltage equal to 26 mV at room temperature.

There are two more aspects that must be taken into account while choosing the transistors’ proper operating region, i.e., its effective resistance tuning range and resistances’ spread from channel to channel. Thus, considering Equations (3) and (4), one can calculate the MOS channel resistance spread for SI and WI operating modes:

Considering the same transistors’ channel dimensions and that the AVT = 6.6303 mVµm and Aβ = 0.6114%µm for a given process, one would obtain ϬRSI/RSI = 0.14% and ϬRWI/RWI = 3.2% (one should keep in mind that ϬRSI/RSI value is produced for the best transistor operating conditions from the resistance spread point of view, i.e., the VGS is considered to be 1.8 V, whereas lowering the VGS would lead to ϬRSI/RSI getting worse). Moreover, it can be seen that one would get much lower MOS-based effective resistance whenever the transistor operates in the SI. However, assuming the same transistors’ channel dimensioning and that the PMOS transistor is used (higher channels’ effective resistance compared to NMOS transistor), one would need to obtain that to cover given frequency range the transistors’ VGS voltage needs to be changed only by 250 mV. On the other hand, utilizing the SI region, one would need to change the VGS voltage by almost 150 V, which is impossible. Therefore, the most promising way to satisfy the LCF tuning range is to use the WI transistors’ operating region and to compensate for its channel resistance spread from channel to channel through additional correction circuitry.

Finally, taking into account Equation (4), one can write the relation for the LCF of the recording channel:

Next, considering Equation (7) a formula for the LCF channel to channel spread may be given:

The ϬC0/C0 LCF spread contribution may be neglected as for C0 = 150 fF it is equal to 0.034% only. Here, taking into account the LCF control range, the PMOS transistor dimensioning was set to produce Ϭβ/β = 0.14%. Finally, one should expect the LCF spread from channel to channel to equal to 3.2% and this is dominated by the transistors’ threshold voltage spread.

3.3. Upper Corner Frequency

The UCF of the recording channel is different for AP and LFP stages (Table 1) and as formerly explained, it is here defined in the two recording channel blocks separately. Taking into account the AP stage it is set by the front-end amplifier, while the LFP is controlled by the amplifier AMP1 (Figure 1). The UCF is here defined by three factors: open and closed-loop gain (KVOL and KVCL, respectively), and the UCF fUCF_OL of the amplifiers’ working in the open loop gain:

Considering Equation (9), one may write a relation for the UCF spread of the recording channel:

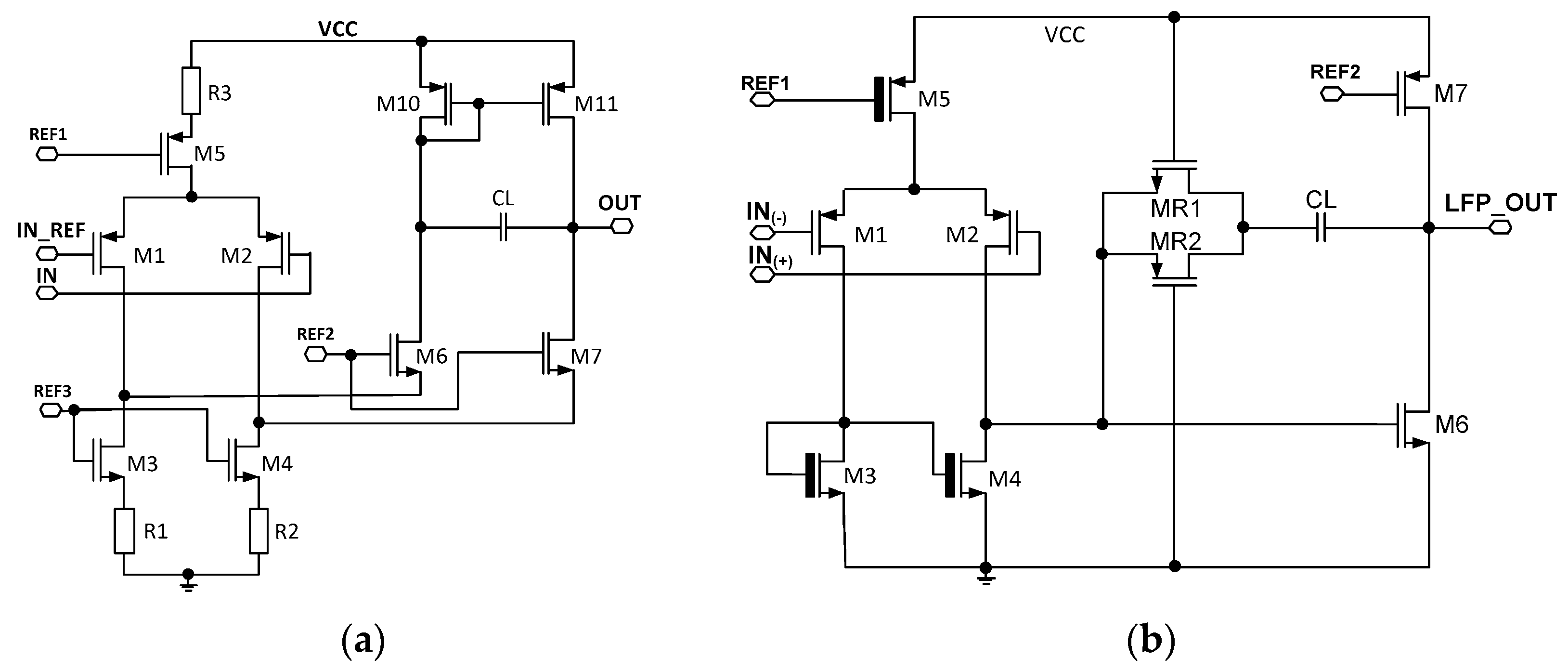

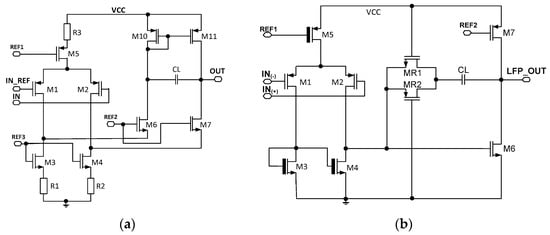

So as to estimate the UCF spread from channel to channel, a detailed analysis amplifiers architecture needs to be performed. In the following project, two core amplifiers are utilized and these work for front-end amplifier and amplifiers AMP1 and AMP2. The core amplifiers are presented in Figure 4. Since the three UCF spread factors analysis (Equation (10)) is very similar in both amplifying stages, only the front-end amplifiers’ UCF uniformity will be analyzed (Figure 4a).

Figure 4.

The schematic idea of the core amplifiers used in (a) front-end amplifier and AMP2, (b) AMP1 amplifier.

Considering the first UCF spread component Equation (10), the open-loop UCF can be given in the following way:

where CL represents amplifiers’ loading capacitance (this is based on the MIM capacitor), and the rOUT is amplifiers’ output resistance (this can be considered as a resistance rds11 as resistance seen from amplifiers output into the M7 transistors drain is a few times higher). The resistance is proportional to the VA (first-order channel length modulation characteristic voltage) and inversely proportional to the M11 transistors’ current [35]:

And

where VE is a technological parameter and la is a characteristic length given by [35]:

Finally, the open-loop gain UCF can be given:

Having this relation, the open-loop amplifiers UCF spread may be evaluated:

For a given process the = 1.8% and the = 3% while the = 0.003%.

Next, the open-loop gain of the front-end amplifier is given by:

where Gm is front-end amplifiers’ effective transconductance.

Here, the open-loop gain spread may be given:

The transistors M11 channel length and its IM11 current were set to 1 µm and 300 nA, respectively. For a given technology, the Ϭβ = 2.81% that resulted in the total drain-source mismatches is equal to 1.8%. Having all the required data and neglecting ϬCL, the open-loop UCF spread is equal to 2.5%. Considering the amplifiers’ transconductance mismatches, it should be kept in mind that this is only the current IM1M2 dependable parameter (input amplifiers’ transistors work in the weak inversion region resulting in Gm = IM1M2/nVT). Therefore, the mismatches originate from the M5 transistors’ current mismatches. Here, for transistors’ M5 W/L = 10 µm/15 µm dimensioning and its current equal to 1.6 µA, the result is Aβ = 2.81%µm, finally producing 0.26% of Gm spread. Having this in mind, the open-loop gain spread is equal to 6.8%. Furthermore, as it was previously shown, the closed-loop voltage gain spread is only 0.245. Ultimately, one should expect Ϭ fUCF/fUCF equal to approximately 7.2%.

4. Stimulating Channel

The electrical stimulation of either current, voltage, or charge impulses is often performed to trigger neuronal activity [36]. This may be required during the neuronal network explorations where, just after a predefined stimulation pattern, the recording is started to check neural network response [37]. Another stimulation application is its use during therapy where only stimulation pulses are generated with no need for recording [38]. Moreover, there are closed-loop implantable systems comprised of both stimulation and recording that are used as prostheses to restore some kinds of disabilities [39,40]. These types of implantable systems are the most complicated, as they need to operate quickly enough to provide proper operation of the controlled function. Therefore, these are comprised not only of recording and stimulation, but are also equipped with on-chip recorded signal classification, data compression, or wireless data transmission [41,42].

Here, it was decided to employ the current stimulation as compared to voltage and charge stimulation, since it is better in terms of impulses controllability, and area occupation. This, however, comes at the expense of higher power consumption.

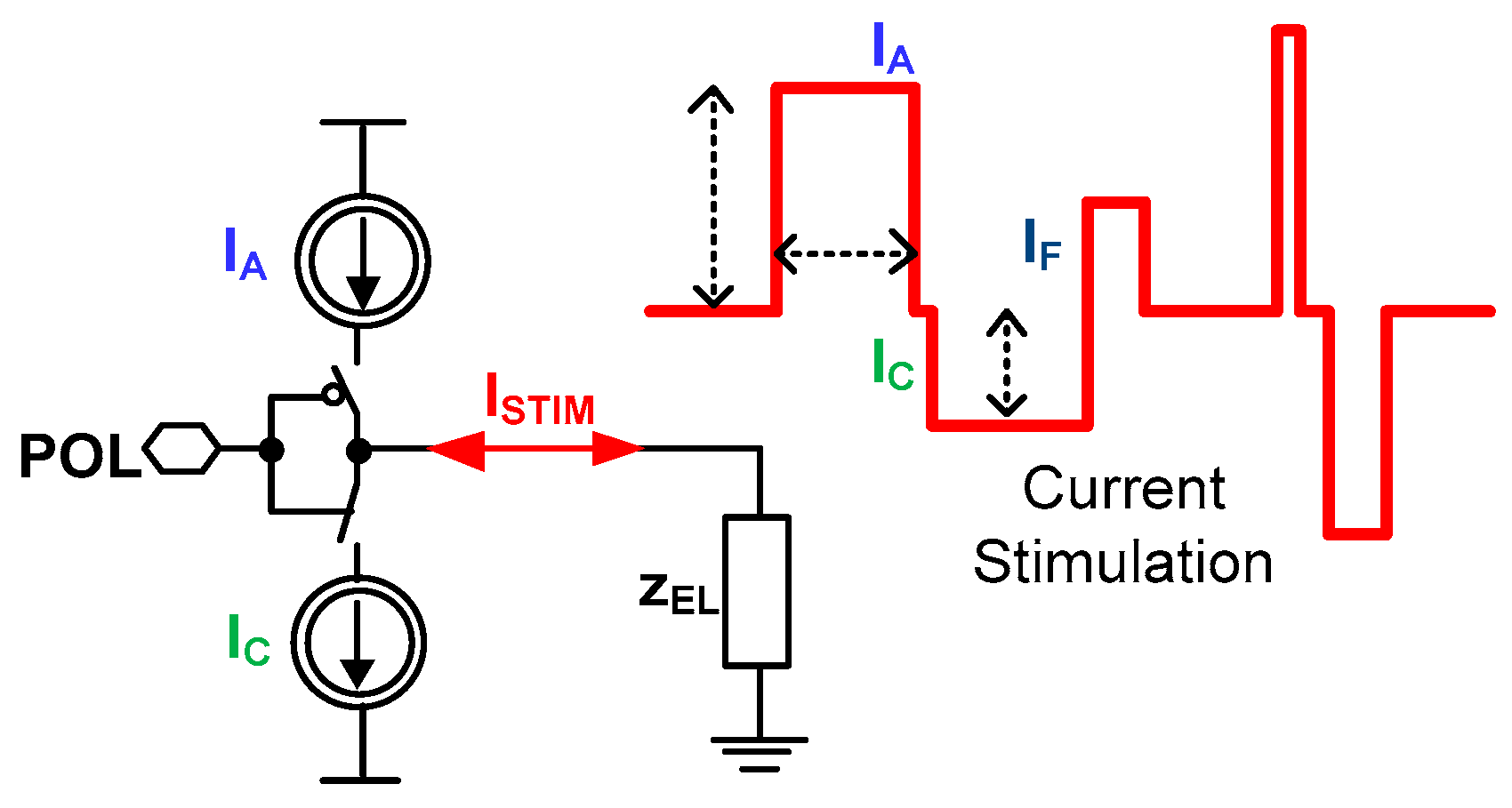

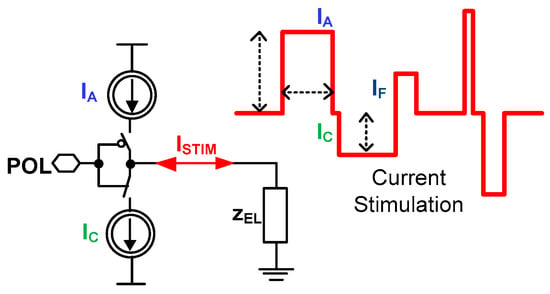

In the simplest stimulation form, there are only a few impulses required to perform effective stimulation (Figure 5). Often during the current stimulation, two types of current pulses are generated one after another, which is motivated by the experiment safety. The first pulse is an anodic current IA that triggers neuronal action, while the second current pulse is a cathodic current IC responsible for extracting charge provided by the anodic pulse. The charge extraction is necessary due to stimulation safety, i.e., any disproportions in these two currents lead to the stimulation electrodes’ built-in potential generation, which finally may be a reason for stimulated neuron death. Another important stimulation aspect is to perform stimulation in a way that allows fast switching from stimulation phase to recording phase not to miss any neural activity already triggered. There are different approaches to minimize that phase switching time [19,43,44,45,46]; however, the most promising one is generating a short current pulse IF just after the stimulation phase [47]. Additionally, there are experiments exploiting different current stimulation patterns to either code the information provided to the neural networks or to make the stimulation more efficient [48]. The most popular current stimulation applications with their main parameters are shown in Table 2.

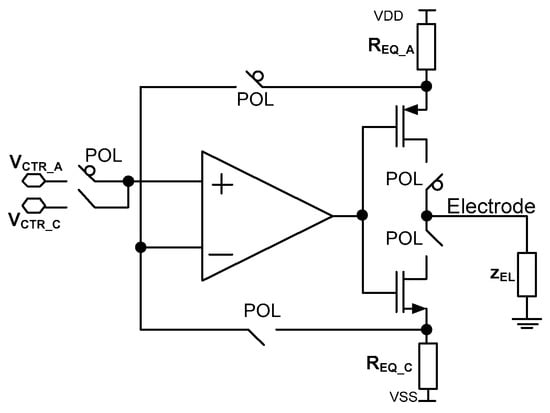

Figure 5.

The conceptual idea of the current stimulator.

Table 2.

Typical current stimulation parameters [49,50,51,52,53].

Bearing all of these in mind, it can be seen that current stimulation should have the possibility of controlling not only IA and IC, but also both the IF current and timing relations of current stimulation particular phases.

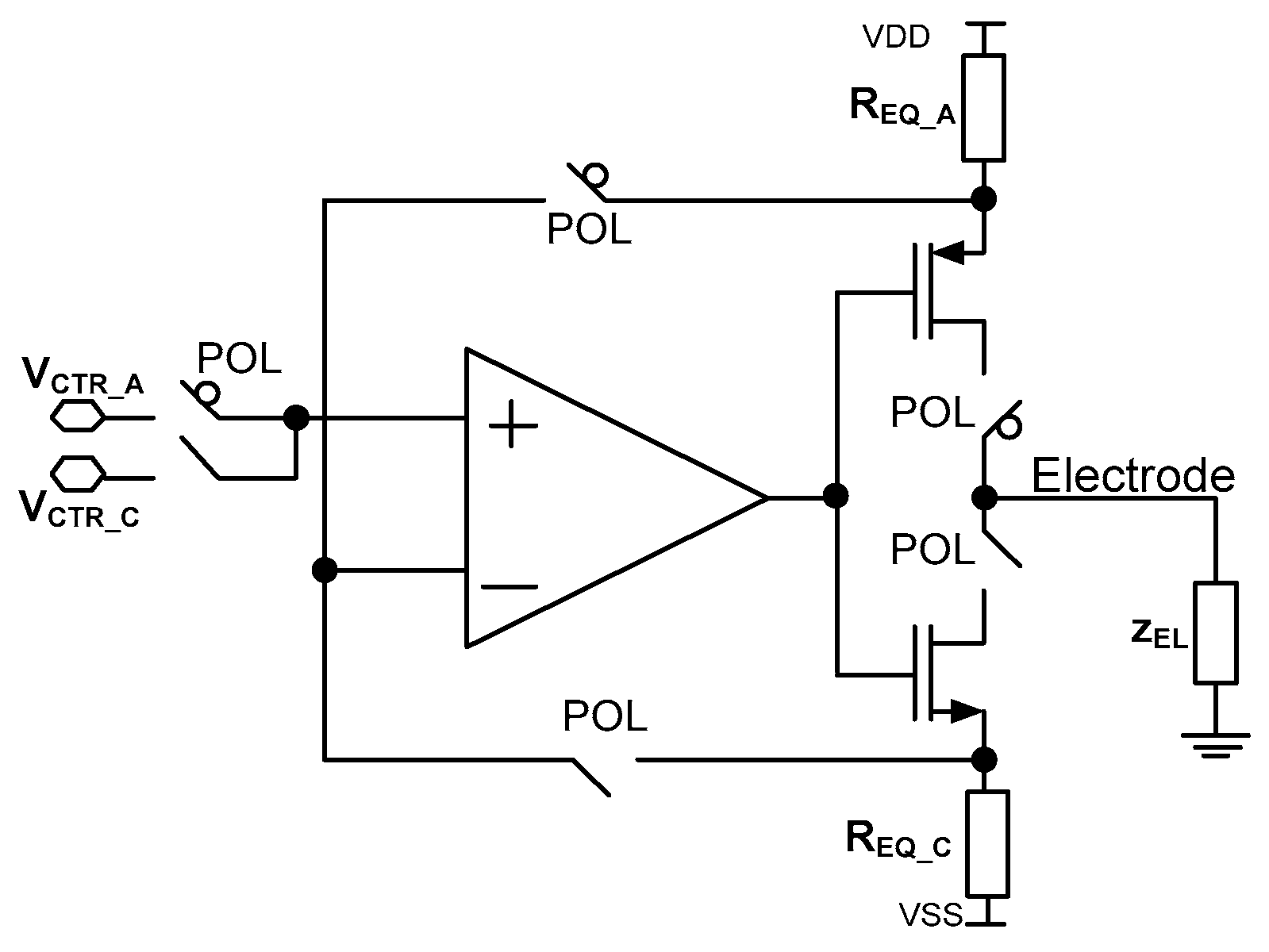

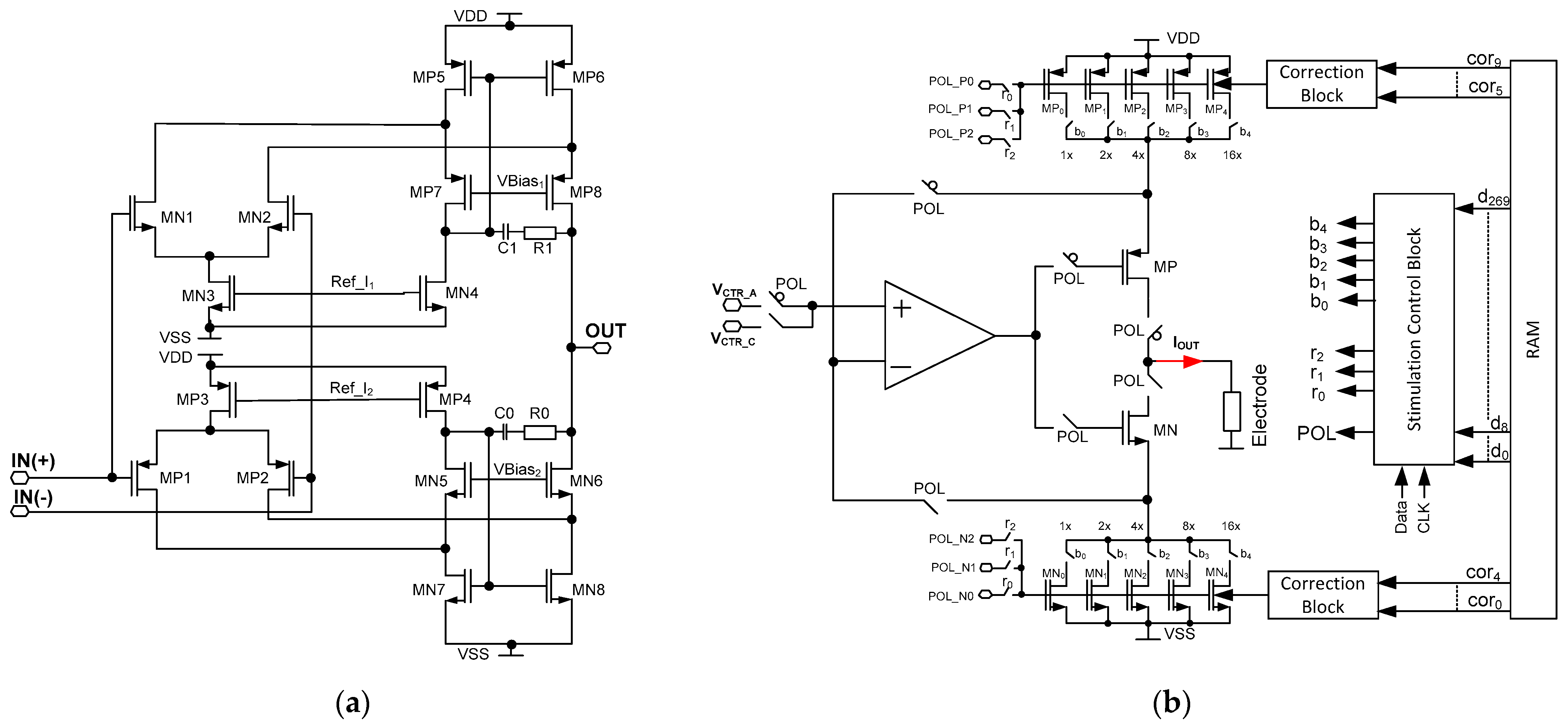

There are many known solutions to the current stimulators’ architectures. The simplest one is based on two current sources composed of complementary PMOS and NMOS transistors. The other architectures exploit current sources’ cascading, capacitor-based memory for opposite stimulation current generation or adiabatic stimulation [48,54,55,56]. Here, a current stimulator architecture is proposed [57], allowing for both precise current control and current stimulation pattern generation for each of the stimulation current channels individually. This functionality is obtained thanks to the in-pixel RAM-supported programmable operational amplifier-based current source. Additionally, to achieve both, lower power consumption, area occupation, and to provide precise cathodic and anodic currents control, it was decided to use an operational amplifier current source (Figure 6).

Figure 6.

Current stimulator schematic idea.

The stimulator idea is based on the proper selection of two parameters, i.e., voltages VCTR_C/VCTR_A and resistances REQ_C/REQ_A, where VCTR_C and VCTR_A are voltages provided to the amplifiers’ input during one of the stimulation phases (cathodic or anodic current generation, respectively, controlled by the POL signal), while REQ_C/REQ_A is equivalent resistance during cathodic/anodic phase (Figure 6). To save power and silicon area, there is only one operational amplifier used that is built of rail-to-rail input stage (Figure 7a).

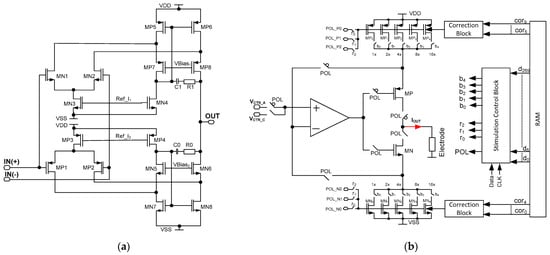

Figure 7.

The schematic idea of the current stimulators’ core amplifier (a) and schematic idea of the programmable current stimulator (b).

Considering the generated stimulation currents IST spread, this depends mainly on two components, i.e., amplifiers voltage offset ϬVCTR/VCTR and resistance REQ spread ϬREQ:

In the given project, the REQ is composed of resistor bank R based on MOS transistors operating in weak inversion. Based on the different requirements of current stimulators (Table 2), it was assumed the current controllability for a given range should be performed with the step at approximately 5%. Therefore, the resistor banks are built of five binary-scaled MOS transistors which result in the current step control of 1/32 resolution. A single MOS based resistance is built of a PMOS or NMOS transistor with channel dimensions of W/L = 2 µm/1 µm or W/L = 1 µm/2 µm respectively. Then, having checked at Equation (19) the unit resistance spread should be approximately 3.2%. Therefore, the overall resistance spread is expected to be √n × 3.2%, where n represents unit resistances connected in parallel. Considering the VCTR voltage spread only, the voltage spread of the amplifier should be taken into account as the VCTR voltage is common for the whole IC. In a given operational amplifier architecture the MP1/MP2 and MN1/MN2 transistor should be taken into account as main voltage offset contributors. Their dimensioning is W/L = 50 µm/0.75 µm (MP1/MP2) or W/L = 4 × 50 µm/0.75 µm (MN1/MN2), and for VCTR = 200 mV, one should expect ϬVCTR/VCTR not higher than 0.4%.

The final stimulation block architecture is shown in Figure 7b. Here, the aim was to both cover different stimulation current ranges with their uniformity being no worse than 5%, and to allow for different stimulation patterns generation. Therefore, besides the resistor bank controllability of 1/32 step, the additional correction that is here used is based on controlling the MOS-based resistor bulks.

The current stimulator is also equipped with a stimulation control block that is a cyclic register, responsible for providing 1 out of 30 RAM stored channel individual settings. These define (Figure 7):

- -

- current range (r0, r1, r2 outputs for selecting POL_P/POL_N voltages);

- -

- current polarity (POL output for selecting either cathodic or anodic current);

- -

- current value (b0 ÷ b4 outputs for defining the REQ resistance value).

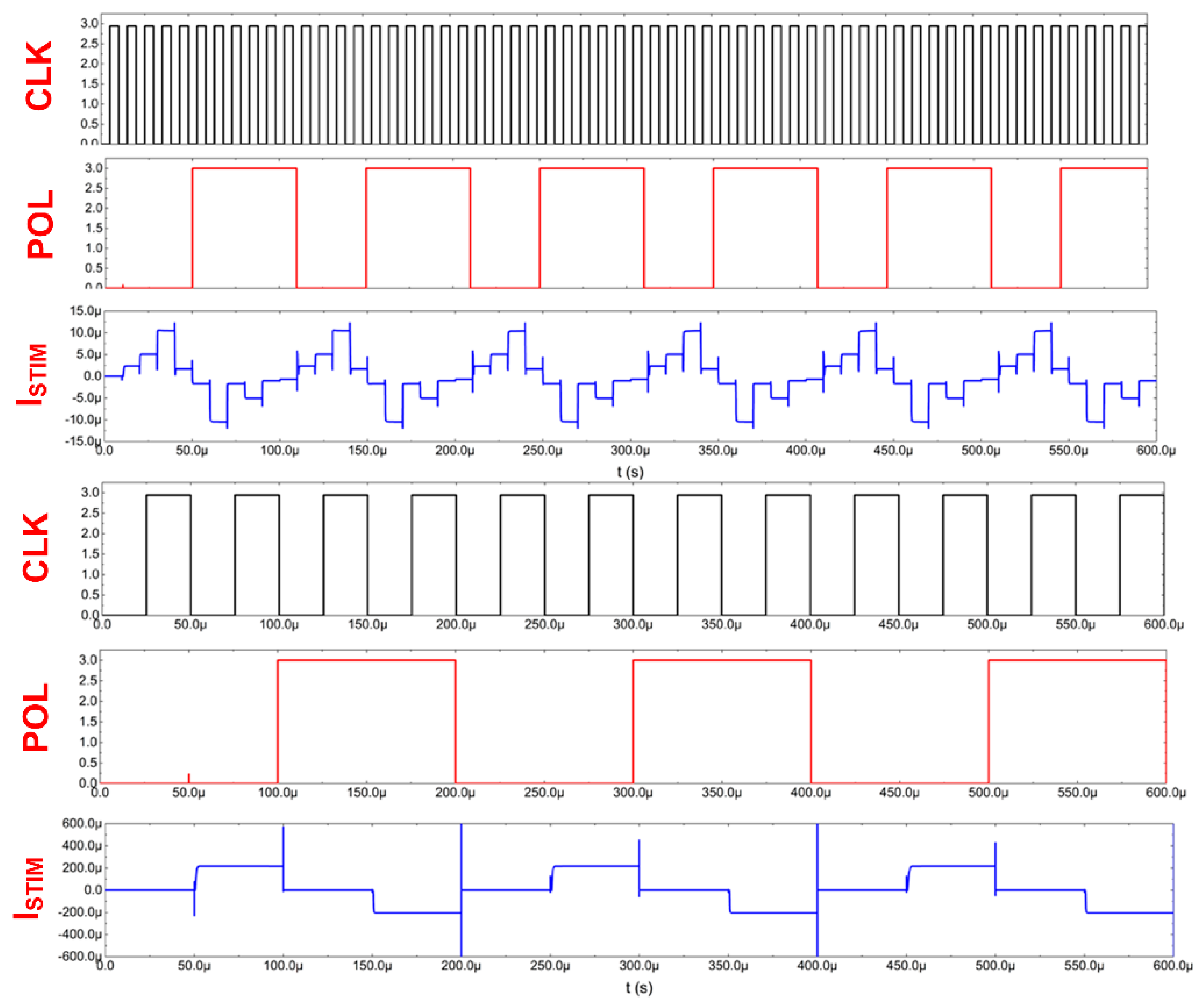

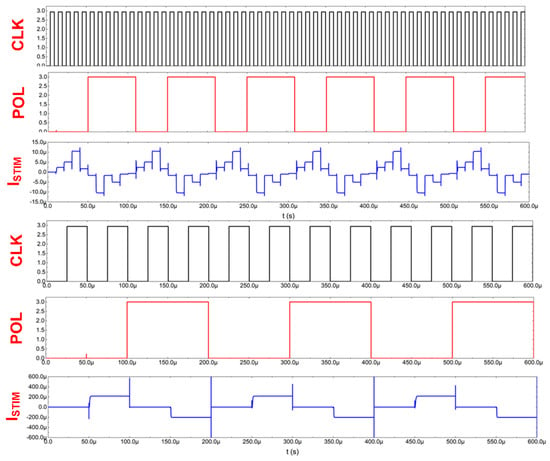

Thanks to the stimulator architecture, it is, therefore, possible to define 30 different stimulating currents that may be individually varied in terms of their timing parameters or current settings, as exemplarily shown in Figure 8.

Figure 8.

Current stimulators’ exemplary signals.

5. Measurement Results

The NRS100 IC is designed in the CMOS 180nm process, occupying an area of 5 × 5 mm2, whereas the single-pixel occupies 400 × 400 µm2. The chip operation was verified by both its main parameters characterization and its application in neurobiological experiments. In total, the three ICs were verified.

The given paper focuses a lot on the IC’s main parameters uniformity that obliges to verify also a measurement systems’ precision. Here, the voltmeter and ammeter were used to measure recording and stimulating blocks, respectively. All measurements were carried out with the use of a LabVIEW environment.

The NRS100 recording channels verification was carried out with the help of the NI-USB 6351 multipurpose card. The voltage measurement accuracy was calculated based on the card datasheet, which is there defined by three uncertainty contributors: gain error, offset error, and noise uncertainty. Considering a voltage range used of ±0.5 V, these are 68 ppm, 17 ppm, and 26 µVRMS, resulting in approximately 0.5 mV absolute accuracy if a noise level of 36 and no averaging are considered. Taking into account that recorded signals are in the range of 100 mV ÷ 400 mV, this directly translates to a measurement error in the range of 0.5% ÷ 0.125%. Regarding the current stimulator verification, it was performed with the use of the Keysight HP34401 multimeter. Here, the current measurement error is defined by 0.005% of reading (4.5/30/400 µA stimulator current ranges) + 0.01% of range (10 mA), resulting in the measurement offset of 1 µA and measurement precision of 0.005%. In general, as shown further in the measurement results, these uncertainties are much lower than the results obtained, and may be omitted.

5.1. NRS100 Main Parameters Characterization

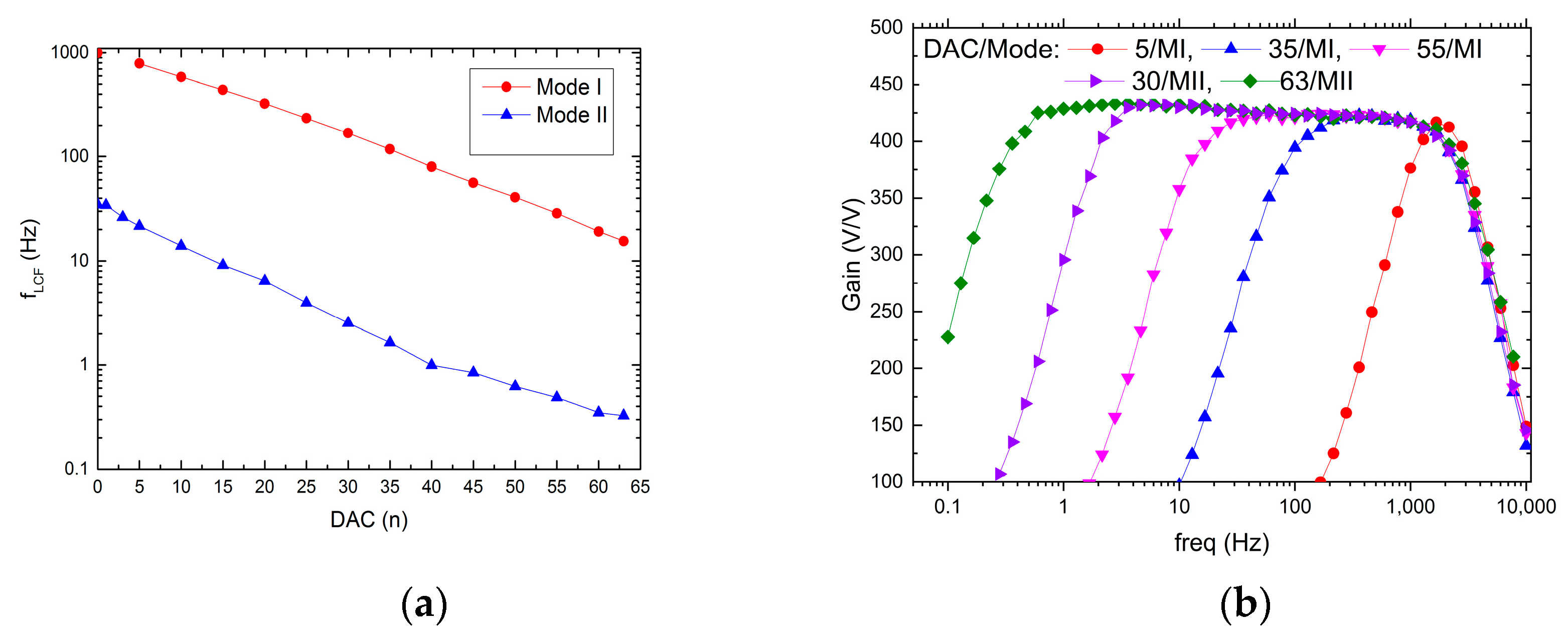

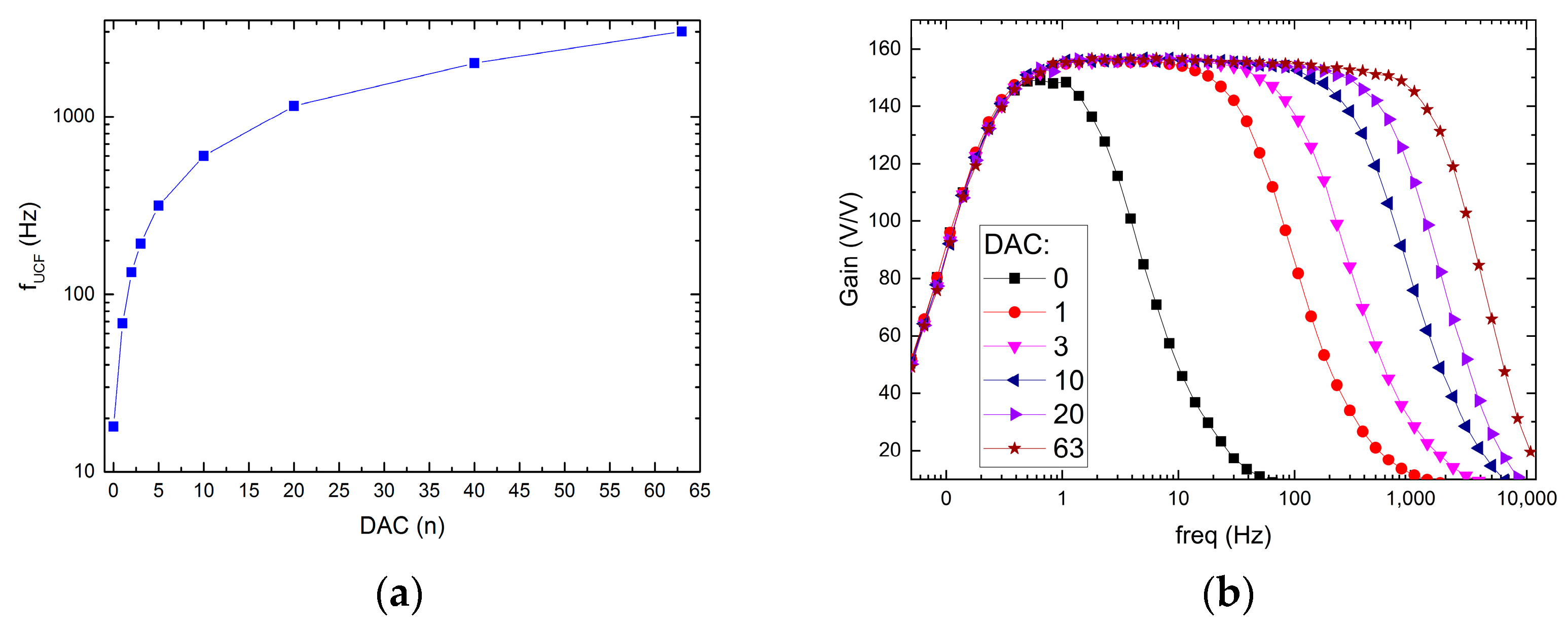

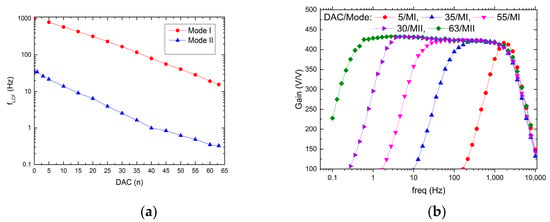

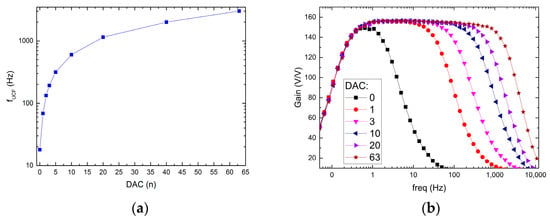

The possible recording channel configurations are shown in Figure 9 and Figure 10. It can be seen that the LCF can be controlled in one of two ranges, i.e., in the 10 Hz ÷ 1 kHz range, or the 300 mHz ÷ 30 Hz range. Importantly, thanks to the fact that the particular pixel is equipped with its 6-bit DAC, the LCF may be tuned individually. The UCF can be controlled globally in the 20 Hz ÷ 3 kHz range. These results show that the thick oxide transistors usage in the second stage of the recording path (AMP1) (see Figure 4b) allowed for the decrease in current supplying the amplifier down to a few pA in each of the recording channels.

Figure 9.

LCF control range (a) and exemplary frequency responses for different DAC settings (b).

Figure 10.

UCF control ranges (a) and exemplary frequency responses for different DAC settings (b).

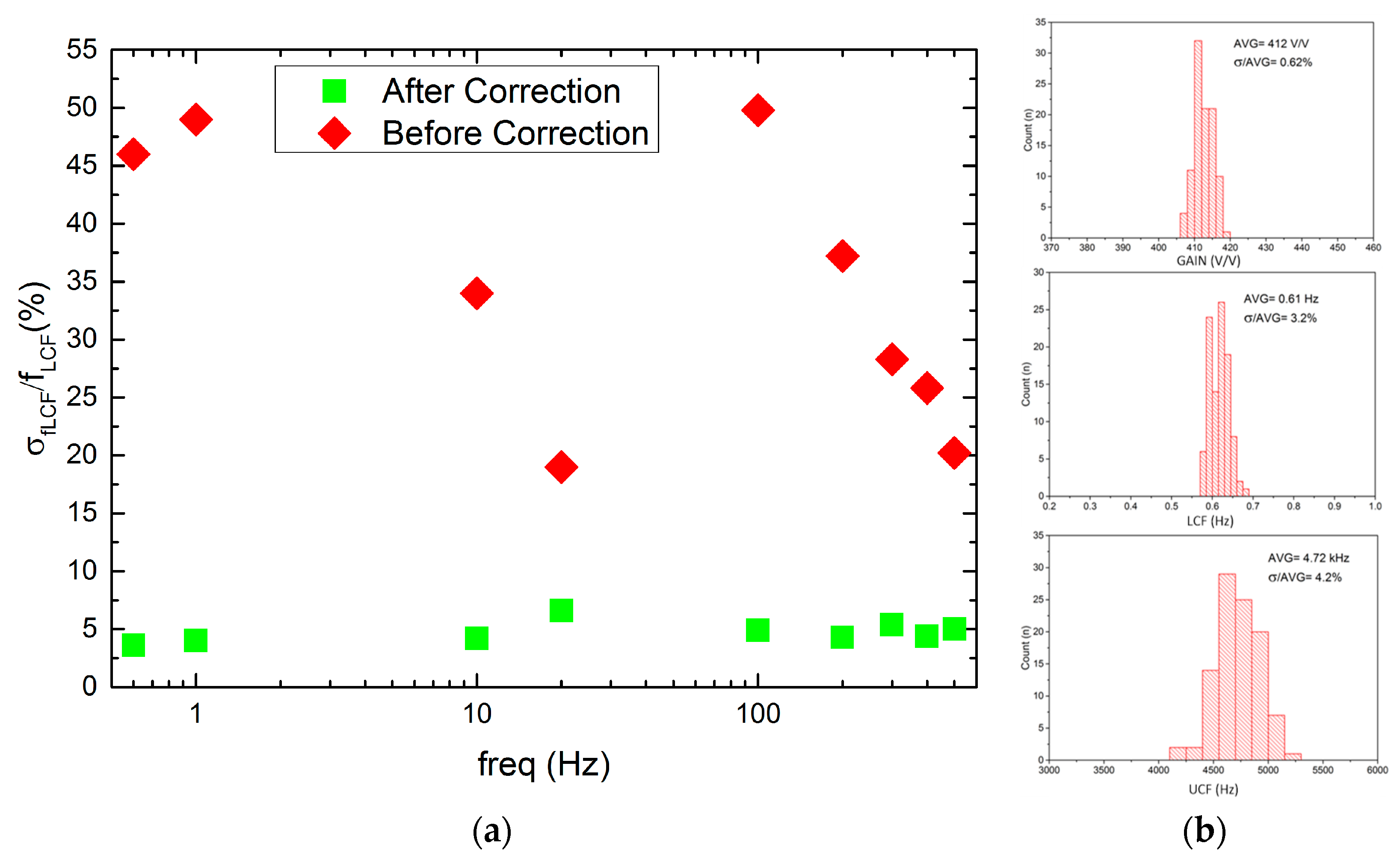

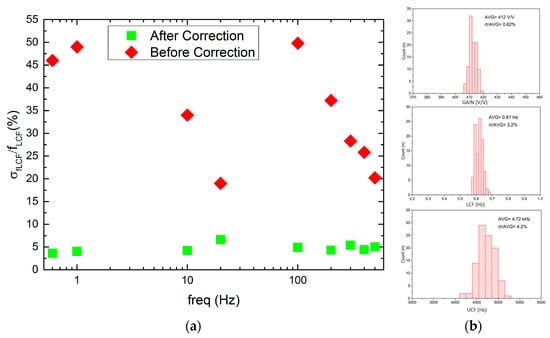

Regarding the LCF uniformity (see Figure 11), it can be seen that it worsens whenever one starts to decrease in LCF, i.e., the ϬfLCF/fLCF for 20 Hz and 600 mHz equals 17% or 45%, respectively. This is a result of LCF controlling DAC which is based on the weighted current mirror. Importantly, the LCF spread may be minimized down to 5% by the individual recording channel correction. The voltage gain and UCF spread are equal to 0.62% and 4.2%, respectively, which is in agreement with former calculations.

Figure 11.

LCF spread from channel to channel before and after correction for a given LCF setting (a) and voltage gain, LCF, and UCF histograms (b).

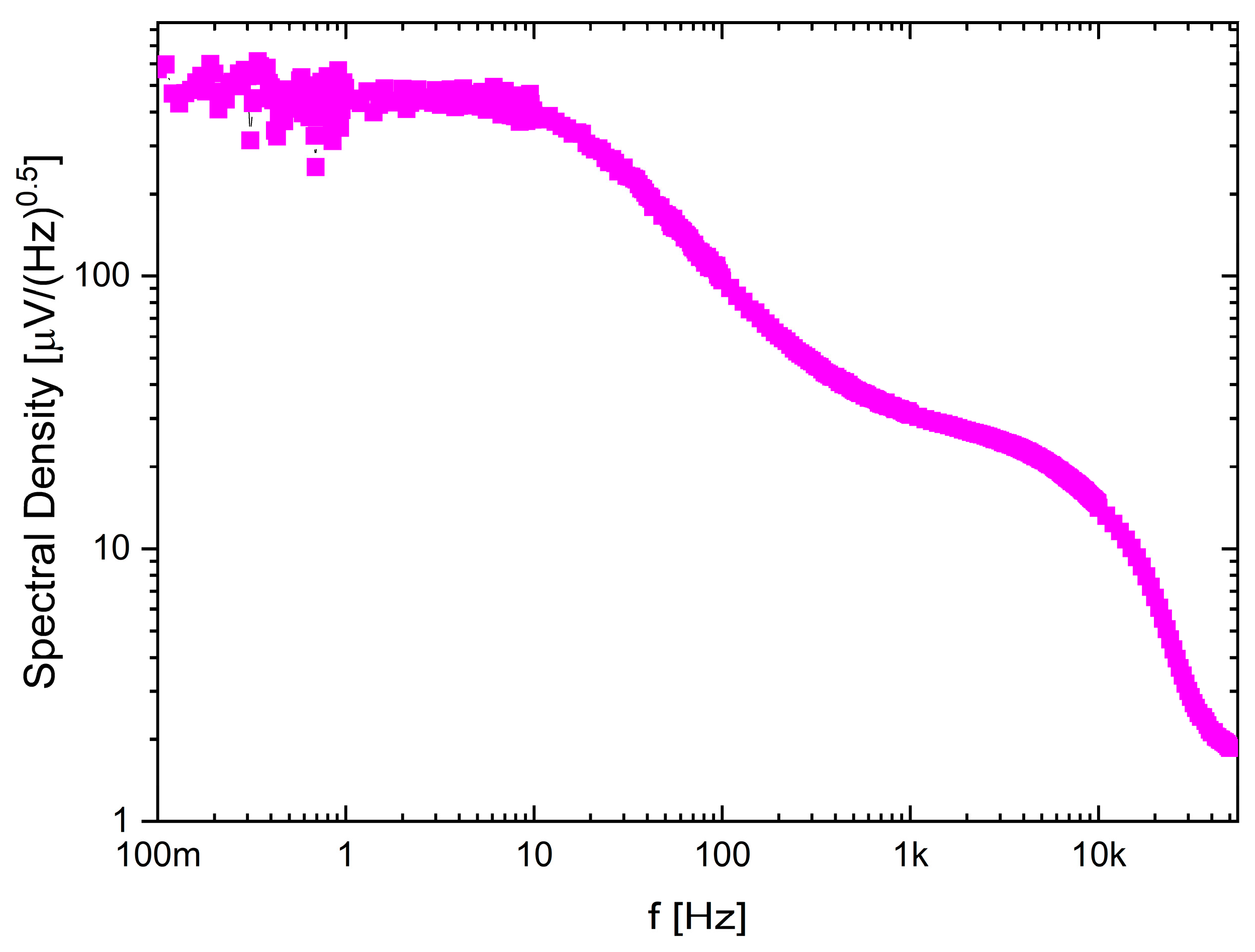

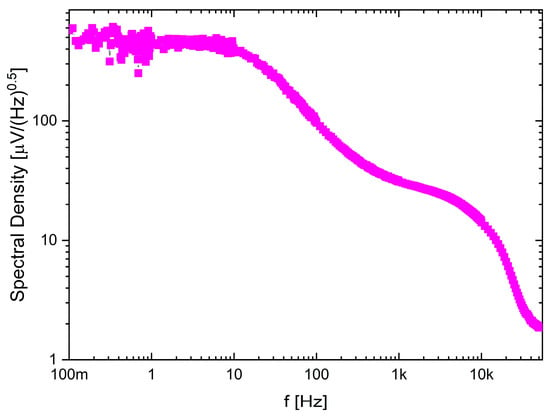

The recording channel noise measurements (see Figure 12) show how the noise characteristic may be shaped by the frequency bandwidth selection. Here, the LCF was set to approximately 10 Hz, while the UCF to 4.7 kHz and it can be seen that the 1/f noise is mitigated below LCF.

Figure 12.

Noise spectral density for one of the selected recording channel settings.

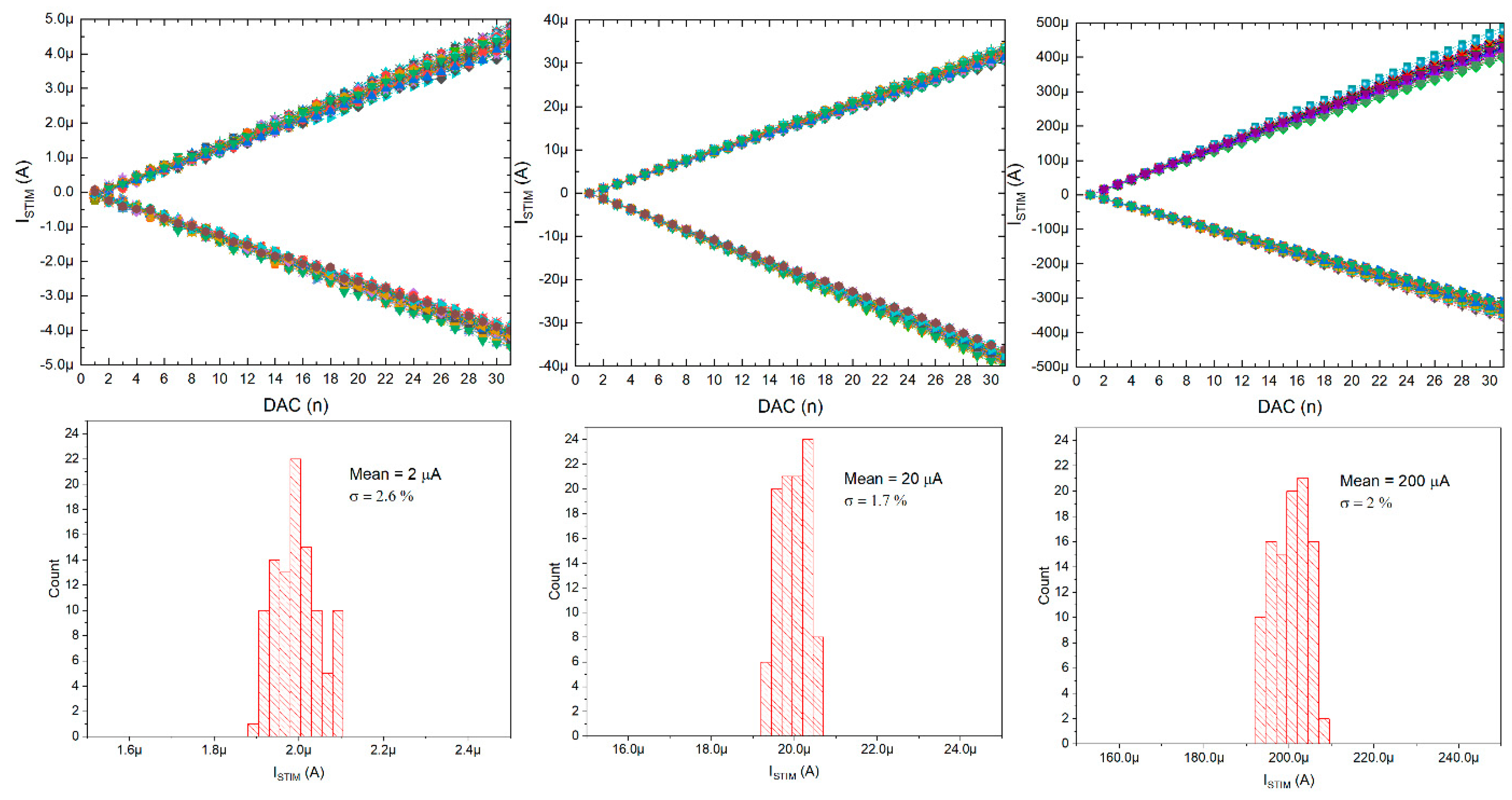

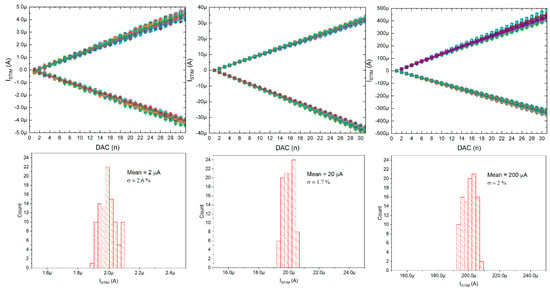

The current stimulators were also verified (only static verification was conducted, these were not used during the neurobiological experiments), and it can be seen that the stimulating currents can be controlled with 32 equal steps in three different current ranges: 0 ÷ ±5 µA, 0 ÷ ±25 µA, and 0 ÷ ±450 µA (see Figure 13). These current ranges can be changed individually, as the POL_N/POL_P voltages are globally controlled by six 6-bit DACs located below the chip matrix. Noticeably, thanks to the in-pixel individual correction, the uniformity of the stimulating current can be as low as 2.6%.

Figure 13.

Current stimulators’ particular current ranges controlling range with inset pictures of histograms for particulars’ current correction (all 100 stimulation channels are here given).

The chip was also verified in terms of other parameters that are listed in the comparison Table 3. The author intended to compare his work to those designs that are fabricated in similar process nodes (i.e., 180 nm or 130 nm) to show that even such an old process may allow for developing ASIC with a large functionality and good performance. Only those designs with multichannel architecture and being comprised of recording and stimulation were taken into account. It can be seen that the NRS100, compared to other designs, is very attractive in terms of its main parameters broad and precise tuning ability, i.e., both corner frequencies, as well as stimulating currents. Importantly, even the single-pixel functionality is expanded, compared to other designs; it occupies a low area, and thanks to its architecture main parameters spread from channel to channel are significantly mitigated. The stimulating current programmability, recording channels power consumption of 12 µW, input-referred noise of 8.5 µVRMS, and individual main parameter correction make the proposed chip a good candidate for a variety of neurobiological experiments.

Table 3.

Performance summary and comparison table.

5.2. Neurobiological Experiments

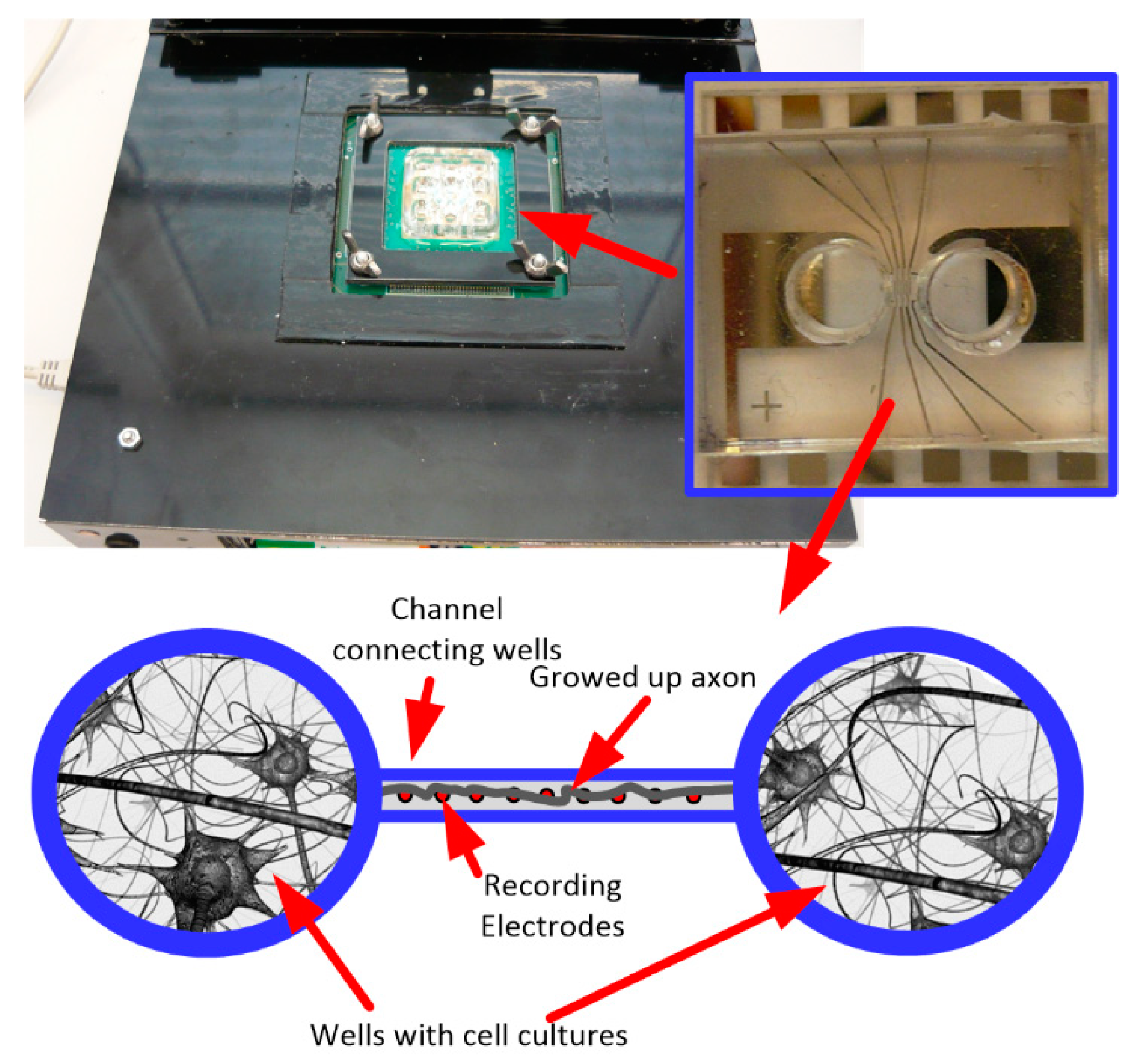

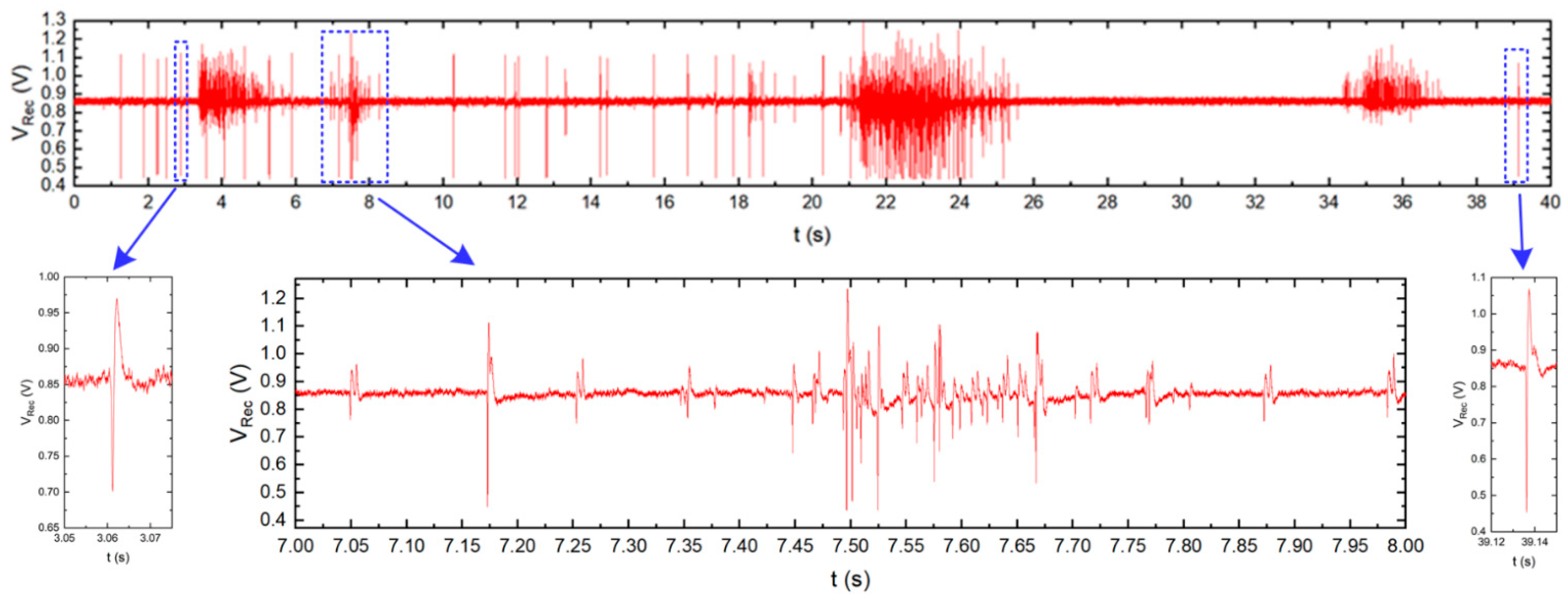

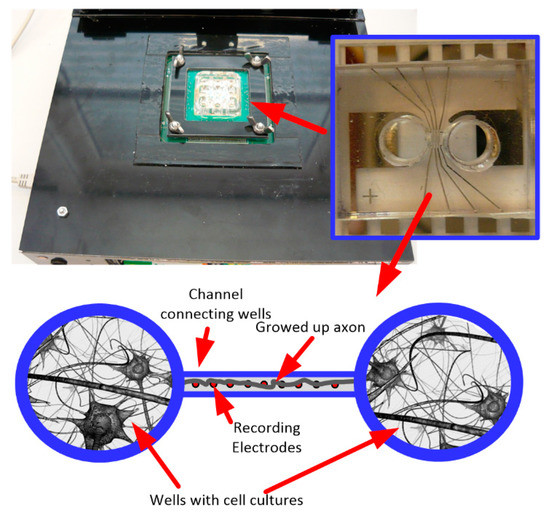

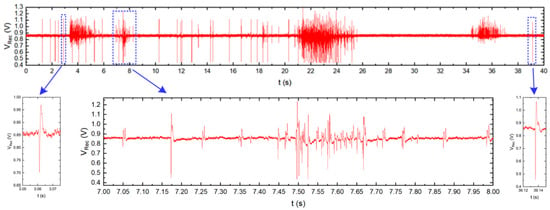

The presented IC was also used in the neurobiological experiment performed in collaboration with Qwane Biosciences SA, Lausanne, Switzerland, that conducted extensive research under the NEUROACT project [58] The idea of this experiment was to produce a first feasibility study of the measure of neuronal signals propagation speed along isolated axons. The motivation of this experiment was to find a way that allows studying the propagation characteristics of neuronal signals along axons, as the impairment of axonal propagation is often a consequence of neurodegenerative diseases. This approach could lead to a platform for drug screening applications whereby neuronal protection or recovery could be monitored by the propagation speed along the axons. Therefore, to perform this experiment, the 256 channel in-vitro recording platform [59] was adapted to a specially developed Micro-Electrode Array (MEA) device (see Figure 14)—the few pixels were combined with existing recording electrodes, and the exemplary recordings are presented. The MEA is composed of two small culture wells measuring 3 mm in diameter, connected by a microchannel (10 µm wide, 3 µm high, and 1 mm long), allowing only neuronal axons to cross it. The recording electrodes (10 µm × 50 µm) are located at equidistant positions along the microchannel and not in the culture chambers as they typically are in MEA devices. The experiment may be started just after the neurons establish their well-to-well connection with the axon, which takes approximately 10–14 days [60,61]. The Figure 15 shows the neurobiological signals recorded during this experiment. Compared to standard MEA devices, obtained single spike amplitudes are much larger in our chip configuration (up to 700 µV instead of typical 50 µV ÷ 100 µV), which is due to the small volume of the microchannel in which the axons are located. As can be seen in the recording, different signal amplitudes are recorded during the experiment. These different signals correspond to different individual axons crossing the microchannel.

Figure 14.

The photo of the 256 channel in-vitro recording platform with inset pictures of the specially developed multielectrode arrays used in the experiment, and figurative experiment description.

Figure 15.

Typical neurobiological signals recorded by the chip presented. Top: signal recorded by one electrode located inside the microchannel. Bottom: enlarged single action potentials (left and right) and burst activity (center). In the burst, several signals from different axons grown through the microchannel can be distinguished due to different signal amplitudes and signal shapes.

The comparison of the signals recorded at the different electrodes, i.e., at both ends of the microchannel, allows for the definition of the time of signal propagation through the microchannel, and the calculation of the propagation speed of the spikes along the axons.

6. Conclusions

In this paper, the design, measurement, and experiment results of the NRS100 chip are presented. The proposed architecture composed of both recording and stimulating functionalities supported by blocks responsible for main parameters correction, configuration, and programmability proves it may be highly efficient in a variety of biomedical experiments. Particular channels’ components spread influence is shown that allows one to define limits in area minimization of such systems.

It can be seen that, thanks to the different techniques employed in the presented design, it was feasible to develop a chip that has both a large functionality (ability to record different neurobiological signals, broad and precise multichannel programmable current stimulation) and good performance (i.e., low power consumption, small area occupation, low input-referred noise, low channel-to-channel parameters spread). These techniques are mainly:

- -

- recording channels’ architecture (two followed stages with individual gain and bandwidth control);

- -

- stimulating channels’ architecture (anodic/cathodic single based amplifier current source individually controlled);

- -

- correction circuitry (in-pixel local DACs supported by global DACs located out-of-the pixel matrix, in-pixel RAM).

However, whenever more than hundreds of channels are required, the ASIC would need to be equipped with data compression, and therefore modern processes would need to be used. However, presented approaches could also be used.

Funding

The presented work has been supported by the National Science Center, Poland under Contract No. UMO-2016/23/D/ST7/00488.

Acknowledgments

The presented work has been supported by the National Science Center, Poland under Contract No. UMO-2016/23/D/ST7/00488. Thibault Francfort and Marc Heuschkel from Qwane Biosciences SA, Lausanne, Switzerland, are acknowledged for neurobiological experiments arrangement and their further data analysis. M. Żoladz from AGH UST, Poland, is acknowledged for support during the neurobiological experiment.

Conflicts of Interest

The authors declare no conflict of interest.

References

- Narayan, R. Encyclopedia of Biomedical Engineering; Elsevier: Amsterdam, The Netherlands, September 2018. [Google Scholar]

- Saltzman, W.M. Biomedical Engineering: Bridging Medicine and Technology; Cambridge University Press: Cambridge, UK, 2015. [Google Scholar]

- Fischer, A.C.; Forsberg, F.; Lapisa, M.; Bleiker, S.J.; Stemme, G.; Roxhed, N.; Niklaus, F. Integrating MEMS and ICs. Microsyst. Nanoeng. 2015, 1, 15005. [Google Scholar] [CrossRef]

- Shin, H.; Jeong, S.; Lee, J.H.; Sun, W.; Choi, N.; Cho, I.J. 3D high density microelectrode array with optical stimulation and drug delivery for investigating neural circuits dynamics. Nat. Commun. 2021, 12, 492. [Google Scholar] [CrossRef] [PubMed]

- Hochberg, L.R.; Bacher, D.; Jarosiewicz, B.; Masse, N.Y.; Simeral, J.D.; Vogel, J.; Haddadin, S.; Lieu, J.; Cash, S.S.; Smagt, P.; et al. Reach and grasp by people with tetraplegia using a neurally controlled robotic arm. Nature 2012, 485, 372–375. [Google Scholar] [CrossRef] [PubMed]

- Johns Hopkins Applied Physics Laboratory. In a First, Patient Controls Two Prosthetic Arms with His Thoughts. Available online: https://www.jhuapl.edu/PressRelease/191016 (accessed on 25 October 2020).

- Lozano, A.M.; Lipsam, N.; Bergman, H.; Brown, P.; Chabardes, S.; Chang, J.W.; Matthews, K.; Mcintyre, C.C.; Schaepfler, T.E.; Schulder, M.; et al. Deep brain stimulation: Current challenges and future directions. Nat. Rev. Neurol. 2019, 15, 148–160. [Google Scholar] [CrossRef] [PubMed]

- Lenarz, T. Cochlear implant—State of the art. GMS Curr. Top. Otorhinolaryngol. Head Neck Surg. 2018, 16, Doc04. [Google Scholar] [CrossRef]

- Bullmann, T.; Radivojevic, M.; Huber, S.T.; Deligkaris, K.; Hierlemann, A.; Frey, U. Large-scale mapping of axonal arbors using high-density microelectrode arrays. Front. Cell. Neurosci. 2019, 13, 404. [Google Scholar] [CrossRef]

- Lee, T.; Je, M. Multimodal Neural Interface Circuits for Diverse Interaction With Neuronall Cell Population in Human Brain. IEEE Trans. Circuits Syst. II Express Briefs 2021, 68, 574–580. [Google Scholar] [CrossRef]

- Denison, T.; Morris, M.; Sun, F. Building a bionic nervous system. IEEE Spectr. 2015, 52, 32–39. [Google Scholar] [CrossRef]

- Delyfer, M.-N.; Gaucher, D.; Govare, M.; Cougnard-Gregoire, A.; Korobelnik, J.F.; Ajana, S.; Mohand-Said, S.; Ayello-Scheer, S.; Rozaiguia-Studer, F.; Dollfus, H.; et al. Adapted Surgical Procedure for Argus II Retinal Implantation: Feasibility, Safety, Efficiency, and Postoperative Anatomic Findings. Ophthalamol. Retin. 2018, 2, 276–287. [Google Scholar] [CrossRef]

- Lopez, C.M.; Andrei, A.; Miltra, S.; Welkenhuysen, M.; Eberle, W.; Bartic, C.; Puers, R.; Yazicioglu, R.F. An Implantable 455-Active-Electrode 52-Channel CMOS Neural Probe. IEEE Int. Solid-State Circuits Conf. 2013, 49, 248–261. [Google Scholar] [CrossRef]

- Buzsaki, G.; Stark, E.; Berenyi, A.; Khodholy, D.; Kipke, D.R.; Yoon, E.; Wise, K. Tools for probing local circuits: High-density silicon probes combined with optogenetics. Neuron 2015, 86, 92–105. [Google Scholar] [CrossRef] [PubMed]

- Lopez, C.M.; Putzeys, J.; Raducanu, B.C.; Ballini, M.; Wang, S.; Andrei, A.; Rochus, V.; Vadebriel, R.; Severi, S.; van Hoof, C.; et al. A Neural Probe with Up to 966 Electrodes and Up to 384 Configurable Channels in 0.13 µm SOI CMOS. IEEE Trans. Biomed. Circuits Syst. 2017, 11, 510–522. [Google Scholar] [CrossRef] [PubMed]

- Ng, K.A.; Greenwald, E.; Xu, Y.P.; Thakor, N.V. Implantable neurotechnologies: A review of integrated circuit amplifiers. Med Biol. Eng. Comput. 2016, 54, 45–62. [Google Scholar] [CrossRef] [PubMed]

- Davis, W.R.; Wilson, J.; Mick, S.; Xu, J.; Hua, H.; Mineo, C.; Sule, A.M.; Steer, M.; Franzon, P.D. Demystifying 3D ICs: The pros and cons on going vertical. IEEE Des. Test. Comput. 2005, 22, 498–510. [Google Scholar] [CrossRef]

- Chang, C.W.; Chou, L.C.; Huang, P.T.; Wu, S.L.; Lee, W.W.; Chuang, C.T.; Chen, K.N.; Hwang, W.; Chen, K.H.; Chiu, C.T.; et al. A double-sided, single-chip integration scheme using through-silicon-via for neural sensing applications. Biomed. Microdevices 2015, 17, 11. [Google Scholar] [CrossRef]

- Brown, A.; Ross, J.D.; Blum, R.A.; Nam, Y.; Wheeler, B.C.; DeWeerth, S.P. Stimulus-artifact elimination in a multi-electrode system. IEEE Trans. Biomed. Circuits Syst. 2008, 2, 10–21. [Google Scholar] [CrossRef]

- Bagheri, A.; Salam, M.T.; Velasquez, J.L.P.; Genov, R. Low-Frequency Noise and Offset Rejection in DC-Coupled Neural Amplifiers: A Review and Digitally-Assisted Design Tutorial. IEEE Trans. Biomed. Circuits Syst. 2016, 11, 161–176. [Google Scholar] [CrossRef] [PubMed]

- Kmon, P.; Grybos, P. Energy Efficient Low-Noise Multichannel Neural Amplifier in Submicron CMOS Process. IEEE Trans. Circuits Syst. –I 2013, 60, 1764–1775. [Google Scholar] [CrossRef]

- Kmon, P. Noise Minimization Limits in Multichannel Integrated Circuits Dedicated to Neurobiology Experiments. Microelectron. J. 2016, 51, 67–74. [Google Scholar] [CrossRef]

- Żołądź, M.; Kmon, P.; Rauza, J.; Gryboś, P.; Blasiak, T. Multichannel Neural Recording System Based on Family ASICs Processed in Submicron Technology. Microelectron. J. 2014, 45, 1226–1231. [Google Scholar] [CrossRef]

- Kmon, P.; Gryboś, P.; Zoladz, M.; Lisicka, A. Fast and Effective Method of CMRR Enhancement For Multichannel Integrated Circuits Dedicated to Biomedical Measurements. Electron. Lett. 2015, 51, 1736–1738. [Google Scholar] [CrossRef]

- Deptuch, G.W.; Fahim, F.; Grybos, P.; Hoff, J.; Holm, S.; Maj, P.; Siddons, D.P.; Trimpl, M.; Zimmerman, T. An algorithm of an X-ray hit allocation to a single pixel in a cluster and its test-circuit implementation. IEEE Trans. Circuits Syst. –I 2017, 65, 185–197. [Google Scholar] [CrossRef]

- Kmon, P.; Deptuch, G.; Fahim, F.; Gryboś, P.; Maj, P.; Szczygieł, R.; Zimmerman, T. Active feedback with leakage current compensation for charge sensitive amplifier used in hybrid pixel detector. IEEE Trans. Nucl. Sci. 2019, 66, 664–673. [Google Scholar] [CrossRef]

- Samiei, A.; Hashemi, H. A Bidirectional Neural Interface SoC with Adaptive IIR Stimulation Artifact Cancelers. IEEE J. Solid-State Circuits 2021, 56, 2142–2157. [Google Scholar] [CrossRef]

- Rezaei, M.; Maghsoudloo, E.; Bories, C.; de Koninck, Y.; Gosselin, B. A low-power current-reuse analog front-end for high-density Neural Recording Implants. IEEE Trans. Biomed. Syst. Circuits 2018, 12, 271–280. [Google Scholar] [CrossRef] [PubMed]

- Ballini, M.; Muller, J.; Livi, P.; Chen, Y.; Frey, U.; Stettler, A.; Shadmani, A.; Viswam, V.; Jones, I.L.; Jackel, D.; et al. A 1024-channel CMOS microelectrode array with 26,400 electrodes for recording and stimulation of electrogenic cells in vitro. IEEE J. Solid-State Circuits 2014, 49, 2705–2719. [Google Scholar] [CrossRef] [PubMed]

- Chen, W.-M.; Chiueh, H.; Chen, T.-J.; Ho, C.-L.; Jeng, C.; Ker, M.-D.; Lin, C.-Y.; Huang, Y.-C.; Chou, C.-W.; Fan, T.-Y. A fully integrated 8-channel closed-loop neural prosthetic SoC for real-time epileptic seizure control. IEEE J. Solid-State Circuits 2014, 49, 232–247. [Google Scholar] [CrossRef]

- Muller, R.; Gambini, S.; Rabaey, J.M. A 0.013 mm 25 μW DCcoupled neural signal acquisition IC with 0.5 V supply. Proc. IEEE Solid-State Circuits Conf. 2011, 47, 232–243. [Google Scholar] [CrossRef]

- Kassiri, H.; Salam, M.T.; Pazhouhandeh, M.R.; Soltani, N.; Velasquez, J.L.P.; Carlen, P.; Genov, R. Rail-to-Rail-Input Dual-Radio 64-Channel Closed-Loop Neurostimulator. IEEE J. Solid State Circuits 2017, 52, 2793–2810. [Google Scholar] [CrossRef]

- Greenwald, E.; So, E.; Wang, Q.; Mollazadeh, M.; Maier, C.; Etienne-Cummings, R.; Cauwenberghs, G.; Thakor, N. A bidirectional neural interface IC with chopper stabilized BioADC array and charge balanced stimulator. IEEE Trans. Biomed. Circuits Syst. 2016, 10, 990–1002. [Google Scholar] [CrossRef] [PubMed]

- Harrison, R.R.; Charles, C. A low-power low-noise CMOS amplifier for neural recording applications. IEEE J. Solid-State Circuits 2003, 38, 958–965. [Google Scholar] [CrossRef]

- Tsividis, Y. Operation and Modelling of the MOS Transistor; Oxford University Press: Oxford, UK, 2003. [Google Scholar]

- Simpson, J.; Ghovanloo, M. An Experimental Study of Voltage, Current, and Charge Controlled Stimulation Front-End Circuitry. In Proceedings of the IEEE International Symposium on Circuits and Systems, New Orleans, LA, USA, 27–30 May 2007. [Google Scholar]

- Gilja, V.; Chestek, C.A.; Diester, I.; Henderson, J.M.; Deisseroth, K.; Shenoy, K.V. Challenges and opportunities for next-generation intracortically based neural prostheses. IEEE Trans. Biomed. Eng. 2011, 58, 1891–1899. [Google Scholar] [CrossRef] [PubMed]

- Michael, J.F.; Samanta, J.; Moustafa, A.A.; Sherman, S.J. Hold your horses: Impulsivity, deep brain stimulation, and medication in Parkinsonism. Science 2007, 318, 1309–1312. [Google Scholar]

- Luo, Y.H.L.; da Cruz, L. The Argus II Retinal Prosthesis System. Prog. Retin. Eye Res. 2016, 50, 89–107. [Google Scholar] [CrossRef]

- Collinger, J.L.; Wodlinger, B.; Downey, J.E.; Wang, W.; Tyler-Kabara, E.C.; Weber, D.J.; McMorland, A.J.C.; Velliste, M.; Boninger, M.L.; Schwartz, A.B. High-performance neuroprosthetic control by an individual with tetraplegia. Lancet 2013, 381, 557–564. [Google Scholar] [CrossRef]

- Liu, Y.; Urso, A.; da Ponte, R.M.; Costa, T.; Valente, V.; Giagka, V.; Serdijn, W.A.; Constandinou, T.G.; Denison, T. Bidirectional Bioelectronic Interfaces: System Design and Circuit Implications. IEEE Solid State Circuits Mag. 2020, 12, 30–46. [Google Scholar] [CrossRef]

- Stanslaski, S.; Herron, J.; Chouinard, T.; Bourget, D.; Isaacson, B.; Kremen, V.; Opri, E.; Drew, W.; Brinkman, B.H.; Gunduz, A.; et al. A chronically-implanted neural coprocessor for exploring treatments for neurological disorders. IEEE Trans. Biomed. Circuits Syst. 2018, 12, 1230–1245. [Google Scholar] [CrossRef]

- Gnadt, J.W.; Echols, S.D.; Yildrim, A.; Zhang, H.; Paul, K. Spectral cancellation of microstimulation artifact for simultaneous neural recording in situ. IEEE Trans. Biomed. Eng. 2003, 50, 1129–1135. [Google Scholar] [CrossRef] [PubMed]

- Frey, U.; Sedivy, J.; Heer, F.; Pedron, R.; Ballini, M.; Mueller, J.; Bakkum, D.; Hafizovic, S.; Faraci, F.D.; Greve, F.; et al. Switch-matrix-based high-density microelectrode array in CMOS technology. IEEE J. Solid-State Circuits 2010, 45, 467–482. [Google Scholar] [CrossRef]

- Jimbo, Y.; Kasai, N.; Torimitsu, K.; Tateno, T.; Robinson, H.P.C. A system for MEA-based multisite stimulation. IEEE Trans. Biomed. Eng. 2003, 50, 241–248. [Google Scholar] [CrossRef] [PubMed]

- Kadlubowski, L.; Kmon, P. Analysis of circuits for effective stimulation in neurobiological experiments. Electr. Rev. 2016, 11. [Google Scholar] [CrossRef]

- Hottowy, P.; Skoczeń, A.; Gunning, D.E.; Kachiguine, S.; Mathieson, K.; Sher, A.; Wiącek, P.; Litke, A.M.; Dąbrowski, W. Properties and application of a multichannel integrated circuit for low-artifact, patterned electrical stimulation of neural tissue. J. Neural Eng. 2012, 9, 066005. [Google Scholar] [CrossRef]

- Valente, V.; Demosthenous, A.; Bayford, R. A Tripolar Current-Steering Stimulator ASIC for Field Shaping in Deep Brain Stimulation. IEEE Trans. Biomed. Circuits Syst. 2011, 6, 197–207. [Google Scholar] [CrossRef] [PubMed]

- Farahmand, S.; Vahedian, H.; Eslami, M.A. Wearable, Battery-Powered, Wireless, Programmable 8-Channel Neural Stimulator. In Proceedings of the 34th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, San Diego, CA, USA, 28 August–1 September 2012. [Google Scholar]

- Mokwa, W.; Goertz, M.; Koch, C.; Krisch, I.; Trieu, H.; Walter, P. Intraocular Epiretinal Prosthesis to Restore Vision in Blind Humans. In Proceedings of the 30th Annual International IEEE Engineering in Medicine and Biology Society, Vancouver, BC, Canada, 20–25 August 2008. [Google Scholar]

- Wagenaar, D.A.; Pine, J.; Potter, S.M. Effective parameters for stimulation of dissociated cultures using multi-electrode arrays. J. Neurosci. Methods 2004, 138, 27–37. [Google Scholar] [CrossRef] [PubMed]

- Laotaveerungrueng, N.; Lahiji, R.R.; Garverick, S.L.; Mehregany, M. A High-Voltage, High-Current CMOS Pulse Generator ASIC for Deep Brain Stimulation. In Proceedings of the 32nd Annual International Conference of the IEEE Engineering in Medicine and Biology Society, Buenos Aires, Argentina, 31 August–4 September 2010. [Google Scholar]

- Chin, C.; Senior, W.; Sung, T.C.; Wu, Y.H.; Hsu, C.H.; Shmilovitz, D. A Reconfigurable 16-channel HV Stimulator ASIC for Spinal Cord Stimulation Systems. In Proceedings of the IEEE Asia Pacific Conference on Circuits and Systems, Kaohsiung, Taiwan, 2–5 December 2012. [Google Scholar]

- Arfin, S.K.; Sarpeshkar, R. An Energy-Efficient, Adiabatic Electrode Stimulator with Inductive Energy Recycling and Feedback Current Regulation. IEEE Trans. Biomed. Circuits Syst. 2012, 6, 1–14. [Google Scholar] [CrossRef]

- Chun, H.; Tran, N.; Yang, Y.; Kavehei, O.; Bai, S.; Skafidas, S. A Precise Charge Balancing and Compliance Voltage MonitoringStimulator Front-End for 1024-electrodes Retinal Prosthesis. In Proceedings of the 34th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, San Diego, CA, USA, 28 August–1 September 2012. [Google Scholar]

- Sooksood, K.; Noorsal, E.; Bihr, U.; Ortmanns, M. Recent Advances in Power Efficient Output Stage for High Density Implantable Stimulators. In Proceedings of the 34th Annual International Conference of the IEEE Engineering in Medicine and Biology Society, San Diego, CA USA, 28 August–1 September 2012. [Google Scholar]

- Kmon, P. Design of a Reconfigurable Stimulator for Multichannel Integrated Systems Dedicated to Neurobiology Experiments. In Proceedings of the 21st International Conference Mixed Design of Integrated Circuits and Systems (MIXDES), Lublin, Poland, 19–21 June 2014. [Google Scholar]

- NEUROACT: A Collaborative Training Program to Develop Multi-Electrode Array (MEA) Platforms to Understand Synaptic Function and Treat Diseases of the Nervous System. Available online: https://cordis.europa.eu/project/id/286403/ (accessed on 25 May 2018).

- Zoladz, M. A System for 256-Channel In-Vitro Recording of the Electrophysiological Activity of Brain Tissue. Metrol. Meas. Syst. 2013, 20, 371–384. [Google Scholar] [CrossRef][Green Version]

- Heuschkel, M. Fabrication of Multi-Electrode Array Devices for Electrophysiological Monitoring of In-Vitro Cell/Tissue Cultures. Ph.D. Thesis, EPFL, Lausanne, Switzerland, 2001. [Google Scholar]

- Van de Vijver, S.; Missault, S.; van Soom, J.; van der Veken, P.; Augustyns, K.; Joossens, J.; Dedeurwaerdere, S.; Giugliano, M. The effect of pharmacological inhibition of Serine Proteases on neuronal networks in vitro. PeerJ 2019, 7, e6796. [Google Scholar] [CrossRef]

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).