A Reference-Sampling Based Calibration-Free Fractional-N PLL with a PI-Linked Sampling Clock Generator

Abstract

:1. Introduction

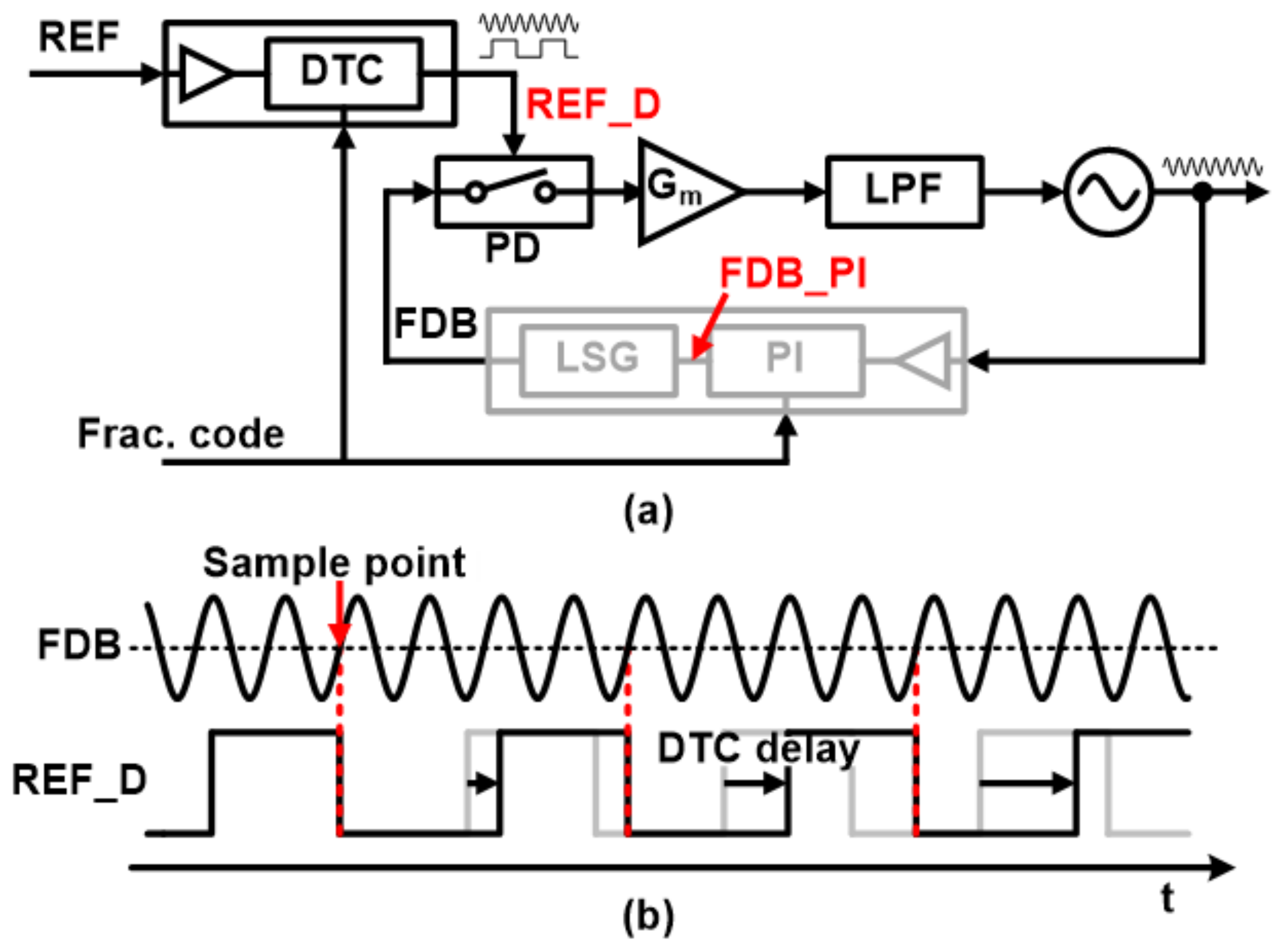

2. Sub-Sampling PLL and Reference-Sampling PLL

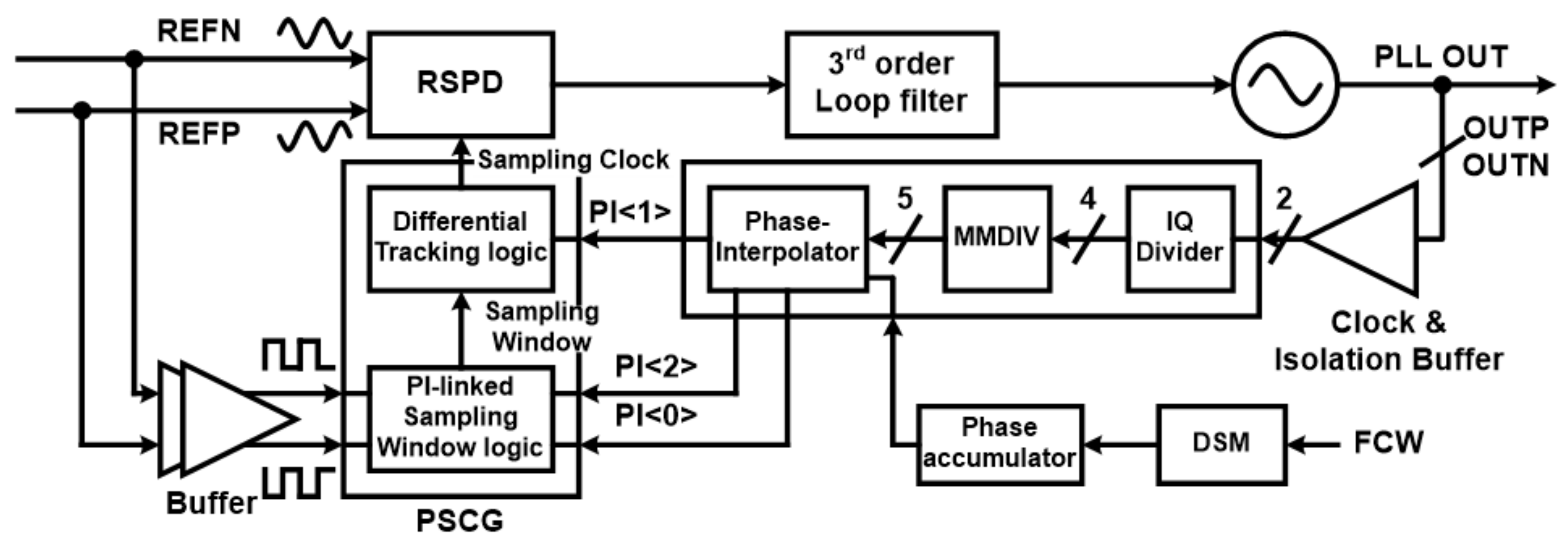

3. Architecture

3.1. Architecture Overview

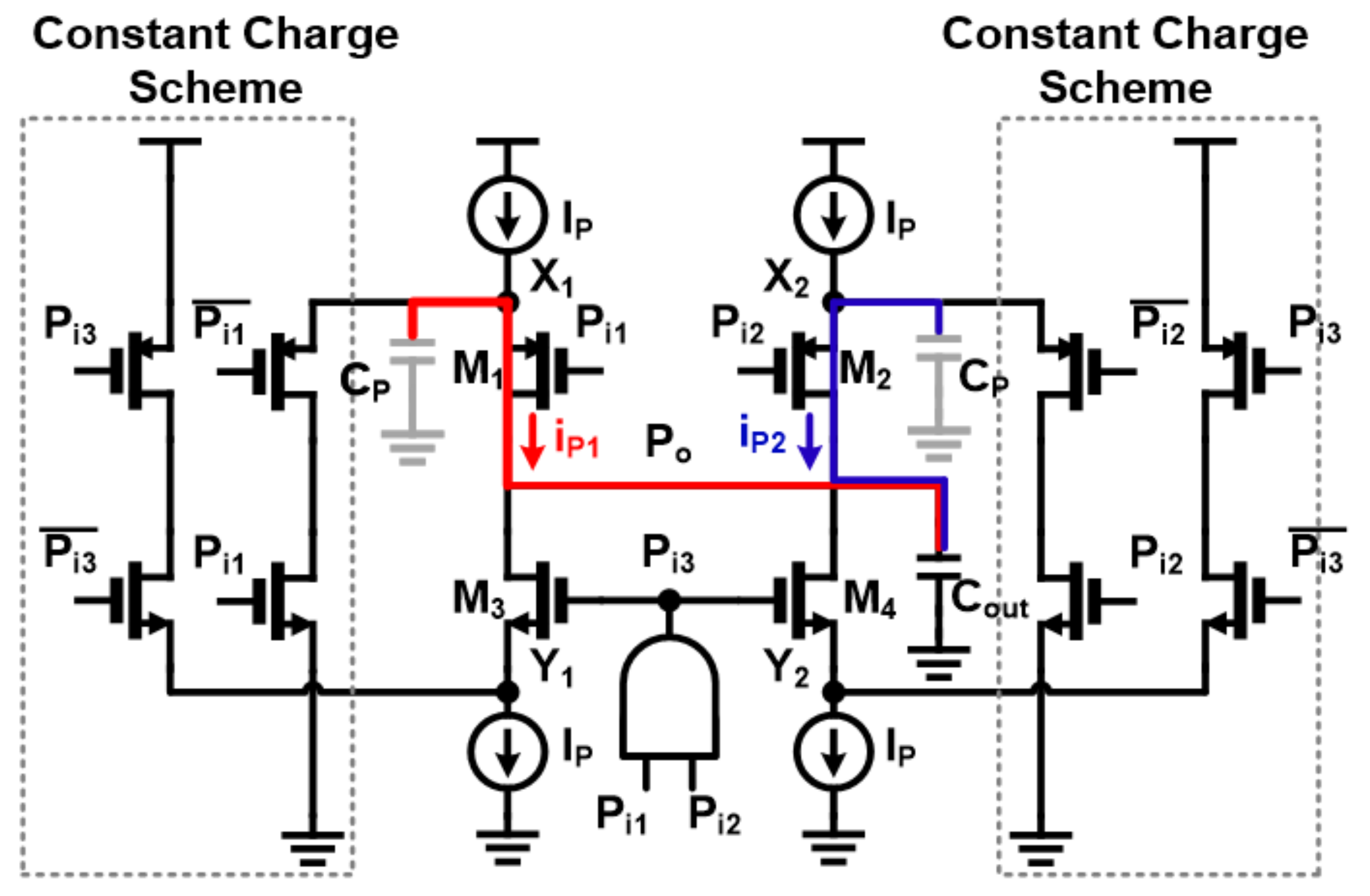

3.2. Pipelined Phase-Interpolator with Constant Charge Technique

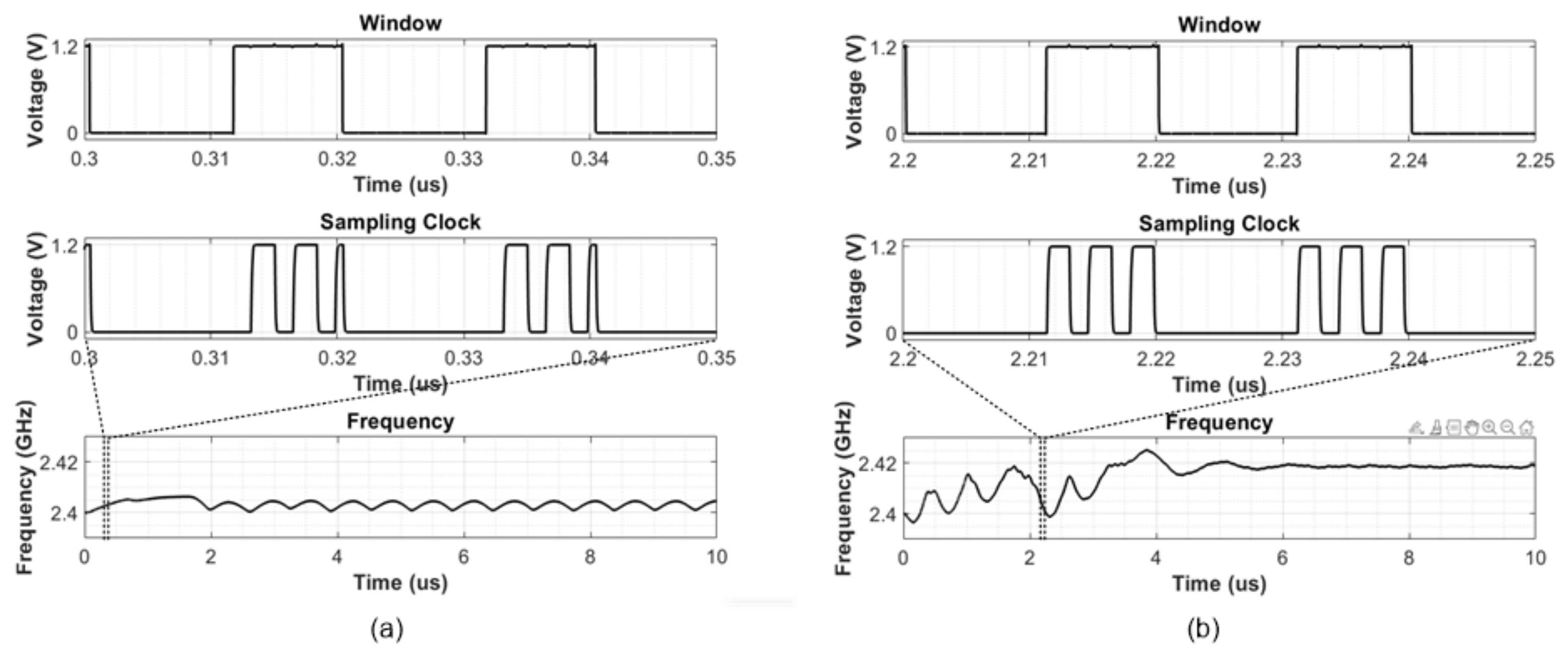

3.3. PI-Linked Sampling Clock Generator (PSCG)

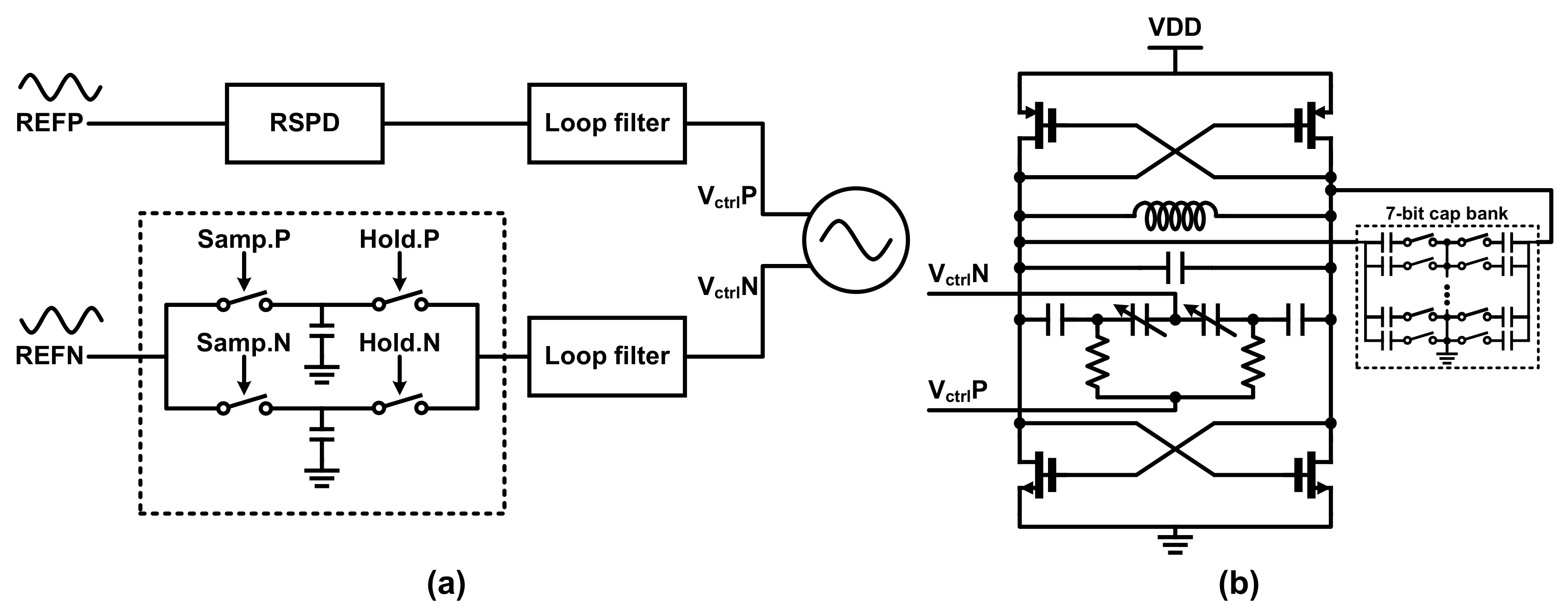

3.4. Reference-Sampling Phase Detector and VCO

4. Noise Analysis

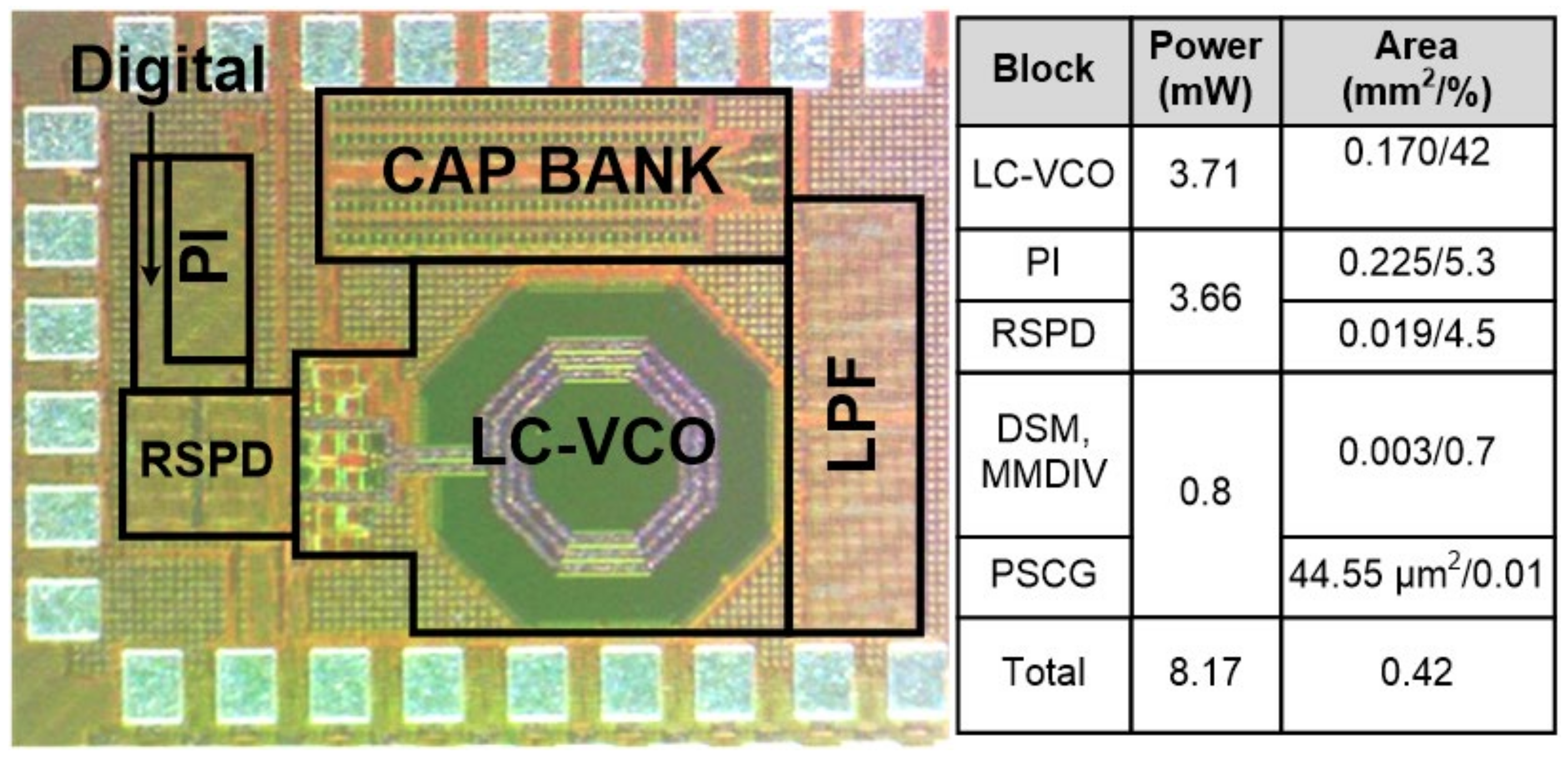

5. Measurement

6. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Conflicts of Interest

References

- Agiwal, M.; Roy, A.; Saxena, N. Next generation 5G wireless networks: A comprehensive survey. IEEE Commun. Surv. Tutor. 2016, 18, 1617–1655. [Google Scholar] [CrossRef]

- Roh, W.; Seol, J.; Park, J.; Lee, B.; Lee, J.; Kim, Y.; Cho, J.; Cheun, K. Millimeter-wave beamforming as an enabling technology for 5G cellular communications: Theoretical feasibility and prototype results. IEEE Comm. Mag. 2014, 52, 106–113. [Google Scholar] [CrossRef]

- Guo, R.; Lu, Z.; Hu, S.; Yu, Q.; Rong, L.; Liu, Y. Design and Verification of a Charge Pump in Local Oscillator for 5G Applications. Electronics 2021, 10, 1009. [Google Scholar] [CrossRef]

- Wu, X.; Deng, F.; Hao, Y.; Fu, Z.; Zhang, L. Design of a Humidity Sensor Tag for Passive Wireless Applications. Sensors 2015, 15, 25564–25576. [Google Scholar] [CrossRef] [PubMed] [Green Version]

- Zanuso, M.; Levantino, S.; Samori, C.; Lacaita, A.L. A Wideband 3.6 GHz Digital ΔΣ Fractional-N PLL With Phase Interpolation Divider and Digital Spur Cancellation. IEEE J. Solid-State Circuits 2011, 46, 627–638. [Google Scholar] [CrossRef]

- Nonis, R.; Grollitsch, W.; Santa, T. digPLL-Lite: A low-complexity low-jitter fractional-N digital PLL architecture. IEEE J. Solid-State Circuits 2013, 48, 3134–3145. [Google Scholar] [CrossRef]

- Temporiti, E.; Weltin-Wu, C.; Baldi, D.; Tonietto, R.; Svelto, F. A 3 GHz fractional all-digital PLL with a 1.8 MHz bandwidth implementing spur reduction techniques. IEEE J. Solid-State Circuits 2009, 44, 824–834. [Google Scholar] [CrossRef]

- Tasca, D.; Zanuso, M.; Marzin, G.; Levantino, S.; Samori, C.; Lacaita, A.L. A 2.9–4.0-GHz Fractional-N Digital PLL With Bang-Bang Phase Detector and 560-fsrms Integrated Jitter at 4.5-mW Power. IEEE J. Solid-State Circuits 2011, 46, 2745–2758. [Google Scholar] [CrossRef]

- Sharkia, A.; Mirabbasi, S.; Shekhar, S. A 0.01 mm2 4.6-to-5.6 GHz sub-sampling type-I frequency synthesizer with −254 dB FOM. In Proceedings of the 2018 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 11–15 February 2018; pp. 256–257. [Google Scholar]

- Gao, X.; Klumperink, E.A.M.; Bohsali, M.; Nauta, B. A Low Noise Sub-Sampling PLL in Which Divider Noise is Eliminated and PD/CP Noise is Not Multiplied by N2. IEEE J. Solid-State Circuits 2009, 44, 3253–3263. [Google Scholar] [CrossRef] [Green Version]

- Gao, X.; Klumperink, E.A.M.; Socci, G.; Bohsali, M.; Nauta, B. Spur Reduction Techniques for Phase-Locked Loops Exploiting A Sub-Sampling Phase Detector. IEEE J. Solid-State Circuits 2010, 45, 1809–1820. [Google Scholar] [CrossRef] [Green Version]

- Sharma, J.; Krishnaswamy, H. A 2.4-GHz Reference-Sampling Phase-Locked Loop That Simultaneously Achieves Low-Noise and Low-Spur Performance. IEEE J. Solid-State Circuits 2019, 54, 1407–1424. [Google Scholar] [CrossRef]

- Du, J.; Siriburanon, T.; Hu, Y.; Govindaraj, V.; Staszewski, R.B. A 2.02–2.87 GHz −249 dB FoM 1.1-mW digital PLL exploiting reference sampling phase detector. IEEE Solid-State Circuits Lett. 2020, 3, 158–161. [Google Scholar] [CrossRef]

- Liao, D.; Zhang, Y.; Dai, F.F.; Chen, Z.; Wang, Y. An mm-Wave Synthesizer With Robust Locking Reference-Sampling PLL and Wide-Range Injection-Locked VCO. IEEE J. Solid-State Circuits 2020, 55, 536–546. [Google Scholar] [CrossRef]

- Chang, W.S.; Huang, P.C.; Lee, T.C. A fractional-N divider-less phase-locked loop with a subsampling phase detector. IEEE J. Solid-State Circuits 2014, 49, 2964–2975. [Google Scholar] [CrossRef]

- Raczkowski, K.; Markulic, N.; Hershberg, B.; Driessche, J.V.; Craninckx, J. A 9.2–12.7 GHz wideband fractional-N subsampling PLL in 28 nm CMOS with 280 fs rms jitter. IEEE J. Solid-State Circuits 2015, 50, 1203–1213. [Google Scholar] [CrossRef]

- Hanumolu, P.K.; Kratyuk, V.; Wei, G.Y.; Moon, U.K. A Sub-Picosecond Resolution 0.5–1.5 GHz Digital-to-Phase Converter. IEEE J. Solid-State Circuits 2008, 43, 414–424. [Google Scholar] [CrossRef]

- Levantino, S.; Marucci, G.; Marzin, G.; Fenaroli, A.; Samori, C.; Lacaita, A.L. A 1.7 GHz fractional-N frequency synthesizer based on a multiplying delay-locked loop. IEEE J. Solid-State Circuits 2015, 50, 2678–2691. [Google Scholar] [CrossRef]

- Wu, W.; Yao, C.; Godbole, K.; Ni, R.; Chiang, P.; Han, Y.; Zuo, Y.; Verma, A.; Lu, I.S.; Son, S.W.; et al. A 28-nm 75-fsrms Analog Fractional- N Sampling PLL With a Highly Linear DTC Incorporating Background DTC Gain Calibration and Reference Clock Duty Cycle Correction. IEEE J. Solid-State Circuits 2019, 54, 1254–1256. [Google Scholar] [CrossRef]

- Tao, J.; Heng, C. A 2.2-GHz 3.2-mW DTC-Free Sampling ΔΣ Fractional-N PLL With −110-dBc/Hz In-Band Phase Noise and −246-dB FoM and −83-dBc Reference Spur. IEEE Trans. Circuits Syst. I Reg. Pap. 2019, 66, 3317–3329. [Google Scholar] [CrossRef]

- Liao, D.; Dai, F.F. A Fractional-N Reference Sampling PLL With Linear Sampler and CDAC Based Fractional Spur Cancellation. IEEE J. Solid-State Circuits 2021, 56, 694–704. [Google Scholar] [CrossRef]

- Nandwana, R.K.; Anand, T.; Saxena, S.; Kim, S.-J.; Talegaonkar, M.; Elkholy, A.; Choi, W.-S.; Elshazly, A.; Hanunolu, P.K. A Calibration-Free Fractional-N Ring PLL Using Hybrid Phase/Current-Mode Phase Interpolation Method. IEEE J. Solid-State Circuits 2015, 50, 882–895. [Google Scholar] [CrossRef]

- Narayanan, A.T.; Katsuragi, M.; Kimura, K.; Kondo, S.; Tokgoz, K.K.; Nakata, K.; Deng, W.; Okada, K.; Matsuzawa, A. A Fractional-N Sub-Sampling PLL using a Pipelined Phase-Interpolator with an FoM of –250 dB. IEEE J. Solid-State Circuits 2016, 51, 1630–1640. [Google Scholar] [CrossRef]

- Levantino, S.; Romano, L.; Pellerano, S.; Samori, C.; Lacaita, A.L. Phase Noise in Digital Frequency Dividers. IEEE J. Solid-State Circuits 2004, 39, 775–784. [Google Scholar] [CrossRef]

- Homayoun, A.; Razavi, B. Analysis of Phase Noise in Phase/Frequency Detectors. IEEE Trans. Circuits Syst. I 2012, 60, 529–539. [Google Scholar] [CrossRef] [Green Version]

- Chen, Z.-Z.; Wang, Y.-H.; Shin, J.; Zhao, Y.; Mirhaj, S.A.; Kuan, Y.-C.; Chen, H.-N.; Jou, C.-P.; Tsai, M.-H.; Hsueh, F.-L.; et al. A Sub-Sampling All-Digital Fractional-N Frequency Synthesizer with −111 dBc/Hz In-Band Phase Noise and an FOM of −242 dB. In Proceedings of the Digest of Technical Papers, Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 22–26 February 2015. [Google Scholar]

- Liao, D.; Dai, F.F.; Nauta, B.; Klumperink, E.A.M. A 2.4-GHz 16-phase sub-sampling fractional-N PLL with robust soft loop switching. IEEE J. Solid-State Circuits 2018, 53, 715–727. [Google Scholar] [CrossRef]

- Liu, Y.-H.; Heuvel, J.V.D.; Kuramochi, T.; Busze, B.; Mateman, P.; Chillara, V.K.; Wang, B.; Staszewski, R.B.; Philips, K. An ultra-low power 1.7–2.7 GHz fractional-N sub-sampling digital frequency synthesizer and modulator for IoT applications in 40 nm CMOS. IEEE Trans. Circuits Syst. I 2017, 64, 1094–1105. [Google Scholar] [CrossRef]

| Tao [20] TOCAS-I’19 | Chen [26] ISSCC’15 | Chang [15] JSSC’14 | Liao [27] JSSC’18 | Liu [28] TOCAS-I’17 | This Work | |

|---|---|---|---|---|---|---|

| PLL Type | Sub-Sampling Analog Fractional-N | Sub-Sampling Digital Fractional-N | Sub-Sampling Analog Fractional-N | Sub-Sampling Analog Fractional-N | Sub-Sampling Digital Fractional-N | Ref-Sampling Analog Fractional-N |

| Technology | 130 nm | 65 nm | 180 nm | 130 nm | 40 nm | 65 nm |

| Ref. (MHz) | 50 | 49.15 | 48 | 50 | 40 | 100 |

| Output (GHz) | 2.3 | 2.6~3.9 | 2.12~2.4 | 2.39~2.46 | 1.7~2.7 | 2.17~2.3 |

| Bandwidth (MHz) | 1 | - | 0.5 | 1.5 | 1.5 | 2 |

| In-band PN (dBc/Hz) | −112 (@200 kHz) | −110.6 (@100 kHz) | −112 (@50 kHz) | −120 (@1 MHz) | −109 (@1 MHz) | −109.9 (@100 kHz) |

| Worst spur(dBc) | −48.5 | −48.5 | −48 | −52 | −37 | −44.06 |

| RMS jitter (fs) | 358.2 (10 k~10 M) | 226 (1 k~100 M) | 266 (10 k~30 M) | 169 (10 k~10 M) | 1700 (10 k~10 M) | 322 (10 k~50 M) |

| Power (mW) | 3.2 | 11.5 | 17.3 | 21 | 1.19 | 8.17 |

| Area (mm2) | 0.45 | 0.23 | 0.75 | 0.43 | 0.22 | 0.42 |

| * FoM | −244 | −241.8 | −239.1 | −242 | −234.6 | −240.7 |

Publisher’s Note: MDPI stays neutral with regard to jurisdictional claims in published maps and institutional affiliations. |

© 2021 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Han, J.-S.; Eom, T.-H.; Choi, S.-W.; Seong, K.; Yoon, D.-H.; Kim, T.T.-H.; Baek, K.-H.; Shim, Y. A Reference-Sampling Based Calibration-Free Fractional-N PLL with a PI-Linked Sampling Clock Generator. Sensors 2021, 21, 6824. https://doi.org/10.3390/s21206824

Han J-S, Eom T-H, Choi S-W, Seong K, Yoon D-H, Kim TT-H, Baek K-H, Shim Y. A Reference-Sampling Based Calibration-Free Fractional-N PLL with a PI-Linked Sampling Clock Generator. Sensors. 2021; 21(20):6824. https://doi.org/10.3390/s21206824

Chicago/Turabian StyleHan, Jae-Soub, Tae-Hyeok Eom, Seong-Wook Choi, Kiho Seong, Dong-Hyun Yoon, Tony Tae-Hyong Kim, Kwang-Hyun Baek, and Yong Shim. 2021. "A Reference-Sampling Based Calibration-Free Fractional-N PLL with a PI-Linked Sampling Clock Generator" Sensors 21, no. 20: 6824. https://doi.org/10.3390/s21206824

APA StyleHan, J.-S., Eom, T.-H., Choi, S.-W., Seong, K., Yoon, D.-H., Kim, T. T.-H., Baek, K.-H., & Shim, Y. (2021). A Reference-Sampling Based Calibration-Free Fractional-N PLL with a PI-Linked Sampling Clock Generator. Sensors, 21(20), 6824. https://doi.org/10.3390/s21206824