Low-Power Highly Robust Resistance-to-Period Converter

Abstract

1. Introduction

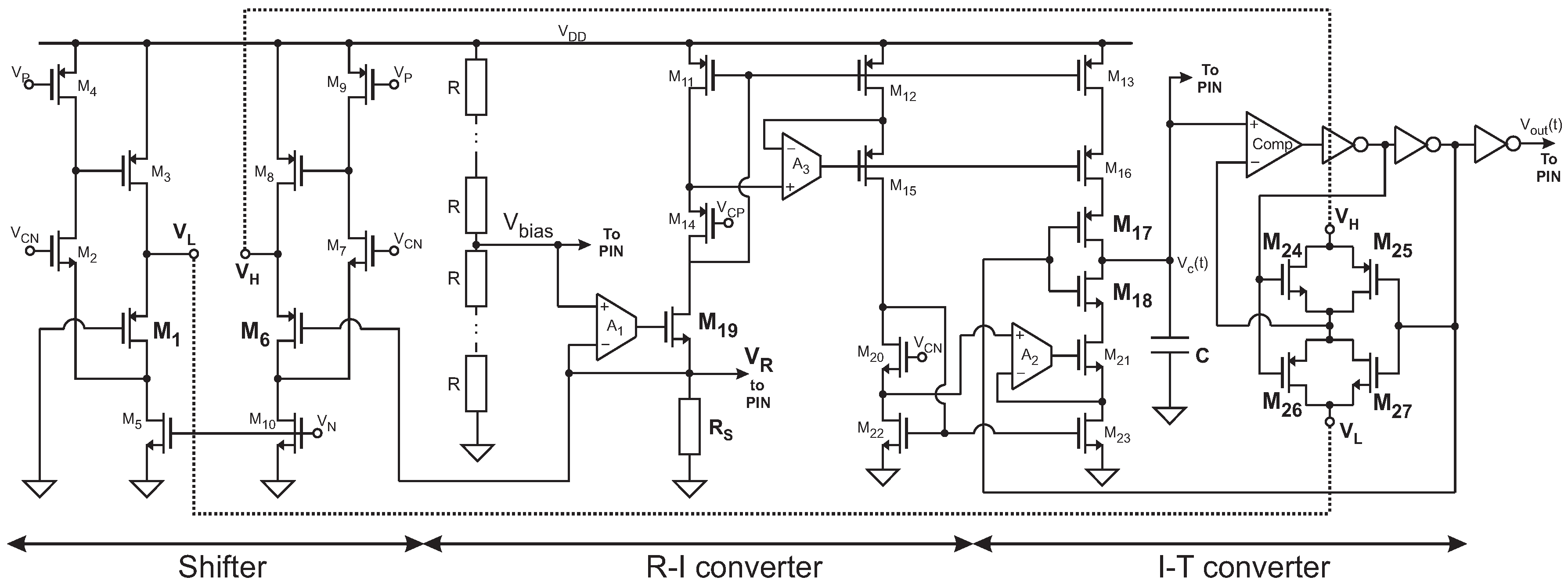

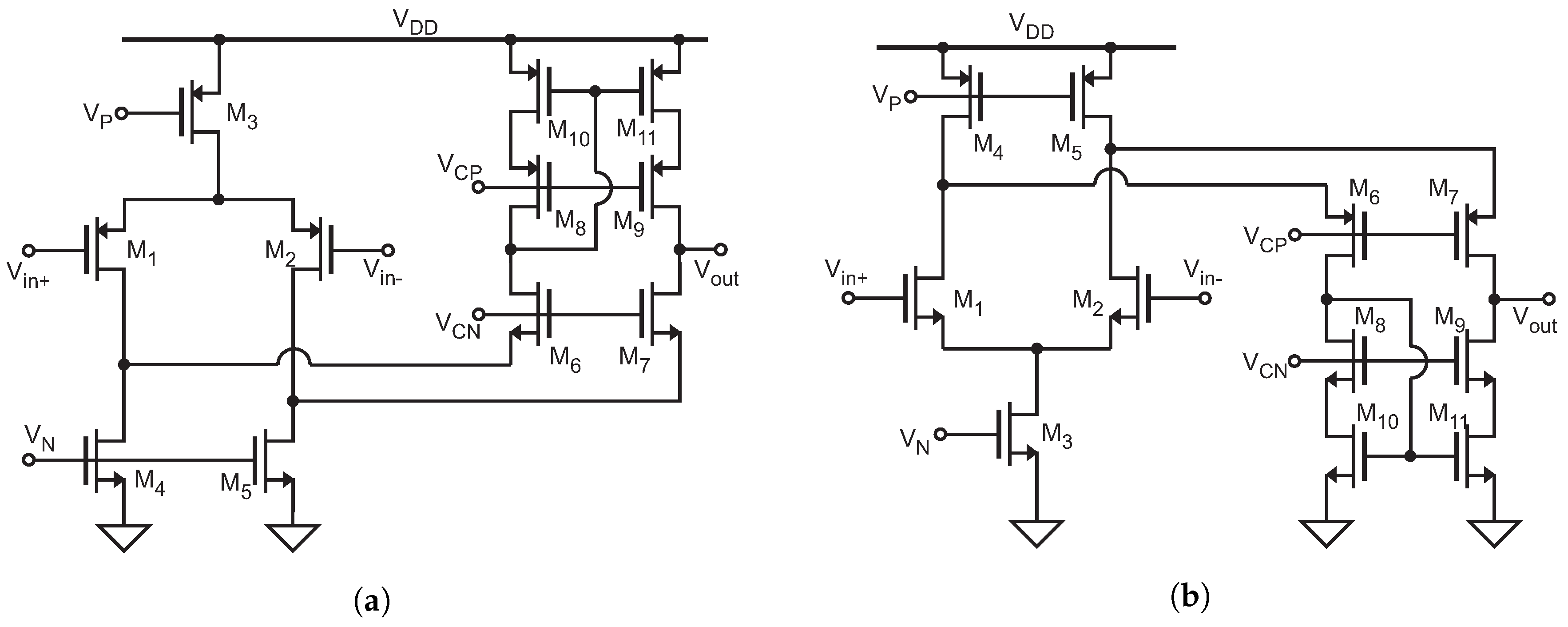

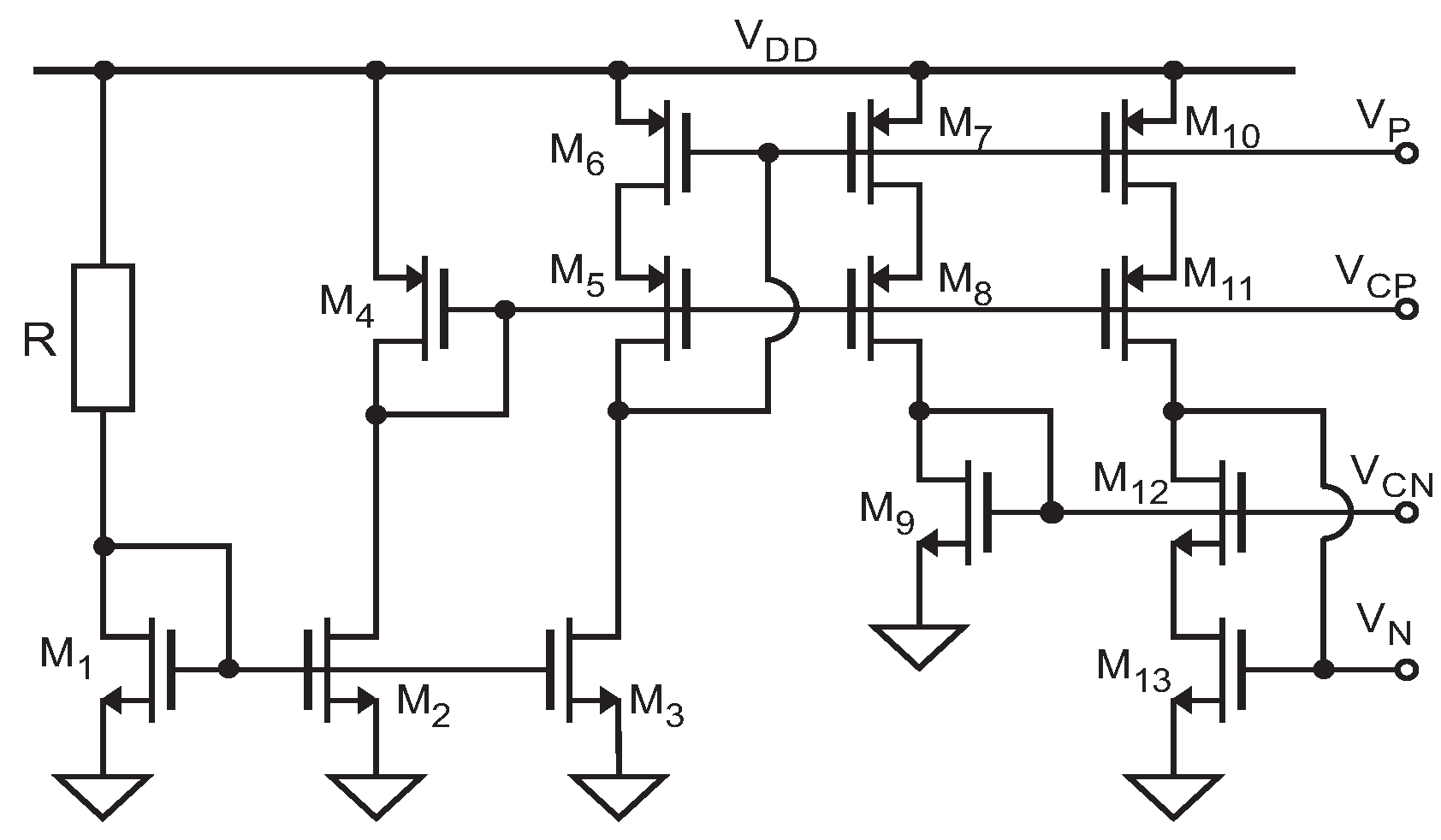

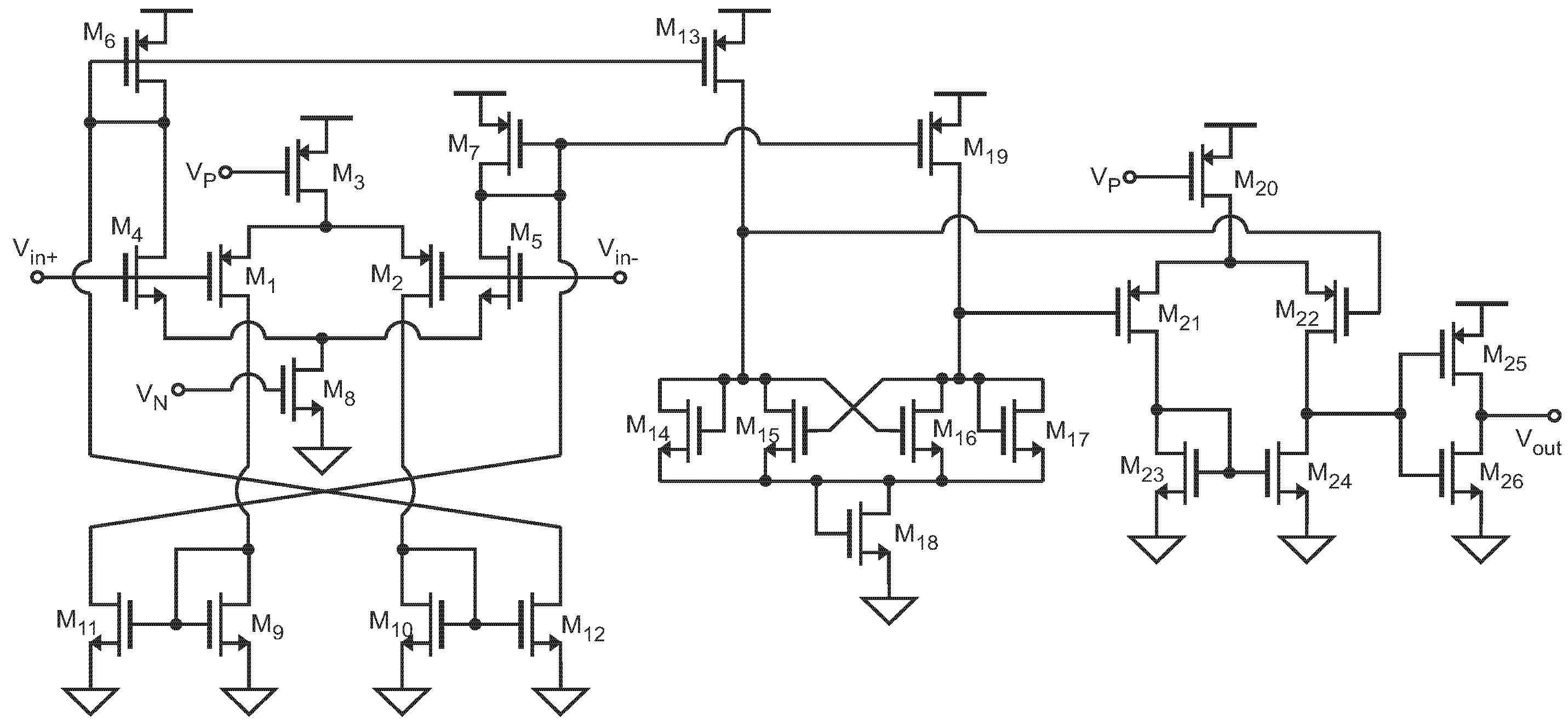

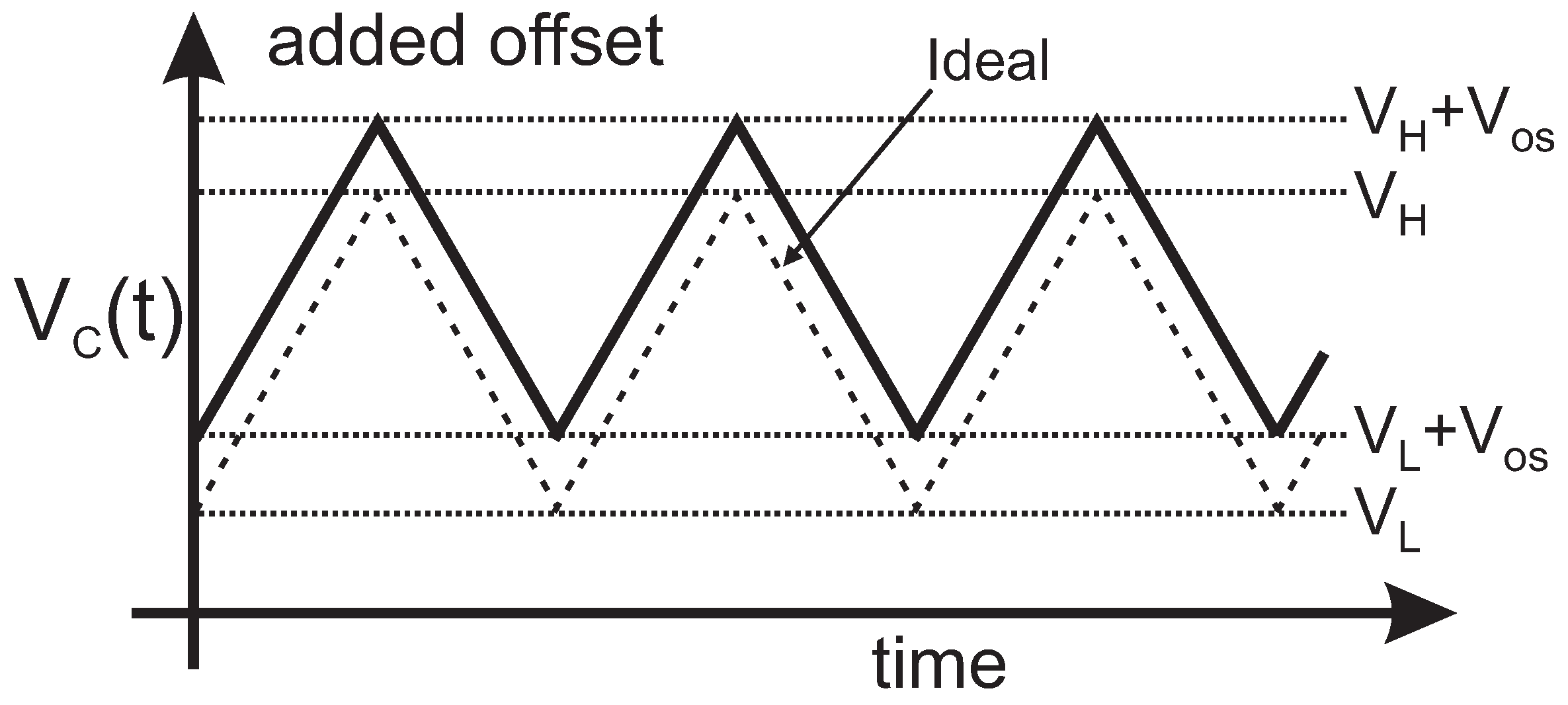

2. Proposed R-T Architecture

3. Resistance-To-Period Converter Implementation

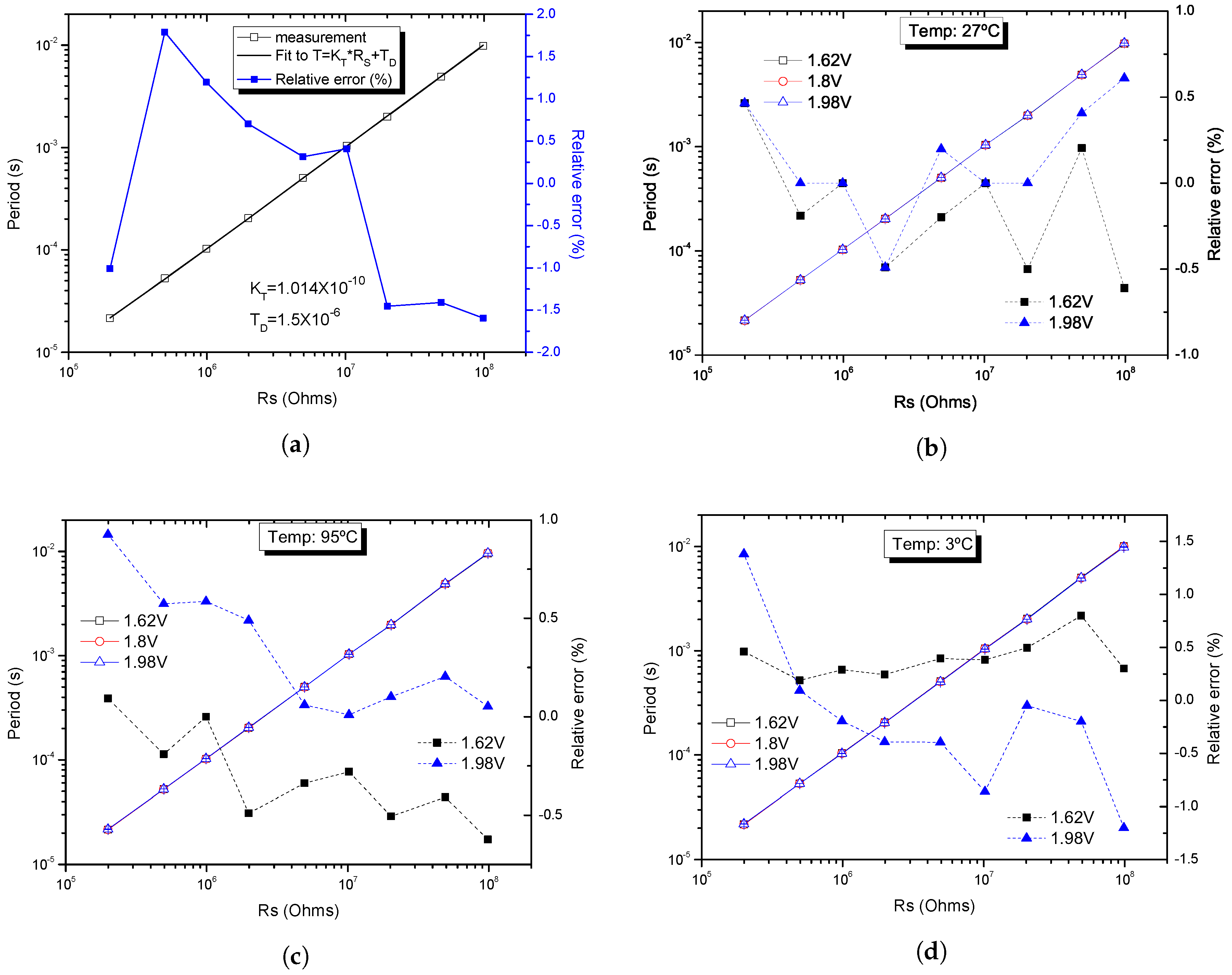

4. Experimental Results

5. Conclusions

Author Contributions

Funding

Conflicts of Interest

Abbreviations

| R-T | Resistance- to-Period |

| CMOS | Complementary Metal-Oxide Semiconductor |

| PVT | Process-Voltage-Temperature |

| MIM | Metal-Insulator-Metal |

| UMC | United Microelectronics Corporation |

| PMOS | P-type metal-oxide-semiconductor |

| NMOS | N-type metal-oxide-semiconductor |

| CMRR | Common Mode Rejection Ratio |

| PSRR | Power Supply Rejection Ratio |

| OTA | Operational Transimpedance Amplifier |

References

- Pizarro, F.; Villavicencio, P.; Yunge, D.; Rodriguez, M.; Hermosilla, G.; Leiva, A. Easy-to-Build Textile Pressure Sensor. Sensors 2018, 18, 1190. [Google Scholar] [CrossRef] [PubMed]

- Ma, L.; Shuai, X.; Zhu, P.; Sun, R. A highly sensitive flexible pressure sensor based on multi-scale structure and silver nanowires. In Proceedings of the 18th International Conference on Electronic Packaging Technology (ICEPT), Harbin, China, 16–19 August 2017; pp. 1366–1370. [Google Scholar]

- Matzeu, G.; Losacco, M.; Parducci, E.; Pucci, A.; Dini, V.; Romanelli, M.; Di Francesco, F. Skin temperature monitoring by a wireless sensor. In Proceedings of the IECON 2011—37th Annual Conference of the IEEE Industrial Electronics Society, Melbourne, VIC, Australia, 7–10 November 2011; pp. 3533–3535. [Google Scholar]

- Ong, G.T.; Chan, P.K. A Power-Aware Chopper-Stabilized Instrumentation Amplifier for Resistive Wheatstone Bridge Sensors. IEEE Trans. Instrum. Meas. 2014, 63, 2253–2263. [Google Scholar] [CrossRef]

- Solar, H.; Beriain, A.; Jiménez-Irastorza, A.; Alvarado, U.; Berenguer, R.; Ortiz de Landaluce, M.; Cojocariu, M.; Martínez, C. A CMOS sensor signal conditioner for an automotive pressure sensor based on a piezo-resistive bridge transducer. In Proceedings of the Conference on Design of Circuits and Integrated Systems (DCIS), Granada, Spain, 23–25 November 2016; pp. 1–5. [Google Scholar]

- Dutta, A.; Bhattacharyya, T.K. Low Offset, Low Noise, Variable Gain Interfacing Circuit with a Novel Scheme for Sensor Sensitivity and Offset Compensation for MEMS Based, Wheatstone Bridge Type, Resistive Smart Sensor. In Proceedings of the 24th Internatioal Conference on VLSI Design, Chennai, India, 2–7 January 2011; pp. 322–327. [Google Scholar]

- Yurish, S.Y. Low-Power, Low-Voltage Resistance-to-Digital Converter for Sensing Applications. Sens. Transducers 2016, 204, 1–10. [Google Scholar]

- Wang, C.; Lee, T.; Li, C.; Hu, R. An All-MOS High-Linearity Voltage-to-Frequency Converter Chip with 520-kHz/V Sensitivity. IEEE Trans. Circuits Syst. II Express Briefs 2006, 53, 744–747. [Google Scholar] [CrossRef]

- Kaliyugavaradan, S. A linear resistance-to-time converter with high resolution. IEEE Trans. Instrum. Meas. 2000, 49, 151–153. [Google Scholar] [CrossRef]

- Tongpakpanang, J.; Rerkratn, A.; Kaewpoonsuk, A.; Riewruja, V.; Petchmaneelumka, W. Simple resistance-to-period converter for resistive sensors. In Proceedings of the 2012 12th International Conference on Control, Automation and Systems, JeJu Island, Korea, 17–21 October 2012; pp. 1071–1075. [Google Scholar]

- Kirianaki, N.; Yurish, S.; Shpak, N.; Deynega, V. Data Acquisition and Signal Processing for Smart Sensors; John Wiley & Sons: Hoboken, NJ, USA, 2002. [Google Scholar]

- Kokolanski, Z.; Gavrovski, C.; Dimcev, V.; Makraduli, M. Simple Interface for Resistive Sensors Based on Pulse Width Modulation. IEEE Trans. Instrum. Meas. 2013, 62, 2983–2992. [Google Scholar] [CrossRef]

- Gardner, J.; Guha, P.; Udrea, F.; Covington, J. CMOS Interfacing for Integrated Gas Sensors: A Review. IEEE Sens. J. 2010, 10, 1833–1848. [Google Scholar] [CrossRef]

- Conso, F.; Grassi, M.; de Berti, C.; Malcovati, P.; Baschirotto, A. I2C System-on-Chip for bi-dimensional gas-sensor arrays providing extended dynamic-range A/D conversion and row temperature regulation. In Proceedings of the 2013 International Conference on IC Design Technology (ICICDT), Pavia, Italy, 29–31 May 2013. [Google Scholar]

- Bhat, N.; Jayaraman, B.; Pratap, R.; Bagga, S.; Mohan, S. Integrated CMOS gas sensors. In Proceedings of the 2nd International Workshop on Electron Devices and Semiconductor Technology, IEDST’09, Mumbai, India, 1–2 June 2009. [Google Scholar]

- Malcovati, P.; Grassi, M.; Baschirotto, A. Towards high-dynamic range CMOS integrated interface circuits for gas sensors. Sens. Actuators B Chem. 2013, 179, 301–312. [Google Scholar] [CrossRef]

- Mohan, N.M.; George, B.; Kumar, V.J. A Novel Dual-Slope Resistance-to-Digital Converter. IEEE Trans. Instrum. Meas. 2010, 59, 1013–1018. [Google Scholar] [CrossRef]

- Depari, A.; Flammini, A.; Marioli, D.; Rosa, S.; Taroni, A. A low- cost circuit for high-value resistive sensors varying over a wide range. Meas. Sci. Technol. 2006, 17, 353–358. [Google Scholar] [CrossRef]

- De Marcellis, A.; Depari, A.; Ferri, G.; Flammini, A.; Marioli, D.; Stornelli, V.; Taroni, A. A CMOS Integrable Oscillator-Based Front End for High-Dynamic-Range Resistive Sensors. IEEE Trans. Instrum. Meas. 2008, 57, 1596–1604. [Google Scholar] [CrossRef]

- Marcellis, A.D.; Depari, A.; Ferri, G.; Flammini, A.; Marioli, D.; Stornelli, V.; Taroni, A. Uncalibrated integrable wide-range single-supply portable interface for resistance and parasitic capacitance determination. Sens. Actuators B Chem. 2008, 132, 477–484. [Google Scholar] [CrossRef]

- Ferri, G.; Carlo, C.D.; Stornelli, V.; Marcellis, A.D.; Flammini, A.; Depari, A.; Jand, N. A single-chip integrated interfacing circuit for wide-range resistive gas sensor arrays. Sens. Actuators B Chem. 2009, 143, 218–225. [Google Scholar] [CrossRef]

- Alvarez-Simon, L.C.; Sanz-Pascual, M.T. A low-power low-voltage cmos resistance-to-period converter. In Proceedings of the 2012 IEEE 55th International Midwest Symposium on Circuits and Systems (MWS-CAS), Boise, ID, USA, 5–8 August 2012. [Google Scholar]

- Yu, Z.; Scherjon, C.; Mahsereci, Y.; Burghartz, J.N. A new CMOS stress sensor ratiometric readout for in-plane stress magnitude and angle detection. In Proceedings of the 2017 IEEE SENSORS, Glasgow, UK, 29 October–1 November 2017; pp. 1–3. [Google Scholar]

- Sim, C.T.Y.; Toumazou, C.; Cheung, P.Y.K. Ratiometric current-mode rational DAC. Electron. Lett. 2004, 40, 409–410. [Google Scholar] [CrossRef]

- Amini, S.; Johns, D.A. A pseudo-differential charge balanced ratiometric readout system for capacitive inertial sensors. In Proceedings of the 2015 IEEE 58th International Midwest Symposium on Circuits and Systems (MWSCAS), Fort Collins, CO, USA, 2–5 August 2015; pp. 1–4. [Google Scholar]

- Beriain, A.; Gutierrez, I.; Solar, H.; Berenguer, R. 0.5 V and 0.43 pJ/bit Capacitive Sensor Interface for Passive Wireless Sensor Systems. Sensors 2015, 15, 21554–21566. [Google Scholar] [CrossRef] [PubMed]

- Westra, J. High-Performance Oscillators and Oscillator Systems. Ph.D. Thesis, Delft University of Technology, Delft, The Netherlands, 1998. [Google Scholar]

- Anderson, R. Understanding Ratiometric Conversions; Technical Report; Texas Instruments: Dallas, TX, USA, 2004. [Google Scholar]

- Maloberti, F. Analog Design for CMOS VLSI Systems; Kluwer Academic Publishers: Dordrecht, The Netherlands, 2003. [Google Scholar]

- Westra, J.; Verhoeven, C.; Van Roermound, A. Oscillators and Oscillator Systems: Classification, Analysis and Synthesis; Springer: Berlin, Germany, 1999. [Google Scholar]

- Conso, F.; Grassi, M.; Malcovati, P.; Baschirotto, A. A very high dynamic range interface circuit for resistive gas sensor matrix read-out. In Proceedings of the 2011 IEEE International Symposium on Circuits and Systems (ISCAS), Rio de Janeiro, Brazil, 15–18 May 2011; pp. 2209–2212. [Google Scholar]

- Choe, K.; Bernal, O.; Nuttman, D.; Je, M. A precision relaxation oscillator with a self-clocked offset-cancellation scheme for implantable biomedical SoCs. In Proceedings of the IEEE International Solid-State Circuits Conference—Digest of Technical Papers, ISSCC 2009, San Francisco, CA, USA, 8–12 February 2009. [Google Scholar]

- Carvajal, R.; Ramirez-Angulo, J.; Lopez-Martin, A.; Torralba, A.; Galan, J.; Carlosena, A.; Chavero, F. The flipped voltage follower: A useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst. I Regul. Pap. 2005, 52, 1276–1291. [Google Scholar] [CrossRef]

- Koay, K.C.; Chan, P.K. A Low-Power Resistance-to-Frequency Converter Circuit With Wide Frequency Range. IEEE Trans. Instrum. Meas. 2015, 64, 3173–3182. [Google Scholar] [CrossRef]

- Reverter, F.; Gasulla, M.; Pallás-Areny, R. Analysis of power supply interference effects on quasi-digital sensors. Sens. Actuators A 2005, 119, 187–195. [Google Scholar] [CrossRef]

- Depari, A.; Flammini, A.; Sisinni, E.; De Marcellis, A.; Ferri, G.; Mantenuto, P. Fast, Versatile, and Low-Cost Interface Circuit for Electrochemical and Resistive Gas Sensor. IEEE Sens. J. 2014, 14, 315–323. [Google Scholar] [CrossRef]

- George, A.K.; Shim, W.; Je, M.; Lee, J. A 114-aFRMS- Resolution 46-nF/10-MΩ -Range Digital-Intensive Reconfigurable RC-to-Digital Converter with Parasitic-Insensitive Femto-Farad Baseline Sensing. In Proceedings of the IEEE Symposium on VLSI Circuits, Honolulu, HI, USA, 18–22 June 2018; pp. 157–158. [Google Scholar]

- Ciciotti, F.; Baschirotto, A.; Buffa, C.; Gaggl, R. A MOX gas sensors resistance-to-digital CMOS interface with 8-bits resolution and 128dB dynamic range for low-power consumer applications. In Proceedings of the 13th Conference on Ph.D. Research in Microelectronics and Electronics (PRIME), Giardini Naxos, Italy, 12–15 June 2017; pp. 21–22. [Google Scholar]

| Parameter | NMOS Input | PMOS Input |

|---|---|---|

| Supply voltage | 1.8 V | |

| DC gain | 79 dB | 71 dB |

| Phase Margin | 66 | 71 |

| CMRR | 99 dB @20 kHz | 103 dB @20 kHz |

| Offset | 0.56 mV | 0.1 mV |

| PSRR @dc | 98 dB | 71 dB |

| PSRR @100 kHz | 77 dB | 63 dB |

| GBW | 36.4 MHz | 39.4 MHz |

| Input reference noise | 109 nV/ | 170 nV/ |

| Corner frequency | 1 kHz | |

| Power consumption | 2.7 W | |

| Silicon area | 0.0002 mm | 0.00017 mm |

| Parameter | NMOS Input |

|---|---|

| Supply voltage | 1.8 V |

| DC gain | 120 dB |

| Input Resolution | 2 V |

| Offset | 0.6 mV |

| GBW | 40.3 MHz |

| Propagation delay at 0.1 mV | 62 ns |

| Propagation delay at 1 mV | 51 ns |

| Average power consumption | 17 W |

| Silicon area | 0.00032 mm |

| Parameter | R-T Converters | ||||||

|---|---|---|---|---|---|---|---|

| Proposed | [15] | [21] | [37] | [38] | [34] | [36] | |

| CMOS Technology | 0.18 m | 0.13 m | 0.35 m | 0.18 m | 0.13 m | 0.65 m | discrete components |

| Supply voltage (V) | 1.8 | 1.2 | 3.3 | 1 | 1.8 | 1.2 | 3.3 |

| Sensitivity | 101.4 ns/k | 1.2 ns/k | 320 ns/k | 46 nF/10 M | 0.01 KHz/k | 41.5 Hz/nA | 2.83 ns/k |

| Input range | 200 k to 100 M | 400 to 200 M | 470 k to 100 G | 15 k to 10 M | 100 to 1 M | 30 nA to 60 A | 1 k to 10 G |

| Max. linearity error | 1.75% | 5% | - | - | - | ±0.6 () | 5% |

| (2.5 decades) | (per decade) | (per decade) | (7 decades) | ||||

| Max. error due to | ±1% | - | ±1% | - | - | −3.32 to +4.21% | - |

| Max. error due to and | ±1.5% | - | - | - | - | - | - |

| Power consumption (mW) | 0.06 | 0.32 | 4 | 0.14 | 0.81 | 0.168 | 25 |

| Area (mm) | 0.018 | - | 0.84 | 0.175 | 0.125 | - | - |

© 2018 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Álvarez-Simón, L.C.; Gómez-Ramírez, E.; Sanz-Pascual, M.T. Low-Power Highly Robust Resistance-to-Period Converter. Sensors 2019, 19, 8. https://doi.org/10.3390/s19010008

Álvarez-Simón LC, Gómez-Ramírez E, Sanz-Pascual MT. Low-Power Highly Robust Resistance-to-Period Converter. Sensors. 2019; 19(1):8. https://doi.org/10.3390/s19010008

Chicago/Turabian StyleÁlvarez-Simón, Luis C., Emmanuel Gómez-Ramírez, and María Teresa Sanz-Pascual. 2019. "Low-Power Highly Robust Resistance-to-Period Converter" Sensors 19, no. 1: 8. https://doi.org/10.3390/s19010008

APA StyleÁlvarez-Simón, L. C., Gómez-Ramírez, E., & Sanz-Pascual, M. T. (2019). Low-Power Highly Robust Resistance-to-Period Converter. Sensors, 19(1), 8. https://doi.org/10.3390/s19010008