A Semi-Floating Gate Memory Based on SOI Substrate by TCAD Simulation

Abstract

1. Introduction

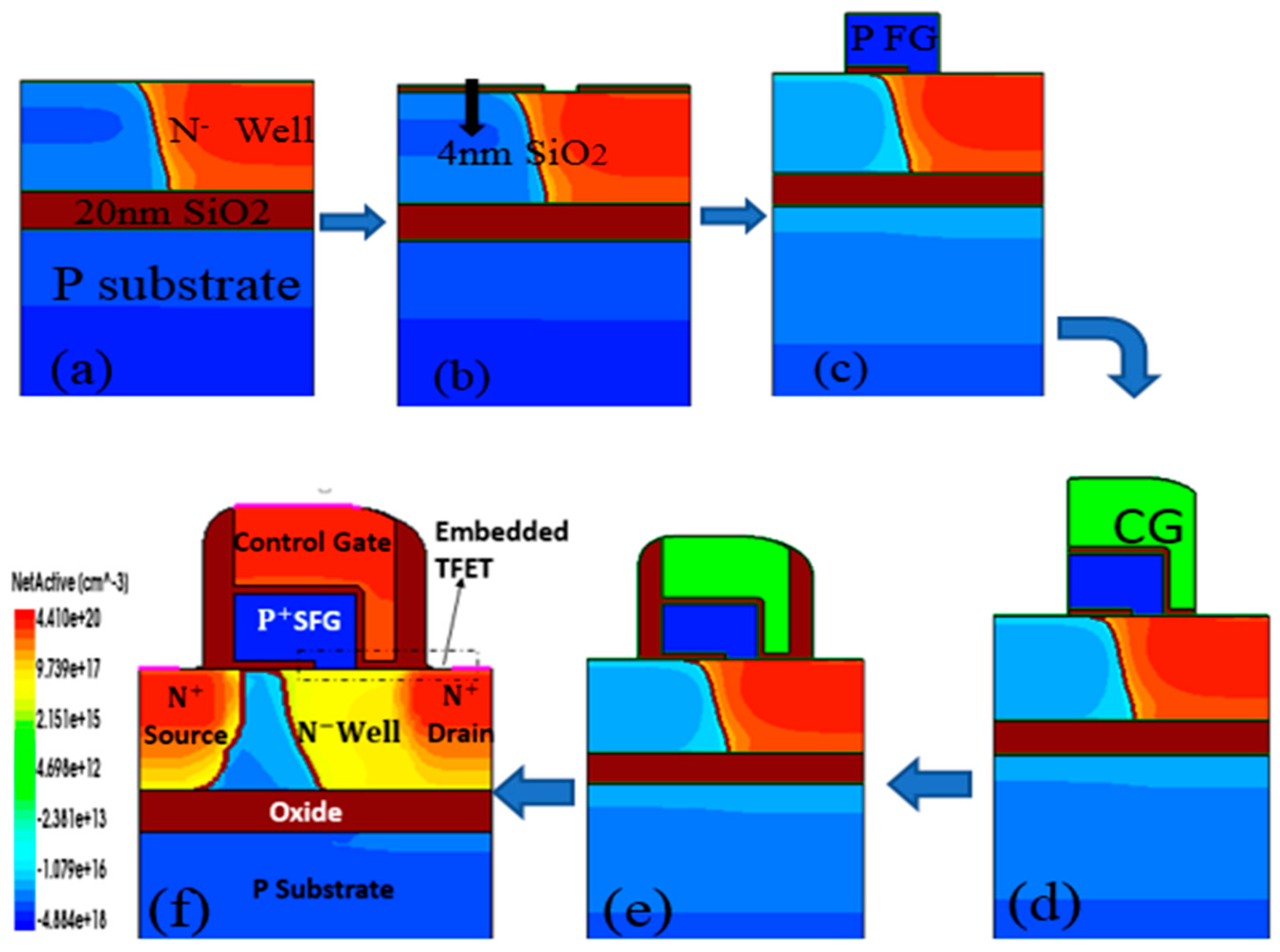

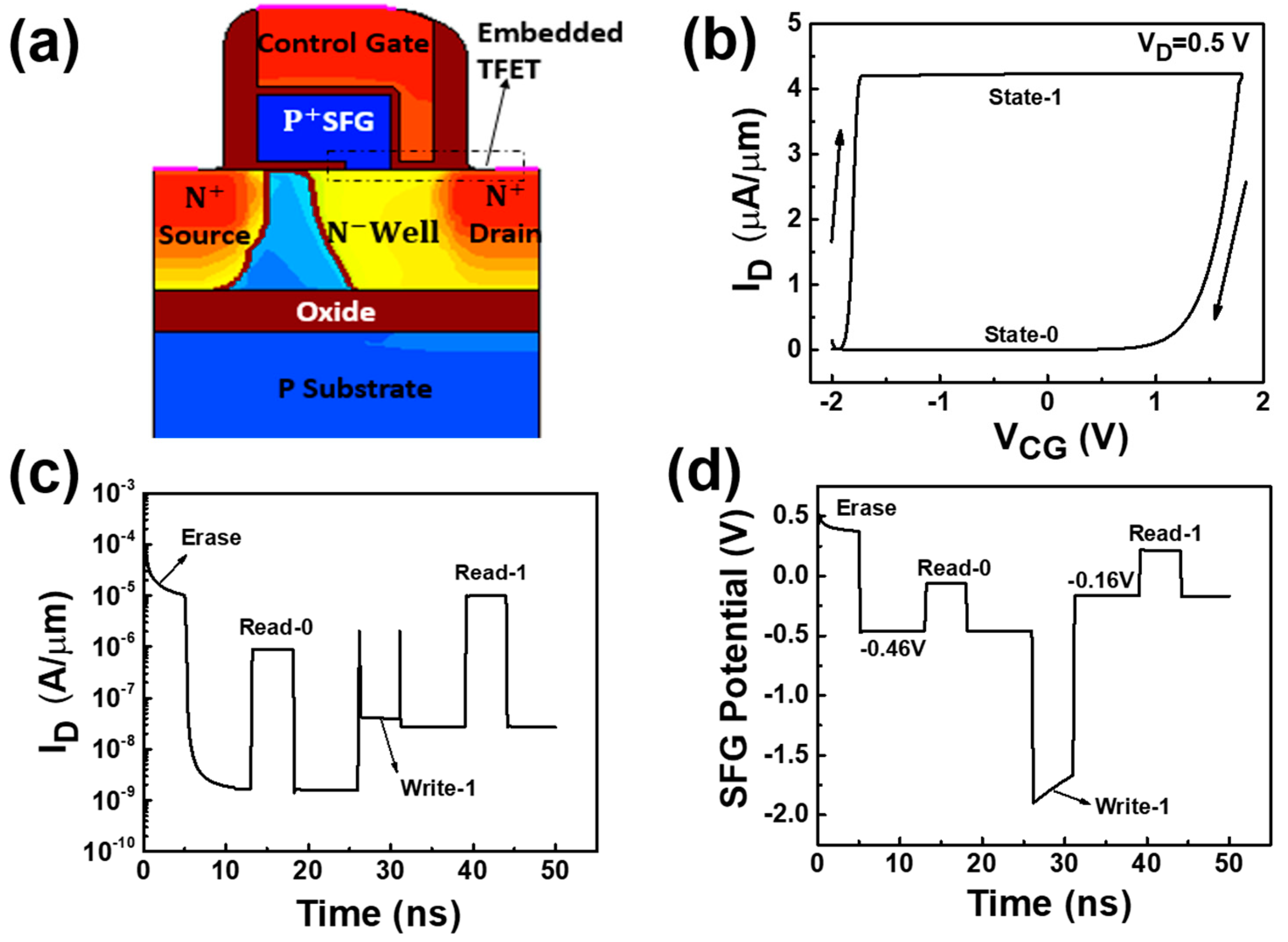

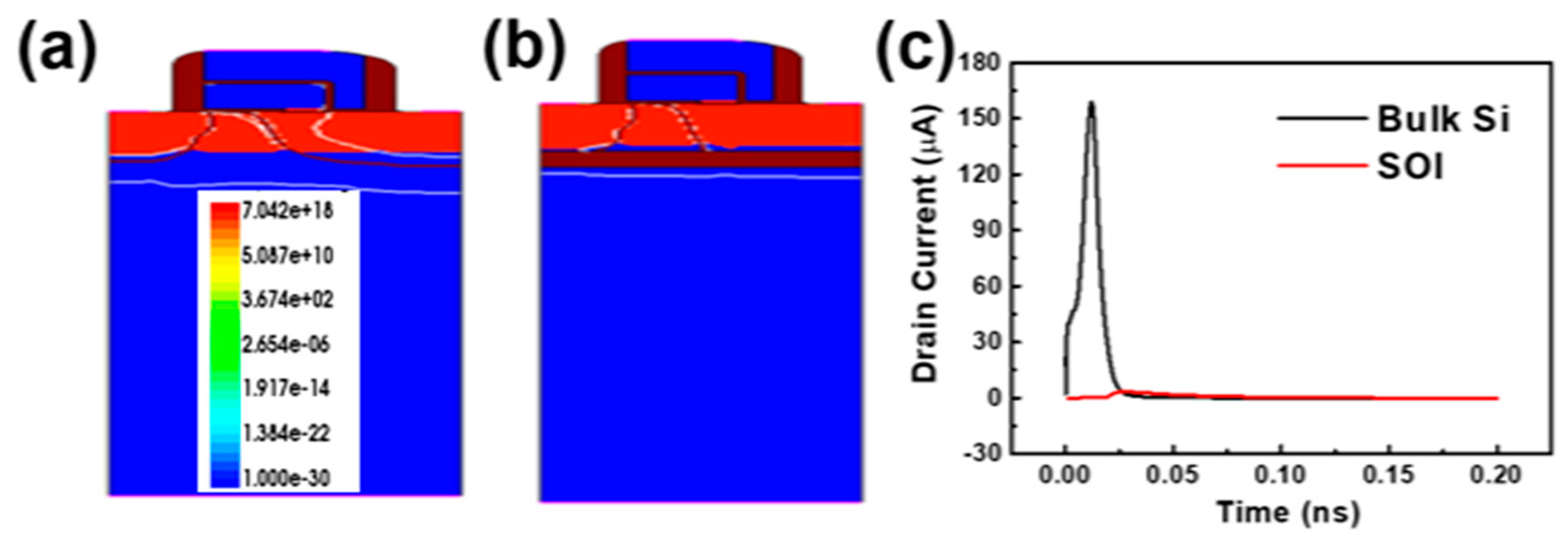

2. Device Structure and Basic Electrical Characteristics

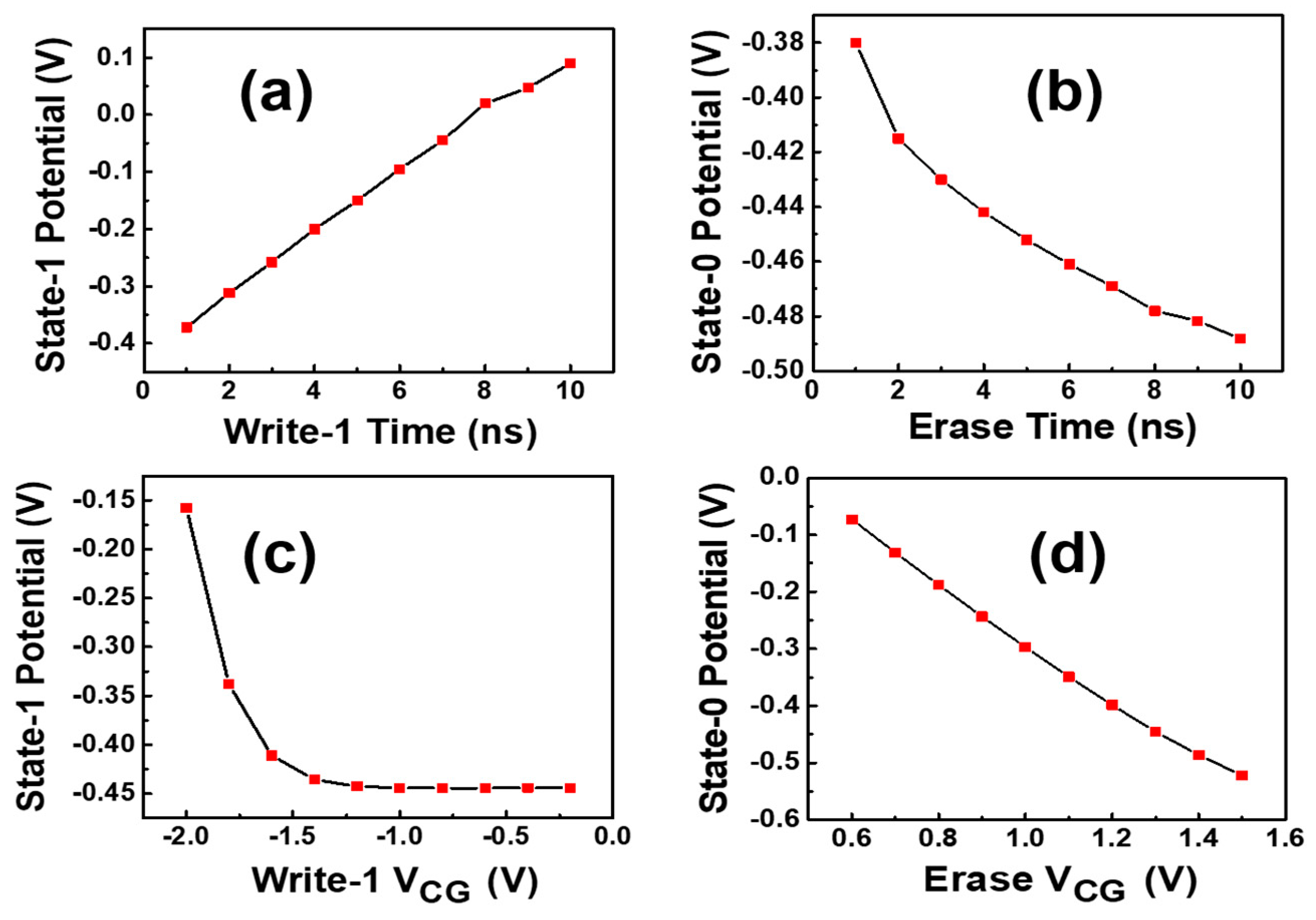

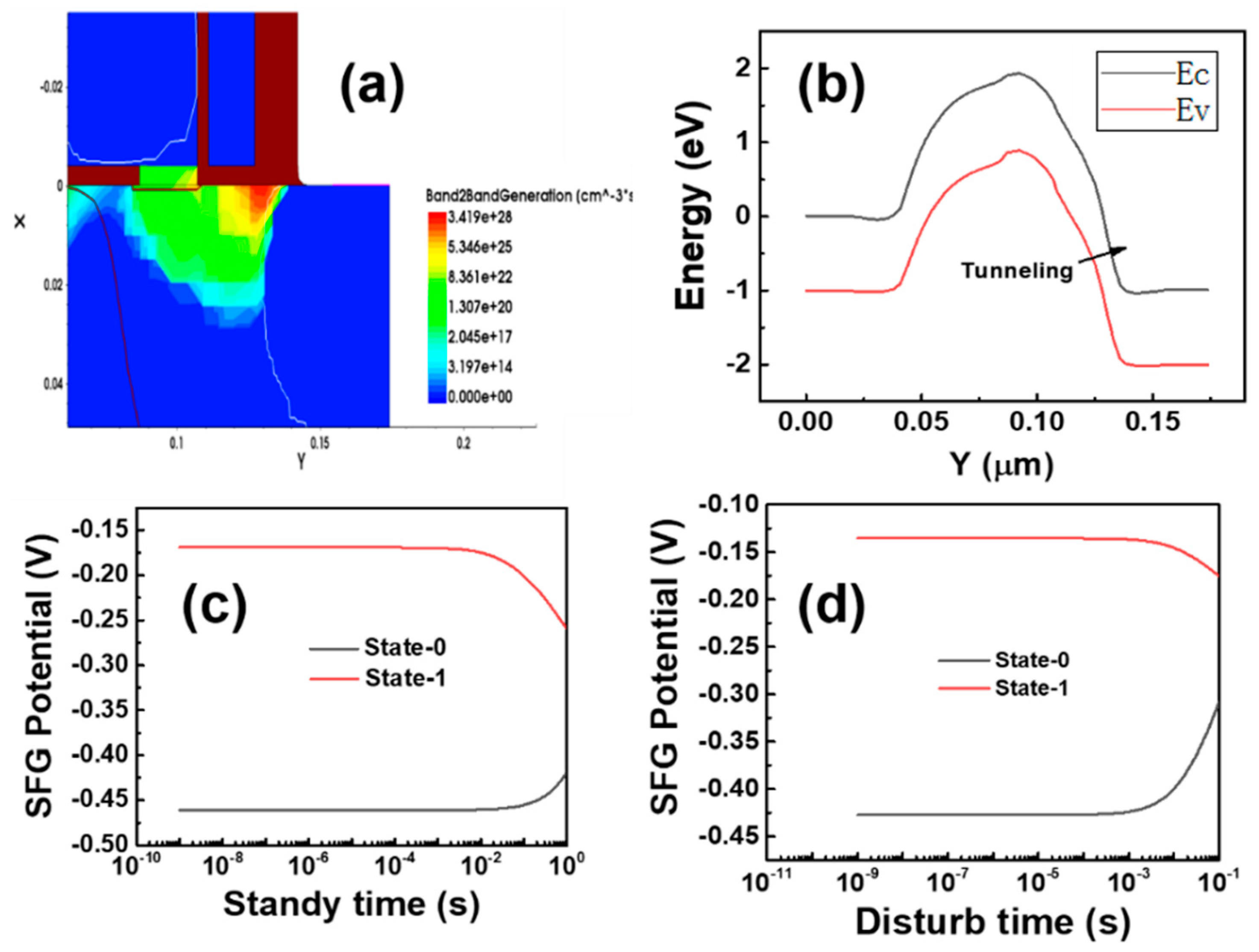

3. Simulation and Results

4. Conclusions

Author Contributions

Funding

Conflicts of Interest

References

- Jiang, S.Y.; Yuan, Y.; Wang, X.; Chen, L.; Zhu, H.; Sun, Q.Q.; Zhang, D.W. A Semi-Floating Gate Transistor with Enhanced Embedded Tunneling Field-Effect Transistor. IEEE Electron Device Lett. 2018, 39, 1497–1499. [Google Scholar]

- Heinrich, A.; Loth, S. A logical use for atoms. Science 2011, 332, 1039–1040. [Google Scholar] [CrossRef] [PubMed]

- THamamoto, T.; Ohsawa, T. Overview and future challenges of floating body RAM (FBRAM) technology for 32 nm technology node and beyond. Solid-State Electron. 2009, 53, 676–683. [Google Scholar] [CrossRef]

- Wang, P.F.; Lin, X.; Liu, L.; Sun, Q.Q.; Zhou, P.; Liu, X.Y.; Liu, W.; Gong, Y.; Zhang, D.W. A semi-floating gate transistor for low- voltage ultrafast memory and sensing operation. Science 2013, 341, 640–643. [Google Scholar] [CrossRef] [PubMed]

- Nirschl, T.; Wang, P.F.; Weber, C.; Sedlmeir, J.; Heinrich, R.; Kakoschke, R.; Schrufer, K.; Holz, J.; Pacha, C.; Schulz, T.; et al. The tunneling field effect transistor (TFET) as an add-on for ultra-low-voltage analog and digital processes. In Proceedings of the IEDM Technical Digest, IEEE International Electron Devices Meeting, San Francisco, CA, USA, 13–15 December 2004; pp. 195–198. [Google Scholar]

- Koga, J.; Toriumi, A. Three-terminal silicon surface junction tunneling device for room temperature operation. IEEE Electron Device Lett. 1999, 20, 529–531. [Google Scholar] [CrossRef]

- Aydin, C.; Zaslavsky, A.; Luryi, S.; Cristoloveanu, S.; Mariolle, D.; Fraboulet, D.; Deleonibus, S. Lateral interband tunneling transistor in silicon-on-insulator. Appl. Phys. Lett. 2004, 84, 1780–1782. [Google Scholar] [CrossRef]

- Hansch, W.; Fink, C.; Schulze, J.; Eisele, I. A vertical MOS-gated Esaki tunneling transistor in silicon. Thin Solid Film 2000, 369, 387–389. [Google Scholar] [CrossRef]

- Anghel, C.; Hraziia, A.; Gupta, A.; Amara, A.; Vladimirescu, A. 30-nm Tunnel FET With Improved Performance and Reduced Ambipolar Current. IEEE Trans. Electron Devices 2011, 58, 1649–1654. [Google Scholar] [CrossRef]

- Hisamoto, D.; Kimura, S.; Kaga, T.; Nakagome, Y.; Isoda, M.; Nishida, T.; Takeda, E. A New Stacked Cell Structure for Giga-Bit DRAMs using Vertical Ultra-Thin SO1 (DELTA) MOSFETs. In Proceedings of the IEDM Tech. Dig., Washington, DC, USA, 8–11 December 1991; pp. 959–961. [Google Scholar]

- Ohtou, T.; Saraya, T.; Hiramoto, T. Variable-Body-Factor SOI MOSFET With Ultrathin Buried Oxide for Adaptive Threshold Voltage and Leakage Control. IEEE Trans. Electron Devices 2008, 55, 40–47. [Google Scholar] [CrossRef]

- Rodriguez, N.; Cristoloveanu, S.; Gamiz, F. Novel Capacitorless 1T-DRAM Cell for 22-nm node Compatible with Bulk and SOI substrates. IEEE Trans. Electron Devices 2011, 58, 2371–2377. [Google Scholar] [CrossRef]

- Okhonin, S.; Nagoga, M.; Sallese, J.; Fazan, P. A Capacitorless 1T-DRAM Cell. IEEE Electron Device Lett. 2002, 23, 85–87. [Google Scholar] [CrossRef]

- Wan, J.; Le Royer, C.; Zaslavsky, A.; Cristoloveanu, S. Progress in Z2-FET 1T-DRAM: Retention time, writing modes, selective array operation, and dual bit storage. Solid State Electron. 2013, 84, 147–154. [Google Scholar] [CrossRef]

| Erase | Write-1 | Read | Standby | |

|---|---|---|---|---|

| VCG (V) | 1.3 | −2 | 0.5 | 0 |

| VD (V) | 0.5 | 1.0 | 1.0 | 0.5 |

| VS (V) | 0 | 0 | 0 | 0 |

| VSub (V) | −0.5 | −0.5 | −0.5 | −0.5 |

| Time (ns) | 4.8 | 4.8 | 4.8 | 7.8 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, H.; Wang, C.; Chen, L.; Zhu, H.; Sun, Q. A Semi-Floating Gate Memory Based on SOI Substrate by TCAD Simulation. Electronics 2019, 8, 1198. https://doi.org/10.3390/electronics8101198

Li H, Wang C, Chen L, Zhu H, Sun Q. A Semi-Floating Gate Memory Based on SOI Substrate by TCAD Simulation. Electronics. 2019; 8(10):1198. https://doi.org/10.3390/electronics8101198

Chicago/Turabian StyleLi, Han, Chen Wang, Lin Chen, Hao Zhu, and Qingqing Sun. 2019. "A Semi-Floating Gate Memory Based on SOI Substrate by TCAD Simulation" Electronics 8, no. 10: 1198. https://doi.org/10.3390/electronics8101198

APA StyleLi, H., Wang, C., Chen, L., Zhu, H., & Sun, Q. (2019). A Semi-Floating Gate Memory Based on SOI Substrate by TCAD Simulation. Electronics, 8(10), 1198. https://doi.org/10.3390/electronics8101198