Impact of Electromagnetic Pulses on N-Type MOSFET Reliability: Experimental Insights

Abstract

1. Introduction

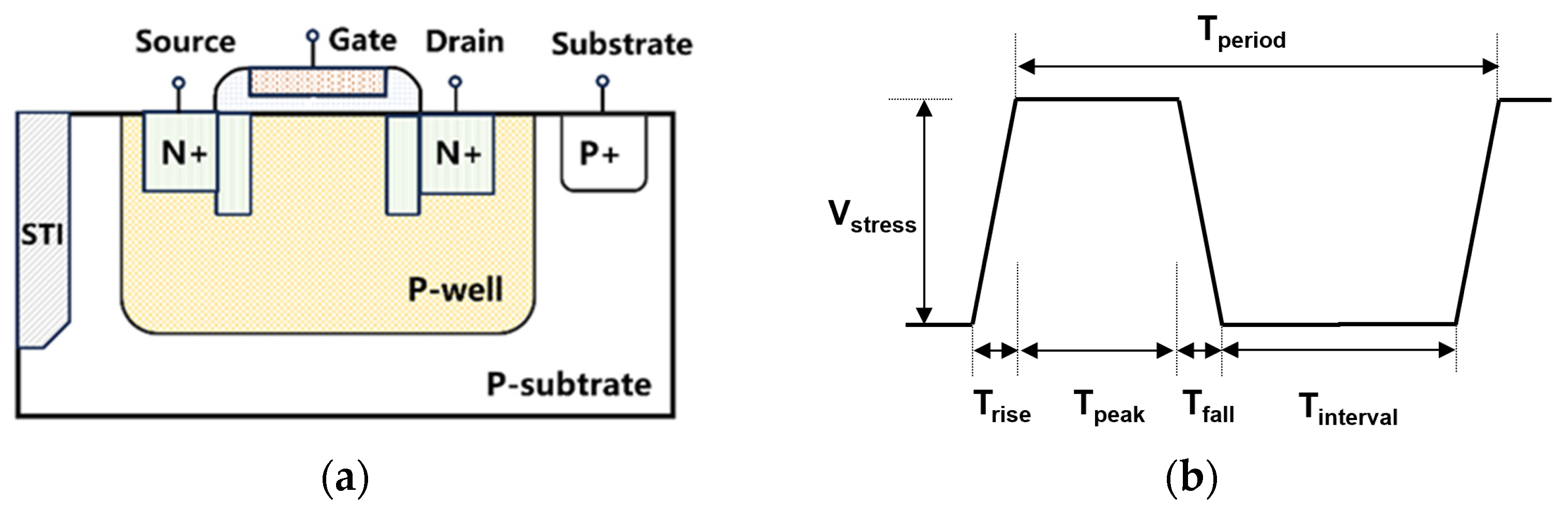

2. Materials and Methods

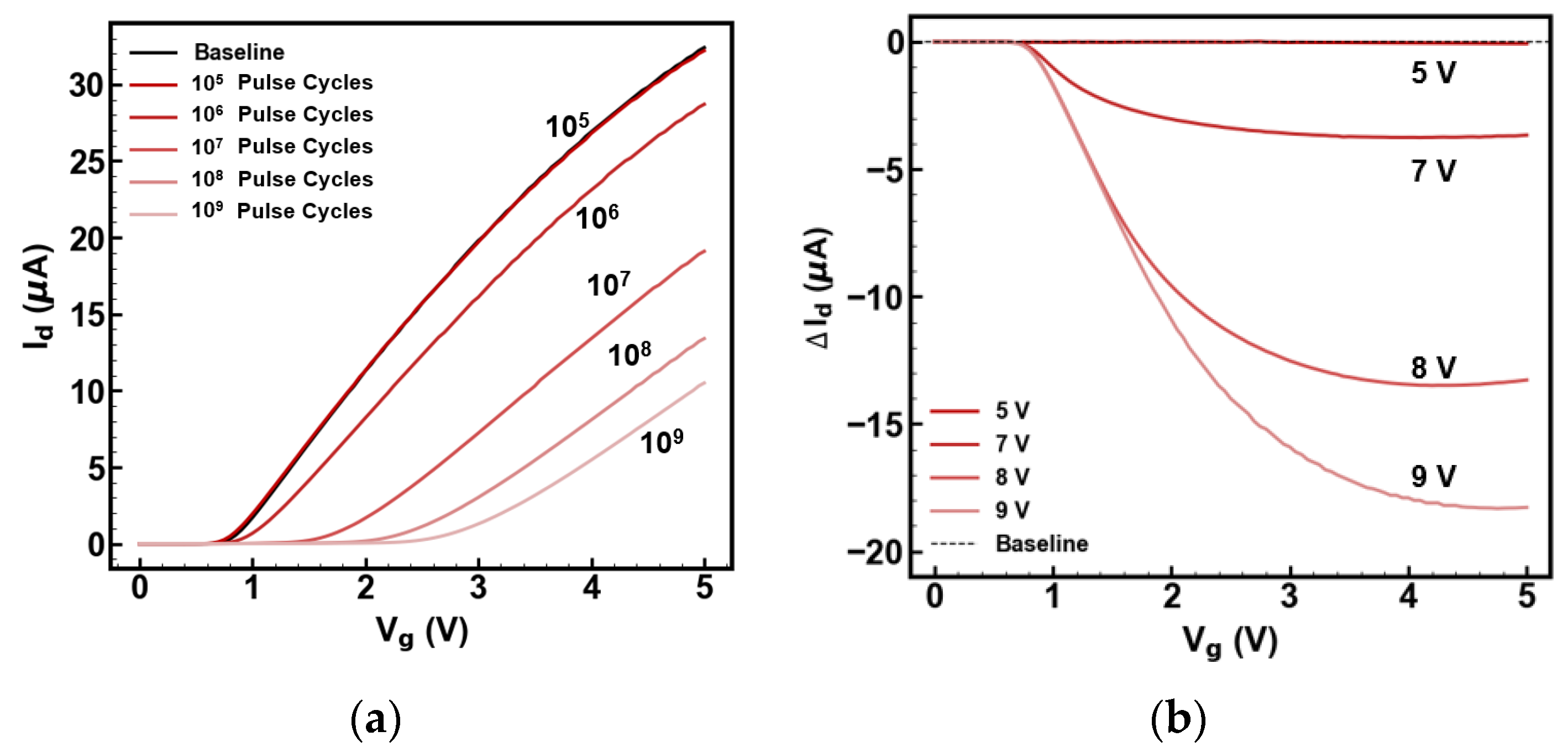

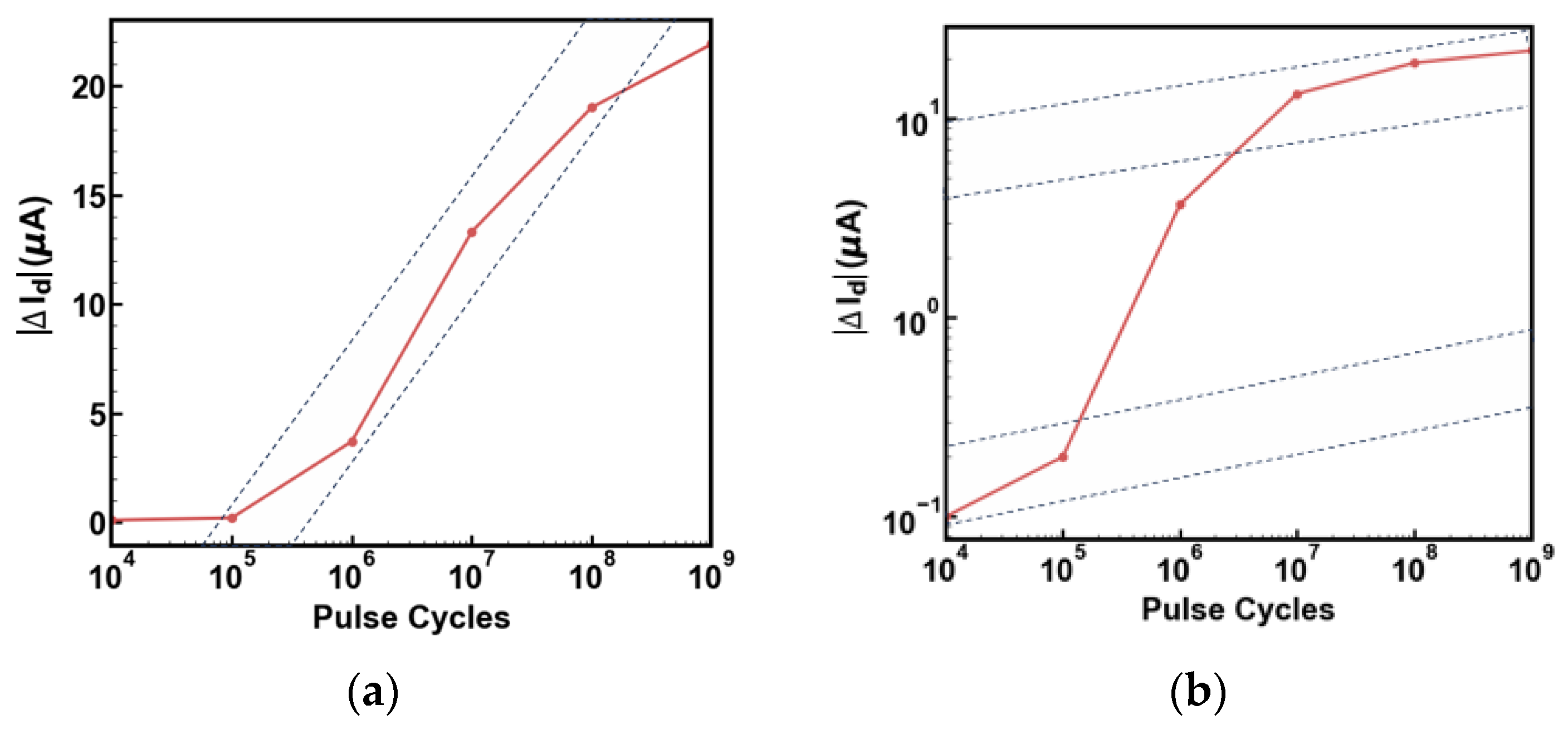

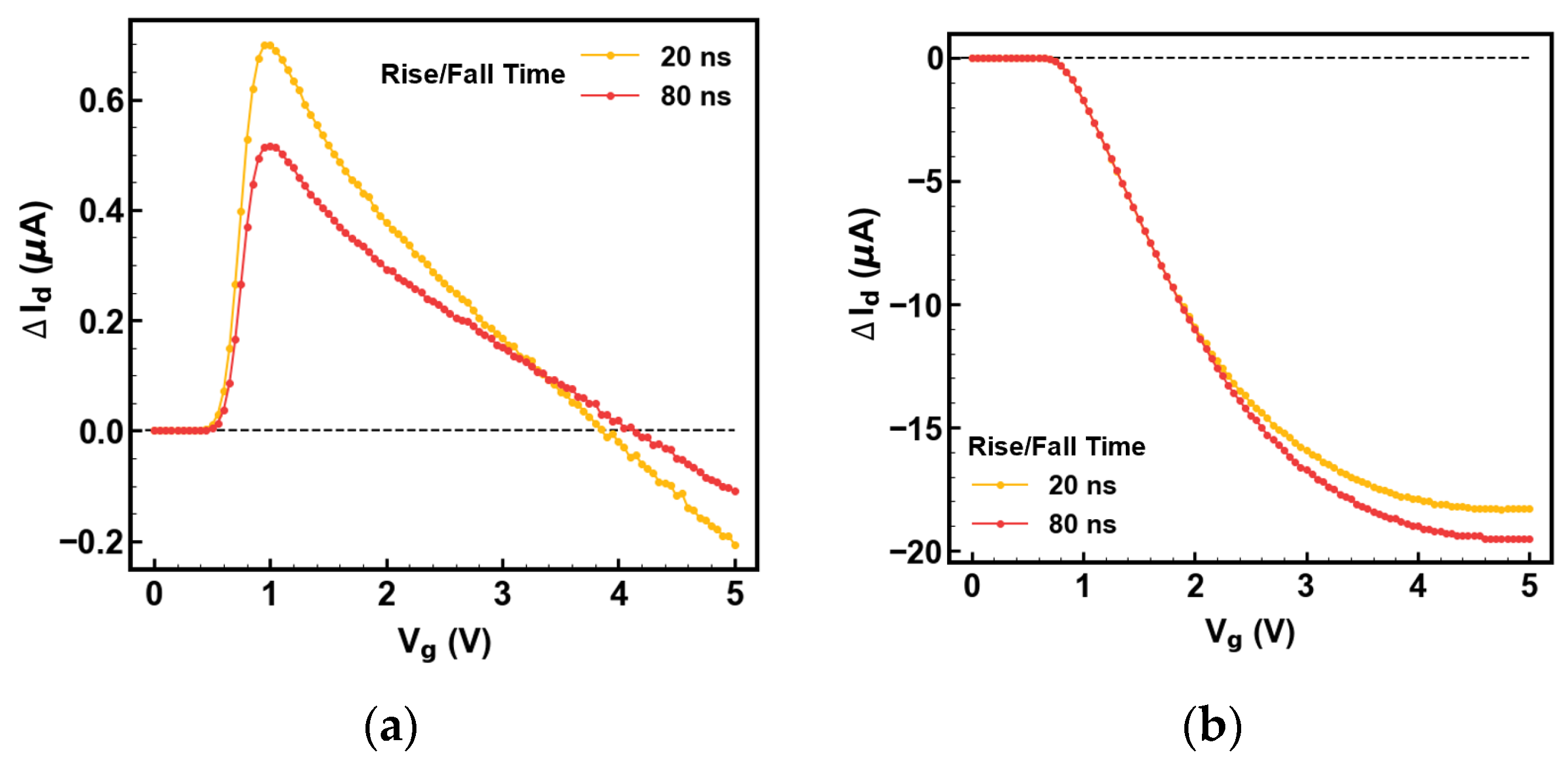

3. Results

4. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- He, X.; Dong, H.; Yang, W.; Li, W. Multi-Source Information Fusion Technology and Its Application in Smart Distribution Power System. Sustainability 2023, 15, 6170. [Google Scholar] [CrossRef]

- Li, M.; Wang, J. 5G and Artificial Intelligence with Multi-Sensor Data Fusion Technology Support Intelligent Operation Monitoring of Power Grid in the Future. In Proceedings of the 2020 Chinese Automation Congress (CAC), Shanghai, China, 6–8 November 2020; IEEE: Piscataway, NJ, USA, 2020; pp. 177–180. [Google Scholar]

- Ma, Z.; Wang, S.; Huang, Q.; Yang, Y. A Review of Radiated EMI Research in Power Electronics Systems. IEEE J. Emerg. Sel. Top. Power Electron. 2023, 12, 675–694. [Google Scholar] [CrossRef]

- Radasky, W.A.; Hoad, R. An Overview of the Impacts of Three High Power Electromagnetic (HPEM) Threats on Smart Grids. In Proceedings of the International Symposium on Electromagnetic Compatibility-EMC EUROPE, Rome, Italy, 17–21 September 2012; IEEE: Piscataway, NJ, USA, 2012; pp. 1–6. [Google Scholar]

- Shadare, A.E.; Sadiku, M.N.O.; Musa, S.M. Electromagnetic Compatibility Issues in Critical Smart Grid Infrastructure. IEEE Electromagn. Compat. Mag. 2017, 6, 63–70. [Google Scholar] [CrossRef]

- Fiori, F. EMI Susceptibility: The Achilles’ Heel of Smart Power ICs. IEEE Electromagn. Compat. Mag. 2015, 4, 101–105. [Google Scholar] [CrossRef]

- McPherson, J.W. Glaser Reliability Physics and Engineering; Springer: Berlin/Heidelberg, Germany, 2010; ISBN 1441963480. [Google Scholar]

- Tang, L.-C.; Yang, G.Y.; Xie, M. Planning of Step-Stress Accelerated Degradation Test. In Proceedings of the Annual Symposium Reliability and Maintainability, 2004-RAMS, Los Angeles, CA, USA, 26–29 January 2004; IEEE: Piscataway, NJ, USA, 2004; pp. 287–292. [Google Scholar]

- Saha, S.; Celaya, J.R.; Vashchenko, V.; Mahiuddin, S.; Goebel, K.F. Accelerated Aging with Electrical Overstress and Prognostics for Power MOSFETs. In Proceedings of the IEEE 2011 EnergyTech, Cleveland, OH, USA, 25–26 May 2011; IEEE: Piscataway, NJ, USA, 2011; pp. 1–6. [Google Scholar]

- Valentine, N.; Das, D.; Sood, B.; Pecht, M. Failure Analyses of Modern Power Semiconductor Switching Devices. In Proceedings of the International Symposium on Microelectronics; International Microelectronics Assembly and Packaging Society: Pittsburgh, PA, USA, 2015; Volume 2015, pp. 690–695. [Google Scholar]

- Sule, N.H.; Powell, T.; Hemmady, S.; Zarkesh-Ha, P. Predicting the Tolerance of Extreme Electromagnetic Interference on MOSFETs. In Proceedings of the 2018 IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Hong Kong, China, 8–11 July 2018; IEEE: Piscataway, NJ, USA, 2018; pp. 597–601. [Google Scholar]

- Iliadis, A.A.; Kim, K. Theoretical Foundation for Upsets in CMOS Circuits Due to High-Power Electromagnetic Interference. IEEE Trans. Device Mater. Reliab. 2010, 10, 347–352. [Google Scholar] [CrossRef]

- Tamersit, K.; Moaiyeri, M.; Jooq, M. Leveraging Negative Capacitance Ferroelectric Materials for Performance Boosting of Sub-10 Nm Graphene Nanoribbon Field-Effect Transistors: A Quantum Simulation Study. Nanotechnology 2022, 33, 46. [Google Scholar] [CrossRef] [PubMed]

- Khan, Q.; Refaat, S.S.; Abu-Rub, H.; Toliyat, H.A. Partial Discharge Detection and Diagnosis in Gas Insulated Switchgear: State of the Art. IEEE Electr. Insul. Mag. 2019, 35, 16–33. [Google Scholar] [CrossRef]

- Wang, X.; Li, Z.; Huang, Y.; Zeng, R.; Yao, L.; Sasse, C.; Han, M. Reliability Test of Using 802.11 b Technology in Switchgear for Measurement and Control. In Proceedings of the 2006 International Conference on Power System Technology, Chongqing, China, 22–26 October 2006; IEEE: Piscataway, NJ, USA, 2006; pp. 1–6. [Google Scholar]

- Voldman, S.H. ESD: Circuits and Devices; John Wiley & Sons: Hoboken, NJ, USA, 2015; ISBN 1118954467. [Google Scholar]

- Esseni, D.; Bude, J.D.; Selmi, L. On Interface and Oxide Degradation in VLSI MOSFETs. II. Fowler-Nordheim Stress Regime. IEEE Trans. Electron Devices 2002, 49, 254–263. [Google Scholar] [CrossRef]

- Penzin, O.; Haggag, A.; McMahon, W.; Lyumkis, E.; Hess, K. MOSFET Degradation Kinetics and Its Simulation. IEEE Trans. Electron Devices 2003, 50, 1445–1450. [Google Scholar] [CrossRef]

- Kuhn, K.J.; Giles, M.D.; Becher, D.; Kolar, P.; Kornfeld, A.; Kotlyar, R.; Ma, S.T.; Maheshwari, A.; Mudanai, S. Process Technology Variation. IEEE Trans. Electron Devices 2011, 58, 2197–2208. [Google Scholar] [CrossRef]

- Li, Y.; Hwang, C.-H.; Li, T.-Y.; Han, M.-H. Process-Variation Effect, Metal-Gate Work-Function Fluctuation, and Random-Dopant Fluctuation in Emerging CMOS Technologies. IEEE Trans. Electron Devices 2009, 57, 437–447. [Google Scholar] [CrossRef]

- Hu, C. Hot-Electron Effects in MOSFETs. In Proceedings of the 1983 International Electron Devices Meeting, Washington, DC, USA, 5–7 December 1983; IEEE: Piscataway, NJ, USA, 1983; pp. 176–181. [Google Scholar]

- Kufluoglu, H.; Alam, M.A. A Generalized Reaction–Diffusion Model with Explicit H–H2 Dynamics for Negative-Bias Temperature-Instability (NBTI) Degradation. IEEE Trans. Electron Devices 2007, 54, 1101–1107. [Google Scholar] [CrossRef]

- Allers, K.-H. Prediction of Dielectric Reliability from I–V Characteristics: Poole–Frenkel Conduction Mechanism Leading to √E Model for Silicon Nitride MIM Capacitor. Microelectron. Reliab. 2004, 44, 411–423. [Google Scholar] [CrossRef]

- Neamen, D.A. Semiconductor Physics and Devices: Basic Principles; McGraw-Hill Companies, Inc.: New York, NY, USA, 2003. [Google Scholar]

- Hastings, A. The Art of Analog Layout; Prentice Hall: Hoboken, NJ, USA, 2001. [Google Scholar]

- Pantelides, S.T.; Tsetseris, L.; Rashkeev, S.N.; Zhou, X.J.; Fleetwood, D.M.; Schrimpf, R.D. Hydrogen in MOSFETs–A Primary Agent of Reliability Issues. Microelectron. Reliab. 2007, 47, 903–911. [Google Scholar] [CrossRef]

- Stahlbush, R.E.; Cartier, E. Interface Defect Formation in MOSFETs by Atomic Hydrogen Exposure. IEEE Trans. Nucl. Sci. 1994, 41, 1844–1853. [Google Scholar] [CrossRef]

- Sah, C.T. Models and Experiments on Degradation of Oxidized Silicon. Solid-State Electron. 1990, 33, 147–167. [Google Scholar] [CrossRef]

- Cartier, E.; Stathis, J.H.; Buchanan, D.A. Passivation and Depassivation of Silicon Dangling Bonds at the Si/SiO2 Interface by Atomic Hydrogen. Appl. Phys. Lett. 1993, 63, 1510–1512. [Google Scholar] [CrossRef]

- Watanabe, N.; Omura, A.; Nohira, H.; Hattori, T. Structural Origin of Carrier Trap Levels at SiO2/Si Interface. Solid State Devices Mater. 1998, 130–131. [Google Scholar] [CrossRef]

- Sasse, G.T.; Kuper, F.G.; Schmitz, J. MOSFET Degradation under RF Stress. IEEE Trans. Electron Devices 2008, 55, 3167–3174. [Google Scholar] [CrossRef]

- Fukuda, Y.; Yamada, T.; Sawada, M. ESD Parameter Extraction by TLP Measurement. In Proceedings of the 2009 31st EOS/ESD Symposium, Anaheim, CA, USA, 30 August–4 September 2009; IEEE: Piscataway, NJ, USA, 2009; pp. 1–6. [Google Scholar]

- Chen, S.L.; Lee, M.H. TLP Characterization and Leakage-Biasing-Voltage (VLB) Correlations in MOSFET Measurements. In Proceedings of the 2014 International Symposium on Computer, Consumer and Control, Taichung, Taiwan, 10–12 June 2014; IEEE: Piscataway, NJ, USA, 2014; pp. 199–202. [Google Scholar]

- Hsu, F.-C.; Chiu, K.-Y. Temperature Dependence of Hot-Electron-Induced Degradation in MOSFET’s. IEEE Electron Device Lett. 1984, 5, 148–150. [Google Scholar] [CrossRef]

- Lee, K.T.; Kang, C.Y.; Yoo, O.S.; Choi, R.; Lee, B.H.; Lee, J.C.; Lee, H.-D.; Jeong, Y.-H. PBTI-Associated High-Temperature Hot Carrier Degradation of NMOSFETs with Metal-Gate/High-k Dielectrics. IEEE Electron Device Lett. 2008, 29, 389–391. [Google Scholar] [CrossRef]

- Semenov, O.; Vassighi, A.; Sachdev, M. Impact of Self-Heating Effect on Long-Term Reliability and Performance Degradation in CMOS Circuits. IEEE Trans. Device Mater. Reliab. 2006, 6, 17–27. [Google Scholar] [CrossRef]

- Prakash, O.; Dabhi, C.K.; Chauhan, Y.S.; Amrouch, H. Transistor Self-Heating: The Rising Challenge for Semiconductor Testing. In Proceedings of the 2021 IEEE 39th VLSI Test Symposium (VTS), San Diego, CA, USA, 25–28 April 2021; IEEE: Piscataway, NJ, USA, 2021; pp. 1–7. [Google Scholar]

| No. | Experimental Equipment | Function Description |

|---|---|---|

| 1 | Transmission Line Pulse Generator: ES622, ESDEMC Technology, Rolla, MO, USA | Generation of stress pulses for the whole experiment. |

| 2 | Mixed Signal Oscilloscope: MSO-X 3104, Keysight Technologies, Santa Rosa, CA, USA | Characterization of TLP waveform during the experiment. |

| 3 | Probe Station: TS3000-SE, MPI Corporation, Mercer, NJ, USA | Providing a stable thermal environment for temperature-controlled device testing. |

| 4 | Semiconductor Device Analyzer: B1500A, Keysight Technologies, Santa Rosa, CA, USA | Characterization of devices’ pre- and post-stress electrical performance. |

| Experiment No. | Vstress/V | Trise/ns | Tpeak/ns | Tfall/ns | Tinterval/ns | Pulse Cycles | Temperature/°C |

|---|---|---|---|---|---|---|---|

| 1 | 8 | 20 | 150 | 20 | 160 | 105~109 | 25 |

| 2 | 5~9 | 20 | 150 | 20 | 160 | 107 | 25 |

| 3 | 7 | 20 | 150 | 20 | 160 | 103~5 × 108 | 25 |

| 8 | 20 | 150 | 20 | 160 | 103~5 × 108 | 25 | |

| 9 | 20 | 150 | 20 | 160 | 103~5 × 108 | 25 | |

| 11 | 20 | 150 | 20 | 160 | 103~105 | 25 | |

| 4 | 9 | 20 | 150 | 20 | 160 | 104 | 25 |

| 9 | 20 | 150 | 20 | 160 | 107 | 25 | |

| 9 | 80 | 150 | 80 | 160 | 104 | 25 | |

| 9 | 80 | 150 | 80 | 160 | 107 | 25 | |

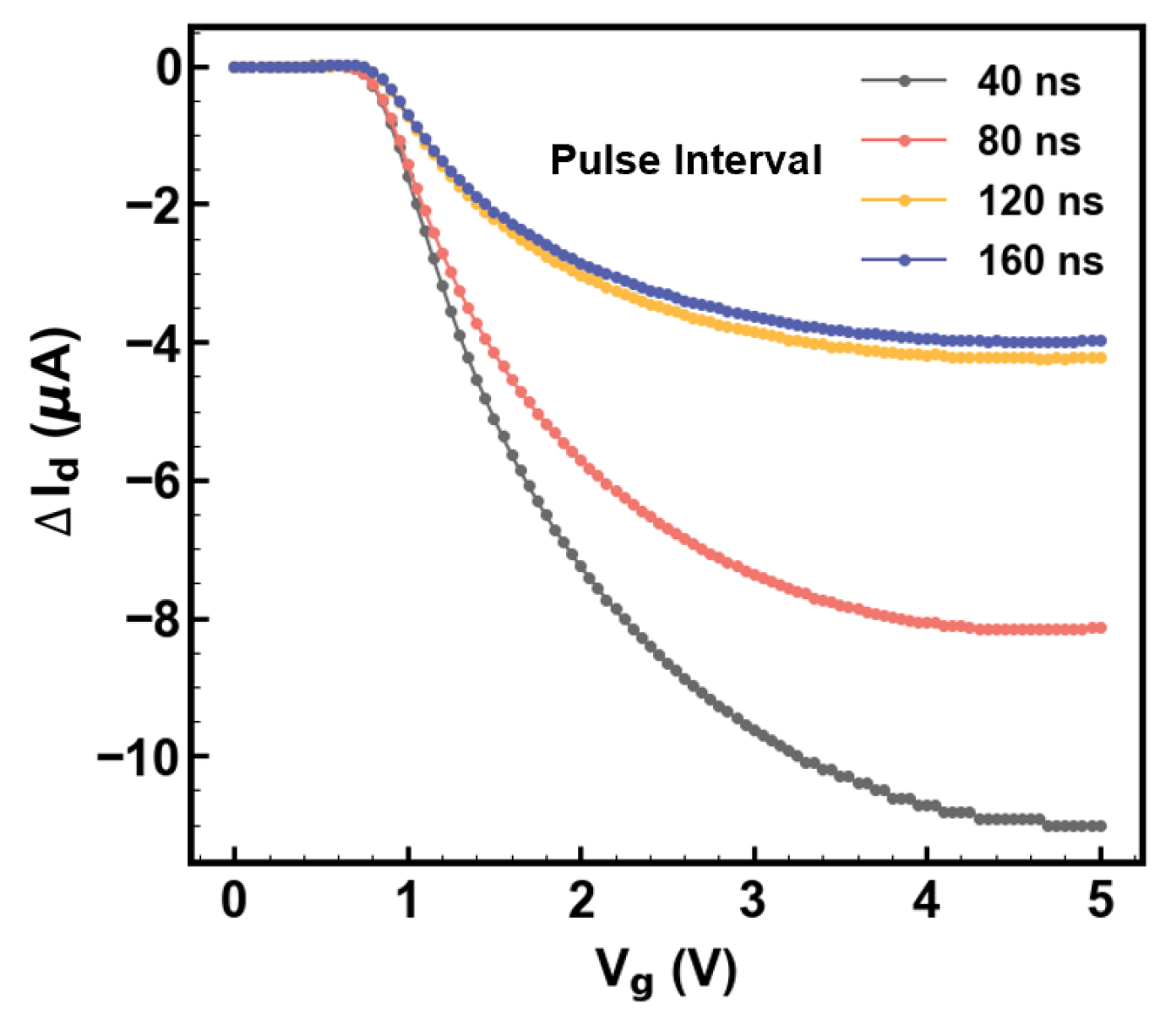

| 5 | 9 | 20 | 150 | 20 | 40~160 | 105 | 25 |

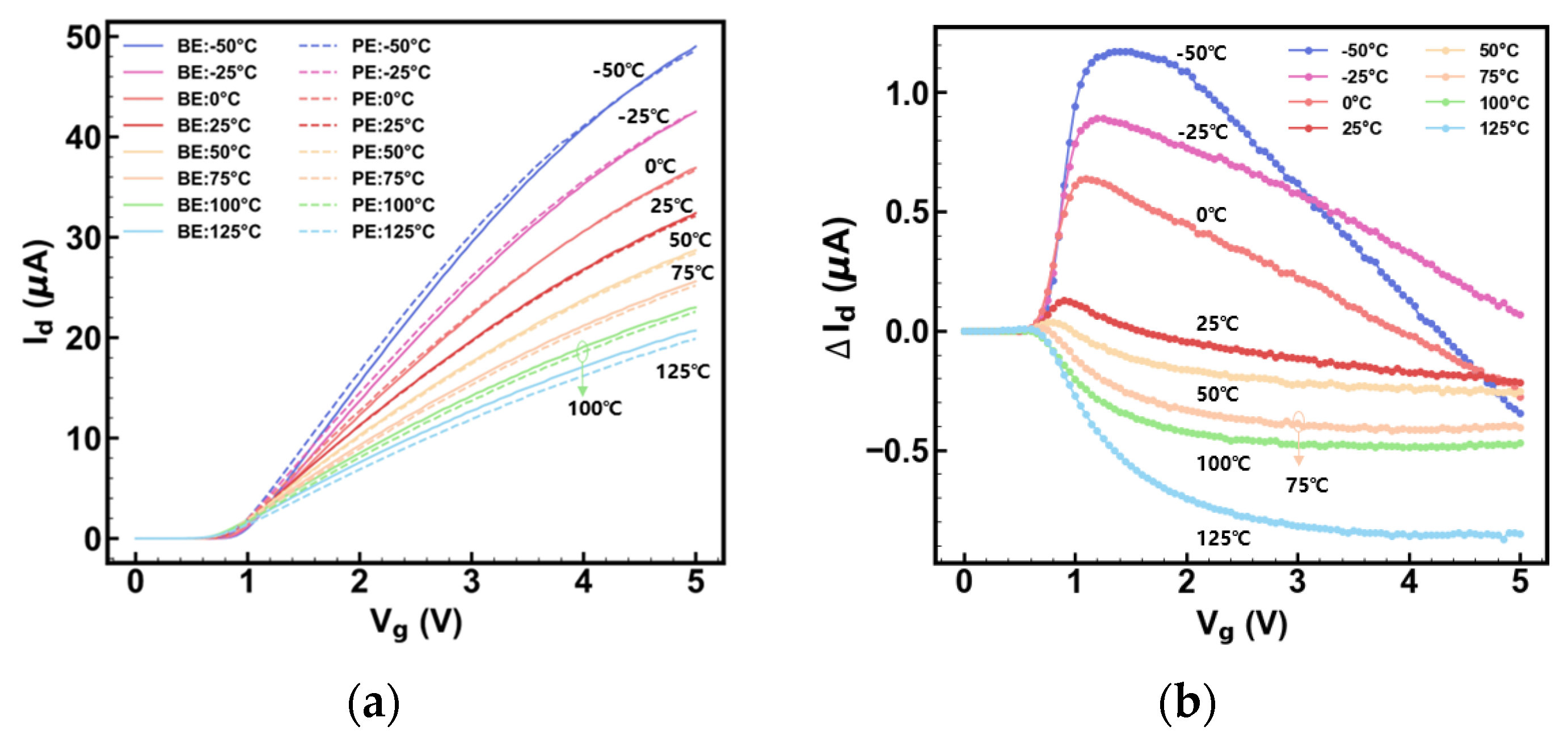

| 6 | 7 | 20 | 150 | 20 | 160 | 106 | −50~125 |

| No. | Degradation Topics | Causes | Theoretical Models | Electrical Parameter Deviation with Respect to Time |

|---|---|---|---|---|

| 1 | Hot Carrier Injection | Si–O bond breakage caused by the redirection of high-energy carriers from the channel to the oxide. | Hot Carrier Injection Model [21] | Changes follow a power-law relation. |

| 2 | Bias Temperature Instability | Si–H bond breakage caused by a hole collection at the heterointerface under a perpendicular gate electric field. | Reaction-Diffusion Model [22] | Changes follow a power-law relation. |

| 3 | Time-Dependent Dielectric Breakdown | Si–O bond breakage caused by electron tunneling in the oxide. | Poole–Frenkel Model [23] | Changes follow a power-law relation. |

| 4 | This Work | Multi-physical contributions are considered, including both S–H bond and Si–O bond breakages under electrical pulse conditions. | Under Discussion | Changes follow a logarithmic relation. |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Zhu, Y.; Zhao, D.; Dai, F.; Chen, Y.; Liu, F.; Wu, B.; Zhao, Y.; Ren, B.; Wang, Y.; Liang, Y.; et al. Impact of Electromagnetic Pulses on N-Type MOSFET Reliability: Experimental Insights. Electronics 2025, 14, 1937. https://doi.org/10.3390/electronics14101937

Zhu Y, Zhao D, Dai F, Chen Y, Liu F, Wu B, Zhao Y, Ren B, Wang Y, Liang Y, et al. Impact of Electromagnetic Pulses on N-Type MOSFET Reliability: Experimental Insights. Electronics. 2025; 14(10):1937. https://doi.org/10.3390/electronics14101937

Chicago/Turabian StyleZhu, Yaxing, Dongyan Zhao, Fei Dai, Yanning Chen, Fang Liu, Bo Wu, Yang Zhao, Bocong Ren, Yanhong Wang, Yingzong Liang, and et al. 2025. "Impact of Electromagnetic Pulses on N-Type MOSFET Reliability: Experimental Insights" Electronics 14, no. 10: 1937. https://doi.org/10.3390/electronics14101937

APA StyleZhu, Y., Zhao, D., Dai, F., Chen, Y., Liu, F., Wu, B., Zhao, Y., Ren, B., Wang, Y., Liang, Y., & Wang, J. (2025). Impact of Electromagnetic Pulses on N-Type MOSFET Reliability: Experimental Insights. Electronics, 14(10), 1937. https://doi.org/10.3390/electronics14101937