A High-Speed 8-Bit Single-Channel SAR ADC with Tailored Bit Intervals and Split Capacitors †

Abstract

1. Introduction

- 1.

- This paper provides a thorough analysis of the constraints that determine asynchronous time intervals during the conversion phase, and a brand-new delay adjustment logic for TBI is proposed, which serves as the basis for proposing an approach for high-speed SAR-ADC circuits.

- 2.

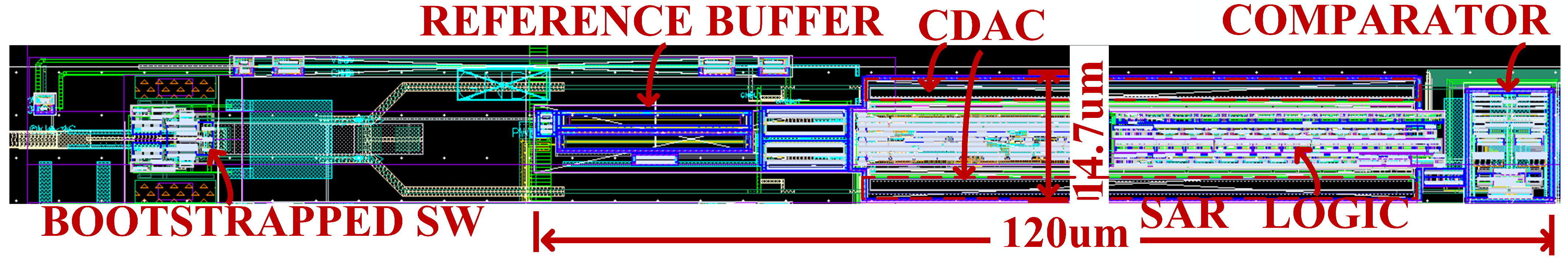

- Based on the analysis, a high-speed SAR ADC is designed, presenting an 8-bit SAR ADC circuit implementation. Inverted dynamic latch pairs and early reset of capacitors are employed to improve speed. Split capacitive digital-to-analog converters (CDACs) by the latch pairs are employed to mitigate common-mode voltage shifts.

- 3.

- The post-layout simulation shows an effective number of bits (ENOB) of 7.20 bits at Typical–Typical (TT) 25 °C with a power consumption of 6.94 mW. With a sampling rate exceeding 1 GS/s across all process corners, our circuit also has the potential for application in high-speed multi-channel time-interleaved ADCs.

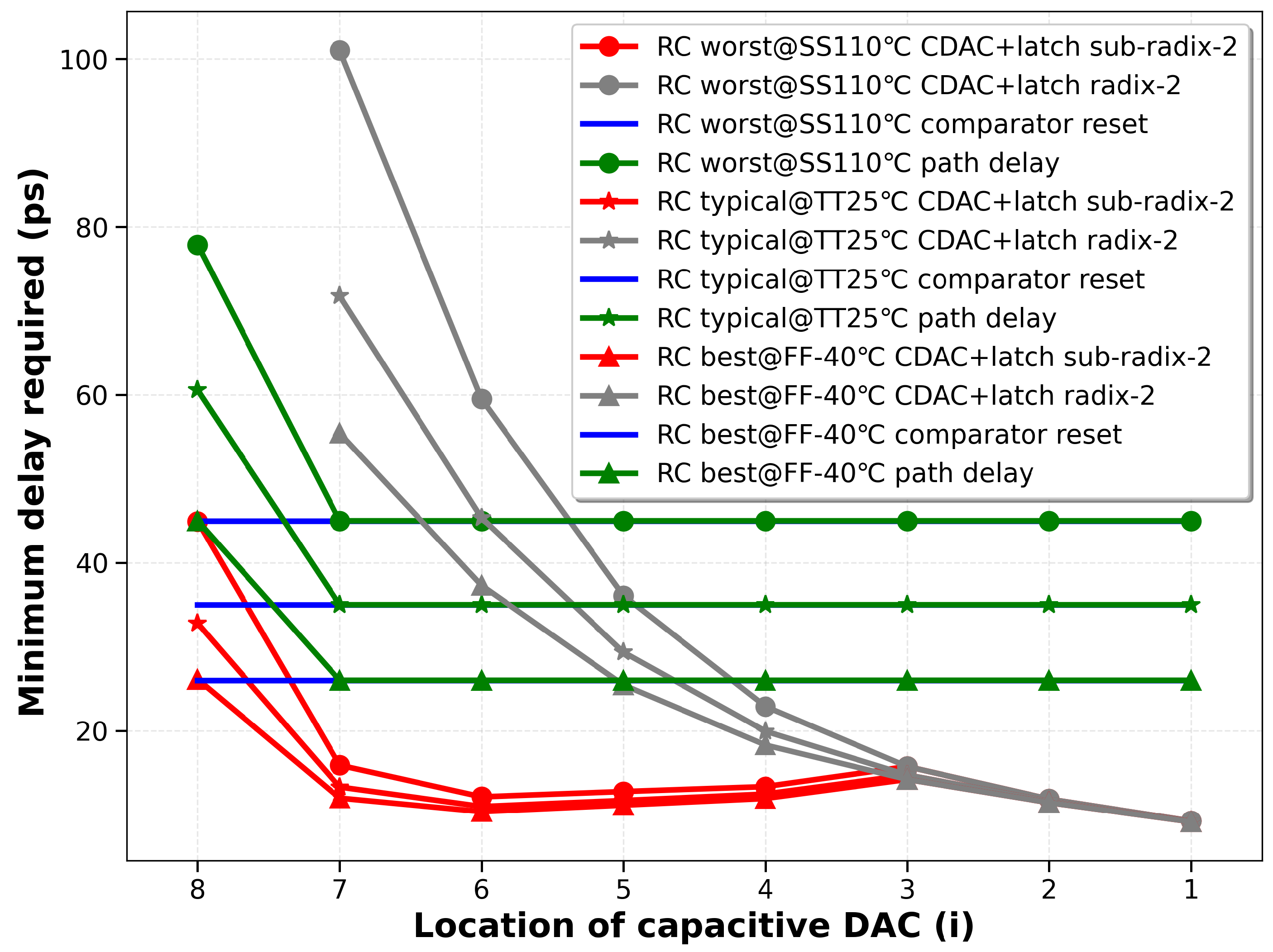

2. Analysis of CDAC Settling

3. Circuit Implementation

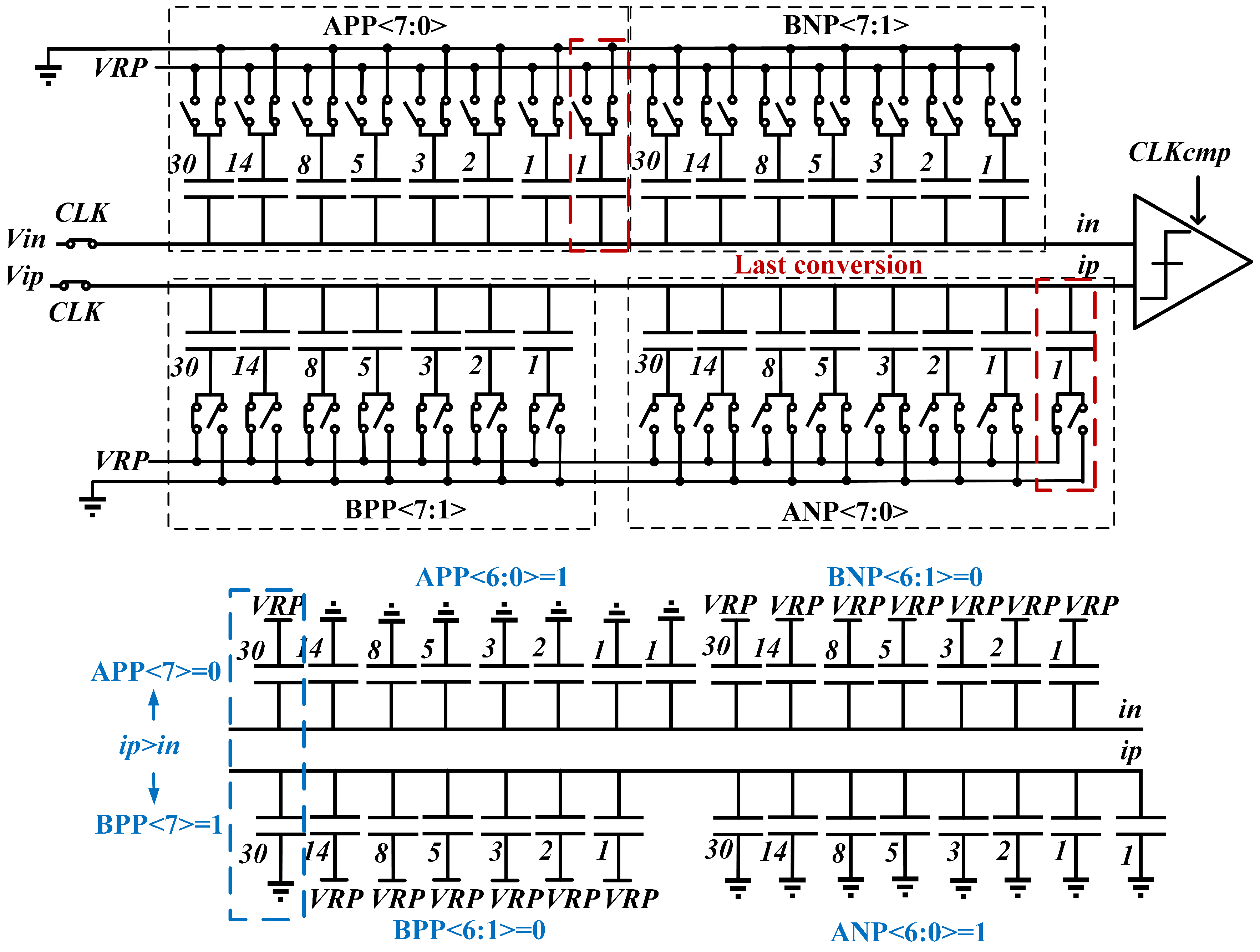

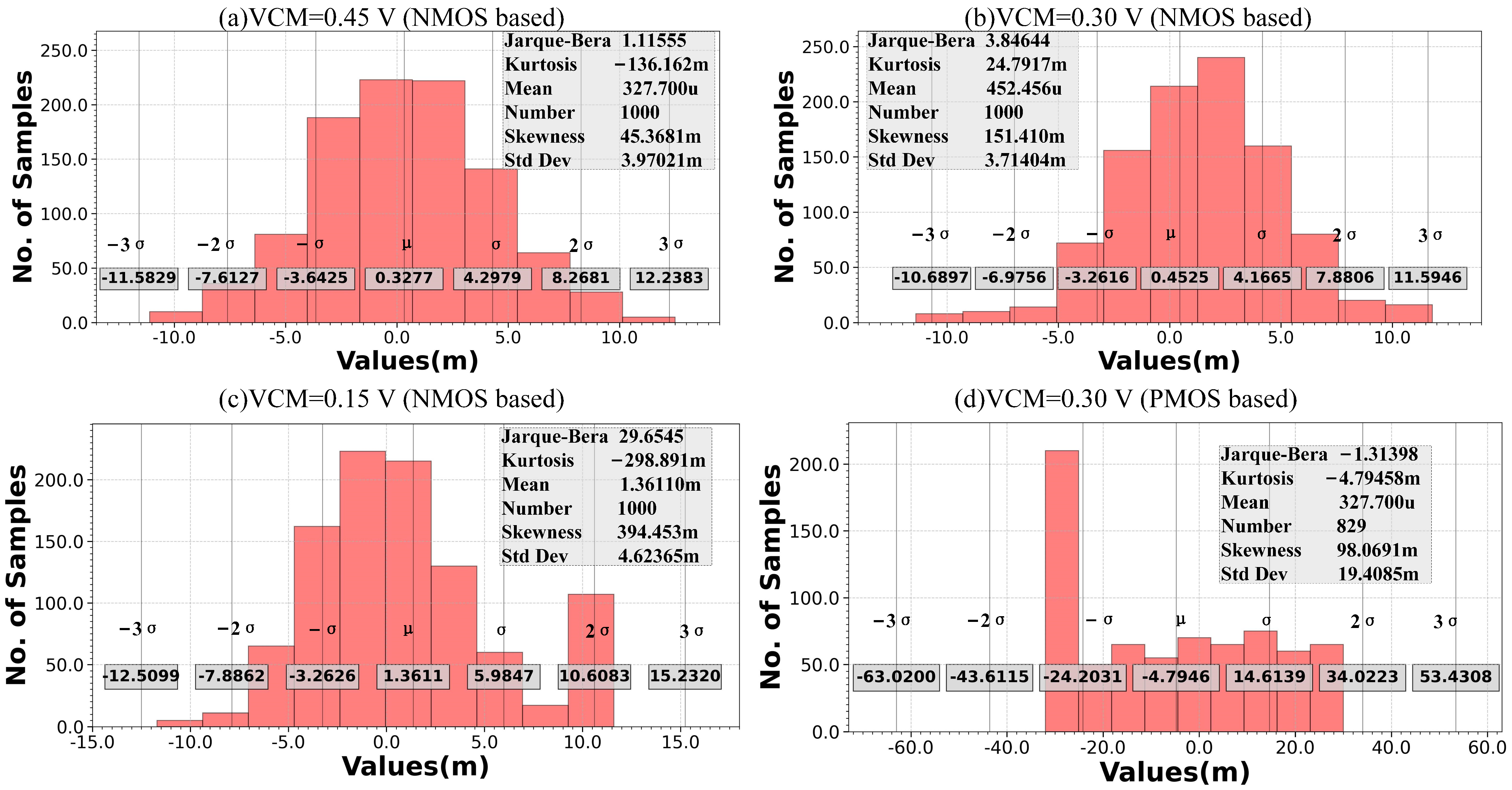

3.1. Split Capacitors

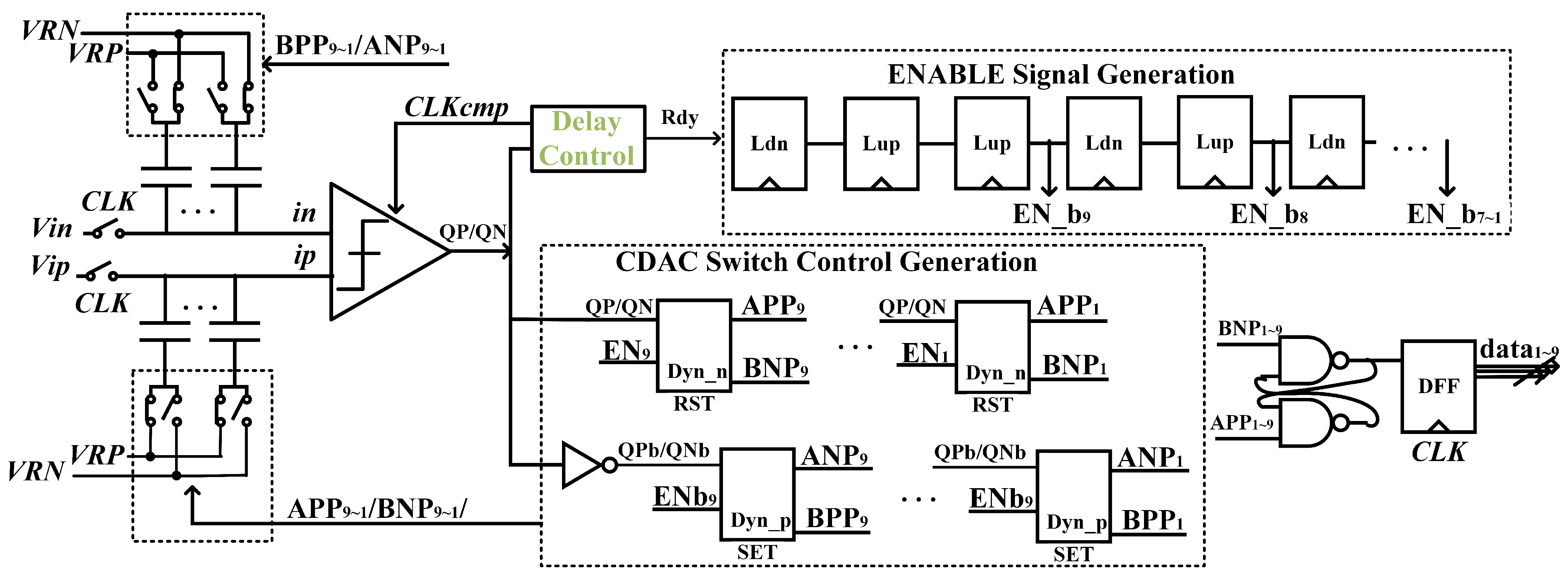

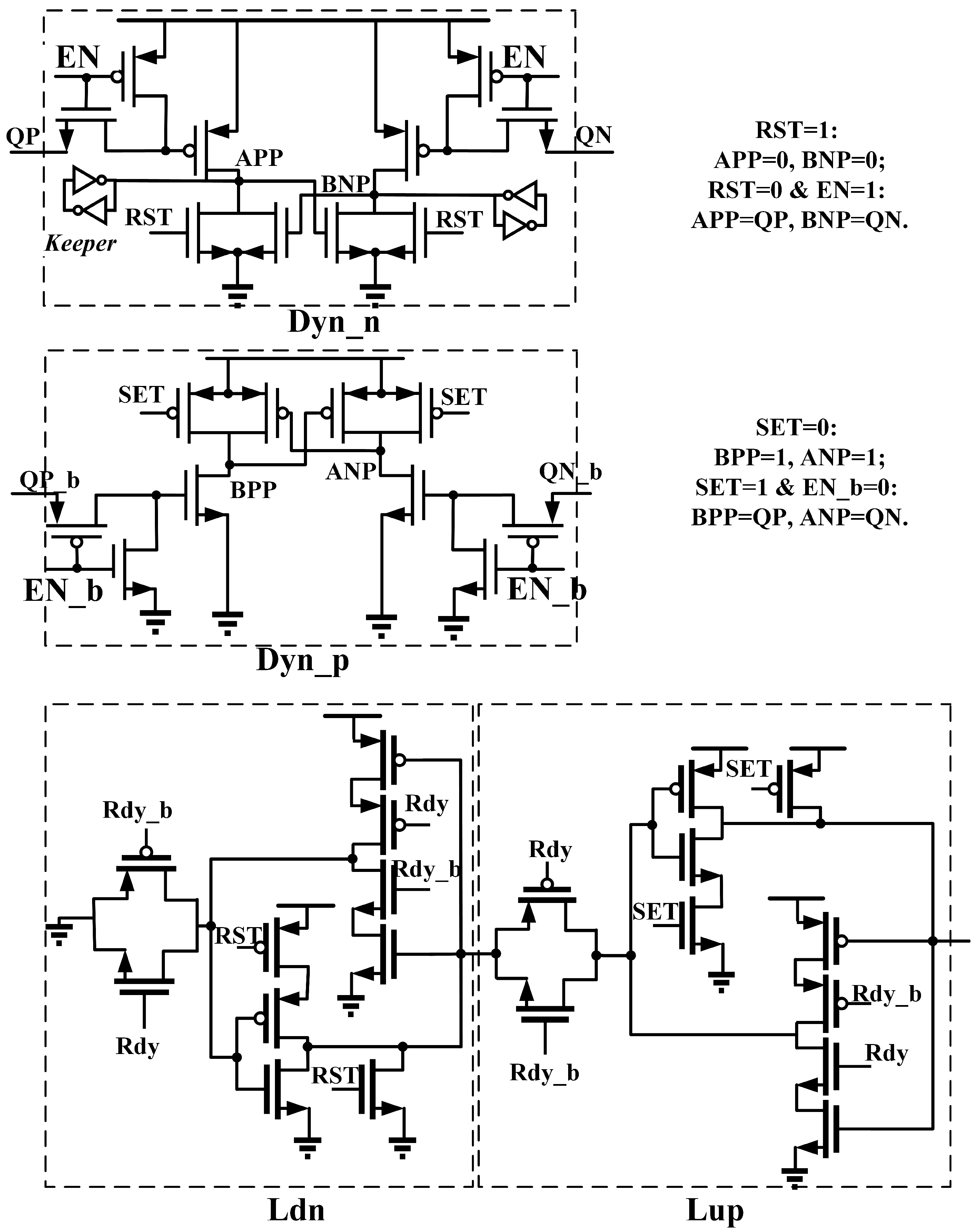

3.2. SAR Logic

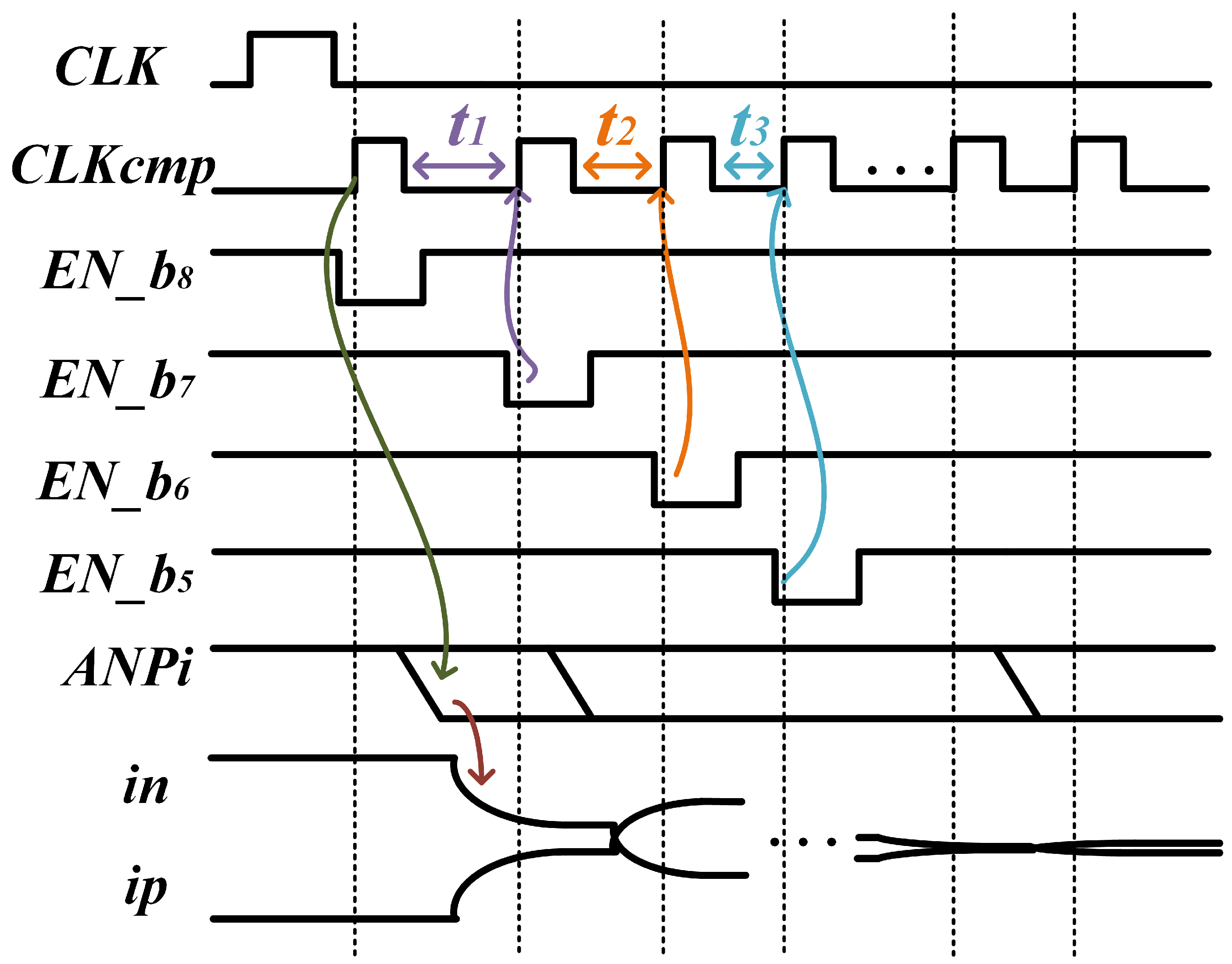

3.3. Delay Generation Logic

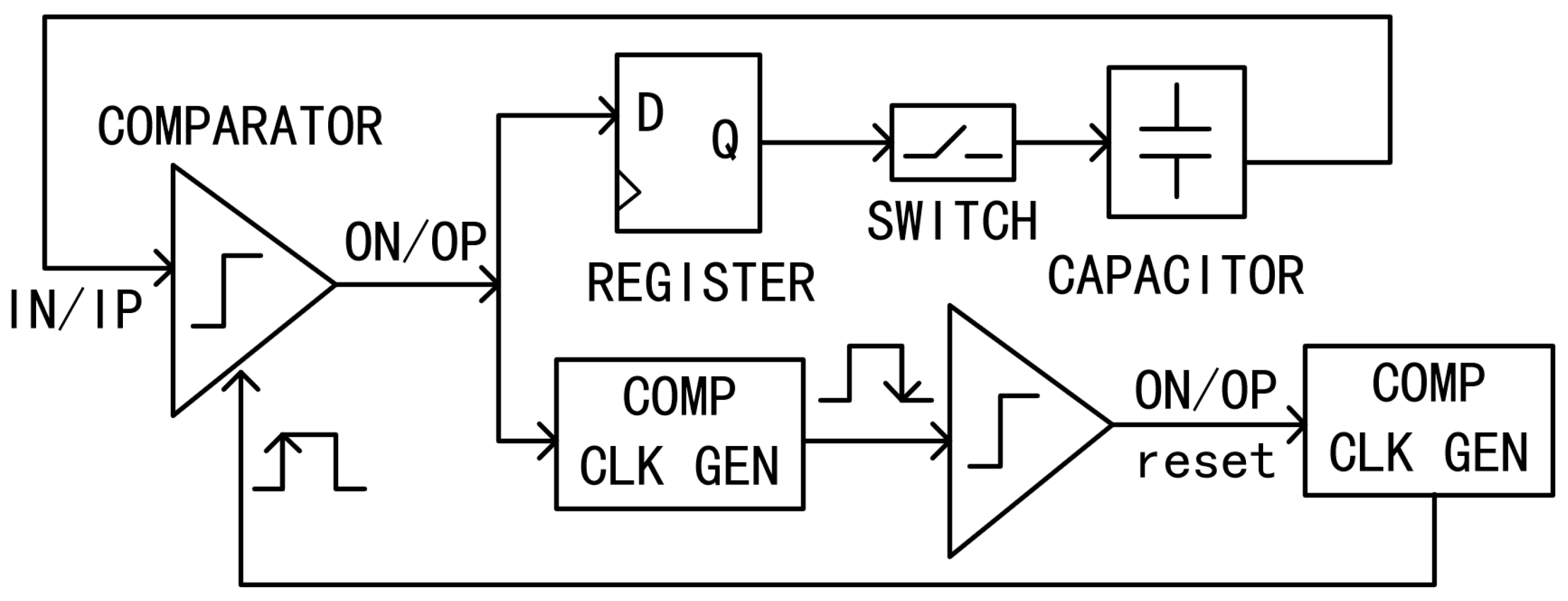

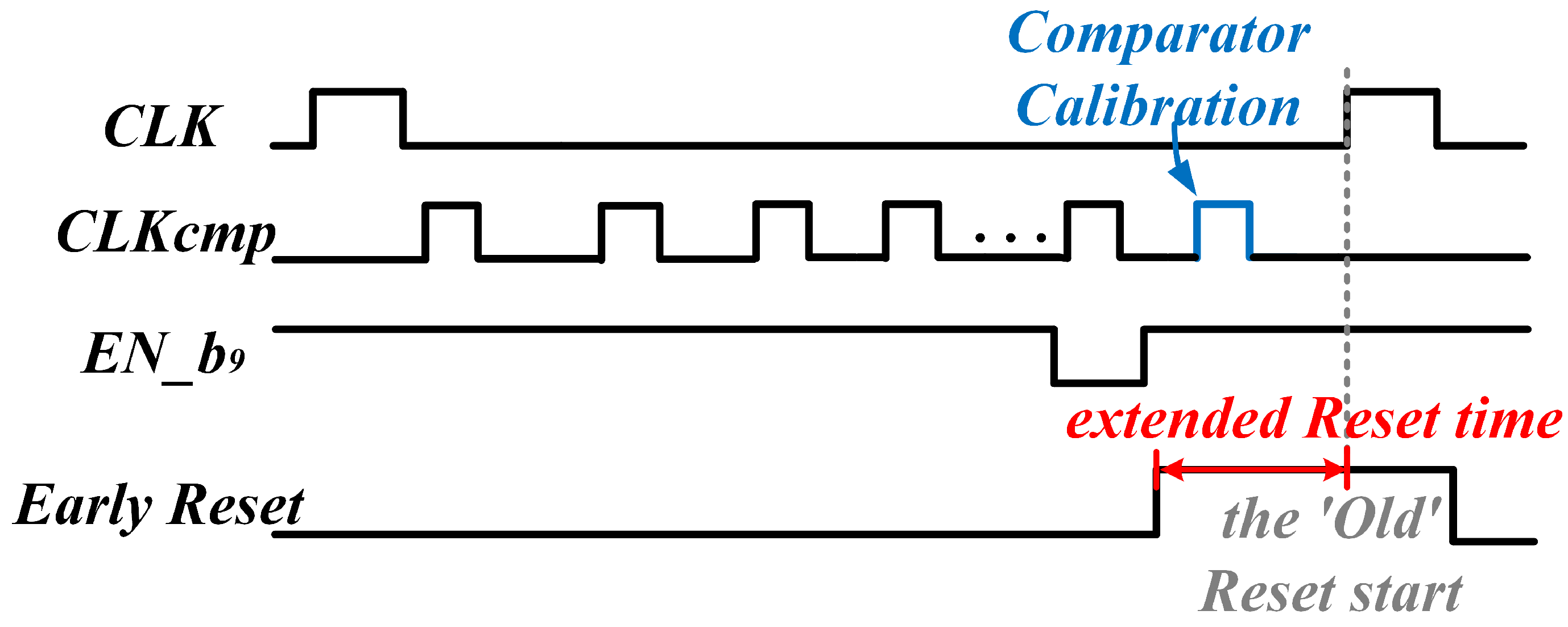

3.4. Early Reset of Dynamic Latch

4. Post-Simulation Results

5. Conclusions

Author Contributions

Funding

Data Availability Statement

Conflicts of Interest

References

- Luan, J.; Zheng, X.; Wu, D.; Zhang, Y.; Wu, L.; Zhou, L.; Wu, J.; Liu, X. A 56 GS/s 8 Bit Time-Interleaved ADC in 28 nm CMOS. Electronics 2022, 11, 688. [Google Scholar] [CrossRef]

- Wang, C.; Yang, Z.; Xing, X.; Duan, Q.; Zheng, X.; Gielen, G. A 10-Bit 400 MS/s Dual-Channel Time-Interleaved SAR ADC Based on Comparator Multiplexing. Electronics 2023, 12, 4062. [Google Scholar] [CrossRef]

- Cao, Y.; Zhang, M.; Zhu, Y.; Martins, R.P.; Chan, C.-H. A 12-GS/s 12-b 4× Time-Interleaved ADC Using Input-Independent Timing Skew Calibration with Global Dither Injection and Linearized Input Buffer. IEEE J. Solid-State Circuits 2024, 59, 4211–4224. [Google Scholar] [CrossRef]

- Tao, Y.; Gu, M.; Chi, B.; Zhong, Y.; Jie, L.; Sun, N. A 4.8GS/s 7-ENoB Time-Interleaved SAR ADC with Dither-Based Background Timing-Skew Calibration and Bit-Distribution-Based Background Ping-Pong Comparator Offset Calibration. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 18–22 February 2024; pp. 394–396. [Google Scholar]

- Mittal, R.; Shibata, H.; Patil, S.; Krommenhoek, E.; Shrestha, P.; Manganaro, G.; Chandrakasan, A.P.; Lee, H.-S. A 6.4-GS/s 1-GHz BW Continuous-Time Pipelined ADC with Time-Interleaved Sub-ADC-DAC Achieving 61.7-dB SNDR in 16-nm FinFET. IEEE J. Solid-State Circuits 2024, 59, 1158–1170. [Google Scholar] [CrossRef]

- Gu, M.; Tao, Y.; He, X.; Zhong, Y.; Jie, L.; Sun, N. A 1-GS/s 11-b Time-Interleaved SAR ADC with Robust, Fast, and Accurate Autocorrelation-Based Background Timing-Skew Calibration. IEEE J. Solid-State Circuits 2025, 48, 421–431. [Google Scholar] [CrossRef]

- Ricci, L.; Bè, G.; Rocco, M.; Scaletti, L.; Zanoletti, G.; Bertulessi, L.; Lacaita, A.L.; Levantino, S.; Samori, C.; Bonfanti, A. A 2-GS/s Time-Interleaved ADC with Embedded Background Calibrations and a Novel Reference Buffer for Reduced Inter-Channel Crosstalk. IEEE J. Solid-State Circuits 2025, 60, 456–468. [Google Scholar] [CrossRef]

- Shiue, M.-T.; Lo, Y.-F.; Jung, C.-Y. Design of an Internal Asynchronous 11-Bit SAR ADC for Biomedical Wearable Application. Electronics 2024, 13, 3549. [Google Scholar] [CrossRef]

- Huang, Y.; Luo, C.; Guo, G. A Cryogenic 8-Bit 32 MS/s SAR ADC Operating down to 4.2 K. Electronics 2023, 12, 1420. [Google Scholar] [CrossRef]

- Tang, J.; Wang, Y.; Gu, H.; Zou, W. Design of Self-Calibration Comparator for 12-Bit SAR ADCs. Electronics 2023, 12, 2277. [Google Scholar] [CrossRef]

- Lakshmi, P.V.; Musala, S.; Srinivasulu, A.; Ravariu, C. Design of a 0.4 V, 8.43 ENOB, 5.29 nW, 2 kS/s SAR ADC for Implantable Devices. Electronics 2023, 12, 4691. [Google Scholar] [CrossRef]

- Yang, J.-I.; Yoon, K.S.; Lim, H. A 12-Bit SAR ADC with Binary Search Calibration Algorithm for a Split Capacitor. Electronics 2024, 13, 414. [Google Scholar] [CrossRef]

- Tang, H.; Xu, W.; Li, H.; Wei, B.; Wei, X. A 0.49–4.34 μW LC-SAR Hybrid ADC with a 10.85-Bit ENOB and 20 KS/s Bandwidth. Electronics 2024, 13, 1078. [Google Scholar] [CrossRef]

- Chan, C.H.; Zhang, M.; Cao, Y.; Zhao, H.; Martins, R.P.; Zhu, Y. The Race for the Extra Pico Second without Losing the Decibel: A Partial-Review of Single-Channel Energy-Efficient High-Speed Nyquist ADCs. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), Denver, CO, USA, 21–24 April 2024; 2024; pp. 1–8. [Google Scholar]

- Li, X.; Wang, R.; Zhang, M.; Zhu, C.; Wang, Z.; Lin, J. A High-Speed 8-bit Single-Channel SAR ADC with Tailored Bit Intervals. In Proceedings of the IEEE International Symposium for Circuits and Systems (ISCAS), London, UK, 25–28 May 2025. [Google Scholar]

- Kull, L.; Toifl, T.; Schmatz, M.; Francese, P.A.; Menolfi, C.; Brändli, M.; Kossel, M.; Morf, T.; Andersen, T.M.; Leblebici, Y. A 3.1 mW 8b 1.2 GS/s Single-Channel Asynchronous SAR ADC with Alternate Comparators for Enhanced Speed in 32 nm Digital SOI CMOS. IEEE J. Solid-State Circuits 2013, 48, 3049–3058. [Google Scholar] [CrossRef]

- Kull, L.; Luu, D.; Menolfi, C.; Brändli, M.; Francese, P.A.; Morf, T.; Kossel, M.; Cevrero, A.; Ozkaya, I.; Toifl, T. A 24–72-GS/s 8-b Time-Interleaved SAR ADC with 2.0–3.3-pJ/Conversion and 30 dB SNDR at Nyquist in 14-nm CMOS FinFET. IEEE J. Solid-State Circuits 2018, 53, 3508–3516. [Google Scholar] [CrossRef]

- Jara, M.; Razavi, B. A 6-bit 10-GS/s 17.6-mW CMOS ADC with 0.8-V supply. In Proceedings of the IEEE Custom Integrated Circuits Conference (CICC), San Antonio, TX, USA, 23–26 April 2023; pp. 1–2. [Google Scholar]

- Tripathi, V.; Murmann, B. An 8-bit 450-MS/s single-bit/cycle SAR ADC in 65-nm CMOS. In Proceedings of the ESSCIRC (ESSCIRC), Bucharest, Romania, 16–20 September 2013; pp. 117–120. [Google Scholar]

- Ramkaj, A.T.; Strackx, M.; Steyaert, M.S.J.; Tavernier, F. A 1.25-GS/s 7-b SAR ADC with 36.4-dB SNDR at 5 GHz Using Switch-Bootstrapping, USPC DAC and Triple-Tail Comparator in 28-nm CMOS. IEEE J. Solid-State Circuits 2018, 53, 1889–1901. [Google Scholar] [CrossRef]

- Tsai, T.-H.; Tai, H.-Y.; Tsai, P.-Y.; Tsai, C.-H.; Chen, H.-S. An 8 b 700 MS/s 1 b/Cycle SAR ADC Using a Delay-Shift Technique. IEEE Trans. Circuits Syst. I Regul. Pap. 2016, 63, 683–692. [Google Scholar] [CrossRef]

- Qiu, L.; Tang, K.; Zheng, Y.; Siek, L.; Zhu, Y.; U, S.-P. A 16-mW 1-GS/s with 49.6-dB SNDR TI-SAR ADC for Software-Defined Radio in 65-nm CMOS. IEEE Trans. Large Scale Integr. (VLSI) Syst. 2018, 26, 572–583. [Google Scholar] [CrossRef]

- Gu, W.; Zhou, H.; Lin, T.; Wang, Z.; Ye, F.; Ren, J. Power efficient SAR ADC with optimized settling technique. In Proceedings of the IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Columbus, OH, USA, 2 December 2013; pp. 1156–1159. [Google Scholar]

- Kang, H.; Lee, S.; Lee, M. A Three-Step Tapered Bit Period SAR ADC Using Area-Efficient Clock Generation. Electronics 2023, 12, 1863. [Google Scholar] [CrossRef]

- Janke, D.; Monk, A.; Swindlehurst, E.; Layton, K.; Chiang, S.-H.; Wood, Y. A 9-Bit 10-MHz 28- μ W SAR ADC Using Tapered Bit Periods and a Partially Interdigitated DAC. IEEE Trans. Circuits Syst. II Express Briefs 2019, 66, 187–191. [Google Scholar] [CrossRef]

- Swindlehurst, E.; Jensen, H.; Petrie, A.; Song, Y.; Kuan, Y.-C.; Chang, M.-C.F.; Wu, J.-T.; Chiang, S.-H.W. An 8-bit 10-GHz 21-mW Time-Interleaved SAR ADC with Grouped DAC Capacitors and Dual-Path Bootstrapped Switch. IEEE Solid-State Circuits Letters 2019, 53, 83–86. [Google Scholar] [CrossRef]

- Huang, H.; Du, L.; Chiu, Y. A 1.2-GS/s 8-bit Two-Step SAR ADC in 65-nm CMOS with Passive Residue Transfer. IEEE J. Solid-State Circuits 2017, 52, 1551–1562. [Google Scholar] [CrossRef]

- Akkaya, A.; Celik, F.; Leblebici, Y. An 8-Bit 800 MS/s Loop-Unrolled SAR ADC with Common-Mode Adaptive Background Offset Calibration in 28 nm FDSOI. IEEE Trans. Circuits Syst. I Regul. Pap. 2021, 68, 2766–2774. [Google Scholar] [CrossRef]

- Choo, K.D.; Bell, J.; Flynn, M.P. Area-efficient 1GS/s 6b SAR ADC with charge-injection-cell-based DAC. In Proceedings of the IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 31 January–4 February 2016; pp. 460–461. [Google Scholar]

| Model | LPE Type | VDD = 0.9V | Temp. | Max. S. R. | ENOB |

|---|---|---|---|---|---|

| TT | RCtypical | nominal | 25 °C | 1.3 GS/s | 7.20@1 GS/s |

| FF | RCbest | 1 + 10% | −40 °C | 1.6 GS/s | 7.21@1.3 GS/s |

| FF | RCbest | 1 + 10% | 110 °C | 1.4 GS/s | 7.18@1 GS/s |

| SS | RCworst | 1 − 10% | −40 °C | 1.05 GS/s | 7.05@0.9 GS/s |

| SS | RCworst | 1 − 10% | 110 °C | 1 GS/s | 7.08@0.8 GS/s |

| JSSC [20] | JSSC [16] | TCAS1 [28] | ISSCC [29] | This Work | |

|---|---|---|---|---|---|

| Technology | 28 nm | 32 nm SOI | 28 nm FDSOI | 40 nm | 16 nm FinFET |

| ADC Type | SAR | 2-compSAR | LU-SAR | ci-SAR | SAR |

| Supply [V] | 1.0 | 1.0 | 1.0 | 1.0 | 1.0 0.9 |

| [GS/s] | 1 | 1.2 | 0.8 | 1 | 1.6 1.3 (max) |

| Resolution [bit] | 7 | 8 | 8 | 6 | 8 |

| SFDR [dB] | 52.0 | 49.8 | 50.7 | 49.7 | 56.2 53.5 @1.3 & 1 GS/s |

| SNDR [dB] | 40.1 | 39.3 | 42.6 | 34.6 | 45.1 45.1 @1.3 & 1 GS/s |

| FOMw [fJ/conv.-s] | 34.4 | 34 | 22.8 | 28.7 | 26.0 24.3 @1.3 & 1 GS/s |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2025 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Li, X.; Wang, R.; He, L.; Yoshioka, K. A High-Speed 8-Bit Single-Channel SAR ADC with Tailored Bit Intervals and Split Capacitors. Electronics 2025, 14, 2032. https://doi.org/10.3390/electronics14102032

Li X, Wang R, He L, Yoshioka K. A High-Speed 8-Bit Single-Channel SAR ADC with Tailored Bit Intervals and Split Capacitors. Electronics. 2025; 14(10):2032. https://doi.org/10.3390/electronics14102032

Chicago/Turabian StyleLi, Xinyu, Ruida Wang, Liulu He, and Kentaro Yoshioka. 2025. "A High-Speed 8-Bit Single-Channel SAR ADC with Tailored Bit Intervals and Split Capacitors" Electronics 14, no. 10: 2032. https://doi.org/10.3390/electronics14102032

APA StyleLi, X., Wang, R., He, L., & Yoshioka, K. (2025). A High-Speed 8-Bit Single-Channel SAR ADC with Tailored Bit Intervals and Split Capacitors. Electronics, 14(10), 2032. https://doi.org/10.3390/electronics14102032