Miniaturization of CMOS

Abstract

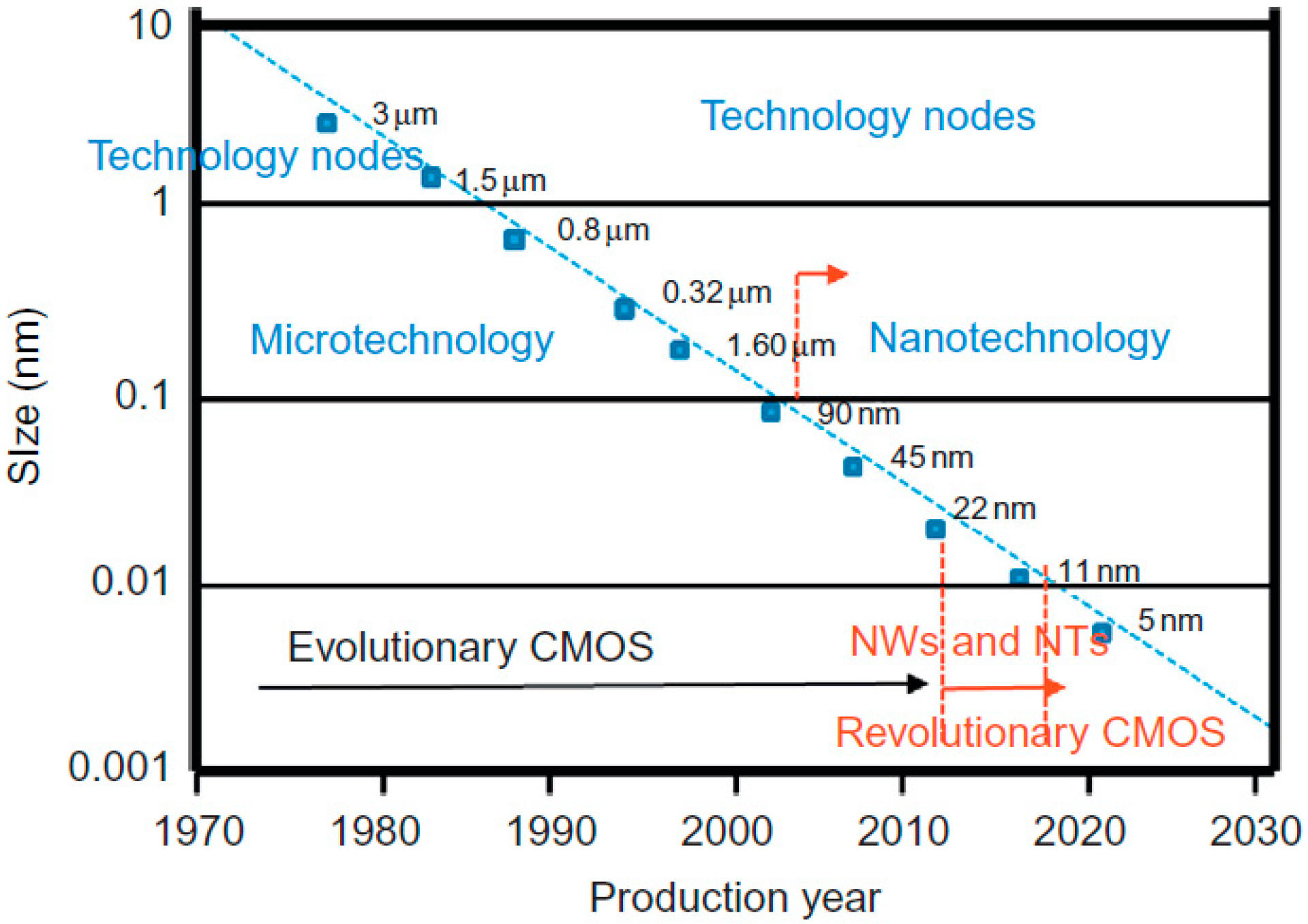

1. Introduction

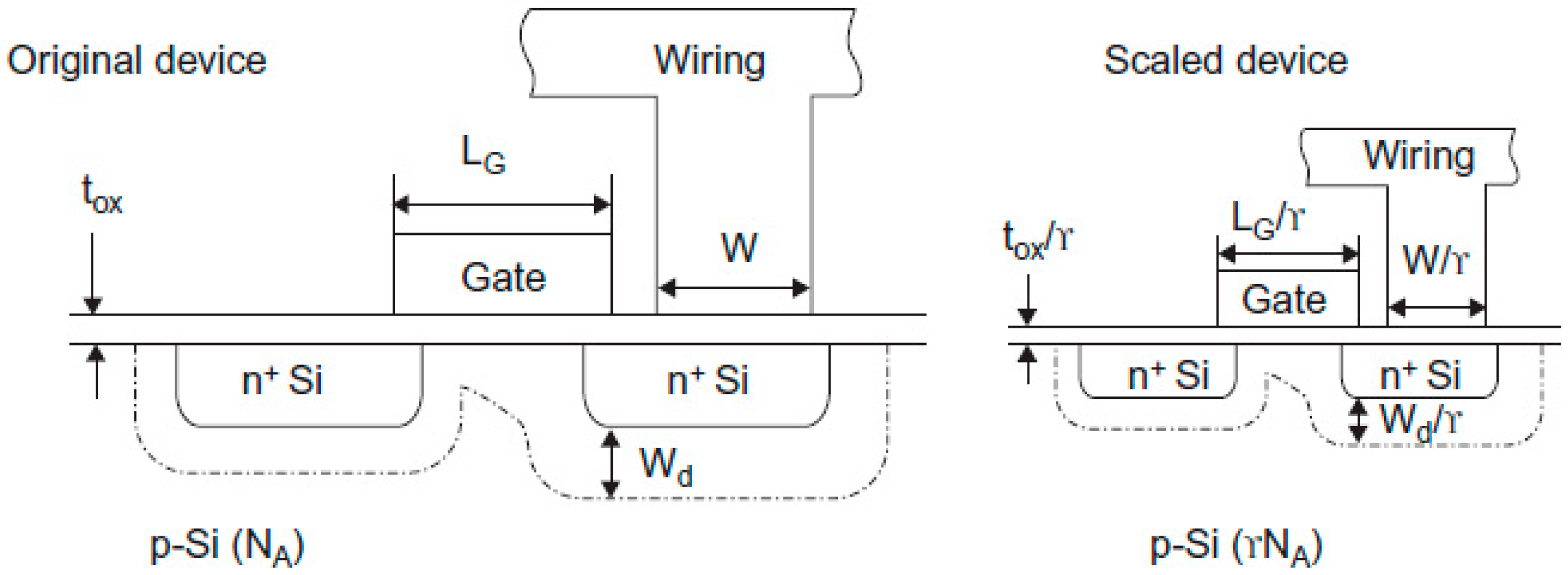

2. Miniaturization Principles

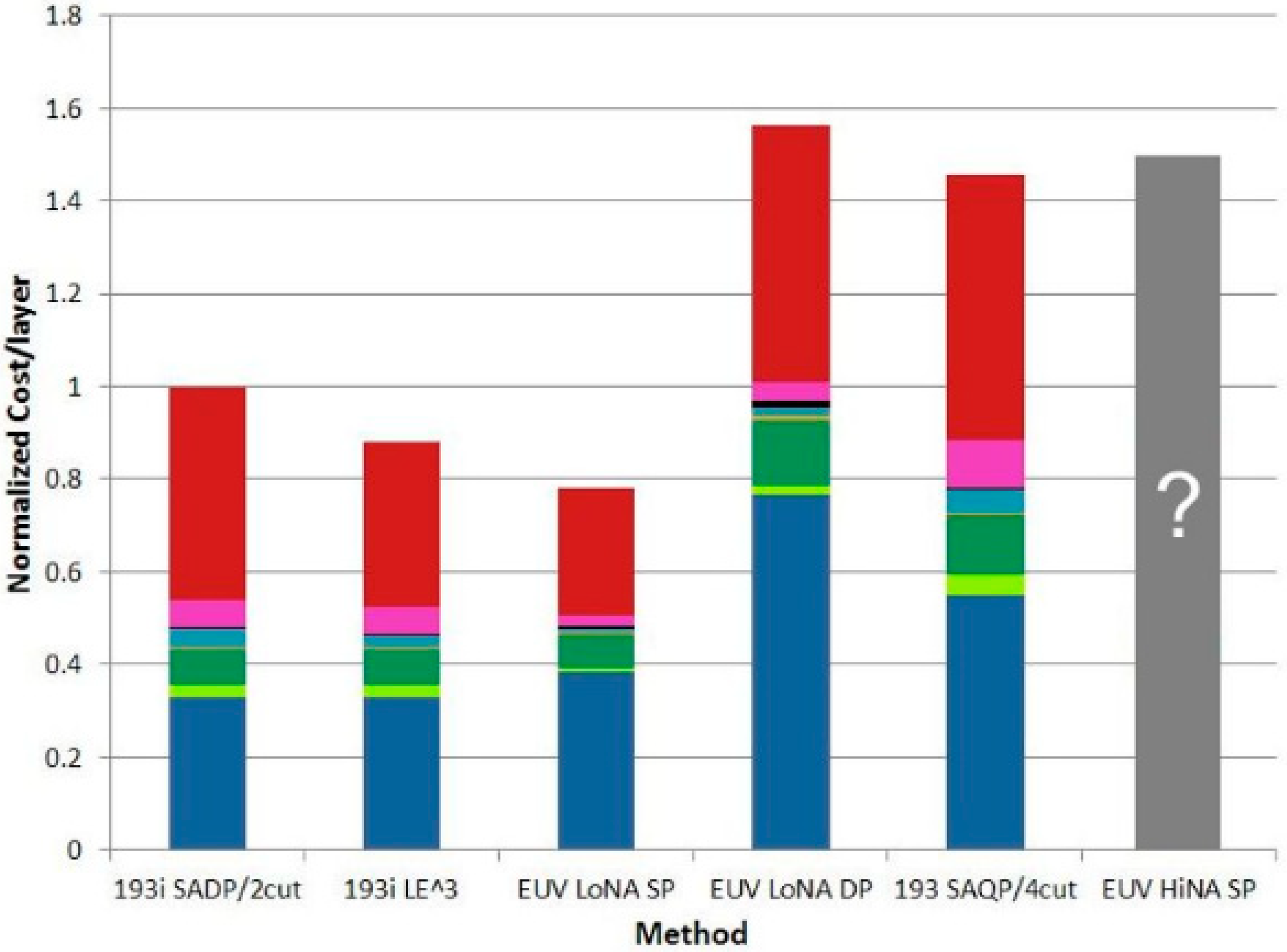

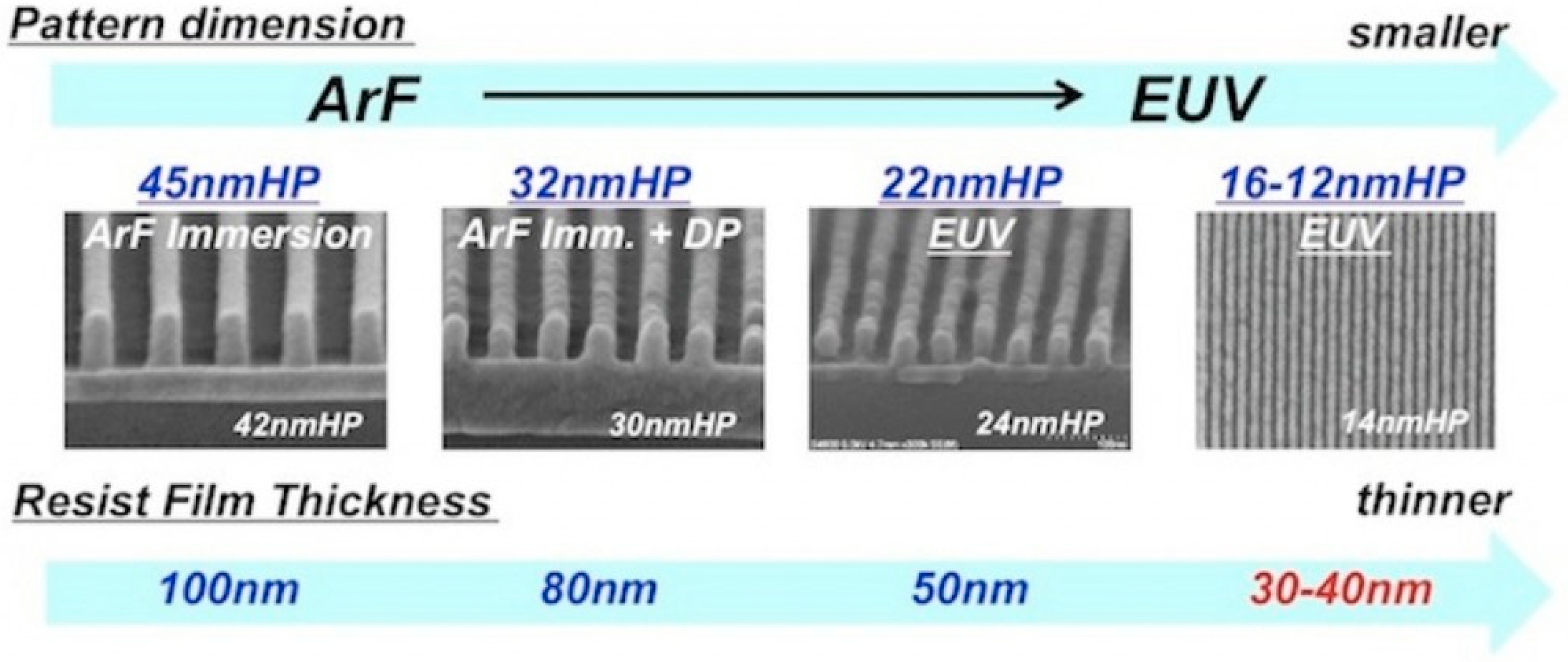

3. Lithography of Nano-Scaled Transistors

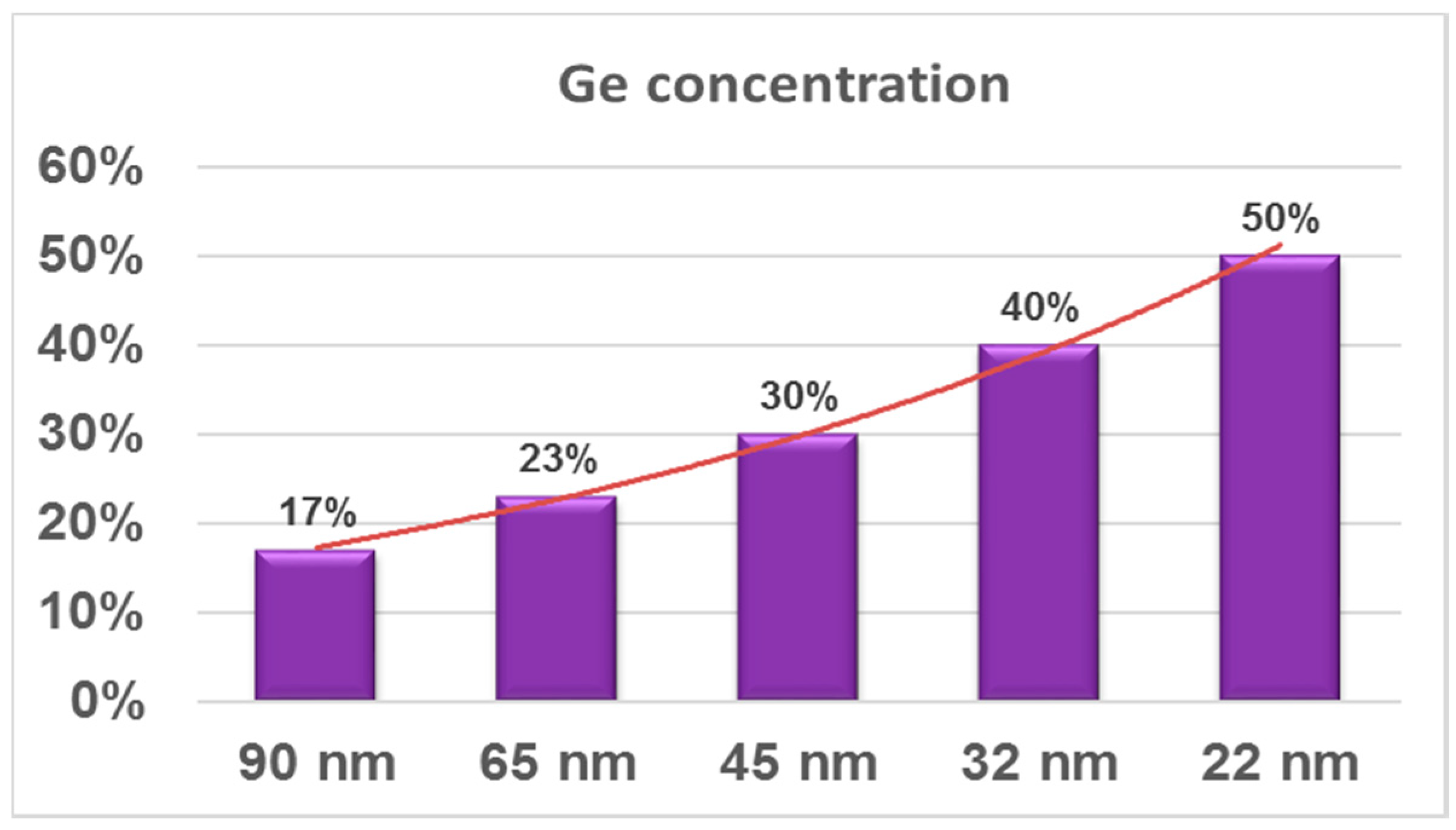

4. Process Integration of New Transistor Architecture

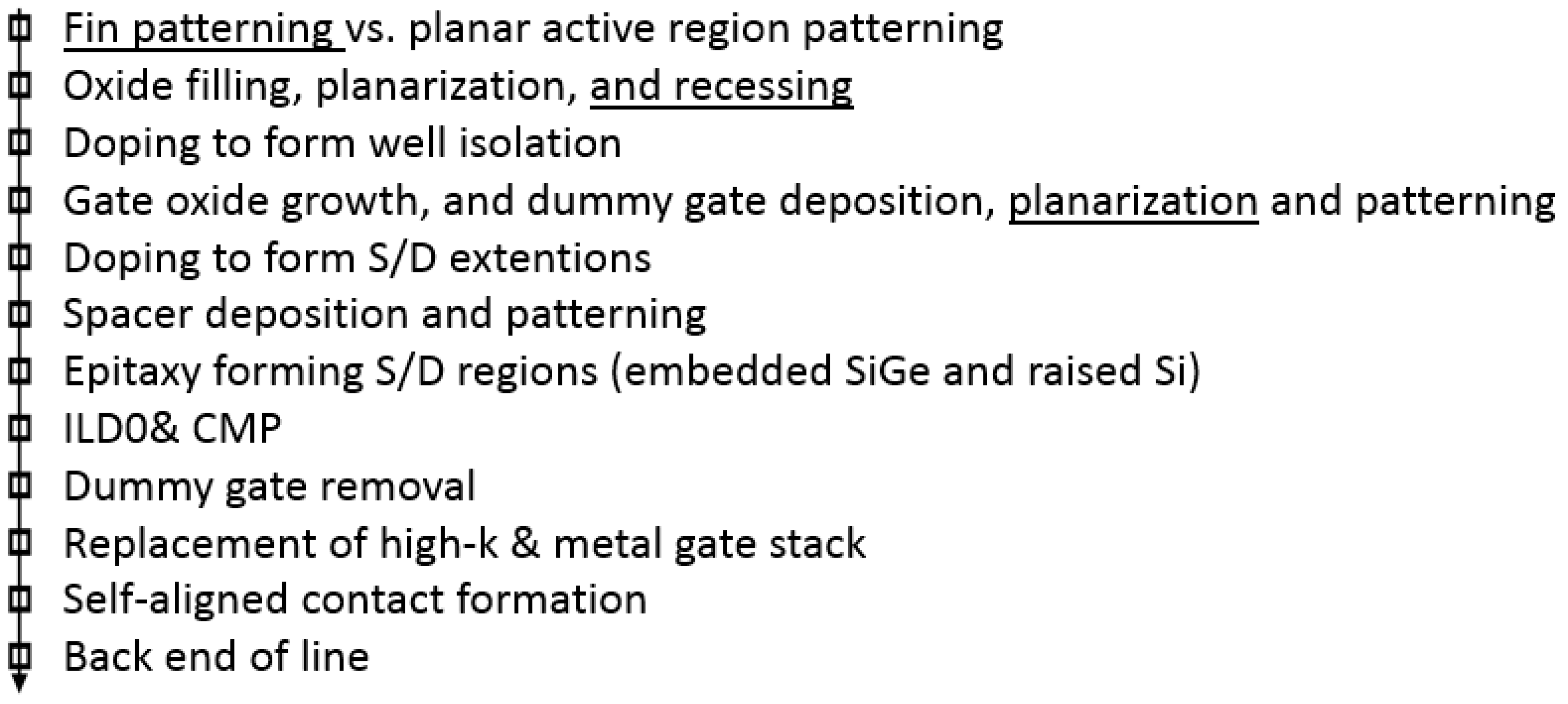

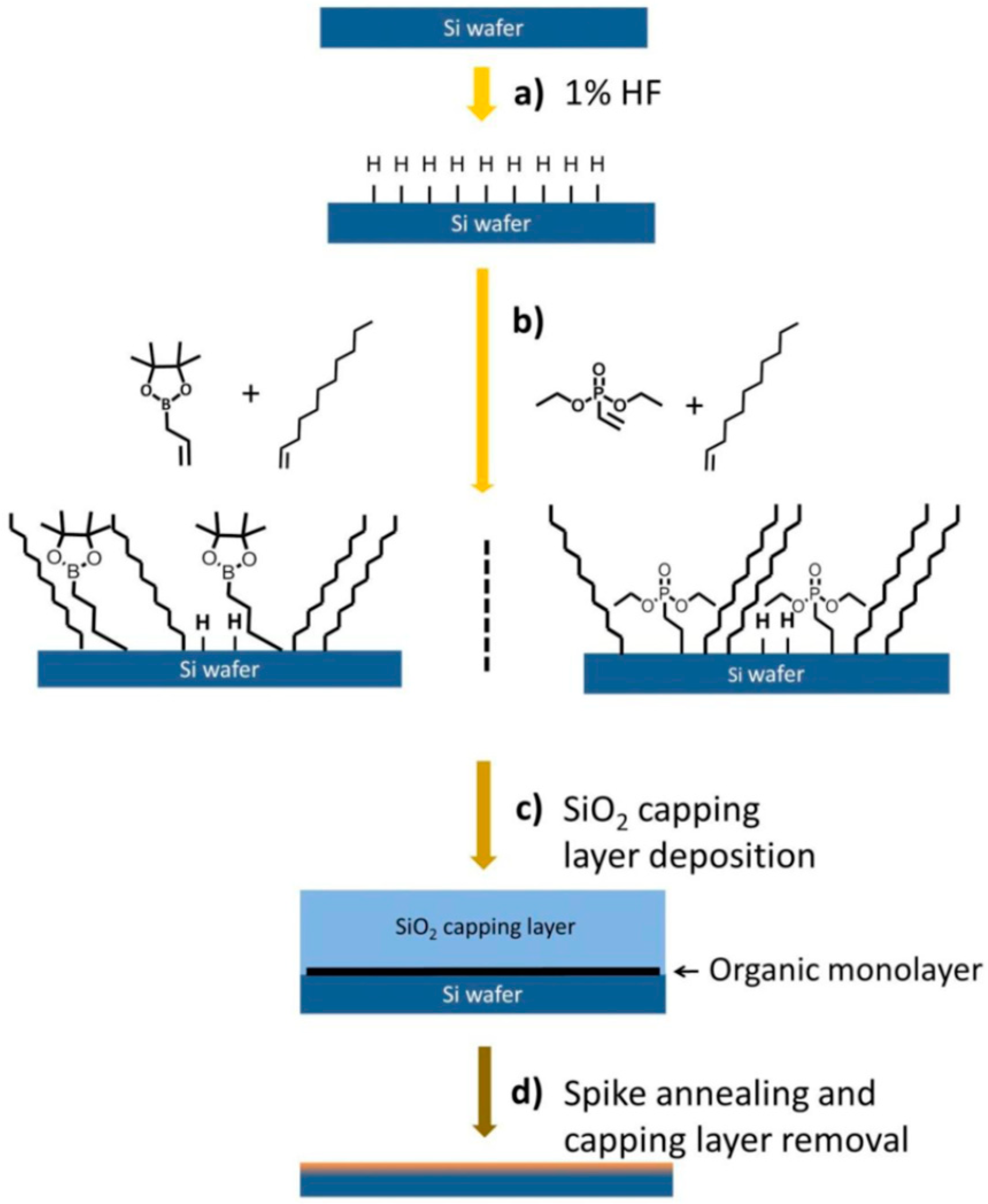

4.1. Process Flow of 2D and 3D Transistors

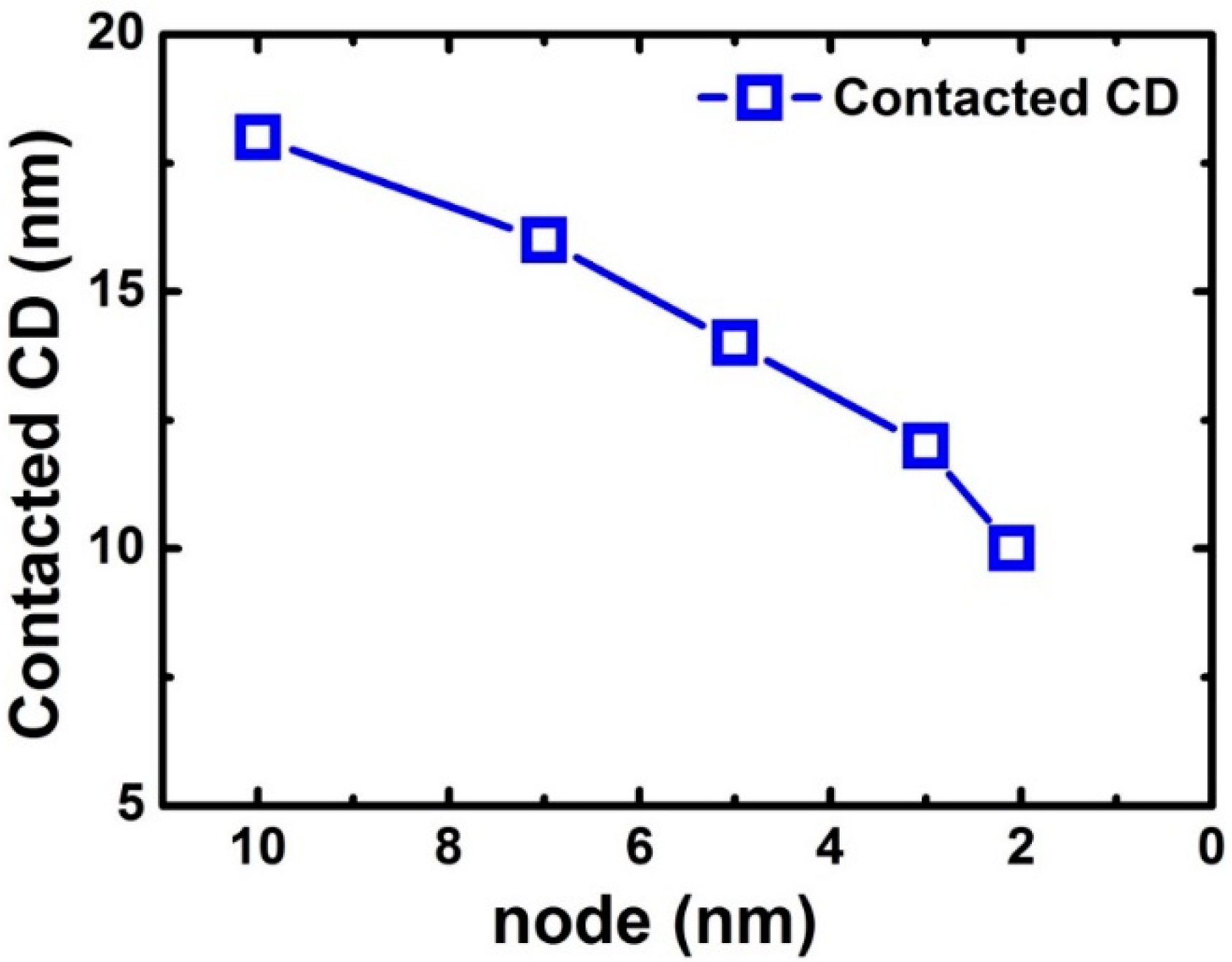

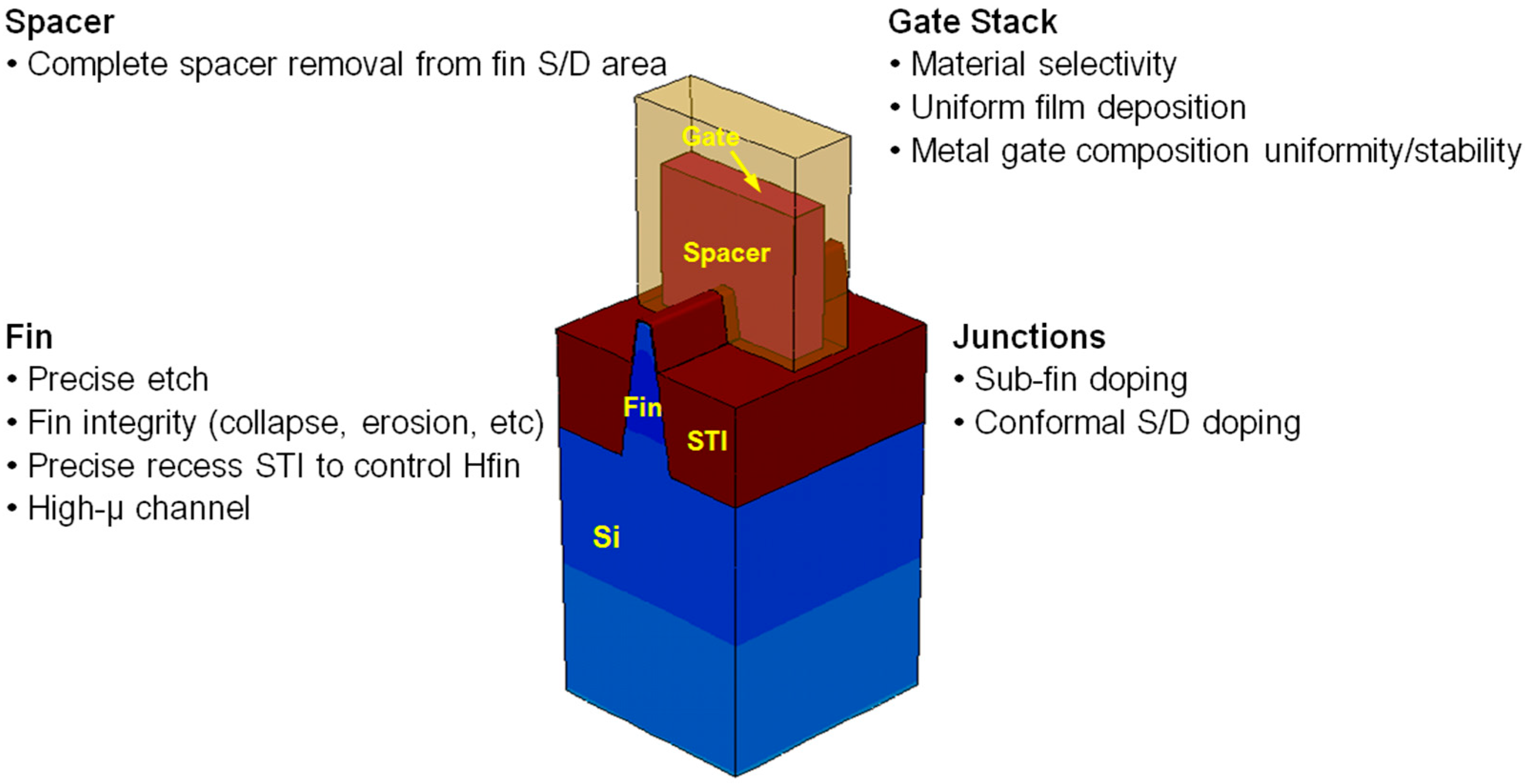

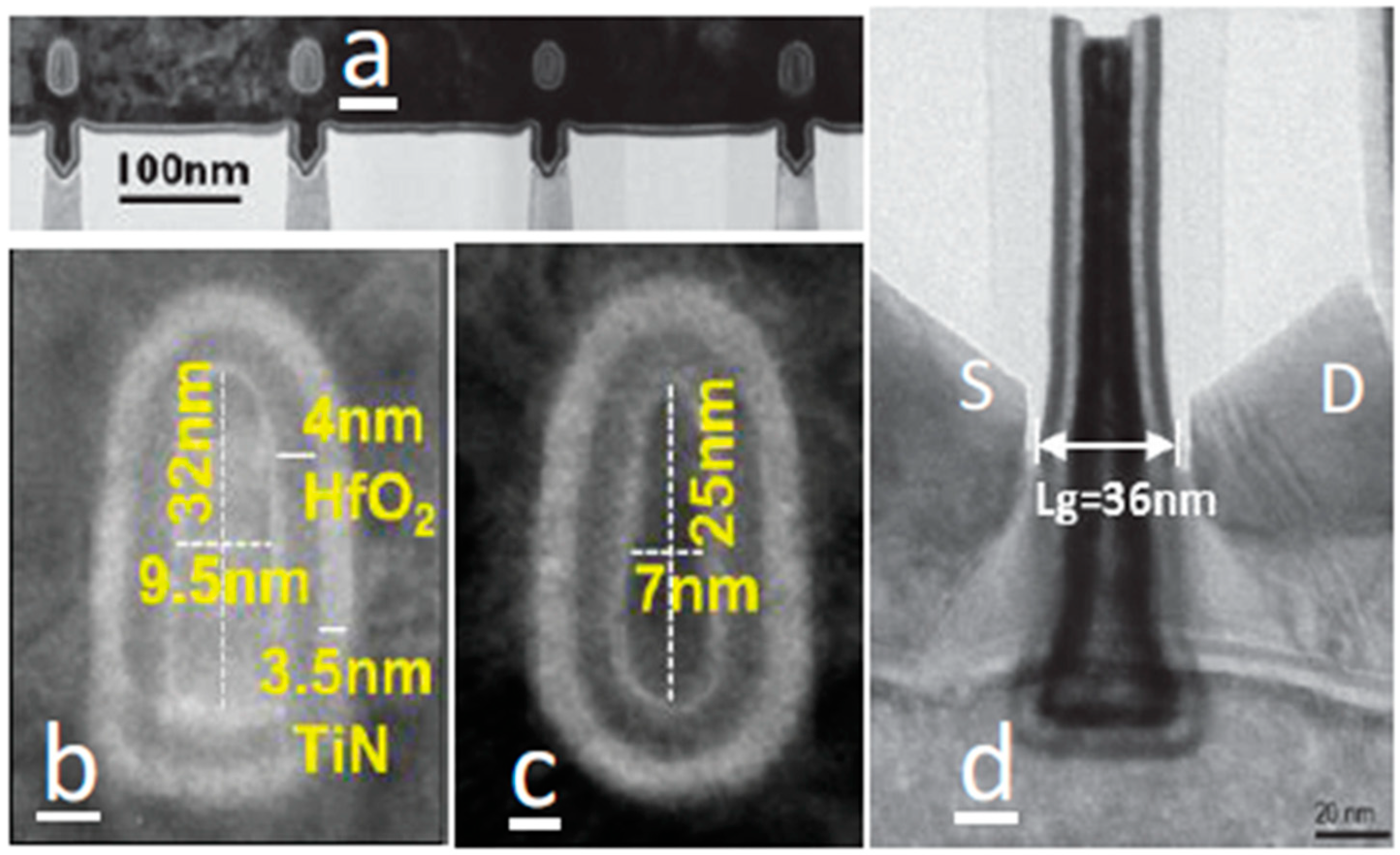

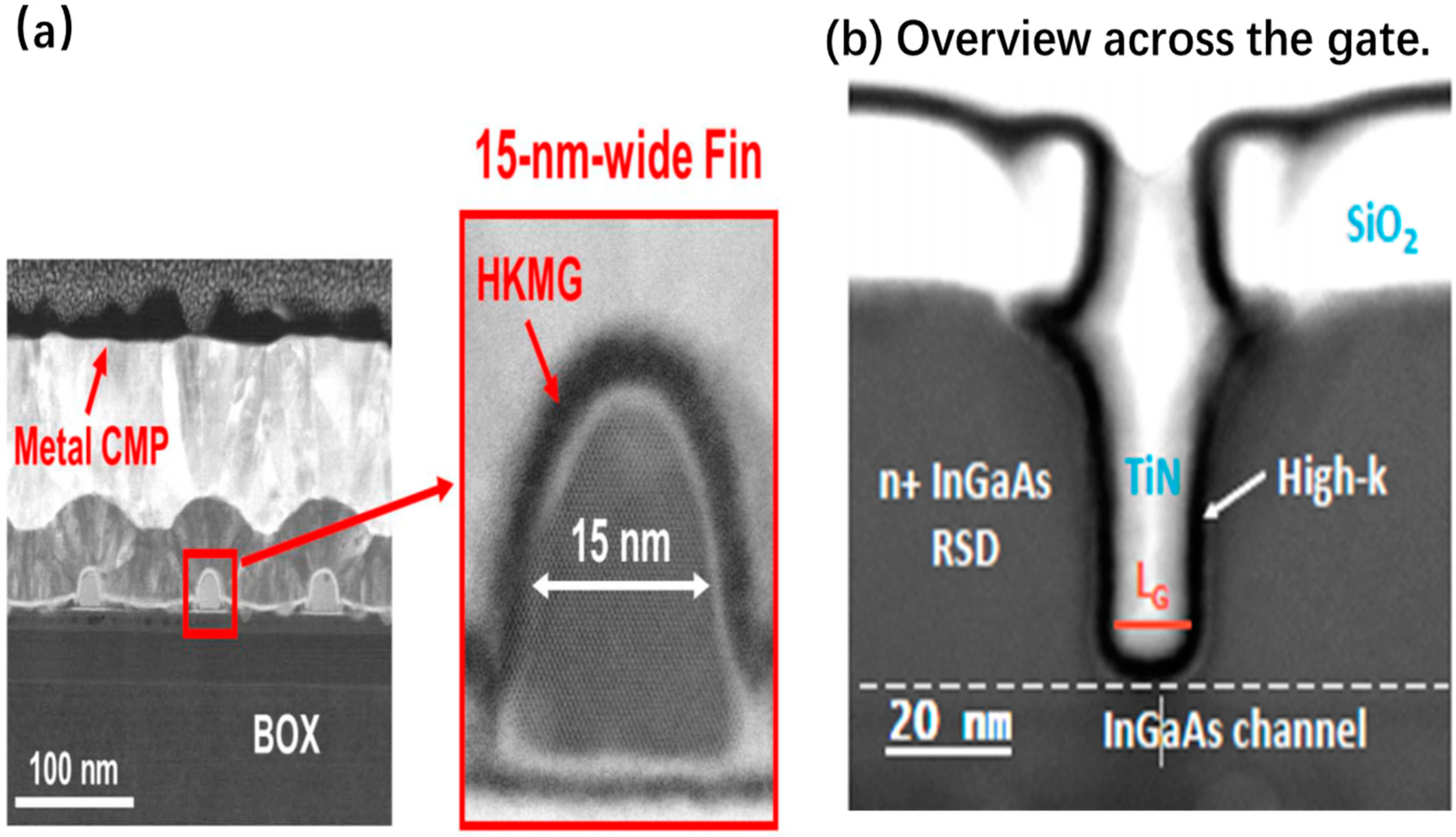

4.2. Challenges in FinFETs’ Process

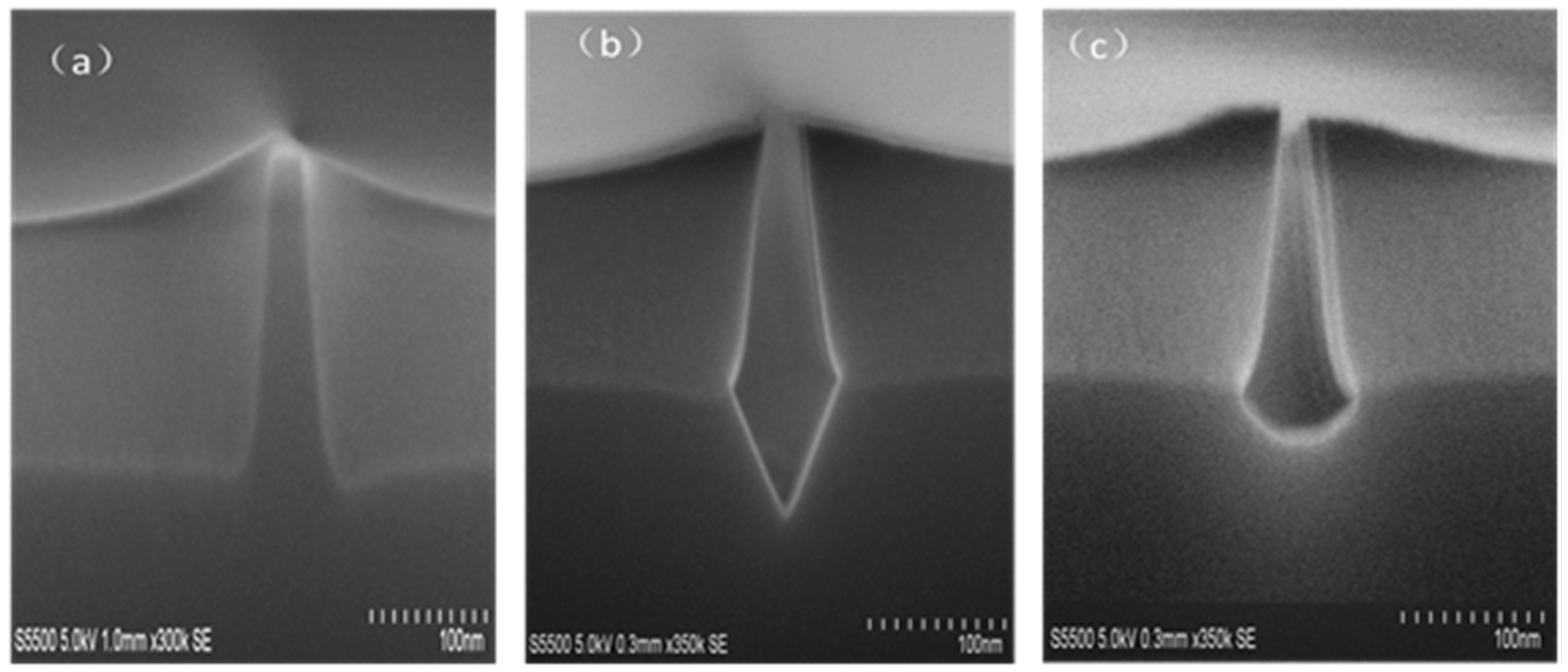

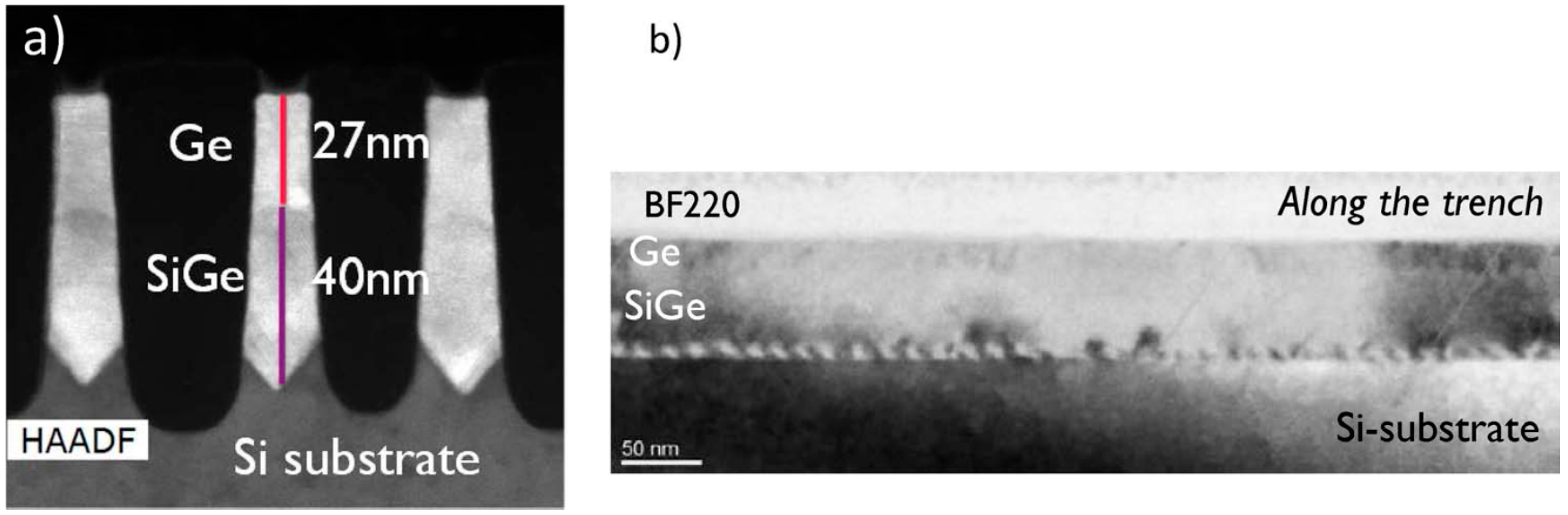

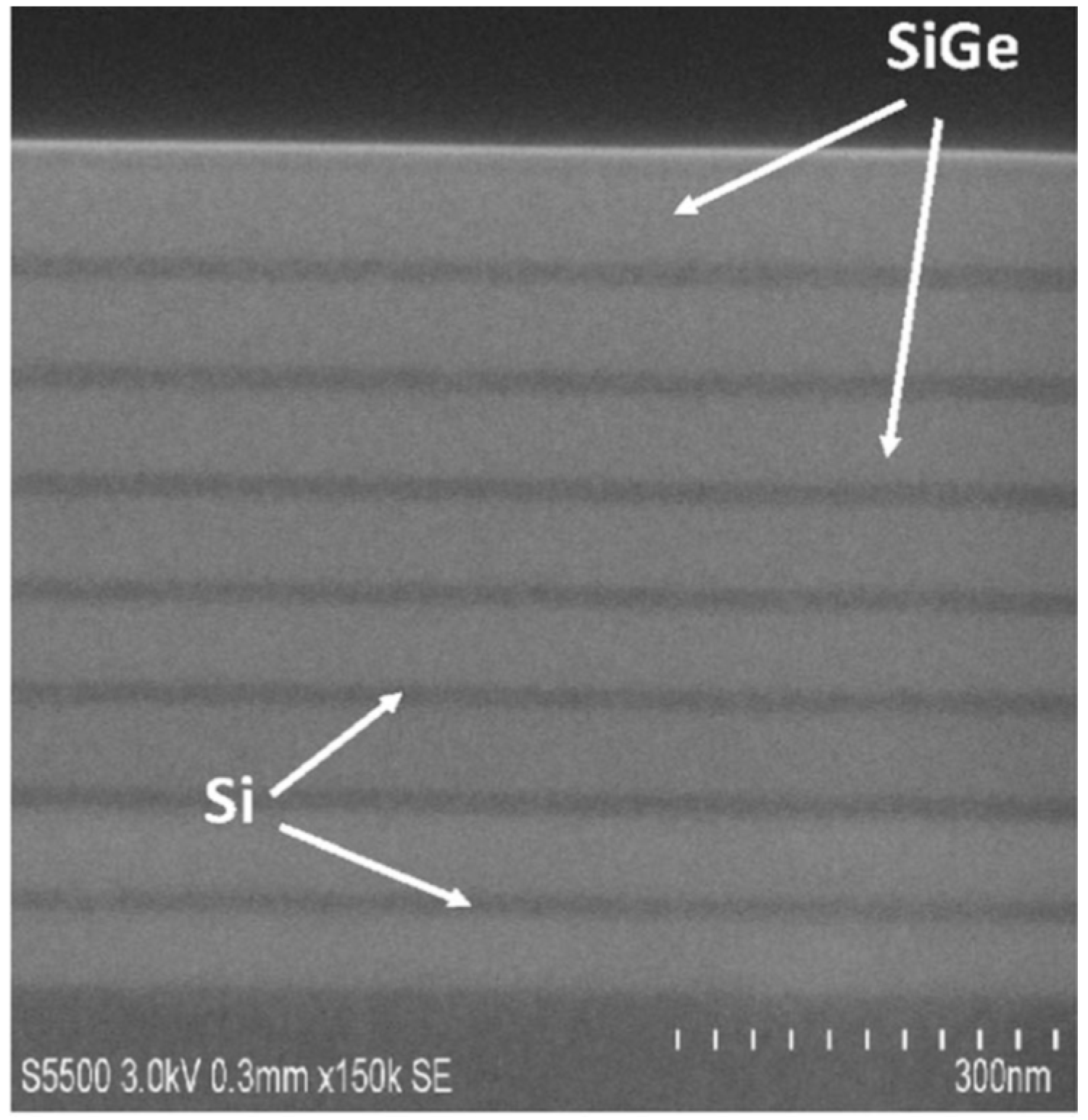

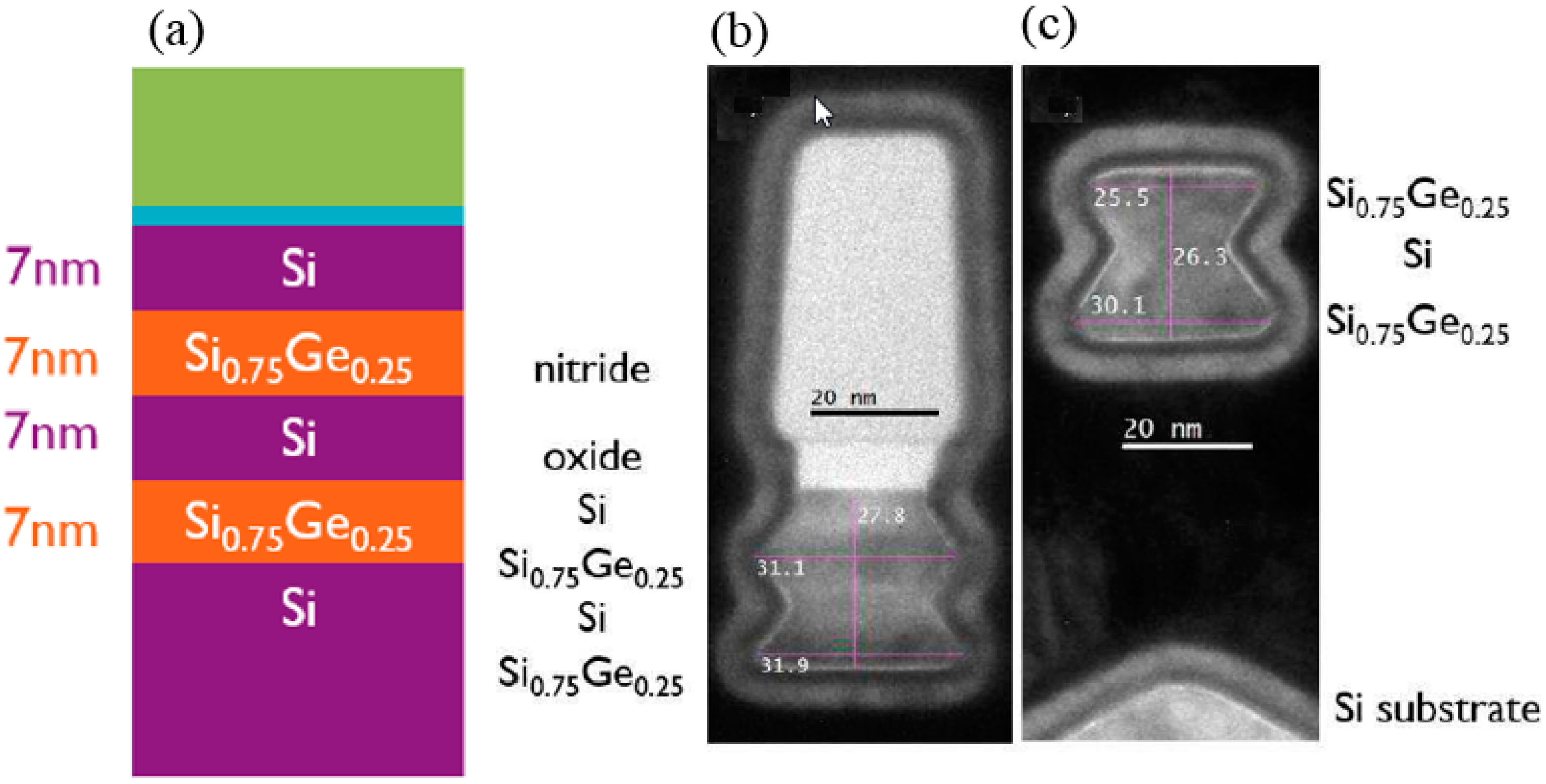

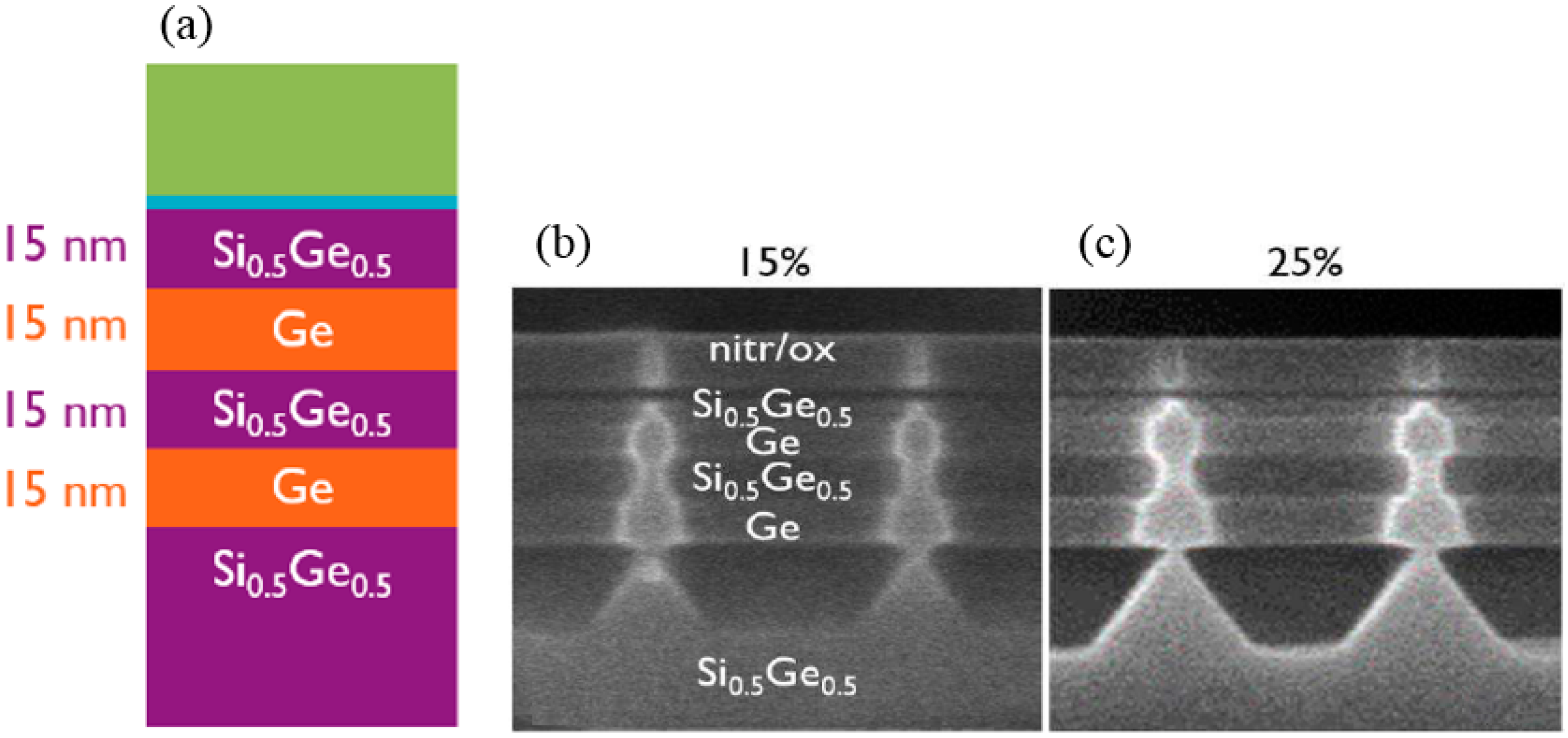

5. SiGe Epitaxy of Nano-Scaled Transistors

6. Monolayer Doping

7. Plasma Doping

8. High-k & Metal Gate (HKMG)

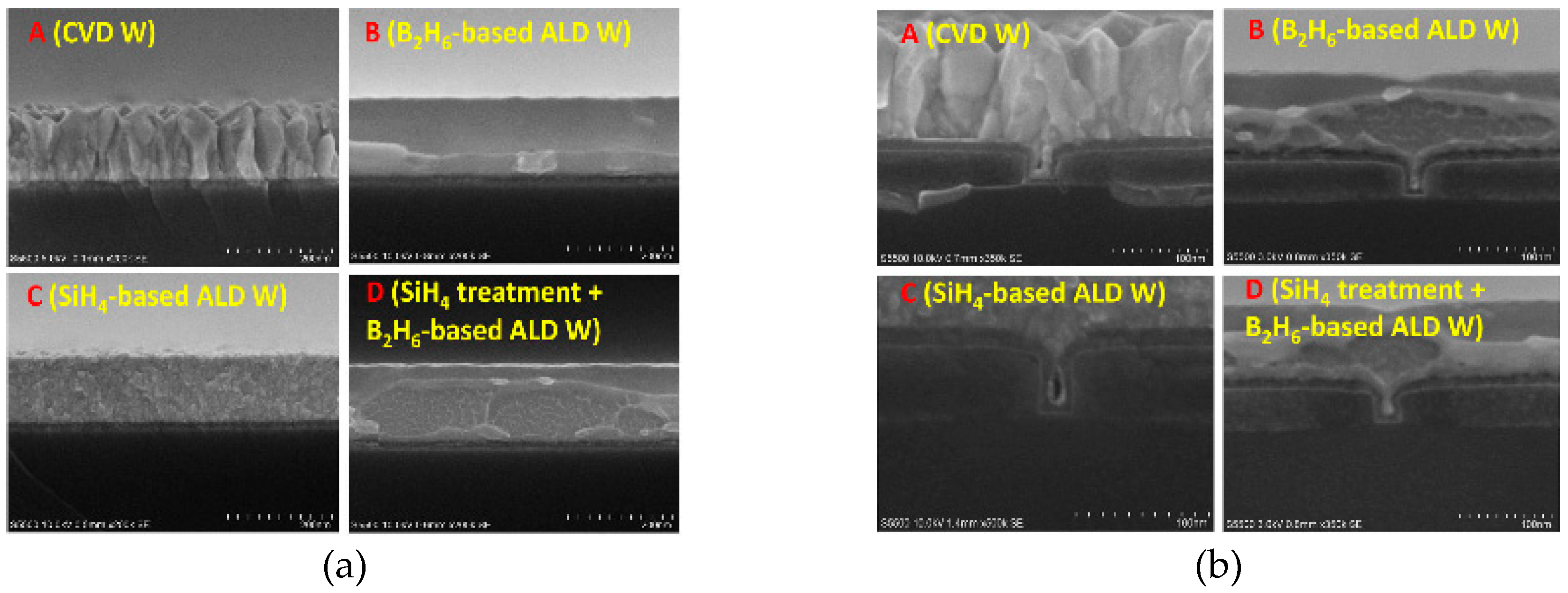

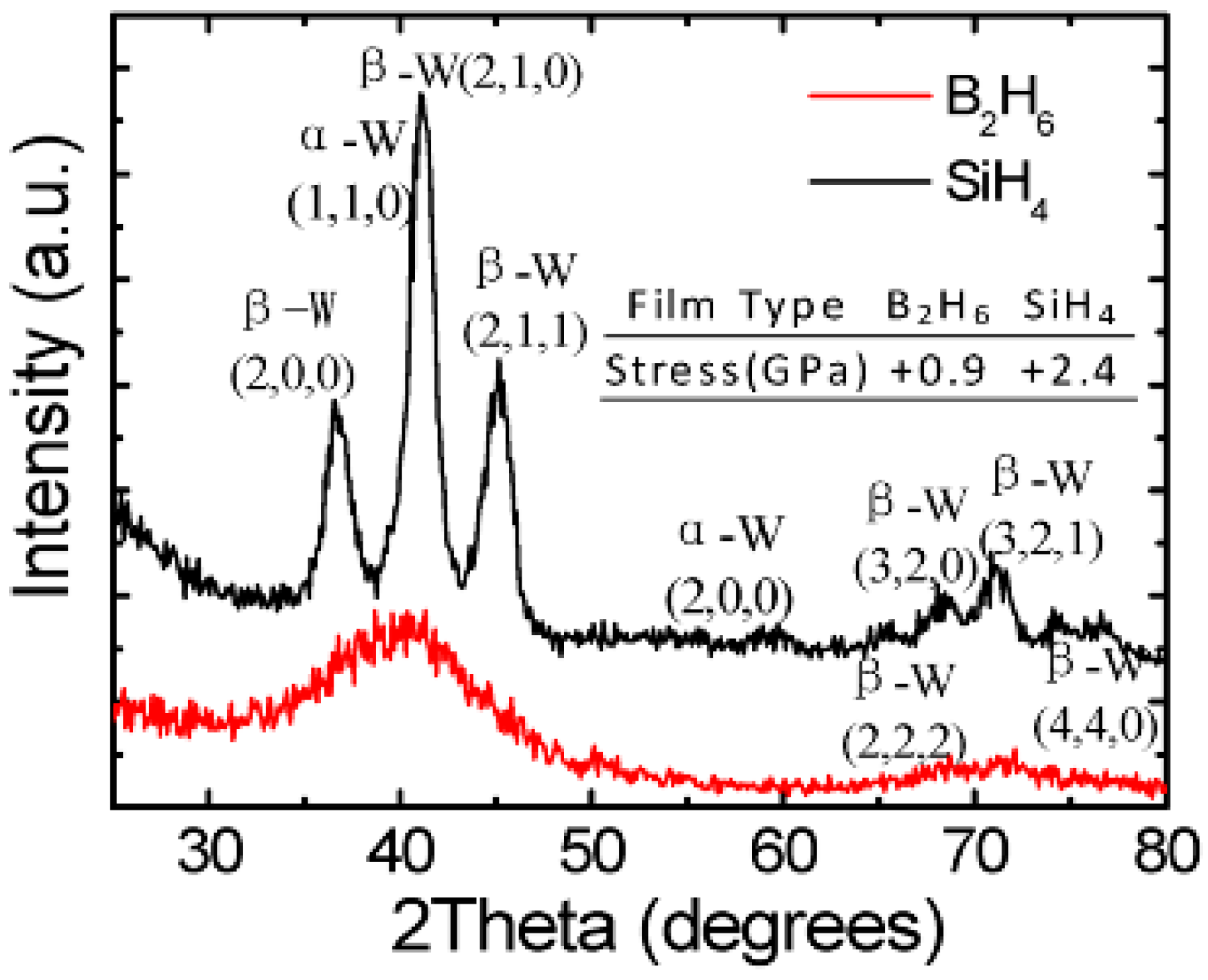

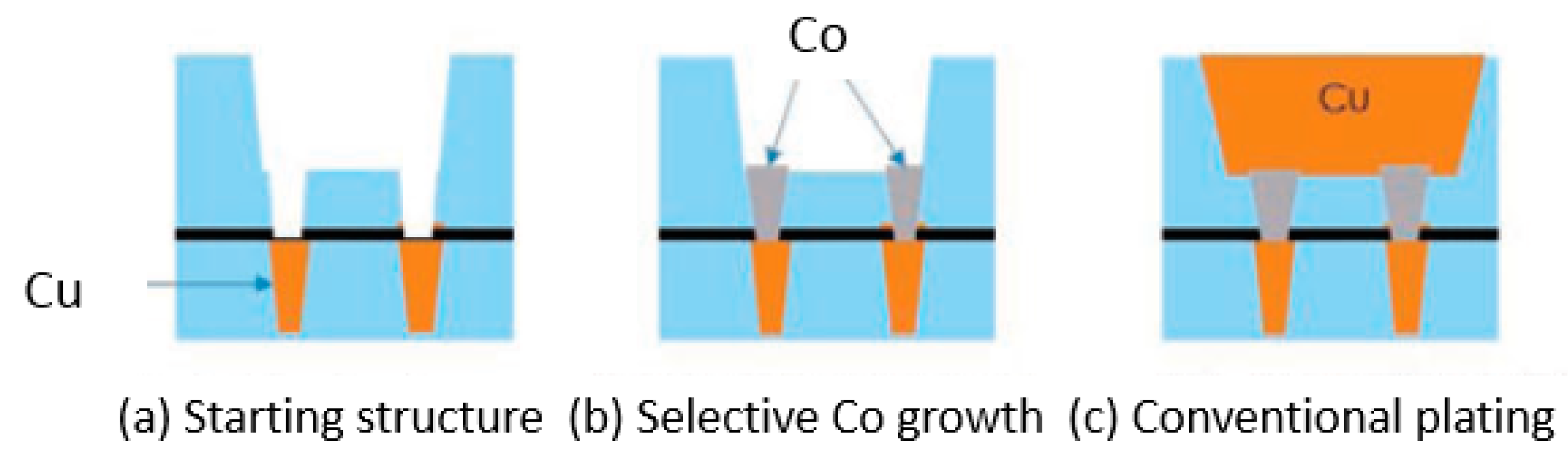

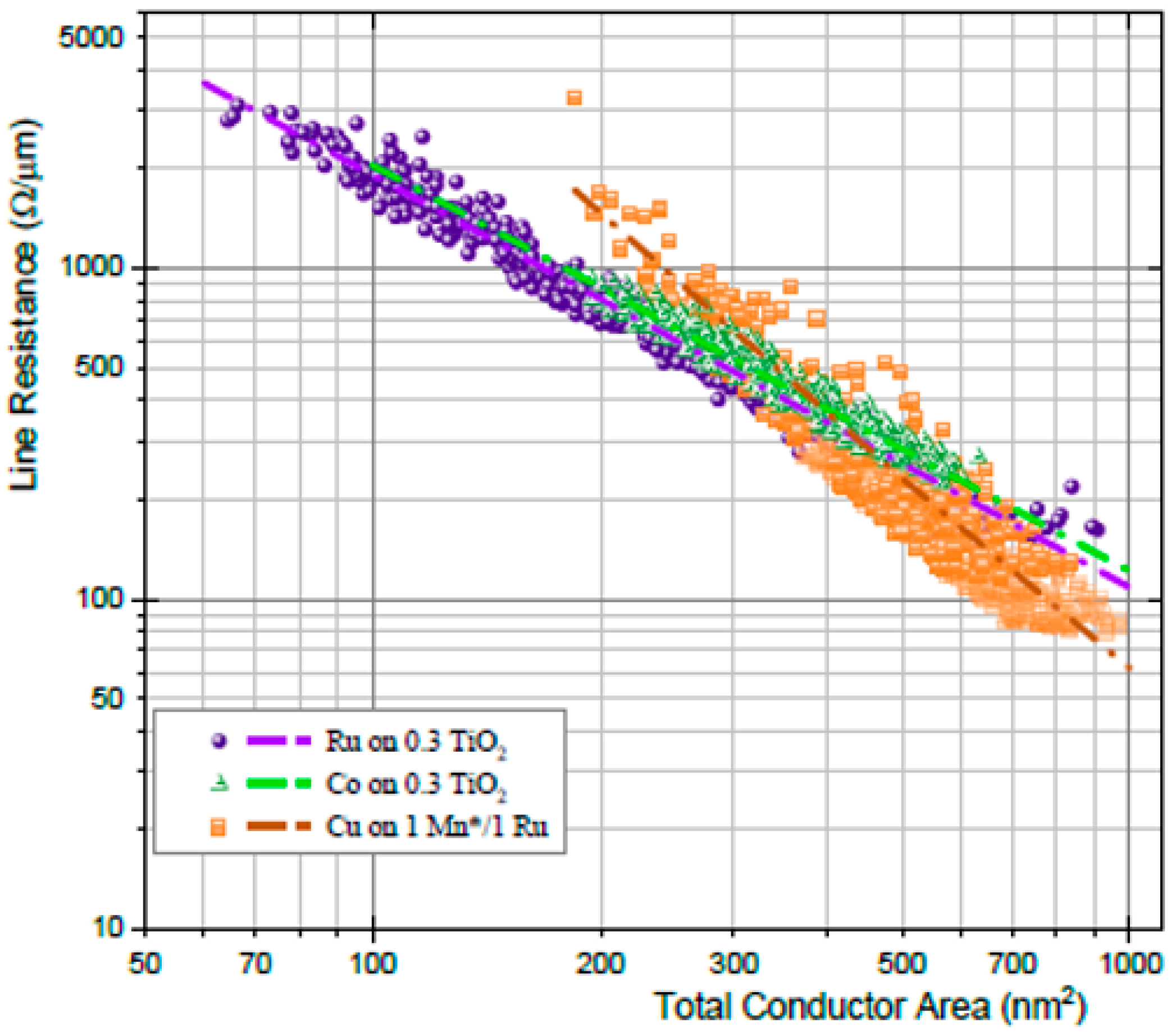

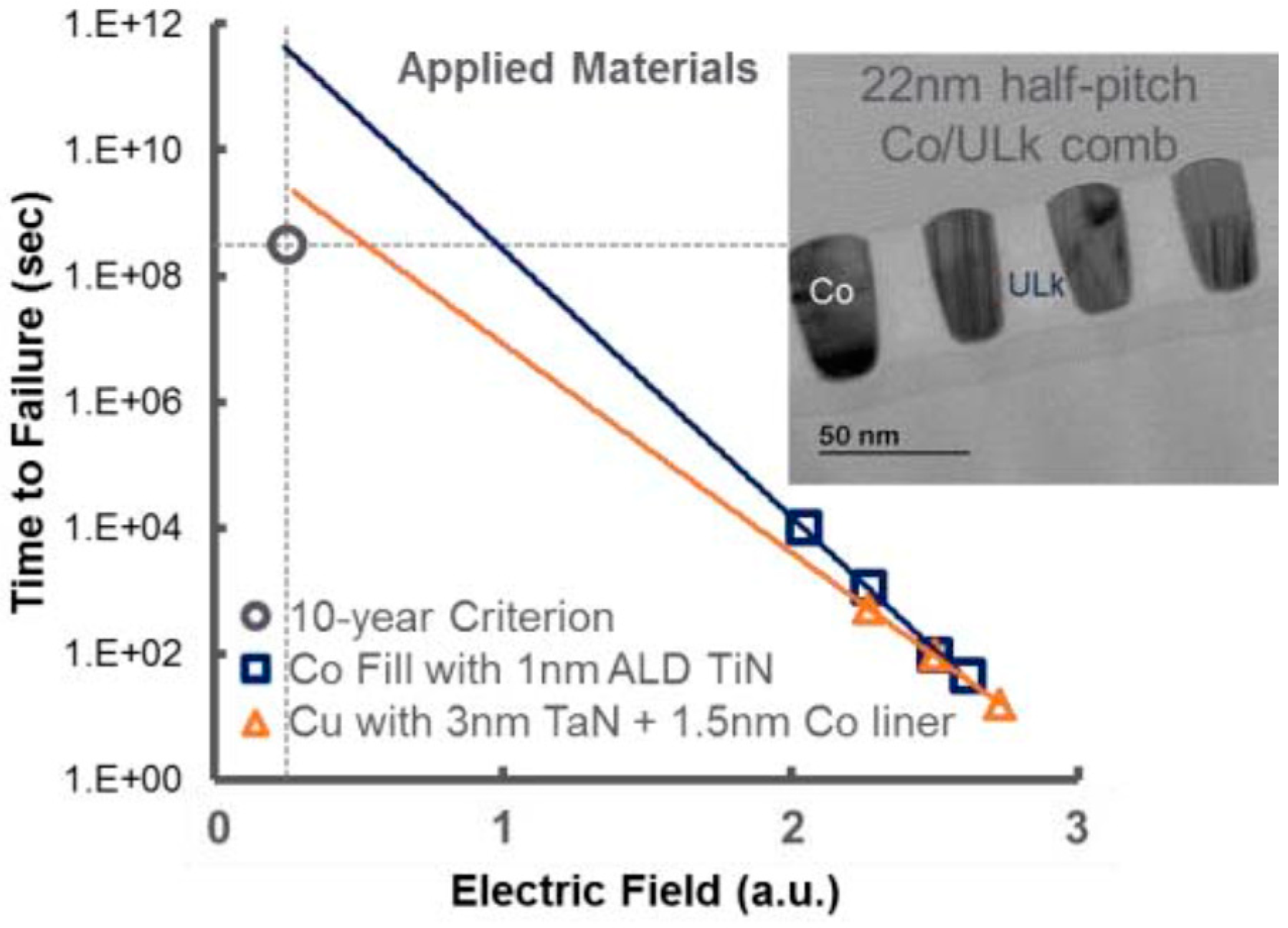

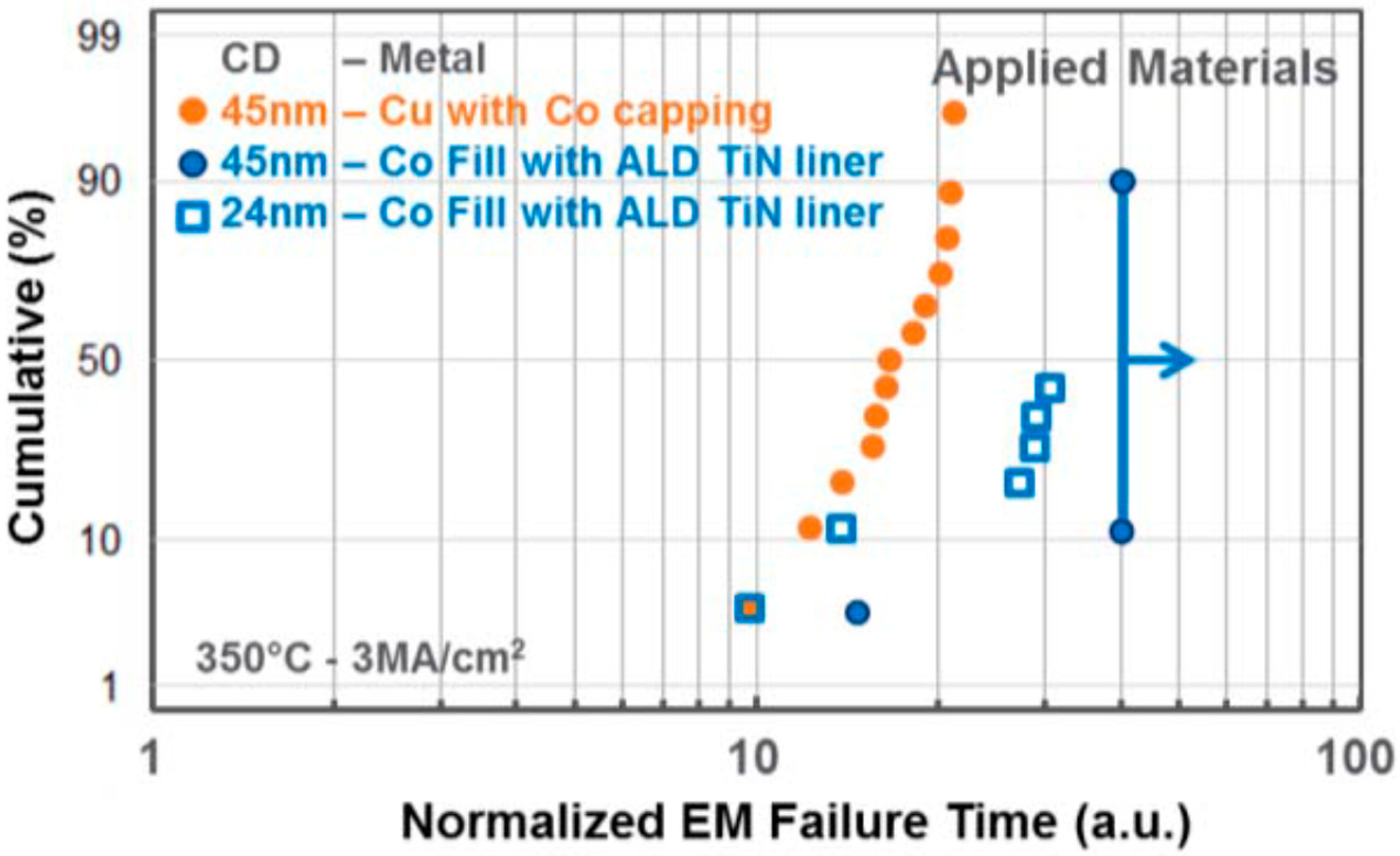

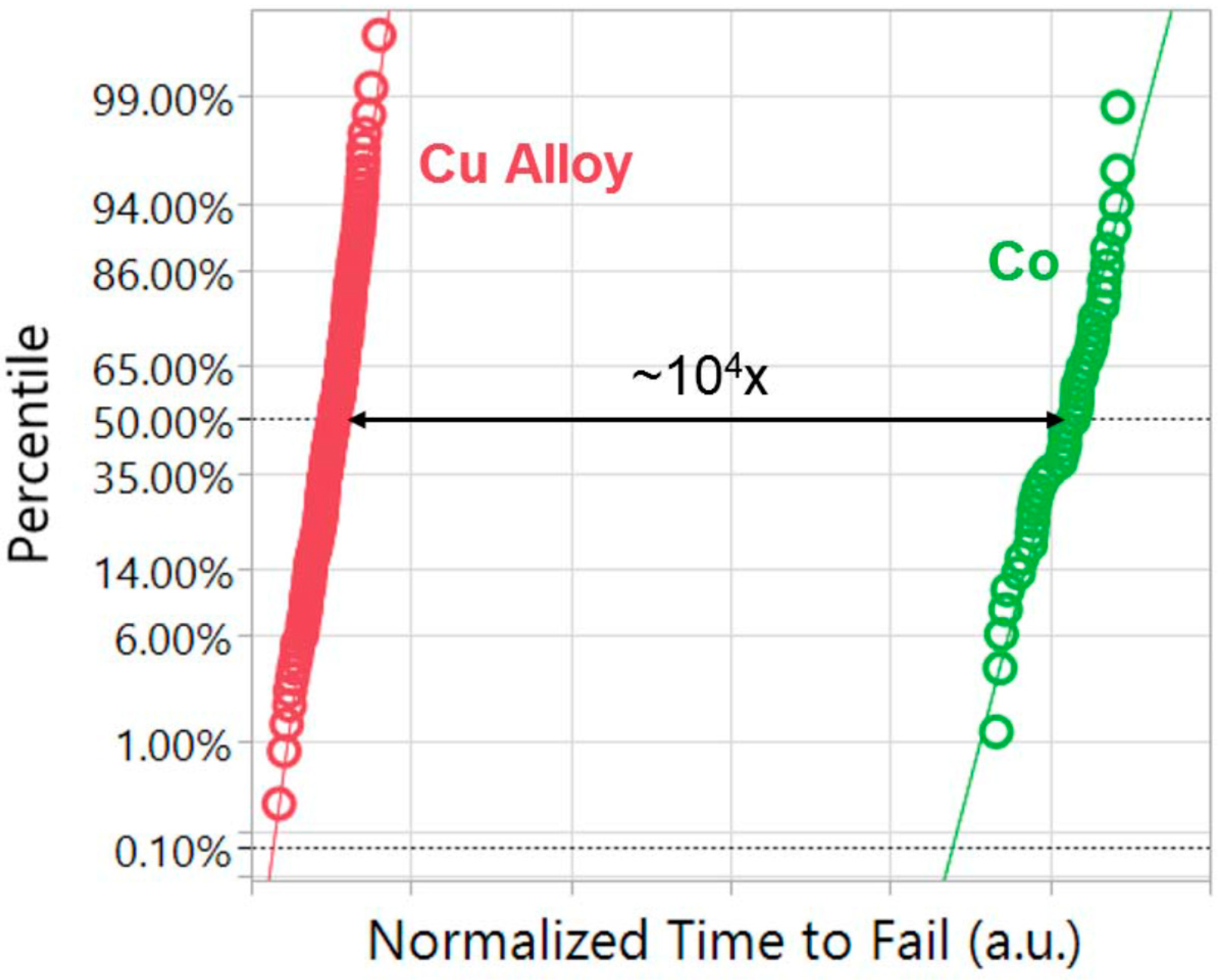

9. Interconnections in CMOS

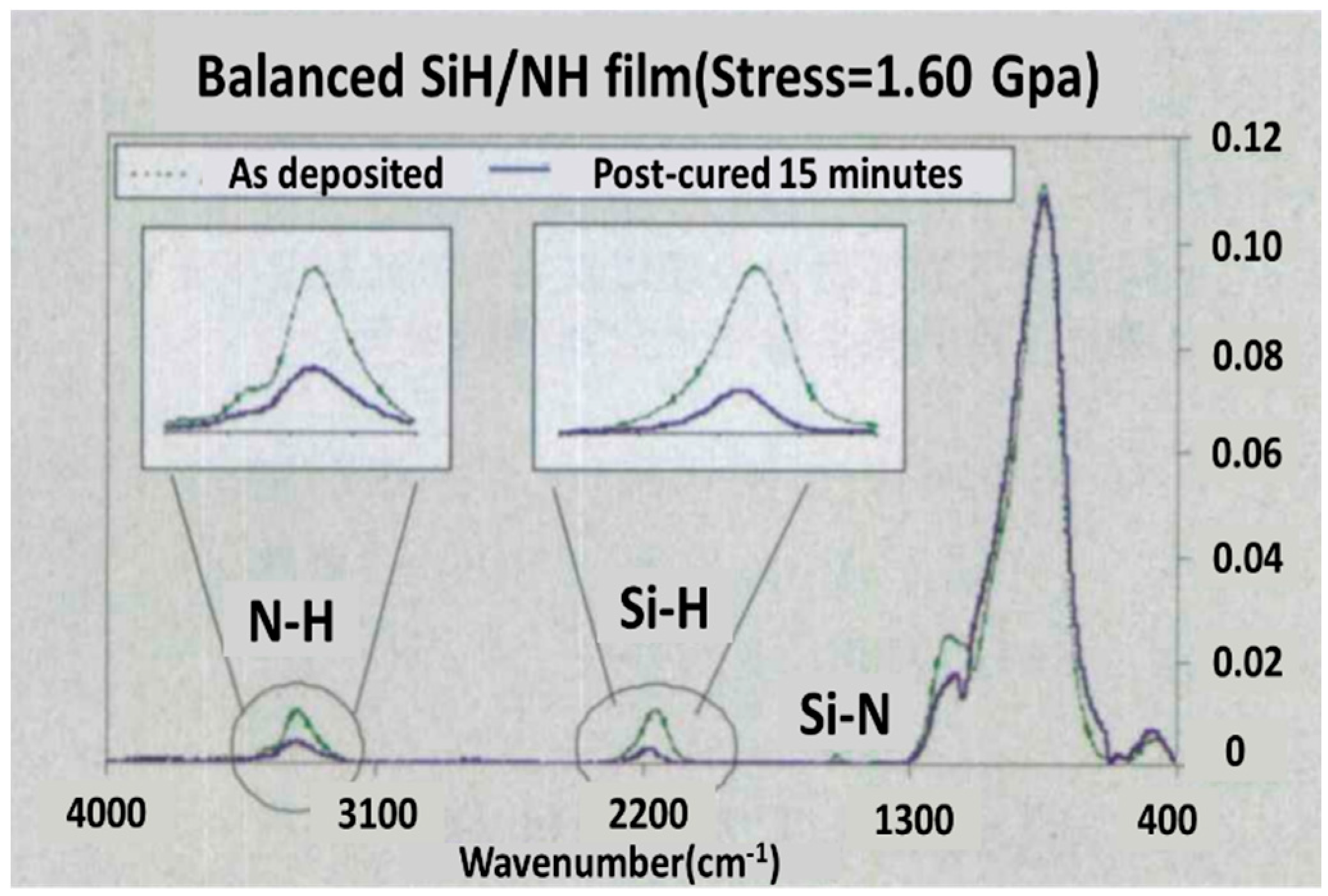

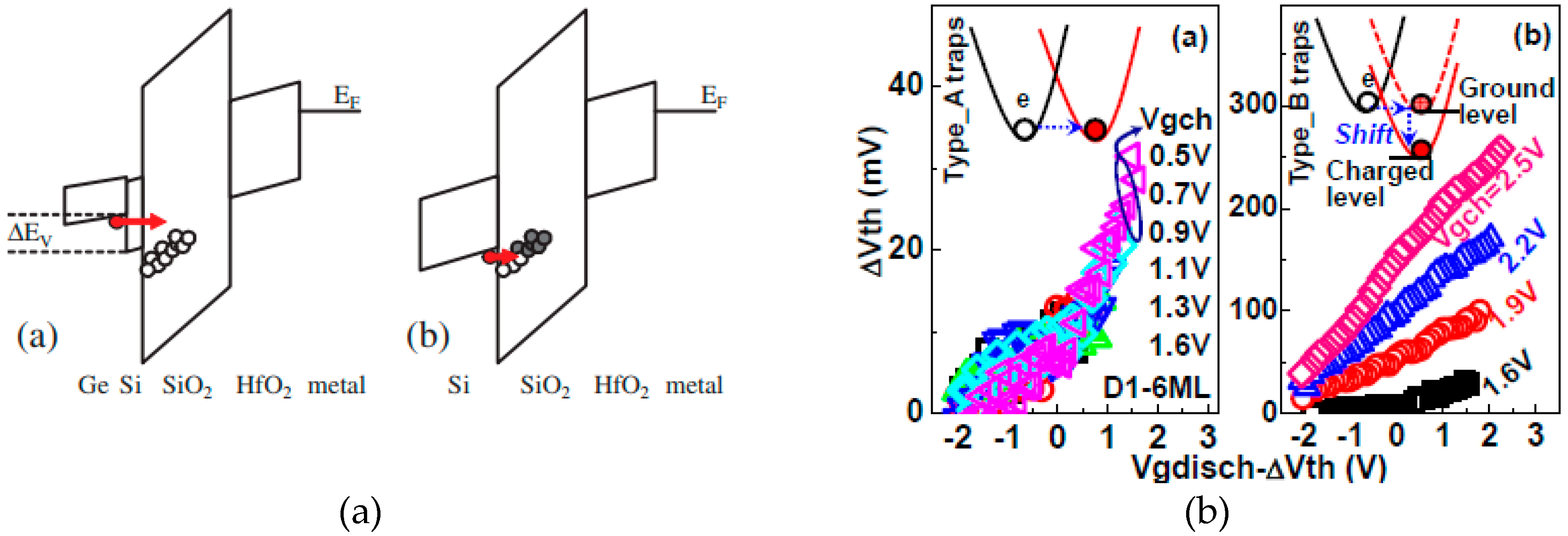

10. Stressors SiNx Contact Etch Stop Layer (CESL) Technology

10.1. High Tensile Stress CESL

10.2. High Compressive Stress CESL

11. Etching Evolution

12. BEOL for Nano-Scale Transistors

13. Reliability

13.1. New Material—Ge/GeSi

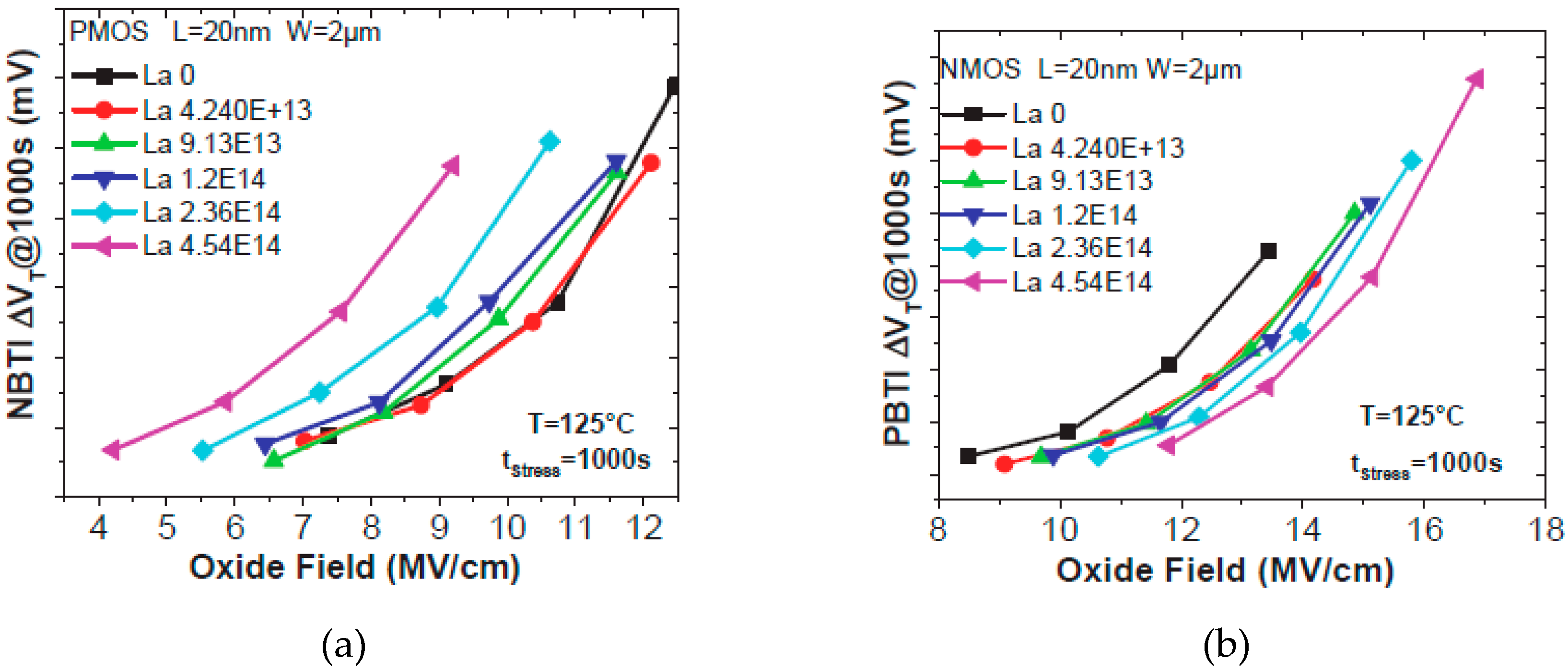

13.2. New Process—Dipole Formation

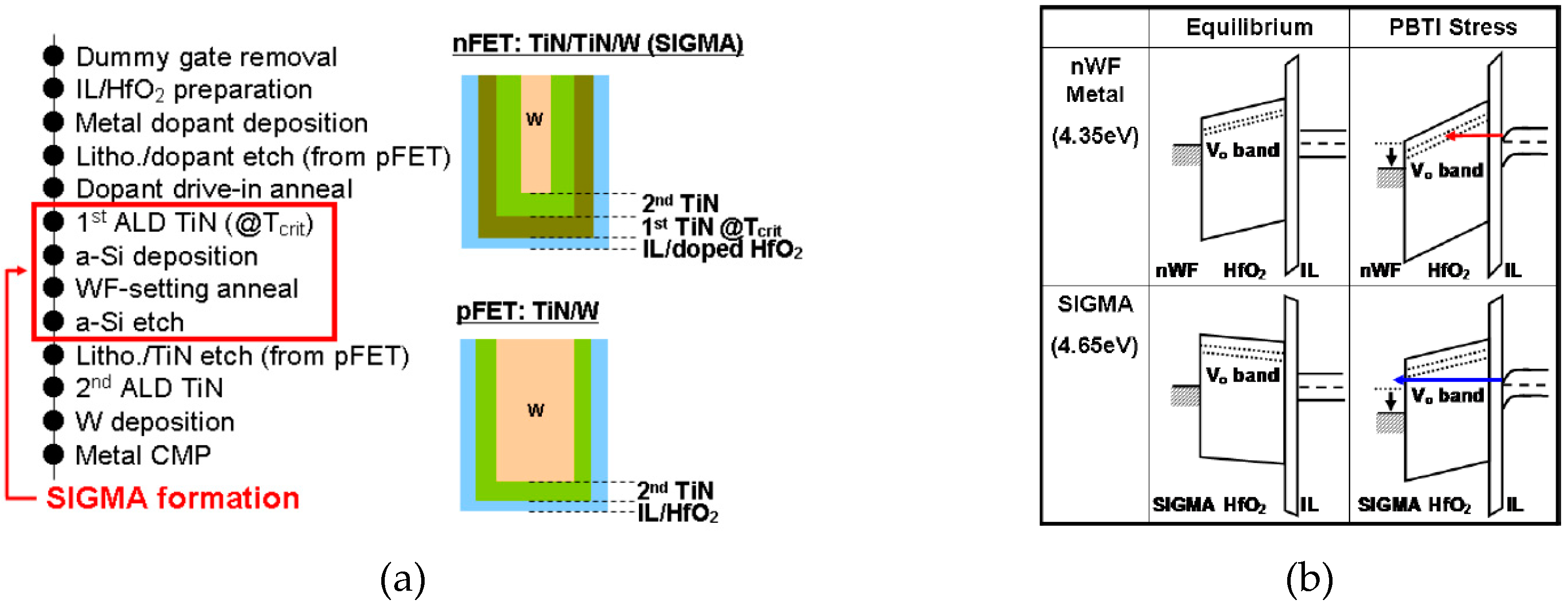

13.3. New Integration—Physical Mechanism

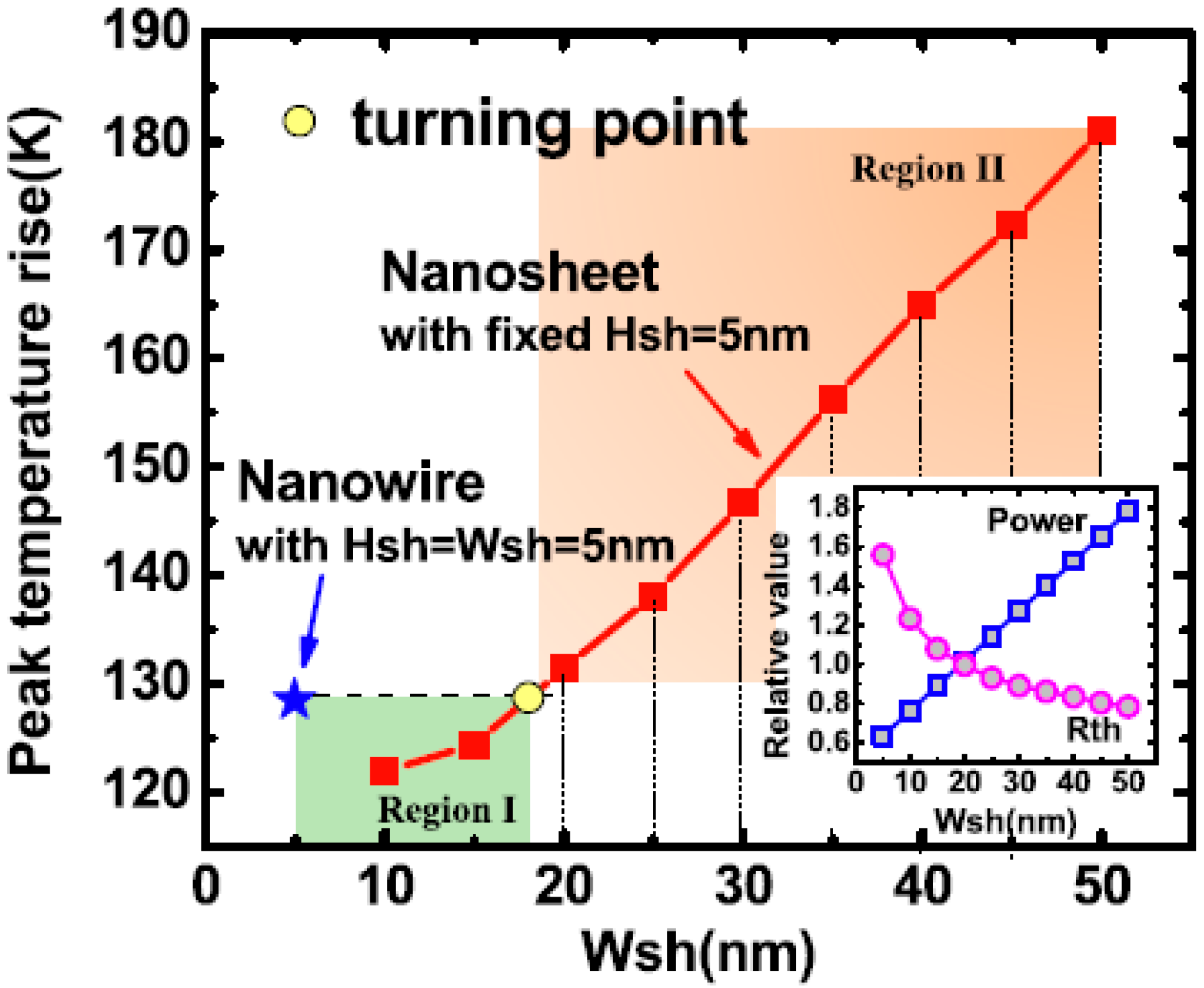

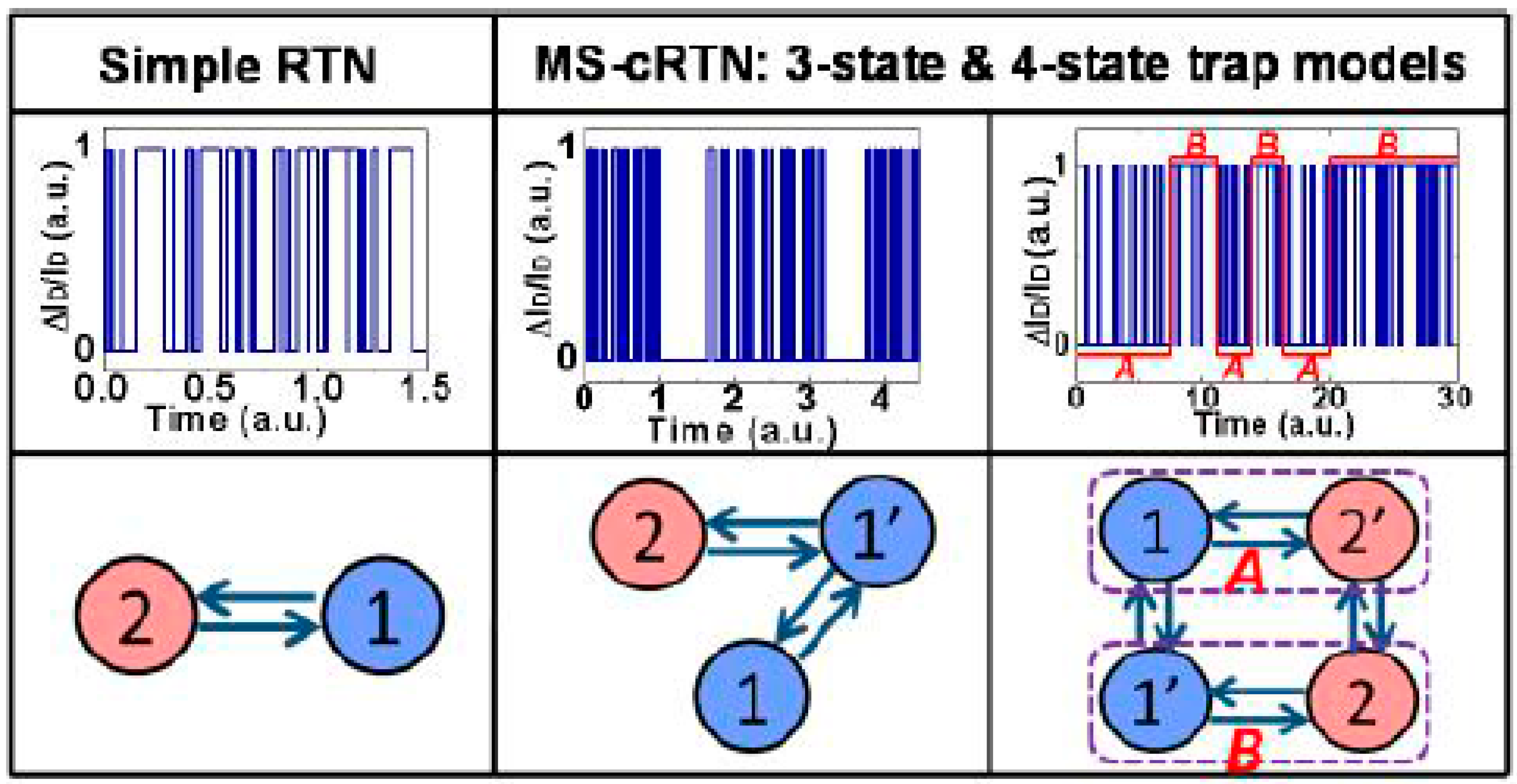

13.4. New Structure—Self-Heating (SH) and Random Telegraph Noise (RTN)

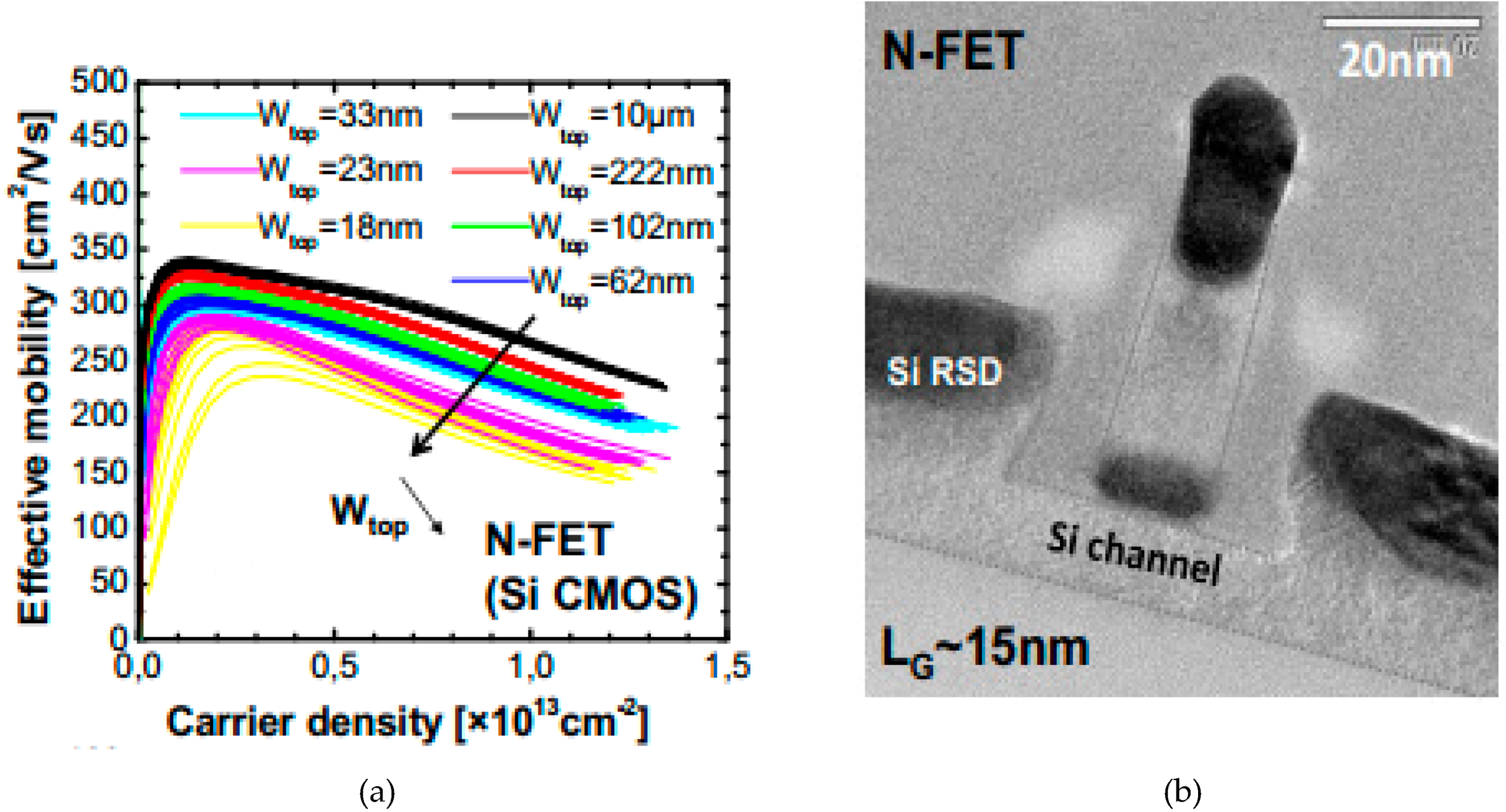

14. Channel Materials for Beyond Moore Era

14.1. III-V on Silicon

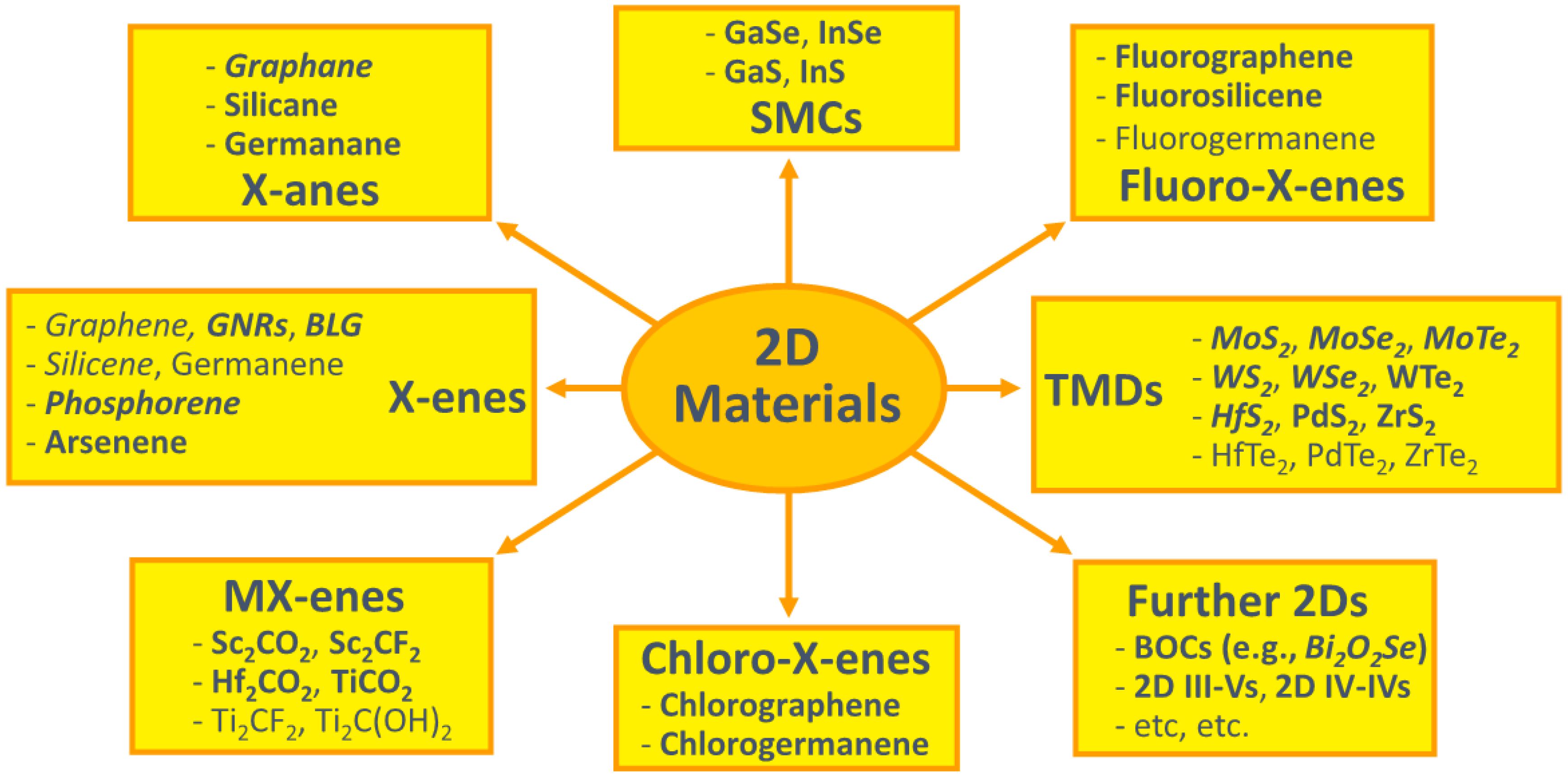

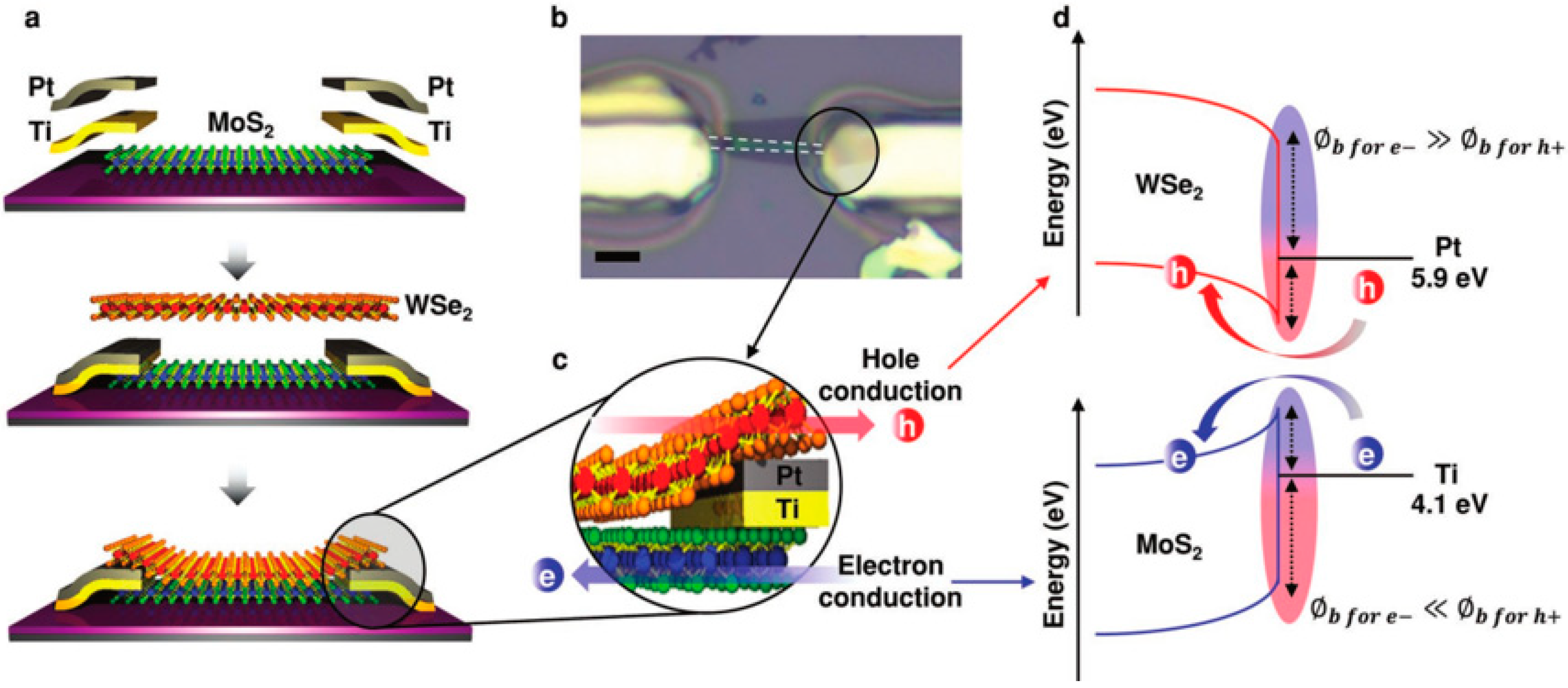

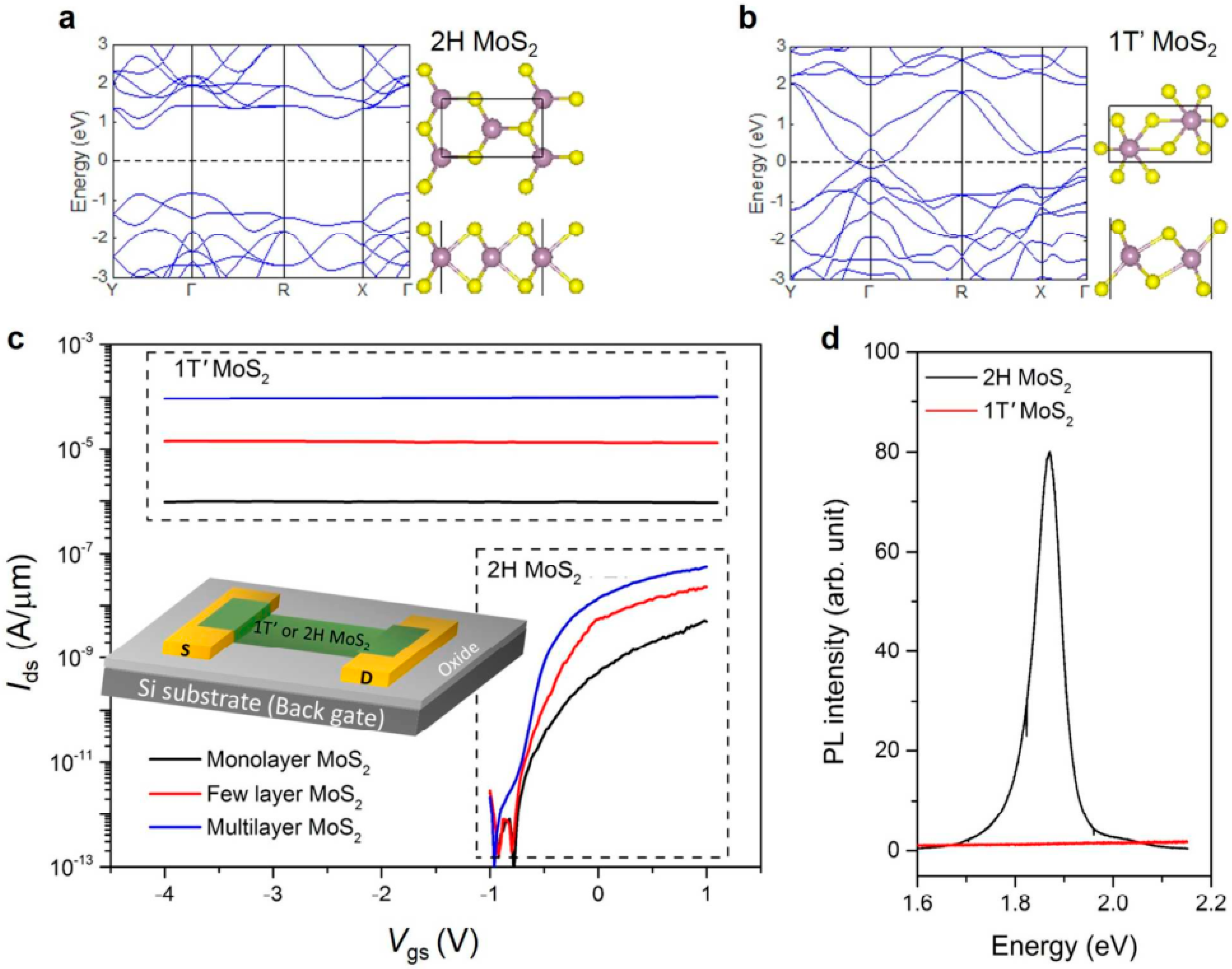

14.2. 2D Channel Materials

14.2.1. Graphene

Single Layer Graphene Field Effect Transistors

Graphene Nanoribbons Field Effect Transistors

Bilayer Graphene Field Effect Transistors

Graphene Heterojunction Field Effect Transistors

14.2.2. Graphene-Like Materials as Channel Materials

15. Advanced Characterization for Ultra-Miniaturized CMOS

15.1. CD-SEM

15.2. 3D AFM (Atomic Force Microscope)

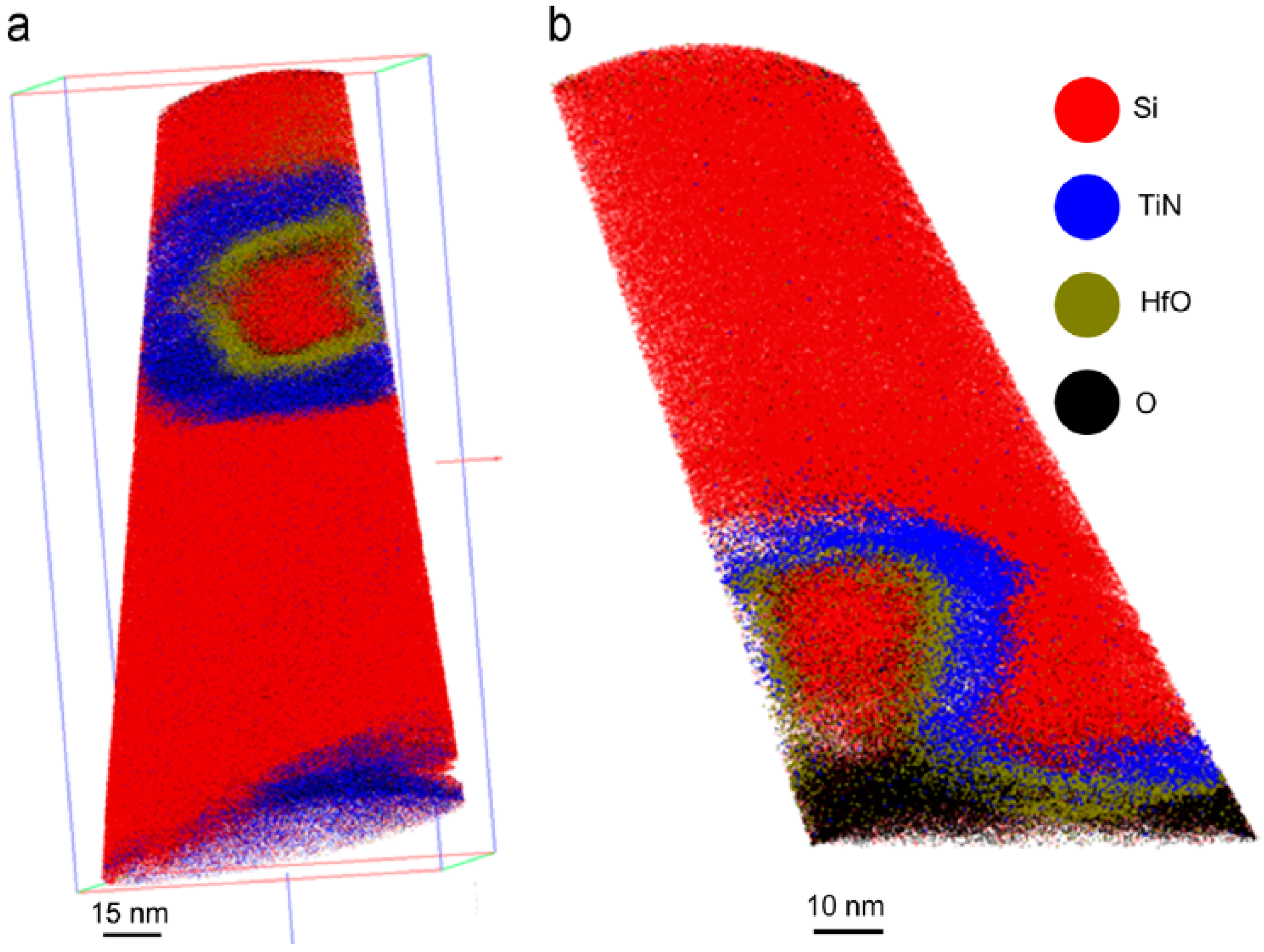

15.3. 3D APT (Atom Probe Tomography)

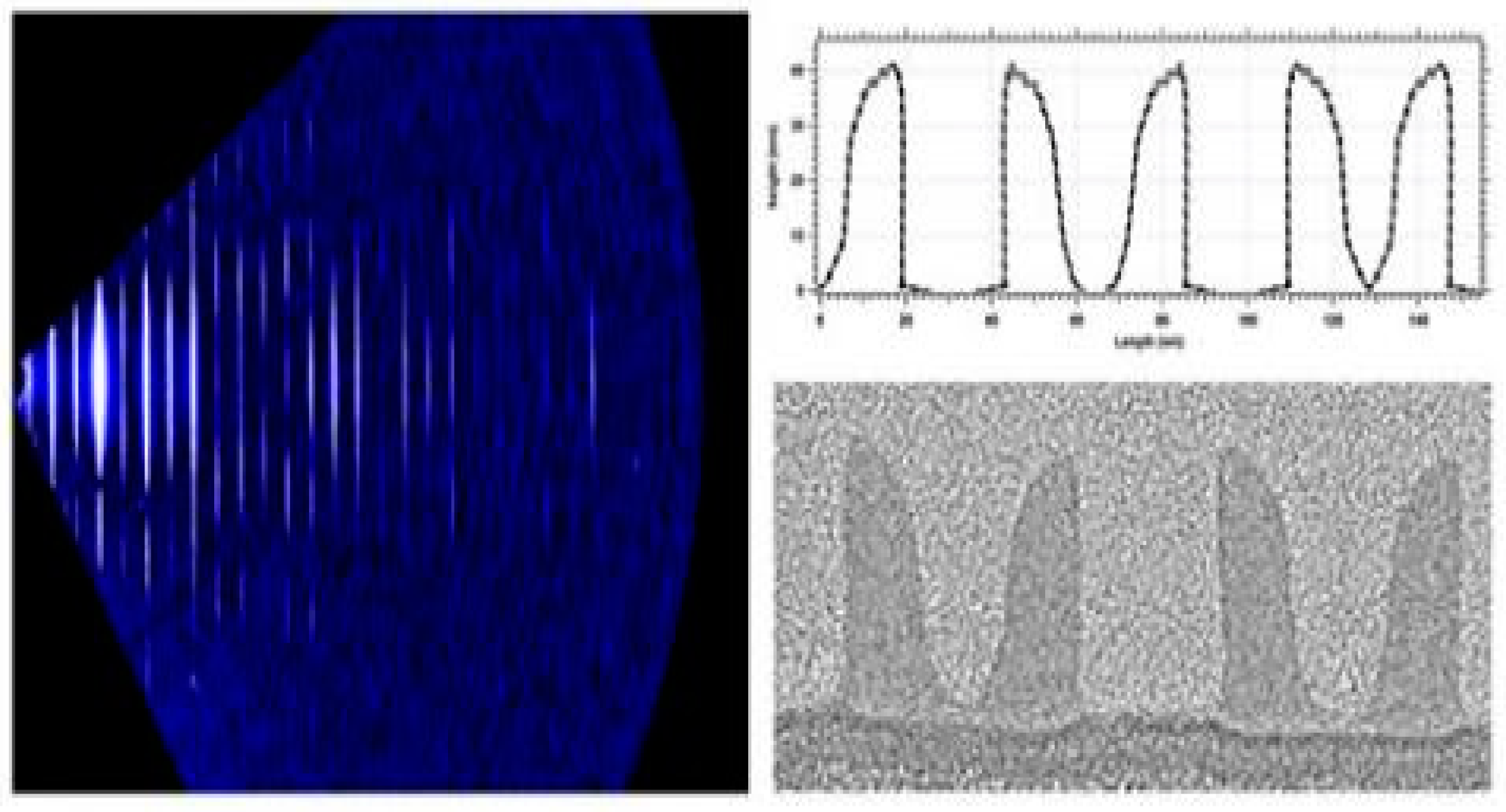

15.4. Optical Critical Dimension

15.5. Hybrid Metrology

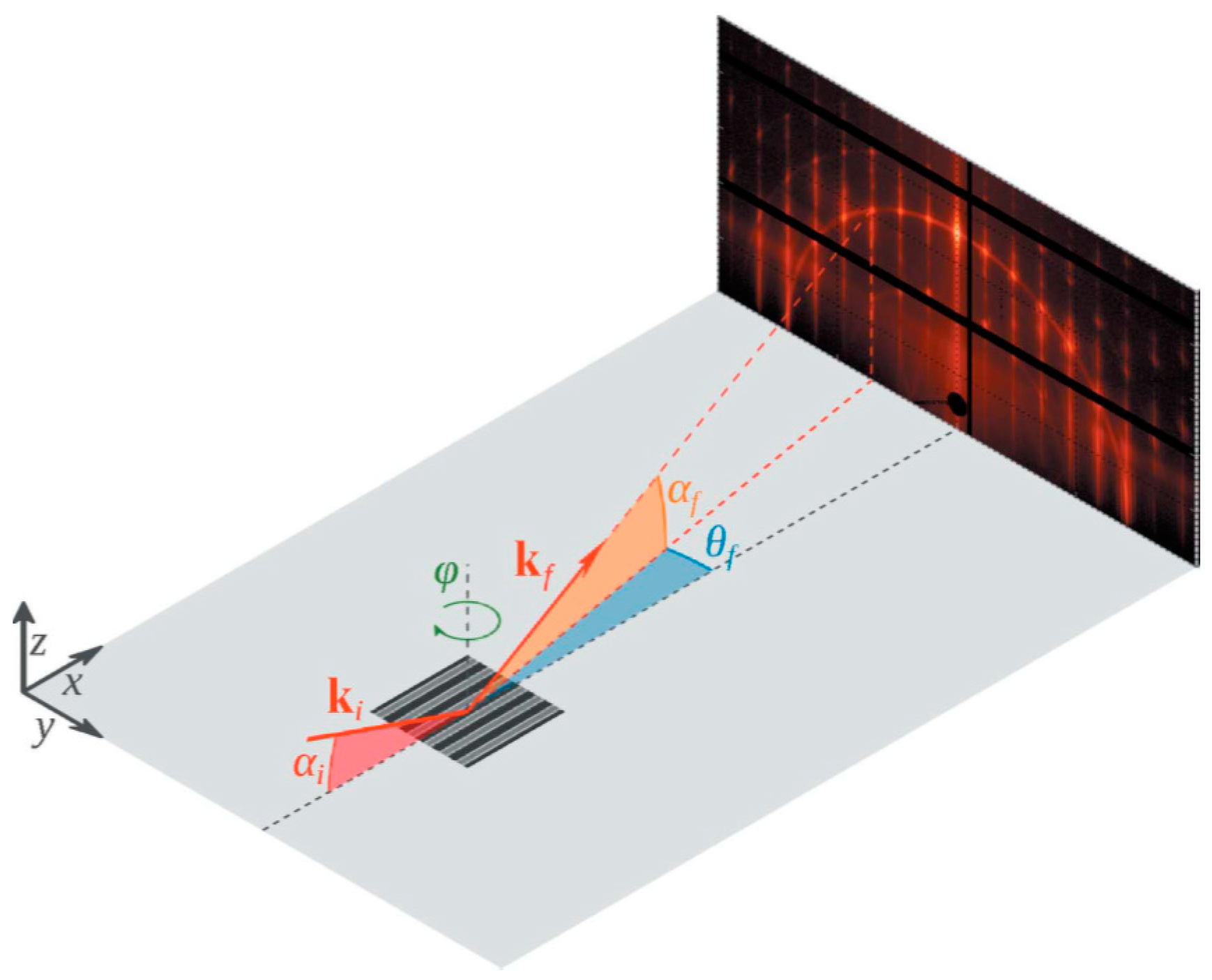

15.6. X-Ray Metrology Technologies

15.7. Artificial Intelligence in Metrology

16. Conclusions

Author Contributions

Acknowledgments

Conflicts of Interest

References

- Moore, G.E. Cramming More Components onto Integrated Circuits. Electronics 1965, 38, 114. [Google Scholar] [CrossRef]

- Colinge, J.-P. FinFETs and other Multi-Gate Transistors; Springer: New York, NY, USA, 2008. [Google Scholar]

- Natarajan, S.; Agostinelli, M.; Akbar, S.; Bost, M.; Bowonder, A.; Chikarmane, V.; Chouksey, S.; Dasgupta, A.; Fischer, K.; Fu, Q.; et al. A 14 nm logic technology featuring 2nd-generation FinFET, air-gapped interconnects, self-aligned double patterning and a 0.0588 µm2 SRAM cell size. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 3–7. [Google Scholar]

- Li, C.C.; Tsai, T.H.; Yuan, M.S.; Liao, C.C.; Chang, C.H.; Huang, T.C.; Liao, H.Y.; Lu, C.T.; Kuo, H.Y.; Hsieh, K.; et al. A 0.034 mm2, 725 fs RMS jitter, 1.8%/V frequency-pushing, 10.8–19.3 GHz transformer-based fractional-N all-digital PLL in 10 nm FinFET CMOS. In Proceedings of the 2016 IEEE Symposium on VLSI Circuits (VLSI-Circuits), Honolulu, HI, USA, 15–17 June 2016; pp. 1–2. [Google Scholar]

- Xu, M.; Zhu, H.L.; Zhao, L.C.; Yin, H.X.; Zhong, J.; Li, J.F.; Zhao, C.; Chen, D.P.; Ye, T.C. Improved Short Channel Effect Control in Bulk FinFETs with Vertical Implantation to Form Self-Aligned Halo and Punch-Through Stop Pocket. IEEE Electron Device Lett. 2015, 36, 648–650. [Google Scholar] [CrossRef]

- Yang, L.; Zhang, Q.Z.; Huang, Y.B.; Zheng, Z.S.; Li, B.; Li, B.H.; Zhang, X.Y.; Zhu, H.P.; Yin, H.X.; Guo, Q.; et al. Total Ionizing Dose Response and Annealing Behavior of Bulk nFinFETs with ON-State Bias Irradiation. IEEE Trans. Nucl. Sci. 2018, 65, 1503–1510. [Google Scholar] [CrossRef]

- Yakimets, D.; Bardon, M.; Garcia Jang, D.; Schuddinck, P.; Sherazi, Y.; Weckx, P.; Miyaguchi, K.; Parvais, B.; Raghavan, P.; Spessot, A.; Verkest, D.; Mocuta, A. Power aware FinFET and lateral nanosheet FET targeting for 3 nm CMOS technology. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 20.4.1–20.4.4. [Google Scholar]

- Cheng, K.; Seo, S.; Faltermeier, J.; Lu, D.; Standaert, T.; Ok, I.; Khakifirooz, A.; Vega, R.; Levin, T.; Li, J.; et al. Bottom oxidation through STI (BOTS)—A novel approach to fabricate dielectric isolated FinFETs on bulk substrates. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Zhang, Q.; Yin, H.; Luo, J.; Yang, H.; Meng, L.; Li, Y.; Wu, Z.; Zhang, Y.; Zhang, Y.; Qin, C.; et al. FOI FinFET with ultra-low parasitic resistance enabled by fully metallic source and drain formation on isolated bulk-fin. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 17.13.11–17.13.14. [Google Scholar]

- Ma, X.L.; Yin, H.X.; Hong, P.Z.; Xu, W.J. Self-Aligned Fin-On-Oxide (FOO) FinFETs for Improved SCE Immunity and Multi-V-TH Operation on Si Substrate. ECS Solid State Lett. 2015, 4, Q13–Q16. [Google Scholar] [CrossRef]

- Hou, Z.Z.; Zhang, Q.Z.; Yin, H.X.; Xiang, J.J.; Qin, C.L.; Yao, J.X.; Gu, J. Fabrication and Characterization of p-Channel Charge Trapping Type FOI-FinFET Memory with MAHAS Structure. ECS J. Solid State Sci. Technol. 2017, 6, Q136–Q142. [Google Scholar] [CrossRef]

- Xu, W.J.; Yin, H.X.; Ma, X.L.; Hong, P.Z.; Xu, M.; Meng, L.K. Novel 14-nm Scallop-Shaped FinFETs (S-FinFETs) on Bulk-Si Substrate. Nanoscale Res. Lett. 2015, 10, 249. [Google Scholar] [CrossRef]

- Mertens, H.; Ritzenthaler, R.; Hikavyy, A.; Kim, M.S.; Tao, Z.; Wostyn, K.; Chew, S.A.; Keersgieter, A.D.; Mannaert, G.; Rosseel, E.; et al. Gate-all-around MOSFETs based on vertically stacked horizontal Si nanowires in a replacement metal gate process on bulk Si substrates. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Lauer, I.; Loubet, N.; Kim, S.D.; Ott, J.A.; Mignot, S.; Venigalla, R.; Yamashita, T.; Standaert, T.; Faltermeier, J.; Basker, V.; et al. Si nanowire CMOS fabricated with minimal deviation from RMG FinFET technology showing record performance. In Proceedings of the 2015 Symposium on VLSI Technology, Kyoto, Japan, 16–18 June 2015; pp. T140–T141. [Google Scholar]

- Zhang, Q.Z.; Yin, H.X.; Meng, L.K.; Yao, J.X.; Li, J.J.; Wang, G.L.; Li, Y.D.; Wu, Z.H.; Xiong, W.J.; Yang, H.; et al. Novel GAA Si Nanowire p-MOSFETs With Excellent Short-Channel Effect Immunity via an Advanced Forming Process. IEEE Electron Device Lett. 2018, 39, 464–467. [Google Scholar] [CrossRef]

- Tu, H.; Zhao, H.; Wei, F.; Zhang, Q.; Du, J. Research Progress in Two-Dimensional Atomic Crystal Materials and Van der Waals Heterostructures. Chin. J. Rare Met. 2017, 41, 449–465. [Google Scholar]

- Pan, Y.; Jia, K.P.; Huang, K.L.; Wu, Z.H.; Bai, G.B.; Yu, J.H.; Zhang, Z.H.; Zhang, Q.Z.; Yin, H.X. Near-ideal subthreshold swing MoS2 back-gate transistors with an optimized ultrathin HfO2 dielectric layer. Nanotechnology 2019, 30, 095202. [Google Scholar] [CrossRef]

- Brunet, L.; Fenouillet-Beranger, C.; Batude, P.; Beaurepaire, S.; Ponthenier, F.; Rambal, N.; Mazzocchi, V.; Pin, J.; Acosta-Alba, P.; Kerdiles, S.; et al. Breakthroughs in 3D Sequential technology. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 7.2.1–7.2.4. [Google Scholar]

- Chiarella, T.; Witters, L.; Mercha, A.; Kerner, C.; Dittrich, R.; Rakowski, M.; Ortolland, C.; Ragnarsson, L.A.; Parvais, B.; De Keersgieter, A.; et al. Migrating from planar to FinFET for further CMOS scaling: SOI or bulk? In Proceedings of the 2009 Proceedings of the European Solid State Device Research Conference (ESSCIRC’09), Athens, Greece, 14–18 September 2009; pp. 84–87. [Google Scholar]

- Bae, G.; Bae, D.I.; Kang, M.; Hwang, S.M.; Kim, S.S.; Seo, B.; Kwon, T.Y.; Lee, T.J.; Moon, C.; Choi, Y.M.; et al. 3 nm GAA Technology featuring Multi-Bridge-Channel FET for Low Power and High Performance Applications. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 28.7.1–28.7.4. [Google Scholar]

- Sackinger, E.; Guggenbuhl, W. A high-swing, high-impedance MOS cascode circuit. IEEE J. Solid-State Circuits 1990, 25, 289–298. [Google Scholar] [CrossRef]

- Radamson, H.; Thylen, L. Monolithic Nanoscale Photonics-Electronics Integration in Silicon and other Group IV Elements; Elsevier Science & Technology: San Diego, CA, USA, 2014. [Google Scholar]

- Frank, D.J.; Dennard, R.H.; Nowak, E.; Solomon, P.M.; Taur, Y.; Wong, H.S.P. Device scaling limits of Si MOSFETs and their application dependencies. Proc. IEEE 2001, 89, 259–288. [Google Scholar] [CrossRef]

- Yaegashi, H. Pattern fidelity control in Multi-patterning towards 7 nm node. In Proceedings of the 2016 IEEE 16th International Conference on Nanotechnology (IEEE-NANO), Sendai, Japan, 22–25 August 2016; pp. 452–455. [Google Scholar]

- Jiang, J.; Chakrabarty, S.; Yu, M.F.; Ober, C.K. Metal Oxide Nanoparticle Photoresists for EUV Patterning. J. Photopolym Sci. Technol. 2014, 27, 663–666. [Google Scholar] [CrossRef]

- Mulkens, J.; Hanna, M.; Wei, H.; Vaenkatesan, V.; Megens, H.; Slotboom, D. Overlay and Edge Placement Control Strategies for the 7-nm node using EUV and ArF lithography. In Extreme Ultraviolet (EUV) Lithography VI; Wood, O.R., Panning, E.M., Eds.; SPIE: San Jose, CA, USA, 2016; Volume 9422. [Google Scholar]

- Kerkhof, M.V.D.; Jasper, H.; Levasier, L.; Peeters, R.; van Es, R.; Bosker, J.W.; Zdravkov, A.; Lenderink, E.; Evangelista, F.; Broman, P.; et al. Enabling sub-10nm node lithography: Presenting the NXE:3400B EUV scanner. Extreme Ultraviolet. Proc. SPIE 2017, 10143. [Google Scholar] [CrossRef]

- Nagahara, S.; Carcasi, M.; Shiraishi, G.; Nakagawa, H.; Dei, S.; Shiozawa, T.; Nafus, K.; De Simone, D.; Vandenberghe, G.; Stock, H.J.; Küchler, B. Photosensitized Chemically Amplified Resist (PSCAR) 2.0 for high-throughput and high-resolution EUV lithography: Dual photosensitization of acid generation and quencher decomposition by flood exposure. Proc. SPIE 2017, 10146. [Google Scholar] [CrossRef]

- Capelli, R.; Hellweg, D.; Dietzel, M.; Koch, M.; Wolke, C.; Kersteen, G. Aerial image based metrology of EUV masks: Recent achievements, status and outlook for the AIMS (TM) EUV platform. In Extreme Ultraviolet (EUV) Lithography IX; Goldberg, K.A., Ed.; SPIE: San Jose, CA, USA, 2018; Volume 10583. [Google Scholar]

- Wojdyla, A.; Benk, M.P.; Naulleau, P.P.; Goldberg, K.A. EUV photolithography mask inspection using Fourier ptychography. In Image Sensing Technologies: Materials, Devices, Systems, and Applications V; Dhar, N.K., Dutta, A.K., Eds.; SPIE: Orlando, FL, USA, 2018; Volume 10656. [Google Scholar]

- Turkot, B.; Carson, S.L.; Lio, A.N.; Liang, T.; Phillips, M.; McCool, B.; Stenehjem, E.; Crimmins, T.; Zhang, G.J.; Sivakumar, S. EUV Progress Toward HVM Readiness. In Extreme Ultraviolet (EUV) Lithography VII; Panning, E.M., Goldberg, K.A., Eds.; SPIE: San Jose, CA, USA, 2016; Volume 9776. [Google Scholar]

- Levinson, H.J.; Brunner, T.A. Current Challenges and Opportunities for EUV Lithography. In International Conference on Extreme Ultraviolet Lithography 2018; Ronse, K.G., Hendrickx, E., Naulleau, P.P., Gargini, P.A., Itani, T., Eds.; SPIE: Monterey, CA, USA, 2018; Volume 10809. [Google Scholar]

- Li, L.; Liu, X.; Pal, S.; Wang, S.L.; Ober, C.K.; Giannelis, E.P. Extreme ultraviolet resist materials for sub-7 nm patterning. Chem. Soc. Rev. 2017, 46, 4855–4866. [Google Scholar] [CrossRef] [PubMed]

- Jan, C.; Bhattacharya, U.; Brain, R.; Choi, S.; Curello, G.; Gupta, G.; Hafez, W.; Jang, M.; Kang, M.; Komeyli, K.; et al. A 22 nm SoC platform technology featuring 3-D tri-gate and high-k/metal gate, optimized for ultra low power, high performance and high density SoC applications. In Proceedings of the 2012 International Electron Devices Meeting, San Francisco, CA, USA, 10–13 December 2012; pp. 3.1.1–3.1.4. [Google Scholar]

- Jan, C.; Agostinelli, M.; Buehler, M.; Chen, Z.; Choi, S.; Curello, G.; Deshpande, H.; Gannavaram, S.; Hafez, W.; Jalan, U.; et al. A 32 nm SoC platform technology with 2nd generation high-k/metal gate transistors optimized for ultra low power, high performance, and high density product applications. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4. [Google Scholar]

- Radamson, H.H.; Zhang, Y.B.; He, X.B.; Cui, H.S.; Li, J.J.; Xiang, J.J.; Liu, J.B.; Gu, S.H.; Wang, G.L. The Challenges of Advanced CMOS Process from 2D to 3D. Appl. Sci. 2017, 7, 1047. [Google Scholar] [CrossRef]

- International Roadmap for Devices and Systems (IRDS™) 2017 Edition. Available online: https://irds.ieee.org/roadmap-2017 (accessed on 4 April 2019).

- Wu, H.; Gluschenkov, O.; Tsutsui, G.; Niu, C.; Brew, K.; Durfee, C.; Prindle, C.; Kamineni, V.; Mochizuki, S.; Lavoie, C.; et al. Parasitic Resistance Reduction Strategies for Advanced CMOS FinFETs Beyond 7 nm. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 35.4.1–35.4.4. [Google Scholar]

- Kise, N.; Kinoshita, H.; Yukimachi, A.; Kanazawa, T.; Miyamoto, Y. Fin width dependence on gate controllability of InGaAs channel FinFETs with regrown source/drain. Solid-State Electron. 2016, 126, 92–95. [Google Scholar] [CrossRef]

- Matsukawa, T.; Liu, Y.; Endo, K.; uchi, S.O.; Masahara, M. Variability origins of FinFETs and perspective beyond 20 nm node. In Proceedings of the IEEE 2011 International SOI Conference, Tempe, AZ, USA, 3–6 October 2011; pp. 1–28. [Google Scholar]

- Kavalieros, J.; Doyle, B.; Datta, S.; Dewey, G.; Doczy, M.; Jin, B.; Lionberger, D.; Metz, M.; Rachmady, W.; Radosavljevic, M.; et al. Tri-Gate Transistor Architecture with High-k Gate Dielectrics, Metal Gates and Strain Engineering. In Proceedings of the Digest of Technical Papers—Symposium on VLSI Technology, Honolulu, HI, USA, 13–15 June 2006; pp. 50–51. [Google Scholar]

- Jan, C.; Al-amoody, F.; Chang, H.; Chang, T.; Chen, Y.; Dias, N.; Hafez, W.; Ingerly, D.; Jang, M.; Karl, E.; et al. A 14 nm SoC platform technology featuring 2nd generation Tri-Gate transistors, 70 nm gate pitch, 52 nm metal pitch, and 0.0499 um2 SRAM cells, optimized for low power, high performance and high density SoC products. In Proceedings of the 2015 Symposium on VLSI Circuits (VLSI Circuits), Kyoto, Japan, 17–19 June 2015; pp. T12–T13. [Google Scholar]

- Jacob, A.P.; Xie, R.; Sung, M.G.; Liebmann, L.; Lee, R.T.P.; Taylor, B. Scaling Challenges for Advanced CMOS Devices. Int. J. High Speed Electron. Syst. 2017, 26, 2–76. [Google Scholar] [CrossRef]

- Veloso, A.; De Keersgieter, A.; Matagne, P.; Horiguchi, N.; Collaert, N. Advances on doping strategies for triple-gate finFETs and lateral gate-all-around nanowire FETs and their impact on device performance. Mater. Sci. Semicond. Process. 2017, 62, 2–12. [Google Scholar] [CrossRef]

- Current, M.I. Ion implantation of advanced silicon devices: Past, present and future. Mater. Sci. Semicond. Process. 2017, 62, 13–22. [Google Scholar] [CrossRef]

- Ghani, T.; Armstrong, M.; Auth, C.; Bost, M.; Charvat, P.; Glass, G.; Hoffmann, T.; Johnson, K.; Kenyon, C.; Klaus, J.; et al. A 90 nm high volume manufacturing logic technology featuring novel 45nm gate length strained silicon CMOS transistors. In Proceedings of the IEEE International Electron Devices Meeting 2003, Washington, DC, USA, 8–10 December 2003; pp. 11.16.11–11.16.13. [Google Scholar]

- Bai, P.; Auth, C.; Balakrishnan, S.; Bost, M.; Brain, R.; Chikarmane, V.; Heussner, R.; Hussein, M.; Hwang, J.; Ingerly, D.; et al. A 65 nm logic technology featuring 35 nm gate lengths, enhanced channel strain, 8 Cu interconnect layers, low-k ILD and 0.57 μm2 SRAM cell. In Proceedings of the IEDM Technical Digest. IEEE International Electron Devices Meeting, 2004, San Francisco, CA, USA, 13–15 December 2004; pp. 657–660. [Google Scholar] [CrossRef]

- Jan, C.H.; Bai, P.; Biswas, S.; Buehler, M.; Chen, Z.P.; Curello, G.; Gannavaram, S.; Hafez, W.; He, J.; Hicks, J.; et al. A 45 nm low power system-on-chip technology with dual gate (logic and I/O) high-k/metal gate strained silicon transistors. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–4. [Google Scholar] [CrossRef]

- Natarajan, S.; Armstrong, M.; Bost, M.; Brain, R.; Brazier, M.; Chang, C.-H.; Chikarmane, V.; Childs, M.; Deshpande, H.; Dev, K.; et al. A 32 nm logic technology featuring 2nd-generation high-k+ metal-gate transistors, enhanced channel strain and 0.171 μm2 SRAM cell size in a 291 Mb array. In Proceedings of the 2008 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2008; pp. 1–3. [Google Scholar] [CrossRef]

- Thompson, S.; Sun, G.; Wu, K.; Lim, J.; Nishida, T. Key differences for process-induced uniaxial vs. substrate-induced biaxial stressed Si and Ge channel MOSFETs. In Proceedings of the Electron Devices Meeting, 2004, IEDM Technical Digest, San Francisco, CA, USA, 13–15 December 2004; pp. 221–224. [Google Scholar]

- Ohta, H.; Kim, Y.; Shimamune, Y.; Sakuma, T.; Hatada, A.; Katakami, A.; Soeda, T.; Kawamura, K.; Kokura, H.; Morioka, H.; et al. High performance 30 nm gate bulk CMOS for 45 nm node with/spl Sigma/-shaped SiGe-SD. In Proceedings of the IEEE International Electron Devices Meeting, 2005, IEDM Technical Digest, Washington, DC, USA, 5 December 2005; pp. 247–250. [Google Scholar]

- Tamura, N.; Shimamune, Y. 45 nm CMOS technology with low temperature selective epitaxy of SiGe. Appl. Surf. Sci. 2008, 254, 6067–6071. [Google Scholar] [CrossRef]

- Qin, C.L.; Yin, H.X.; Wang, G.L.; Hong, P.Z.; Ma, X.L.; Cui, H.S.; Lu, Y.H.; Meng, L.K.; Yin, H.Z.; Zhong, H.C.; et al. Study of sigma-shaped source/drain recesses for embedded-SiGe pMOSFETs. Microelectron. Eng. 2017, 181, 22–28. [Google Scholar] [CrossRef]

- Vescan, L.; Grimm, K.; Dieker, C. Facet investigation in selective epitaxial growth of Si and SiGe on (001) Si for optoelectronic devices. J. Vac. Sci. Technol. B 1998, 16, 1549–1554. [Google Scholar] [CrossRef]

- Dutartre, D.; Talbot, A. Facet propagation in Si and SiGe epitaxy or etching. ECS Trans. 2006, 3, 473–487. [Google Scholar] [CrossRef]

- Mujumdar, S.; Maitra, K.; Datta, S. Layout-Dependent Strain Optimization for p-Channel Trigate Transistors. IEEE Trans. Electron Devices 2012, 59, 72–78. [Google Scholar] [CrossRef]

- Hallstedt, J.; Kolahdouz, M.; Ghandi, R.; Radamson, H.H. Pattern dependency in selective epitaxy of B-doped SiGe layers for advanced metal oxide semiconductor field effect transistors. J. Appl. Phys. 2008, 103, 054907. [Google Scholar] [CrossRef]

- Radamson, H.H.; Kolahdouz, M. Selective epitaxy growth of Si1-x Gex layers for MOSFETs and FinFET. J. Mater. Sci. Mater. Electron. 2015, 26, 4584–4603. [Google Scholar] [CrossRef]

- Wang, G.L.; Moeen, M.; Abedin, A.; Xu, Y.F.; Luo, J.; Guo, Y.L.; Qin, C.L.; Tang, Z.Y.; Yin, H.Z.; Li, J.F.; et al. Impact of pattern dependency of SiGe layers grown selectively in source/drain on the performance of 22 nm node pMOSFETs. Solid-State Electron. 2015, 114, 43–48. [Google Scholar] [CrossRef]

- Qin, C.L.; Wang, G.L.; Kolahdouz, M.; Luo, J.; Yin, H.X.; Yang, P.; Li, J.F.; Zhu, H.L.; Chao, Z.; Ye, T.C.; et al. Impact of pattern dependency of SiGe layers grown selectively in source/drain on the performance of 14 nm node FinFETs. Solid-State Electron. 2016, 124, 10–15. [Google Scholar] [CrossRef]

- Wang, G.; Luo, J.; Qin, C.; Cui, H.; Liu, J.; Jia, K.; Li, J.; Yang, T.; Li, J.; Yin, H.; et al. Integration of Selective Epitaxial Growth of SiGe/Ge Layers in 14nm Node FinFETs. ECS Trans. 2016, 75, 273–279. [Google Scholar] [CrossRef]

- Loo, R.; Hikavyy, A.Y.; Witters, L.; Schulze, A.; Arimura, H.; Cott, D.; Mitard, J.; Porret, C.; Mertens, H.; Ryan, P.; et al. Processing Technologies for Advanced Ge Devices. ECS J. Solid State Sci. Technol. 2016, 6, P14–P20. [Google Scholar] [CrossRef]

- Radamson, H.H.; Luo, J.; Simeon, E.; Chao, Z. Past, Present and Future of CMOS; Elsevier: Duxford, UK, 2018. [Google Scholar]

- Wang, G.L.; Abedin, A.; Moeen, M.; Kolandouz, M.; Luo, J.; Guo, Y.L.; Chen, T.; Yin, H.X.; Zhu, H.L.; Li, J.F.; et al. Integration of highly-strained SiGe materials in 14 nm and beyond nodes FinFET technology. Solid-State Electron. 2015, 103, 222–228. [Google Scholar] [CrossRef]

- Wan, G.X.; Wang, G.L.; Zhu, H.L. Hetero-Epitaxy and Self-Adaptive Stressor Based on Freestanding Fin for the 10 nm Node and Beyond. Chin. Phys. Lett. 2017, 34, 4. [Google Scholar] [CrossRef]

- Wang, G.L.; Luo, J.; Qin, C.L.; Liang, R.R.; Xu, Y.F.; Liu, J.B.; Li, J.F.; Yin, H.X.; Yan, J.; Zhu, H.L.; et al. Integration of Highly Strained SiGe in Source and Drain with HK and MG for 22 nm Bulk PMOS Transistors. Nanoscale Res. Lett. 2017, 12, 078502. [Google Scholar] [CrossRef]

- Han, K.; Tang, S.; Rockwell, T.; Godet, L.; Persing, H.; Campbell, C.; Salimian, S. A novel plasma-based technique for conformal 3D FINFET doping. In Proceedings of the 2012 12th International Workshop on Junction Technology, Shanghai, China, 14–15 May 2012; pp. 35–37. [Google Scholar]

- Felch, S.; Hobbs, C.; Barnett, J.; Etienne, H.; Duchaine, J.; Rodgers, M.; Bennett, S.; Torregrosa, F.; Spiegel, Y.; Roux, L. Plasma doping of silicon fin structures. In Proceedings of the 11th International Workshop on Junction Technology (IWJT), Kyoto, Japan, 9–10 June 2011; pp. 22–25. [Google Scholar]

- Linford, M.R.; Chidsey, C.E.D. Alkyl monolayers covalently bonded to silicon surfaces. J. Am. Chem. Soc. 1993, 115, 12631–12632. [Google Scholar] [CrossRef]

- Ye, L.; Pujari, S.P.; Zuilhof, H.; Kudernac, T.; de Jong, M.P.; van der Wiel, W.G.; Huskens, J. Controlling the Dopant Dose in Silicon by Mixed-Monolayer Doping. ACS Appl. Mater. Interfaces 2015, 7, 3231–3236. [Google Scholar] [CrossRef]

- Sieval, A.B.; Vleeming, V.; Zuilhof, H.; Sudholter, E.J.R. An improved method for the preparation of organic monolayers of 1-alkenes on hydrogen-terminated silicon surfaces. Langmuir 1999, 15, 8288–8291. [Google Scholar] [CrossRef]

- Ford, A.C.; Ho, J.C.; Chueh, Y.; Javey, A. Monolayer doping and diameter-dependent electron mobility assessment of nanowires. In Proceedings of the 2009 IEEE International Conference on IC Design and Technology, Austin, TX, USA, 18–20 May 2009; pp. 223–227. [Google Scholar]

- Ok, I.; Ang, K.; Hobbs, C.; Baek, R.H.; Kang, C.Y.; Snow, J.; Nunan, P.; Nadahara, S.; Kirsch, P.D.; Jammy, R. Conformal, low-damage shallow junction technology (Xj~5 nm) with optimized contacts for FinFETs as a Solution Beyond 14 nm Node. In Proceedings of the 2012 12th International Workshop on Junction Technology, Shanghai, China, 14–15 May 2012; pp. 29–34. [Google Scholar]

- Ho, J.C.; Yerushalmi, R.; Jacobson, Z.A.; Fan, Z.; Alley, R.L.; Javey, A. Controlled nanoscale doping of semiconductors via molecular monolayers. Nat. Mater. 2008, 7, 62–67. [Google Scholar] [CrossRef]

- Long, B.; Verni, G.A.; Connell, J.O.; Holmes, J.; Shayesteh, M.; Connell, D.O.; Duffy, R. Molecular Layer Doping: Non-destructive doping of silicon and germanium. In Proceedings of the 2014 20th International Conference on Ion Implantation Technology (IIT), Portland, OR, USA, 26 June–4 July 2014; pp. 1–4. [Google Scholar]

- Kim, Y.S.; Kown, H. Ultra-shallow junction formation on 3D silicon and germanium device structures by ion energy decoupled plasma doping. In Proceedings of the 2017 17th International Workshop on Junction Technology (IWJT), Uji, Japan, 1–2 June 2017; pp. 62–65. [Google Scholar]

- Takeuchi, H.; King, T.J. Scaling limits of hafnium-silicate films for gate-dielectric applications. Appl. Phys. Lett. 2003, 83, 788–790. [Google Scholar] [CrossRef]

- Seong, N.J.; Yoon, S.G.; Yeom, S.J.; Woo, H.K.; Kil, D.S.; Roh, J.S.; Sohn, H.C. Effect of nitrogen incorporation on improvement of leakage properties in high-k HfO2 capacitors treated by N-2-plasma. Appl. Phys. Lett. 2005, 87. [Google Scholar] [CrossRef]

- Zhao, C.; Witters, T.; Brijs, B.; Bender, H.; Richard, O.; Caymax, M.; Heeg, T.; Schubert, J.; Afanas’ev, V.V.; Stesmans, A.; et al. Ternary rare-earth metal oxide high-k layers on silicon oxide. Appl. Phys. Lett. 2005, 86. [Google Scholar] [CrossRef]

- Barlage, D.; Arghavani, R.; Dewey, G.; Doczy, M.; Doyle, B.; Kavalieros, J.; Murthy, A.; Roberds, B.; Stokley, P.; Chau, R. High-frequency response of 100 nm integrated CMOS transistors with high-K gate dielectrics. In Proceedings of the International Electron Devices Meeting. Technical Digest, Washington, DC, USA, 2–5 December 2001; pp. 10.16.11–10.16.14. [Google Scholar]

- Packan, P.; Akbar, S.; Armstrong, M.; Bergstrom, D.; Brazier, M.; Deshpande, H.; Dev, K.; Ding, G.; Ghani, T.; Golonzka, O.; et al. High performance 32 nm logic technology featuring 2nd generation high-k + metal gate transistors. In Proceedings of the 2009 IEEE International Electron Devices Meeting (IEDM), Baltimore, MD, USA, 7–9 December 2009; pp. 1–4. [Google Scholar]

- Triyoso, D.H.; Gregory, R.; Schaeffer, J.K.; Werho, D.; Li, D.; Marcus, S.; Wilk, G.D. Atomic layer deposited TaC(y) metal gates: Impact on microstructure, electrical properties, and work function on HfO(2) high-k dielectrics. J. Appl. Phys. 2007, 102, 104509. [Google Scholar] [CrossRef]

- Cho, G.H.; Rhee, S.W. Plasma-Enhanced Atomic Layer Deposition of TaCxNy Films with tert-Butylimido Tris-diethylamido Tantalum and Methane/Hydrogen Gas. Electrochem. Solid State Lett. 2010, 13, H426–H427. [Google Scholar] [CrossRef]

- Kim, C.K.; Ahn, H.J.; Moon, J.M.; Lee, S.; Moon, D.I.; Park, J.S.; Cho, B.J.; Choi, Y.K.; Lee, S.H. Temperature control for the gate workfunction engineering of TiC film by atomic layer deposition. Solid-State Electron. 2015, 114, 90–93. [Google Scholar] [CrossRef]

- Zonensain, O.; Fadida, S.; Fisher, I.; Gao, J.W.; Chattopadhyay, K.; Harm, G.; Mountsier, T.; Danek, M.; Eizenberg, M. Work function tuning of plasma-enhanced atomic layer deposited WCxNy electrodes for metal/oxide/semiconductor devices. Appl. Phys. Lett. 2015, 106, 082107. [Google Scholar] [CrossRef]

- Ahn, H.J.; Moon, J.; Koh, S.; Seo, Y.; Kim, C.; Rho, I.C.; Kim, C.H.; Hwang, W.S.; Cho, B.J. Very Low-Work-Function ALD-Erbium Carbide (ErC2) Metal Electrode on High-K Dielectrics. IEEE Trans. Electron Devices 2016, 63, 2858–2863. [Google Scholar] [CrossRef]

- Xiang, J.J.; Zhang, Y.B.; Li, T.T.; Wang, X.L.; Gao, J.F.; Yin, H.X.; Li, J.F.; Wang, W.W.; Ding, Y.Q.; Xu, C.Y.; et al. Investigation of thermal atomic layer deposited TiAlX (X = N or C) film as metal gate. Solid-State Electron. 2016, 122, 64–69. [Google Scholar] [CrossRef]

- Xiang, J.J.; Li, T.T.; Zhang, Y.B.; Wang, X.L.; Gao, J.F.; Cui, H.S.; Yin, H.X.; Li, J.F.; Wang, W.W.; Ding, Y.Q.; et al. Investigation of TiAlC by Atomic Layer Deposition as N Type Work Function Metal for FinFET. ECS J. Solid State Sci. Technol. 2015, 4, P441–P444. [Google Scholar] [CrossRef]

- Xiang, J.J.; Ding, Y.Q.; Du, L.Y.; Xu, C.Y.; Li, T.T.; Wang, X.L.; Li, J.F.; Zhao, C. Investigation of N Type Metal TiAlC by Thermal Atomic Layer Deposition Using TiCl4 and TEA as Precursors. ECS J. Solid State Sci. Technol. 2016, 5, P299–P303. [Google Scholar] [CrossRef]

- Xiang, J.J.; Li, T.T.; Wang, X.L.; Du, L.Y.; Ding, Y.Q.; Wang, W.W.; Li, J.F.; Zhao, C. Thermal Atomic Layer Deposition of TaAlC with TaCl5 and TMA as Precursors. ECS J. Solid State Sci. Technol. 2016, 5, P633–P636. [Google Scholar] [CrossRef]

- Xiang, J.J.; Wang, X.L.; Li, T.T.; Gao, J.F.; Han, K.; Yu, J.H.; Wang, W.W.; Li, J.F.; Zhao, C. Investigation of Thermal Atomic Layer Deposited TaAlC with Low Effective Work-Function on HfO2 Dielectric Using TaCl5 and TEA as Precursors. ECS J. Solid State Sci. Technol. 2017, 6, P38–P41. [Google Scholar] [CrossRef]

- Khan, A.I.; Chatterjee, K.; Wang, B.; Drapcho, S.; You, L.; Serrao, C.; Bakaul, S.R.; Ramesh, R.; Salahuddin, S. Negative capacitance in a ferroelectric capacitor. Nat. Mater. 2015, 14, 182–186. [Google Scholar] [CrossRef] [PubMed]

- Wang, G.L.; Xu, Q.; Yang, T.; Xiang, J.J.; Xu, J.; Gao, J.F.; Li, C.L.; Li, J.F.; Yan, J.; Chen, D.P.; et al. Application of Atomic Layer Deposition Tungsten (ALD W) as Gate Filling Metal for 22 nm and Beyond Nodes CMOS Technology. ECS J. Solid State Sci. Technol. 2014, 3, P82–P85. [Google Scholar] [CrossRef]

- Lemaire, P.C.; King, M.; Parsons, G.N. Understanding inherent substrate selectivity during atomic layer deposition: Effect of surface preparation, hydroxyl density, and metal oxide composition on nucleation mechanisms during tungsten ALD. J. Chem. Phys. 2017, 146, 052811. [Google Scholar] [CrossRef] [PubMed]

- Kalanyan, B.; Lemaire, P.C.; Atanasov, S.E.; Ritz, M.J.; Parsons, G.N. Using Hydrogen to Expand the Inherent Substrate Selectivity Window During Tungsten Atomic Layer Deposition. Chem. Mater. 2016, 28, 117–126. [Google Scholar] [CrossRef]

- Pai, C.F.; Liu, L.Q.; Li, Y.; Tseng, H.W.; Ralph, D.C.; Buhrman, R.A. Spin transfer torque devices utilizing the giant spin Hall effect of tungsten. Appl. Phys. Lett. 2012, 101, 122404. [Google Scholar] [CrossRef]

- Neumann, L.; Meier, D.; Schmalhorst, J.; Rott, K.; Reiss, G.; Meinert, M. Temperature dependence of the spin Hall angle and switching current in the nc-W(O)/CoFeB/MgO system with perpendicular magnetic anisotropy. Appl. Phys. Lett. 2016, 109, 142405. [Google Scholar] [CrossRef]

- Wang, G.L.; Luo, J.; Liu, J.B.; Yang, T.; Xu, Y.F.; Li, J.F.; Yin, H.X.; Yan, J.; Zhu, H.L.; Zhao, C.; et al. pMOSFETs Featuring ALD W Filling Metal Using SiH4 and B2H6 Precursors in 22 nm Node CMOS Technology. Nanoscale Res. Lett. 2017, 12, 306. [Google Scholar] [CrossRef]

- Fabreguette, F.H.; Sechrist, Z.A.; Elam, J.W.; George, S.M. Quartz crystal microbalance study of tungsten atomic layer deposition using WF6 and Si2H6. Thin Solid Films 2005, 488, 103–110. [Google Scholar] [CrossRef]

- Elam, J.W.; Nelson, C.E.; Grubbs, R.K.; Nelson, C.E. Nucleation and Growth During Tungsten Atomic Layer Deposition on Oxide Surfaces. MRS Online Proc. Libr. Arch. 2001, 386, 41–52. [Google Scholar]

- Luoh, T.; Su, C.T.; Yang, T.H.; Chen, K.C.; Lu, C.Y. Advanced tungsten plug process for beyond nanometer technology. Microelectron. Eng. 2008, 85, 1739–1747. [Google Scholar] [CrossRef]

- Kim, C.H.; Rho, I.C.; Kim, S.H.; Sohn, Y.S.; Kang, H.S.; Kim, H.J. Improvement of Adhesion Performances of CVD-W Films Deposited on B2H6-Based ALD-W Nucleation Layer. Electrochem. Solid State Lett. 2009, 12, H80–H83. [Google Scholar] [CrossRef]

- Kim, C.; Rho, I.; Eun, B.; Kim, H.; Jin, S.; Kang, H. Electrical performances of low resistive W buried gate using B2H6-reduced W nucleation layer technology for 30nm-based DRAM devices. In Proceedings of the 2011 IEEE International Interconnect Technology Conference, Dresden, Germany, 8–12 May 2011; pp. 1–3. [Google Scholar]

- Xu, Q.; Luo, J.; Wang, G.L.; Yang, T.; Li, J.F.; Ye, T.C.; Chen, D.P.; Zhao, C. Application of ALD W films as gate filling metal in 22 nm HKMG-last integration: Evaluation and improvement of the adhesion in CMP process. Microelectron. Eng. 2015, 137, 43–46. [Google Scholar] [CrossRef]

- Yang, M.D.; Aarnink, A.A.I.; Schmitz, J.; Kovalgin, A.Y. Low-resistivity alpha-phase tungsten films grown by hot-wire assisted atomic layer deposition in high-aspect-ratio structures. Thin Solid Films 2018, 646, 199–208. [Google Scholar] [CrossRef]

- Kim, S.H.; Kim, J.T.; Kwak, N.; Kim, J.; Yoon, T.S.; Sohn, H. Effects of phase of underlying W film on chemical vapor deposited-W film growth and applications to contact-plug and bit line processes for memory devices. J. Vac. Sci. Technol. B 2007, 25, 1574–1580. [Google Scholar] [CrossRef]

- Yang, H.S.; Malik, R.; Narasimha, S.; Li, Y.; Divakaruni, R.; Agnello, P.; Allen, S.; Antreasyan, A.; Arnold, J.C.; Bandy, K.; et al. Dual stress liner for high performance sub-45nm gate length SOI CMOS manufacturing. In Proceedings of the IEDM Technical Digest, IEEE International Electron Devices Meeting, 2004, San Francisco, CA, USA, 13–15 December 2004; pp. 1075–1077. [Google Scholar]

- Nguyen, P.; Barraud, S.; Tabone, C.; Gaben, L.; Cassé, M.; Glowacki, F.; Hartmann, J.; Samson, M.; Maffini-Alvaro, V.; Vizioz, C.; et al. Dual-channel CMOS co-integration with Si NFET and strained-SiGe PFET in nanowire device architecture featuring sub-15nm gate length. In Proceedings of the 2014 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 15–17 December 2014; pp. 16.12.11–16.12.14. [Google Scholar]

- Jing, W. Strained Silicon—A Technology to Extend Moore’s Law. Microelectronics 2008, 38, 50–56. [Google Scholar]

- Orain, S.; Fiori, V.; Villanueva, D.; Dray, A.; Ortolland, C. Method for Managing the Stress Due to the Strained Nitride Capping Layer in MOS Transistors. IEEE Trans. Electron Devices 2007, 54, 814–821. [Google Scholar] [CrossRef]

- Varadarajan, B.; Sims, J.; Singhal, A.; Christensen, M.; Jiang, G.; Ilcisir, K.; Shrinivasan, K.; Ayoub, M.; Dharmadhikari, V. The development of high stress silicon nitride film used in strain silicon. Integr. Circuit Appl. 2006, 2, 36–39. [Google Scholar]

- Wang, J. The application and forecast of high stress silicon nitride films. Integr. Circuit Appl. 2008, 4, 63–64. [Google Scholar]

- Kim, D.; Krishnamohan, T.; Smith, L.; Wong, H.S.P.; Saraswat, K.C. Band to band tunneling study in high mobility materials: III-V, Si, Ge and strained SiGe. In Proceedings of the 2007 65th Annual Device Research Conference, Notre Dame, IN, USA, 18–20 June 2007; pp. 57–58. [Google Scholar] [CrossRef]

- Oktyabrsky, S.; Ye, P.D. Fundamentals of III-V Semiconductor MOSFETs; Springer: New York, NY, USA, 2010; pp. 1–445. [Google Scholar] [CrossRef]

- Kobayashi, M.; Thareja, G.; Ishibashi, M.; Sun, Y.; Griffin, P.; McVittie, J.; Pianetta, P.; Saraswat, K.; Nishi, Y. Radical oxidation of germanium for interface gate dielectric GeO2 formation in metal-insulator-semiconductor gate stack. J. Appl. Phys. 2009, 106, 104117. [Google Scholar] [CrossRef]

- Si-Silicon Electrical Properties. Available online: http://www.ioffe.ru/SVA/NSM/Semicond/Si/electric.html (accessed on 30 December 2018).

- Kuhn, K.J. Considerations for Ultimate CMOS Scaling. IEEE Trans. Electron Devices 2012, 59, 1813–1828. [Google Scholar] [CrossRef]

- Hussain, M.M.; Shamiryan, D.; Paraschiv, V.; Sano, K.; Reinhardt, K. Cleaning Challenges of High-κ/Metal Gate Structures. In Handbook of Cleaning in Semiconductor Manufacturing; Scrivener Publishing LLC.: Salem, MA, USA, 2011; pp. 249–251. [Google Scholar] [CrossRef]

- Huff, H.R.; Richter, C.A.; Green, M.L.; Lucovsky, G.; Hattori, T. Ultrathin SiO2 and High-K Materials for ULSI Gate Dielectrics; Materials Research Society: Warrendale, PA, USA, 1999; Volume 567. [Google Scholar]

- Mertens, H.; Ritzenthaler, R.; Arimura, H.; Franco, J.; Sebaai, F.; Hikavyy, A.; Pawlak, B.J.; Machkaoutsan, V.; Devriendt, K.; Tsvetanova, D.; et al. Si-cap-free SiGe p-channel FinFETs and gate-all-around transistors in a replacement metal gate process: Interface trap density reduction and performance improvement by high-pressure deuterium anneal. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T142–T143. [Google Scholar]

- Destefanis, V.; Hartmann, J.M.; Borel, S.; Bensahel, D. High pressure in situ HCl etching of Si(1-x)Ge(x) versus Si for advanced devices. Semicond. Sci. Technol. 2008, 23, 105019. [Google Scholar] [CrossRef]

- Wieser, U.; Iamundo, D.; Kunze, U.; Hackbarth, T.; Konig, U. Nanoscale patterning of Si/SiGe heterostructures by electron-beam lithography and selective wet-chemical etching. Semicond. Sci. Technol. 2000, 15, 862–867. [Google Scholar] [CrossRef]

- Chang, G.K.; Carns, T.K.; Rhee, S.S.; Wang, K.L. Selective etching of SiGe on SiGe/Si heterostructures. J. Electrochem. Soc. 1991, 138, 202–204. [Google Scholar] [CrossRef]

- Carns, T.K.; Tanner, M.O.; Wang, K.L. Chemical Etching of Si1-Xgex In Hf-H2O2-CH3COOH. J. Electrochem. Soc. 1995, 142, 1260–1266. [Google Scholar]

- Seidel, H.; Csepregi, L.; Heuberger, A.; Baumgartel, H. Anisotropic etching of crystalline silicon in alkaline solutions I. Orientation dependence and behavior of passivation layers. J. Electrochem. Soc. 1990, 137, 3612–3626. [Google Scholar] [CrossRef]

- Wang, F.; Shi, Y.; Liu, J.L.; Lu, Y.; Gu, S.L.; Zheng, Y.D. Highly selective chemical etching of Si vs. Si1-xGex using NH4OH solution. J. Electrochem. Soc. 1997, 144, L37–L39. [Google Scholar] [CrossRef]

- Wostyn, K.; Sebai, F.; Rip, J.; Mertens, H.; Witters, L.; Loo, R.; Hikavyy, A.; Milenin, A.; Horiguchi, N.; Collaert, N.; et al. Selective Etch of Si and SiGe for Gate All-Around Device Architecture. ECS Trans. 2015, 69, 147–152. [Google Scholar] [CrossRef]

- Ahles, C.F.; Choi, J.Y.; Wolf, S.; Kummel, A.C. Selective Etching of Silicon in Preference to Germanium and Si0.5Ge0.5. ACS Appl. Mater. Interfaces 2017, 9, 20947–20954. [Google Scholar] [CrossRef]

- Kil, Y.H.; Yang, J.-H.; Kang, S.; Jeong, T.S.; Kim, T.S.; Shim, K.-H. Selective Chemical Wet Etching of Si0.8Ge0.2/Si Multilayer. J. Semicond. Technol. Sci. 2013, 13, 668–675. [Google Scholar] [CrossRef]

- Liu, W.D.; Lee, Y.C.; Sekiguchi, R.; Yoshida, Y.; Komori, K.; Wostyn, K.; Sebaai, F.; Holsteyns, F. Selective Wet Etching in Fabricating SiGe and Ge Nanowires for Gate-all-Around MOSFETs. Solid State Phenom. 2018, 282, 101–106. [Google Scholar] [CrossRef]

- Bogumilowicz, Y.; Hartmann, J.M.; Truche, R.; Campidelli, Y.; Rolland, G.; Billon, T. Chemical vapour etching of Si, SiGe and Ge with HCl; applications to the formation of thin relaxed SiGe buffers and to the revelation of threading dislocations. Semicond. Sci. Technol. 2004, 20, 127. [Google Scholar] [CrossRef]

- Witters, L.; Arimura, H.; Sebaai, F.; Hikavyy, A.; Milenin, A.P.; Loo, R.; Keersgieter, A.D.; Eneman, G.; Schram, T.; Wostyn, K.; et al. Strained Germanium Gate-All-Around pMOS Device Demonstration Using Selective Wire Release Etch Prior to Replacement Metal Gate Deposition. IEEE Trans. Electron Devices 2017, 64, 4587–4593. [Google Scholar] [CrossRef]

- Sebaai, F.; Witters, L.; Holsteyns, F.; Wostyn, K.; Rip, J.; Yukifumi, Y.; Lieten, R.R.; Bilodeau, S.; Cooper, E. Wet Selective SiGe Etch to Enable Ge Nanowire Formation. Solid State Phenom. 2016, 255, 3–7. [Google Scholar] [CrossRef]

- Koyama, K.; Hiroi, M.; Tatsumi, T.; Hirayama, H. Etching characteristics of Si1−xGex alloy in ammoniac wet cleaning. Appl. Phys. Lett. 1990, 57, 2202–2204. [Google Scholar] [CrossRef]

- Bloem, J.; van Vessem, J.C. Etching Ge with Mixtures of HF-H2O2-H2O. J. Electrochem. Soc. 1962, 109, 33–36. [Google Scholar] [CrossRef]

- Markov, I.L. Limits on fundamental limits to computation. Nature 2014, 512, 147–154. [Google Scholar] [CrossRef]

- Edelstein, D.; Heidenreich, J.; Goldblatt, R.; Cote, W.; Uzoh, C.; Lustig, N.; Roper, P.; McDevitt, T.; Motsiff, W.; Simon, A.; et al. Full Copper Wiring in a Sub-0.25 μm CMOS ULSI Technology. In Proceedings of the International Electron Devices Meeting, IEDM Technical Digest, Washington, DC, USA, 10 December 1997; pp. 773–776. [Google Scholar]

- Hung, R.; Park, J.H.; Ha, T.H.; Lee, M.; Hou, W.; Lei, J.; Bakke, J.R.; Sharma, S.; Sharma, K.R.; Kim, N.S.; et al. Extreme Contact Scaling with Advanced Metallization of Cobalt. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 30–32. [Google Scholar]

- Bekiaris, N.; Wu, Z.; Ren, H.; Naik, M.; Park, J.H.; Lee, M.; Ha, T.H.; Hou, W.; Bakke, J.R.; Gage, M.; et al. Cobalt fill for advanced interconnects. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017; pp. 1–3. [Google Scholar]

- Zhang, W.; Brongersma, S.H.; Li, Z.; Li, D.; Richard, O.; Maex, K. Analysis of the size effect in electroplated fine copper wires and a realistic assessment to model copper resistivity. J. Appl. Phys. 2007, 101, 063703. [Google Scholar] [CrossRef]

- Wen, L.G.; Roussel, P.; Pedreira, O.V.; Briggs, B.; Groven, B.; Dutta, S.; Popovici, M.I.; Heylen, N.; Ciofi, I.; Vanstreels, K.; et al. Atomic Layer Deposition of Ruthenium with TiN Interface for Sub-10 nm Advanced Interconnects beyond Copper. ACS Appl. Mater. Interfaces 2016, 8, 26119–26125. [Google Scholar] [CrossRef]

- Veen, M.H.v.d.; Heyler, N.; Pedreira, O.V.; Ciofi, I.; Decoster, S.; Gonzalez, V.V.; Jourdan, N.; Struyf, H.; Croes, K.; Wilson, C.J.; et al. Damascene Benchmark of Ru, Co and Cu in Scaled Dimensions. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 172–174. [Google Scholar]

- Dutta, S.; Kundu, S.; Gupta, A.; Jamieson, G.; Granados, J.F.G.; Bömmels, J.; Wilson, C.J.; Tőkei, Z.; Adelmann, C. Highly Scaled Ruthenium Interconnects. IEEE Electron Device Lett. 2017, 38, 949–951. [Google Scholar] [CrossRef]

- Liang Gong, W.; Adelmann, C.; Pedreira, O.V.; Dutta, S.; Popovici, M.; Briggs, B.; Heylen, N.; Vanstreels, K.; Wilson, C.J.; Elshocht, S.V.; et al. Ruthenium metallization for advanced interconnects. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 23–26 May 2016; pp. 34–36. [Google Scholar]

- Wu, Z.; Li, R.; Xie, X.; Suen, W.; Tseng, J.; Bekiaris, N.; Vinnakota, R.; Kashefizadeh, K.; Naik, M. PVD- Treated ALD TaN for Cu Interconnect Extension to 5nm Node and Beyond. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 149–151. [Google Scholar]

- Chawla, J.S.; Sung, S.H.; Bojarski, S.A.; Carver, C.T.; Chandhok, M.; Chebiam, R.V.; Clarke, J.S.; Harmes, M.; Jezewski, C.J.; Kobrinski, M.J.; et al. Resistance and electromigration performance of 6 nm wires. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 23–26 May 2016; pp. 63–65. [Google Scholar]

- Veen, M.H.v.d.; Vandersmissen, K.; Dictus, D.; Demuynck, S.; Liu, R.; Bin, X.; Nalla, P.; Lesniewska, A.; Hall, L.; Croes, K.; et al. Cobalt bottom-up contact and via prefill enabling advanced logic and DRAM technologies. In Proceedings of the 2015 IEEE International Interconnect Technology Conference and 2015 IEEE Materials for Advanced Metallization Conference (IITC/MAM), Grenoble, France, 18–21 May 2015; pp. 25–28. [Google Scholar]

- Zheng, J.; Chen, P.; Baum, T.H.; Lieten, R.R.; Hunks, W.; Lippy, S.; Frye, A.; Li, W.; Neill, J.O.; Xu, J.; et al. Selective co growth on Cu for void-free via fill. In Proceedings of the 2015 IEEE International Interconnect Technology Conference and 2015 IEEE Materials for Advanced Metallization Conference (IITC/MAM), Grenoble, France, 18–21 May 2015; pp. 265–268. [Google Scholar]

- Hu, C.; Kelly, J.; Chen, J.H.; Huang, H.; Ostrovski, Y.; Patlolla, R.; Peethala, B.; Adusumilli, P.; Spooner, T.; Gignac, L.M.; et al. Electromigration and resistivity in on-chip Cu, Co and Ru damascene nanowires. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017; pp. 1–3. [Google Scholar]

- Posser, G.; Mishra, V.; Reis, R.; Sapatnekar, S.S. Analyzing the Electromigration Effects on Different Metal Layers and Different Wire Lengths. In Proceedings of the 21st IEEE International Conference on Electronics Circuits and Systems (ICECS), Marseille, France, 7–10 December 2014. [Google Scholar] [CrossRef]

- Jiang, Y.; Nalla, P.; Matsushita, Y.; Harm, G.; Wang, J.; Kolics, A.; Zhao, L.; Mountsier, T.; Besser, P.; Wu, H.J. Development of electroless Co via-prefill to enable advanced BEOL metallization and via resistance reduction. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 23–26 May 2016; pp. 111–113. [Google Scholar]

- Ciofi, I.; Roussel, P.J.; Saad, Y.; Moroz, V.; Hu, C.; Baert, R.; Croes, K.; Contino, A.; Vandersmissen, K.; Gao, W.; et al. Modeling of Via Resistance for Advanced Technology Nodes. IEEE Trans. Electron Devices 2017, 64, 2306–2313. [Google Scholar] [CrossRef]

- Wan, D.; Paolillo, S.; Rassoul, N.; Kotowska, B.K.; Blanco, V.; Adelmann, C.; Lazzarino, F.; Ercken, M.; Murdoch, G.; Bömmels, J.; et al. Subtractive Etch of Ruthenium for Sub-5nm Interconnect. In Proceedings of the 2018 IEEE International Interconnect Technology Conference (IITC), Santa Clara, CA, USA, 4–7 June 2018; pp. 10–12. [Google Scholar]

- Griggio, F.; Palmer, J.; Pan, F.; Toledo, N.; Schmitz, A.; Tsameret, I.; Kasim, R.; Leatherman, G.; Hicks, J.; Madhavan, A.; et al. Reliability of dual-damascene local interconnects featuring cobalt on 10 nm logic technology. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 6E.3-1–6E.3-5. [Google Scholar]

- Pandey, R.; Agrawal, N.; Arghavani, R.; Datta, S. Analysis of local interconnect resistance at scaled process nodes. In Proceedings of the 2015 73rd Annual Device Research Conference (DRC), Columbus, OH, USA, 21–24 June 2015; p. 184. [Google Scholar]

- Kamineni, V.; Raymond, M.; Siddiqui, S.; Mont, F.; Tsai, S.; Niu, C.; Labonte, A.; Labelle, C.; Fan, S.; Peethala, B.; et al. Tungsten and cobalt metallization: A material study for MOL local interconnects. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 23–26 May 2016; pp. 105–107. [Google Scholar]

- Xunyuan, Z.; Huai, H.; Patlolla, R.; Wei, W.; Mont, F.W.; Juntao, L.; Chao-Kun, H.; Liniger, E.G.; McLaughlin, P.S.; Labelle, C.; et al. Ruthenium interconnect resistivity and reliability at 48 nm pitch. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 23–26 May 2016; pp. 31–33. [Google Scholar]

- Fan, S.S.; Chen, J.H.; Kamineni, V.K.; Zhang, X.; Raymond, M.; Labelle, C. Middle of line RC performance study at the 7 nm node. In Proceedings of the 2017 IEEE International Interconnect Technology Conference (IITC), Hsinchu, Taiwan, 16–18 May 2017; pp. 1–3. [Google Scholar]

- Hosseini, M.; Ando, D.; Sutou, Y.; Koike, J. Co and CoTix for contact plug and barrier layer in integrated circuits. Microelectron. Eng. 2018, 189, 78–84. [Google Scholar] [CrossRef]

- Hosseini, M.; Koike, J.; Sutou, Y.; Zhao, L.; Lai, S.; Arghavani, R. Amorphous Co-Ti alloy as a single layer barrier for Co local interconnect structure. In Proceedings of the 2016 IEEE International Interconnect Technology Conference/Advanced Metallization Conference (IITC/AMC), San Jose, CA, USA, 23–26 May 2016; pp. 162–164. [Google Scholar]

- Hellings, G.; Subirats, A.; Franco, J.; Schram, T.; Ragnarsson, L.; Witters, L.; Roussel, P.; Linten, D.; Horiguchi, N.; Boschke, R. Demonstration of sufficient BTI reliability for a 14-nm finFET 1.8 V I/O technology featuring a thick ALD SiO2 IL and Ge p-channel. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. FA-5.1–FA-5.4. [Google Scholar]

- Ren, P.; Gao, R.; Ji, Z.; Arimura, H.; Zhang, J.F.; Wang, R.; Duan, M.; Zhang, W.; Franco, J.; Sioncke, S.; et al. Understanding charge traps for optimizing Si-passivated Ge nMOSFETs. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Benbakhti, B.; Zhang, J.F.; Ji, Z.; Zhang, W.; Mitard, J.; Kaczer, B.; Groeseneken, G.; Hall, S.; Robertson, J.; Chalker, P. Characterization of Electron Traps in Si-Capped Ge MOSFETs With HfO2/SiO2 Gate Stack. IEEE Electron Device Lett. 2012, 33, 1681–1683. [Google Scholar] [CrossRef]

- Bao, R.; Southwick, R.G.; Zhou, H.; Lee, C.H.; Linder, B.P.; Ando, T.; Guo, D.; Jagannathan, H.; Narayanan, V. Differentiated Performance and Reliability Enabled by Multi-Work Function Solution in RMG Silicon and SiGe MOSFETs. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 115–116. [Google Scholar]

- Franco, J.; Kaczer, B.; Chasin, A.; Bury, E.; Linten, D. Hot electron and hot hole induced degradation of SiGe p-FinFETs studied by degradation maps in the entire bias space. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. 5A.1-1–5A.1-7. [Google Scholar]

- Waltl, M.; Rzepa, G.; Grill, A.; Goes, W.; Franco, J.; Kaczer, B.; Witters, L.; Mitard, J.; Horiguchi, N.; Grasser, T. Superior NBTI in High-k SiGe Transistors—Part II: Theory. IEEE Trans. Electron Devices 2017, 64, 2099–2105. [Google Scholar] [CrossRef]

- Waltl, M.; Rzepa, G.; Grill, A.; Goes, W.; Franco, J.; Kaczer, B.; Witters, L.; Mitard, J.; Horiguchi, N.; Grasser, T. Superior NBTI in High-k SiGe Transistors—Part I: Experimental. IEEE Trans. Electron Devices 2017, 64, 2092–2098. [Google Scholar] [CrossRef]

- Kumar, P.; Leroux, C.; Mohamad, B.; Toffoli, A.; Romano, G.; Garros, X.; Reimbold, G.; Kumar, P.; Domengie, F.; Segovia, C.S.; et al. Effect of La and Al addition used for threshold voltage shift on the BTI reliability of HfON-based FDSOI MOSFETs. In Proceedings of the 2017 IEEE International Reliability Physics Symposium (IRPS), Monterey, CA, USA, 2–6 April 2017; pp. 2B-2.1–2B-2.7. [Google Scholar]

- Zhang, J.; Ando, T.; Yeung, C.W.; Wang, M.; Kwon, O.; Galatage, R.; Chao, R.; Loubet, N.; Moon, B.K.; Bao, R.; et al. High-k metal gate fundamental learning and multi-Vt options for stacked nanosheet gate-all-around transistor. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 22.21.21–22.21.24. [Google Scholar]

- Vandooren, A.; Franco, J.; Wu, Z.; Parvais, B.; Li, W.; Witters, L.; Walke, A.; Peng, L.; Deshpande, V.; Rassoul, N.; et al. First Demonstration of 3D stacked Finfets at a 45 nm fin pitch and 110nm gate pitch technology on 300 mm wafers. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 7.1.1–7.1.4. [Google Scholar]

- Lima, L.P.B.; Dekkers, H.F.W.; Lisoni, J.G.; Diniz, J.A.; Van Elshocht, S.; De Gendt, S. Metal gate work function tuning by Al incorporation in TiN. J. Appl. Phys. 2014, 115, 074504. [Google Scholar] [CrossRef]

- Lim, A.E.; Lee, R.T.P.; Samudra, G.S.; Kwong, D.; Yeo, Y. Modification of molybdenum gate electrode work function via (La-, Al-induced) dipole effect at High-k/SiO2 interface. IEEE Electron Device Lett. 2008, 29, 848–851. [Google Scholar] [CrossRef]

- Bao, R.; Hung, S.; Wang, M.; Chung, K.; Barman, S.; Krishnan, S.A.; Yang, Y.; Tang, W.; Li, L.; Lin, Y.; et al. Novel Materials and Processes in Replacement Metal Gate for Advanced CMOS Technology. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 11.14.11–11.14.14. [Google Scholar]

- Ando, T.; Kannan, B.; Kwon, U.; Lai, W.L.; Linder, B.P.; Cartier, E.A.; Haight, R.; Copel, M.; Bruley, J.; Krishnan, S.A.; et al. Simple Gate Metal Anneal (SIGMA) stack for FinFET Replacement Metal Gate toward 14nm and beyond. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Ragnarsson, L.; Chew, S.A.; Dekkers, H.; Luque, M.T.; Parvais, B.; Keersgieter, A.D.; Devriendt, K.; Ammel, A.V.; Schram, T.; Yoshida, N.; et al. Highly scalable bulk FinFET Devices with Multi-VT options by conductive metal gate stack tuning for the 10-nm node and beyond. In Proceedings of the 2014 Symposium on VLSI Technology (VLSI-Technology): Digest of Technical Papers, Honolulu, HI, USA, 9–12 June 2014; pp. 1–2. [Google Scholar]

- Bury, E.; Kaczer, B.; Linten, D.; Witters, L.; Mertens, H.; Waldron, N.; Zhou, X.; Collaert, N.; Horiguchi, N.; Spessot, A.; et al. Self-heating in FinFET and GAA-NW using Si, Ge and III/V channels. In Proceedings of the 2016 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 3–7 December 2016; pp. 15.16.11–15.16.14. [Google Scholar]

- Chalia, G.; Hegde, R.S. Study of Self-Heating Effects in Silicon Nano-Sheet Transistors. In Proceedings of the 2018 IEEE International Conference on Electron Devices and Solid State Circuits (EDSSC), Shenzhen, China, 6–8 June 2018; pp. 1–2. [Google Scholar]

- Cai, L.; Chen, W.; Du, G.; Zhang, X.; Liu, X. Layout Design Correlated with Self-Heating Effect in Stacked Nanosheet Transistors. IEEE Trans. Electron Devices 2018, 65, 2647–2653. [Google Scholar] [CrossRef]

- Chen, W.; Cai, L.; Wang, K.; Zhang, X.; Liu, X.; Du, G. Self-heating induced Variability and Reliability in Nanosheet-FETs Based SRAM. In Proceedings of the 2018 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 16–19 July 2018; pp. 1–4. [Google Scholar]

- Wang, R.; Guo, S.; Zhang, Z.; Zou, J.; Mao, D.; Huang, R. Complex Random Telegraph Noise (RTN): What Do We Understand? In Proceedings of the 2018 IEEE International Symposium on the Physical and Failure Analysis of Integrated Circuits (IPFA), Singapore, 16–19 July 2018; pp. 1–7. [Google Scholar]

- Guo, S.; Lin, Z.; Wang, R.; Zhang, Z.; Zhang, Z.; Wang, Y.; Huang, R. Investigation on the amplitude coupling effect of random telegraph noise (RTN) in nanoscale FinFETs. In Proceedings of the 2018 IEEE International Reliability Physics Symposium (IRPS), Burlingame, CA, USA, 11–15 March 2018; pp. P-TX.6-1–P-TX.6-4. [Google Scholar]

- Brown, J.; Gao, R.; Ji, Z.; Chen, J.; Wu, J.; Zhang, J.; Zhou, B.; Shi, Q.; Crowford, J.; Zhang, W. A low-power and high-speed True Random Number Generator using generated RTN. In Proceedings of the 2018 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 18–22 June 2018; pp. 95–96. [Google Scholar]

- Wangran, W.; Wu, H.; Si, M.; Conrad, N.; Yi, Z.; Ye, P.D. RTN and low frequency noise on ultra-scaled near-ballistic Ge nanowire nMOSFETs. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Takagi, S.; Ahn, D.H.; Gotow, T.; Noguchi, M.; Nishi, K.; Kim, S.; Yokoyama, M.; Chang, C.; Yoon, S.; Yokoyama, C.; et al. III–V-based low power CMOS devices on Si platform. In Proceedings of the 2017 IEEE International Conference on IC Design and Technology (ICICDT), Austin, TX, USA, 23–25 May 2017; pp. 1–4. [Google Scholar]

- Mols, Y.; Kunert, B.; Gaudin, G.; Langer, R.; Caymax, M. Study towards integration of In0.53Ga0.47As on 300 mm Si for CMOS sub-7 nm node: Development of thin graded InxGa1-xAs buffers on GaAs. J. Cryst. Growth 2016, 452, 244–247. [Google Scholar] [CrossRef]

- Zhou, X.; Waldron, N.; Boccardi, G.; Sebaai, F.; Merckling, C.; Eneman, G.; Sioncke, S.; Nyns, L.; Opdebeeck, A.; Maes, J.W.; et al. Scalability of InGaAs gate-all-around FET integrated on 300 mm Si platform: Demonstration of channel width down to 7 nm and L-g down to 36 nm. In Proceedings of the 2016 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 14–16 June 2016; pp. 1–2. [Google Scholar]

- Liu, Z.Y.; Merckling, C.; Rooyackers, R.; Franquet, A.; Richard, O.; Bender, H.; Vila, M.; Rubio-Zuazo, J.; Castro, G.R.; Collaert, N.; et al. The effect of Ga pre-deposition on Si (111) surface for InAs nanowire selective area hetero-epitaxy. J. Appl. Phys. 2018, 123, 145301. [Google Scholar] [CrossRef]

- Sollier, S.; Widiez, J.; Gaudin, G.; Mazen, F.; Baron, T.; Martin, M.; Roure, M.C.; Besson, P.; Morales, C.; Beche, E.; et al. 300 mm InGaAsOI substrate fabrication using the Smart CutTM technology. In Proceedings of the 2015 IEEE SOI-3D-Subthreshold Microelectronics Technology Unified Conference (S3S), Rohnert Park, CA, USA, 5–8 October 2015; pp. 1–2. [Google Scholar]

- Mauthe, S.; Schmid, H.; Mayer, B.; Wirths, S.; Convertino, C.; Baumgartner, Y.; Czornomaz, L.; Sousa, M.; Staudinger, P.; Riel, H.; et al. Monolithic Integration of III–V on silicon for photonic and electronic applications. In Proceedings of the 2018 76th Device Research Conference (DRC), Santa Barbara, CA, USA, 24–27 June 2018; pp. 1–2. [Google Scholar]

- Knoedler, M.; Bologna, N.; Schmid, H.; Borg, M.; Moselund, K.E.; Wirths, S.; Rossell, M.D.; Riel, H. Observation of Twin-free GaAs Nanowire Growth Using Template Assisted Selective Epitaxy. Cryst. Growth Des. 2017, 17, 6297–6302. [Google Scholar] [CrossRef]

- Czornomaz, L.; Uccelli, E.; Sousa, M.; Deshpande, V.; Djara, V.; Caimi, D.; Rossell, M.D.; Erni, R.; Fompeyrine, J. Confined Epitaxial Lateral Overgrowth (CELO): A novel concept for scalable integration of CMOS-compatible InGaAs-on-insulator MOSFETs on large-area Si substrates. In Proceedings of the 2015 Symposium on VLSI Technology (VLSI Technology), Kyoto, Japan, 16–18 June 2015; pp. T172–T173. [Google Scholar]

- Djara, V.; Deshpande, V.; Sousa, M.; Caimi, D.; Czornomaz, L.; Fompeyrine, J. CMOS-Compatible Replacement Metal Gate InGaAs-OI FinFET with I-ON = 156 mu A/mu m at V-DD = 0.5 V and I-OFF = 100 nA/mu m. IEEE Electron Device Lett. 2016, 37, 169–172. [Google Scholar] [CrossRef]

- Hahn, H.; Deshpande, V.; Caruso, E.; Sant, S.; Connor, E.O.; Baumgartner, Y.; Sousa, M.; Caimi, D.; Olziersky, A.; Palestri, P.; et al. A scaled replacement metal gate InGaAs-on-Insulator n-FinFET on Si with record performance. In Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 2–6 December 2017; pp. 17.15.11–17.15.14. [Google Scholar]

- Deshpande, V.; Djara, V.; O’Connor, E.; Hashemi, P.; Balakrishnan, K.; Caimi, D.; Sousa, M.; Czornomaz, L.; Fompeyrine, J. DC and RF characterization of InGaAs replacement metal gate (RMG) nFETs on SiGe-OI FinFETs fabricated by 3D monolithic integration. Solid-State Electron. 2017, 128, 87–91. [Google Scholar] [CrossRef]

- Li, X.M.; Tao, L.; Chen, Z.F.; Fang, H.; Li, X.S.; Wang, X.R.; Xu, J.B.; Zhu, H.W. Graphene and related two-dimensional materials: Structure-property relationships for electronics and optoelectronics. Appl. Phys. Rev. 2017, 4, 021306. [Google Scholar] [CrossRef]

- Balandin, A.A.; Ghosh, S.; Bao, W.Z.; Calizo, I.; Teweldebrhan, D.; Miao, F.; Lau, C.N. Superior thermal conductivity of single-layer graphene. Nano Lett. 2008, 8, 902–907. [Google Scholar] [CrossRef]

- Bonaccorso, F.; Sun, Z.; Hasan, T.; Ferrari, A.C. Graphene photonics and optoelectronics. Nat. Photonics 2010, 4, 611–622. [Google Scholar] [CrossRef]

- Wu, Y.Q.; Jenkins, K.A.; Valdes-Garcia, A.; Farmer, D.B.; Zhu, Y.; Bol, A.A.; Dimitrakopoulos, C.; Zhu, W.J.; Xia, F.N.; Avouris, P.; et al. State-of-the-Art Graphene High-Frequency Electronics. Nano Lett. 2012, 12, 3062–3067. [Google Scholar] [CrossRef]

- Jiao, L.Y.; Wang, X.R.; Diankov, G.; Wang, H.L.; Dai, H.J. Facile synthesis of high-quality graphene nanoribbons. Nat. Nanotechnol. 2010, 5, 321–325. [Google Scholar] [CrossRef]

- Wang, X.R.; Ouyang, Y.J.; Li, X.L.; Wang, H.L.; Guo, J.; Dai, H.J. Room-temperature all-semiconducting sub-10-nm graphene nanoribbon field-effect transistors. Phys. Rev. Lett. 2008, 100, 206803. [Google Scholar] [CrossRef]

- Zhou, S.Y.; Gweon, G.H.; Fedorov, A.V.; First, P.N.; De Heer, W.A.; Lee, D.H.; Guinea, F.; Castro Neto, A.H.; Lanzara, A. Substrate-induced bandgap opening in epitaxial graphene. Nat. Mater. 2007, 6, 916. [Google Scholar] [CrossRef][Green Version]

- Liu, W.; Kraemer, S.; Sarkar, D.; Li, H.; Ajayan, P.M.; Banerjeet, K. Controllable and Rapid Synthesis of High-Quality and Large-Area Bernal Stacked Bilayer Graphene Using Chemical Vapor Deposition. Chem. Mat. 2014, 26, 907–915. [Google Scholar] [CrossRef]

- Moon, J.S.; Seo, H.C.; Stratan, F.; Antcliffe, M.; Schmitz, A.; Ross, R.S.; Kiselev, A.A.; Wheeler, V.D.; Nyakiti, L.O.; Gaskill, D.K.; et al. Lateral Graphene Heterostructure Field-Effect Transistor. IEEE Electron Device Lett. 2013, 34, 1190–1192. [Google Scholar] [CrossRef]

- Yuan, S.G.; Yang, Z.B.; Xie, C.; Yan, F.; Dai, J.Y.; Lau, S.P.; Chan, H.L.W.; Hao, J.H. Ferroelectric-Driven Performance Enhancement of Graphene Field-Effect Transistors Based on Vertical Tunneling Heterostructures. Adv. Mater. 2016, 28, 10048–10054. [Google Scholar] [CrossRef]

- Schwierz, F.; Pezoldt, J.; Granzner, R. Two-dimensional materials and their prospects in transistor electronics. Nanoscale 2015, 7, 8261–8283. [Google Scholar] [CrossRef]

- Lee, I.; Rathi, S.; Lim, D.; Li, L.; Park, J.; Lee, Y.; Yi, K.S.; Dhakal, K.P.; Kim, J.; Lee, C.; et al. Gate-Tunable Hole and Electron Carrier Transport in Atomically Thin Dual-Channel WSe2/MoS2 Heterostructure for Ambipolar Field-Effect Transistors. Adv. Mater. 2016, 28, 9519–9525. [Google Scholar] [CrossRef]

- Nourbakhsh, A.; Zubair, A.; Sajjad, R.N.; Tavakkoli, K.G.A.; Chen, W.; Fang, S.; Ling, X.; Kong, J.; Dresselhaus, M.S.; Kaxiras, E.; et al. MoS2 Field-Effect Transistor with Sub-10 nm Channel Length. Nano Lett. 2016, 16, 7798–7806. [Google Scholar] [CrossRef]

- Roy, T.; Tosun, M.; Kang, J.S.; Sachid, A.B.; Desai, S.B.; Hettick, M.; Hu, C.M.C.; Javey, A. Field-Effect Transistors Built from All Two-Dimensional Material Components. ACS Nano 2014, 8, 6259–6264. [Google Scholar] [CrossRef]

- Salahuddin, S.; Datta, S. Use of negative capacitance to provide voltage amplifcation for low power nanoscale devices. Nano Lett. 2008, 8, 405–410. [Google Scholar] [CrossRef]

- Zhirnov, V.V.; Cavin, R.K. Nanoelectronics: Negative capacitance to the rescue? Nat. Nanotechnol. 2008, 3, 77–78. [Google Scholar] [CrossRef]

- Verhulst, A.S.; Vandenberghe, W.G.; Maex, K.; Groeseneken, G. Boosting the on-current of a n-channel nanowire tunnel field-effect transistor by source material optimization. J. Appl. Phys. 2008, 104, 064514. [Google Scholar] [CrossRef]

- Avci, U.E.; Morris, D.H.; Young, I.A. Tunnel field-effect transistors: Prospects and challenges. IEEE J. Electron Devices Soc. 2015, 3, 88–95. [Google Scholar] [CrossRef]

- Gandhi, R.; Chen, Z.; Singh, N.; Banerjee, K.; Lee, S. Vertical Si-Nanowire n-Type Tunneling FETs with Low Subthreshold Swing (≤50 mV/decade) at Room Temperature. IEEE Electron Device Lett. 2011, 32, 437–439. [Google Scholar] [CrossRef]

- Lu, H.; Seabaugh, A. Tunnel field-effect transistors: State-of-the-art. IEEE J. Electron Devices Soc. 2014, 2, 44–49. [Google Scholar] [CrossRef]

- Kim, S.H.; Kam, H.; Hu, C.; Liu, T.J. Germanium-source tunnel field effect transistors with record high ION/IOFF. In Proceedings of the 2009 Symposium on VLSI Technology, Honolulu, HI, USA, 16–18 June 2009; pp. 178–179. [Google Scholar]

- Luisier, M.; Klimeck, G. Simulation of nanowire tunneling transistors: From the Wentzel–Kramers–Brillouin approximation to full-band phonon-assisted tunneling. J. Appl. Phys. 2010, 107, 084507. [Google Scholar] [CrossRef]

- Zhao, P.; Chauhan, J.; Guo, J. Computational study of tunneling transistor based on graphene nanoribbon. Nano Lett. 2009, 9, 684–688. [Google Scholar] [CrossRef]

- Chin, S.K.; Seah, D.; Lam, K.T.; Samudra, G.S.; Liang, G. Device physics and characteristics of graphene nanoribbon tunneling FETs. IEEE Trans. Electron Devices 2010, 57, 3144–3152. [Google Scholar] [CrossRef]

- Lam, K.T.; Cao, X.; Guo, J. Device performance of heterojunction tunneling field-effect transistors based on transition metal dichalcogenide monolayer. IEEE Electron Device Lett. 2013, 34, 1331–1333. [Google Scholar] [CrossRef]

- Ilatikhameneh, H.; Tan, Y.; Novakovic, B.; Klimeck, G.; Rahman, R.; Appenzeller, J. Tunnel field-effect transistors in 2-D transition metal dichalcogenide materials. IEEE J. Explor. Solid-State Comput. Devices Circuits 2015, 1, 12–18. [Google Scholar] [CrossRef]

- Seo, J.; Jung, S.; Shin, M. The Performance of Uniaxially Strained Phosphorene Tunneling Field-Effect Transistors. IEEE Electron Device Lett. 2017, 38, 1150–1152. [Google Scholar] [CrossRef]

- Chen, F.W.; Ilatikhameneh, H.; Ameen, T.A.; Klimeck, G.; Rahman, R. Thickness engineered tunnel field-effect transistors based on phosphorene. IEEE Electron Device Lett. 2017, 38, 130–133. [Google Scholar] [CrossRef]

- Szabó, Á.; Koester, S.J.; Luisier, M. Ab-initio simulation of van der waals MoTe2–SnS2 heterotunneling fets for low-power electronics. IEEE Electron Device Lett. 2015, 36, 514–516. [Google Scholar]

- Cao, J.; Logoteta, D.; Özkaya, S.; Biel, B.; Cresti, A.; Pala, M.G.; Esseni, D. Operation and Design of van der Waals Tunnel Transistors: A 3-D Quantum Transport Study. IEEE Trans. Electron Devices 2016, 63, 4388–4394. [Google Scholar] [CrossRef]

- Manipatruni, S.; Nikonov, D.E.; Lin, C.C.; Gosavi, T.A.; Liu, H.; Prasad, B.; Huang, Y.L.; Onturim, E.; Ramesh, R.; Young, I.A. Scalable energy-efficient magnetoelectric spin–orbit logic. Nature 2019, 565, 35–42. [Google Scholar] [CrossRef]

- Watanabe, K.; Takagi, Y.; Obara, K.; Okuda, H.; Nakagaki, R.; Kurosaki, T. Efficient killer-defect control using reliable high-throughput SEM-ADC. In Proceedings of the 2001 IEEE/SEMI Advanced Semiconductor Manufacturing Conference (IEEE Cat. No.01CH37160), Munich, Germany, 23–24 April 2001; pp. 219–222. [Google Scholar]

- Patterson, O.D.; Seefeldt, B.; Liang, W.; Hu, H.; Chen, J.; Su, Y.; Yeh, H.T.; Zhang, P. Shortest path CD measurement using contour extraction. In Proceedings of the 2018 29th Annual SEMI Advanced Semiconductor Manufacturing Conference (ASMC), Saratoga Springs, NY, USA, 30 April–3 May 2018; pp. 313–319. [Google Scholar]

- Takamizawa, H.; Shimizu, Y.; Inoue, K.; Toyama, T.; Okada, N.; Kato, M.; Uchida, H.; Yano, F.; Nishida, A.; Mogami, T.; et al. Origin of characteristic variability in metal-oxide-semiconductor field-effect transistors revealed by three-dimensional atom imaging. Appl. Phys. Lett. 2011, 99, 133502. [Google Scholar] [CrossRef]

- Grenier, A.; Duguay, S.; Barnes, J.P.; Serra, R.; Haberfehlner, G.; Cooper, D.; Bertin, F.; Barraud, S.; Audoit, G.; Arnoldi, L.; et al. 3D analysis of advanced nano-devices using electron and atom probe tomography. Ultramicroscopy 2014, 136, 185–192. [Google Scholar] [CrossRef]

- Barnes, J.P.; Grenier, A.; Mouton, I.; Barraud, S.; Audoit, G.; Bogdanowicz, J.; Fleischmann, C.; Melkonyan, D.; Vandervorst, W.; Duguay, S.; et al. Atom probe tomography for advanced nanoelectronic devices: Current status and perspectives. Scr. Mater. 2018, 148, 91–97. [Google Scholar] [CrossRef]

- Giddings, A.D.; Koelling, S.; Shimizu, Y.; Estivill, R.; Inoue, K.; Vandervorst, W.; Yeoh, W.K. Industrial application of atom probe tomography to semiconductor devices. Scr. Mater. 2018, 148, 82–90. [Google Scholar] [CrossRef]

- Patrick, H.J.; Germer, T.A. Progress towards traceable nanoscale optical critical dimension metrology for semiconductors. In Advanced Characterization Techniques for Optics, Semiconductors, and Nanotechnologies III; Duparre, A., Singh, B., Gu, Z.H., Eds.; SPIE: San Diego, CA, USA, 2007; Volume 6672. [Google Scholar]

- Germer, T.A.; Patrick, H.J.; Silver, R.M.; Bunday, B. Developing an Uncertainty Analysis for Optical Scatterometry; SPIE: San Diego, CA, USA, 2009; Volume 7272. [Google Scholar]

- Diebold, A.C. Characterization and metrology for nanoelectronics. In Frontiers of Characterization and Metrology for Nanoelectronics: 2007; Seiler, D.G., Diebold, A.C., McDonald, R., Garner, C.M., Herr, D., Khosla, R.P., Secula, E.M., Eds.; American Institute of Physics: Melville, NY, USA, 2007; Volume 931, pp. 20–33. [Google Scholar]

- Vagos, P.; Rovira, P.I. Mueller Matrix Spectroscopy Using Chiroptic. US Patent 8427645-B2, 23 April 2013. [Google Scholar]

- Novikova, T.; De Martino, A.; Ben Hatit, S.; Drevillon, B. Application of Mueller polarimetry in conical diffraction for critical dimension measurements in microelectronics. Appl. Opt. 2006, 45, 3688–3697. [Google Scholar] [CrossRef]

- Liu, S.Y.; Chen, X.G.; Zhang, C.W. Development of a broadband Mueller matrix ellipsometer as a powerful tool for nanostructure metrology. Thin Solid Films 2015, 584, 176–185. [Google Scholar] [CrossRef]

- Vaid, A.; Bin Yan, B.; Jiang, Y.T.; Kelling, M.; Hartig, C.; Allgair, J.; Ebersbach, P.; Sendelbach, M.; Rana, N.; Katnani, A.; et al. A Holistic Metrology Approach: Hybrid Metrology Utilizing Scatterometry, CD-AFM and CD-SEM. In Metrology, Inspection, and Process Control for Microlithography Xxv, Pt 1 and Pt 2; Raymond, C.J., Ed.; SPIE: San Jose, CA, USA, 2011; Volume 7971. [Google Scholar]

- Radamson, H.H.; Hallstedt, J. Application of high-resolution X-ray diffraction for detecting defects in SiGe(C) materials. J. Phys. Condes. Matter 2005, 17, S2315–S2322. [Google Scholar] [CrossRef]

- Hansson, G.V.; Radamsson, H.H.; Ni, W.X. Strain and relaxation in SI-MBE structures studied by reciprocal space mapping using high-resolution X-ray-diffraction. J. Mater. Sci. Mater. Electron. 1995, 6, 292–297. [Google Scholar] [CrossRef]

- Radamson, H.H.; Sardela, M.R.; Hultman, L.; Hansson, G.V. Characterization of highly sb-doped SI using high-resolution X-ray-diffraction and transmission electron-microscopy. J. Appl. Phys. 1994, 76, 763–767. [Google Scholar] [CrossRef]

- Radamson, H.H.; Kolahdouz, M.; Ghandi, R.; Ostling, M. High strain amount in recessed junctions induced by selectively deposited boron-doped SiGe layers. Mater. Sci. Eng. B Adv. Funct. Solid-State Mater. 2008, 154, 106–109. [Google Scholar] [CrossRef]

- Sardela, M.R.; Radamson, H.H.; Ekberg, J.O.; Sundgren, J.E.; Hansson, G.V. Relation between electrical activation and the B-induced strain in Si determined by reciprocal lattice mapping. Semicond. Sci. Technol. 1994, 9, 1272–1275. [Google Scholar] [CrossRef]

- Hung, P.Y.; Kasper, N.; Nadeau, J.; Ok, I.; Hobbs, C.; Vigliante, A. Application of inline high resolution X-ray diffraction in monitoring Si/SiGe and conventional Si in SOI fin-shaped field effect transistor processes. J. Vac. Sci. Technol. B 2012, 30, 5. [Google Scholar] [CrossRef]

- Medikonda, M.; Muthinti, G.R.; Fronheiser, J.; Kamineni, V.; Wormington, M.; Matney, K.; Adam, T.N.; Karapetrova, E.; Diebold, A.C. Measurement of periodicity and strain in arrays of single crystal silicon and pseudomorphic Si1-xGex/Si fin structures using x-ray reciprocal space maps. J. Vac. Sci. Technol. B 2014, 32, 021804. [Google Scholar] [CrossRef]

- Mochizuki, S.; Murray, C.E.; Madan, A.; Pinto, T.; Wang, Y.Y.; Li, J.T.; Weng, W.H.; Jagannathan, H.; Imai, Y.; Kimura, S.; et al. Quantification of local strain distributions in nanoscale strained SiGe FinFET structures. J. Appl. Phys. 2017, 122, 135705. [Google Scholar] [CrossRef]

- Schulze, A.; Loo, R.; Witters, L.; Mertens, H.; Gawlik, A.; Horiguchi, N.; Collaert, N.; Wormington, M.; Ryan, P.; Vandervorst, W.; et al. Strainand Compositional Analysis of (Si) Ge Fin Structures Using High Resolution X-Ray Diffraction. Phys. Status Solidi (c) 2017, 14. [Google Scholar] [CrossRef]

- Reboh, S.; Coquand, R.; Barraud, S.; Loubet, N.; Bernier, N.; Audoit, G.; Rouviere, J.L.; Augendre, E.; Li, J.; Gaudiello, J.; et al. Strain, stress, and mechanical relaxation in fin-patterned Si/SiGe multilayers for sub-7nm nanosheet gate-all-around device technology. Appl. Phys. Lett. 2018, 112, 051901. [Google Scholar] [CrossRef]

- Wang, C.Q.; Jones, R.L.; Lin, E.K.; Wu, W.L.; Villarrubia, J.S.; Choi, K.W.; Clarke, J.S.; Rice, B.J.; Leeson, M.; Roberts, J.; et al. Line edge roughness characterization of sub-50 nm structures using CD-SAXS: Round-robin benchmark results. In Metrology, Inspection, and Process Control for Microlithography Xxi, Pts 1–3; Archie, C.N., Ed.; SPIE: San Jose, CA, USA, 2007; Volume 6518. [Google Scholar]

- Sunday, D.F.; List, S.; Chawla, J.S.; Kline, R.J. Determining the shape and periodicity of nanostructures using small-angle X-ray scattering. J. Appl. Cryst. 2015, 48, 1355–1363. [Google Scholar] [CrossRef]

- Sunday, D.F.; Hammond, M.R.; Wang, C.Q.; Wu, W.L.; Kline, R.J.; Stein, G.E. Three-dimensional X-ray metrology for block copolymer lithography line-space patterns. J. Micro-Nanolithogr. MEMS MOEMS 2013, 12, 031103. [Google Scholar] [CrossRef]

- Pfluger, M.; Soltwisch, V.; Probst, J.; Scholze, F.; Krumrey, M. Grazing-incidence small-angle X-ray scattering (GISAXS) on small periodic targets using large beams. IUCrJ 2017, 4, 431–438. [Google Scholar] [CrossRef] [PubMed]

- NovaFit™. Nova’s Data Empowered Metrology Solution. Available online: http://www.novami.com/nova-product/novafit (accessed on 4 April 2019).

| Technology Nodes | Film Thickness (nm) | |||

|---|---|---|---|---|

| Thermal Oxide | High-k | TiAl(N) | TiN | |

| 45 nm | ~1.2 | ~1.5 | ~2 | ~2.1 |

| 32 nm | ~1.2 | ~1.1 | ~1.7 | ~2 |

| 22 nm | ~1.1 | ~1.0 | ~1.2 | ~1.4 |

| 14 nm | ~0.6 | ~1.2 | ~1.2 | ~1.4 |

| 5 nm | ~0.5 | ~1.0 | ~1.0 | ~1.2 |

| Metal | Dep. Method | Effective Work Function | Ref. |

|---|---|---|---|

| TaCy | PEALD | 4.77–4.54 eV | [84] |

| TaCN | PEALD | 4.37 eV | [85] |

| TiC | PEALD | 5.24 eV–4.45 eV | [86] |

| WC0.4 | PEALD | 4.2+/-0.1 eV | [87] |

| ErC2 | ALD | 3.9 eV | [88] |

| TiAlC | thermal ALD | 4.79–4.49 | [90] |

| TiAlC | thermal ALD | 4.46–4.24 | [91] |

| TaAlC | thermal ALD | 4.74–4.49 | [92] |

| TaAlC | thermal ALD | 4.65–4.26 | [93] |

| No. | Process Name | Material | Normalized Total Resistance | |

|---|---|---|---|---|

| S/D Contact Level | MOL LI Level | |||

| 1 | By Scaling | Ti/TiN W | Ti/TiN W | 1 |

| 2 | Process A | Ti/TiN W | Co | 0.85 |

| 3 | Process B | Ti/TiN W | Liner free W | 0.7 |

| 4 | Process C | Liner free W | Co | 0.55 |

| 5 | Process D | Liner free W | Ru | 0.55 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Radamson, H.H.; He, X.; Zhang, Q.; Liu, J.; Cui, H.; Xiang, J.; Kong, Z.; Xiong, W.; Li, J.; Gao, J.; et al. Miniaturization of CMOS. Micromachines 2019, 10, 293. https://doi.org/10.3390/mi10050293

Radamson HH, He X, Zhang Q, Liu J, Cui H, Xiang J, Kong Z, Xiong W, Li J, Gao J, et al. Miniaturization of CMOS. Micromachines. 2019; 10(5):293. https://doi.org/10.3390/mi10050293

Chicago/Turabian StyleRadamson, Henry H., Xiaobin He, Qingzhu Zhang, Jinbiao Liu, Hushan Cui, Jinjuan Xiang, Zhenzhen Kong, Wenjuan Xiong, Junjie Li, Jianfeng Gao, and et al. 2019. "Miniaturization of CMOS" Micromachines 10, no. 5: 293. https://doi.org/10.3390/mi10050293

APA StyleRadamson, H. H., He, X., Zhang, Q., Liu, J., Cui, H., Xiang, J., Kong, Z., Xiong, W., Li, J., Gao, J., Yang, H., Gu, S., Zhao, X., Du, Y., Yu, J., & Wang, G. (2019). Miniaturization of CMOS. Micromachines, 10(5), 293. https://doi.org/10.3390/mi10050293