Design and Optimization of Germanium-Based Gate-Metal-Core Vertical Nanowire Tunnel FET

Abstract

1. Introduction

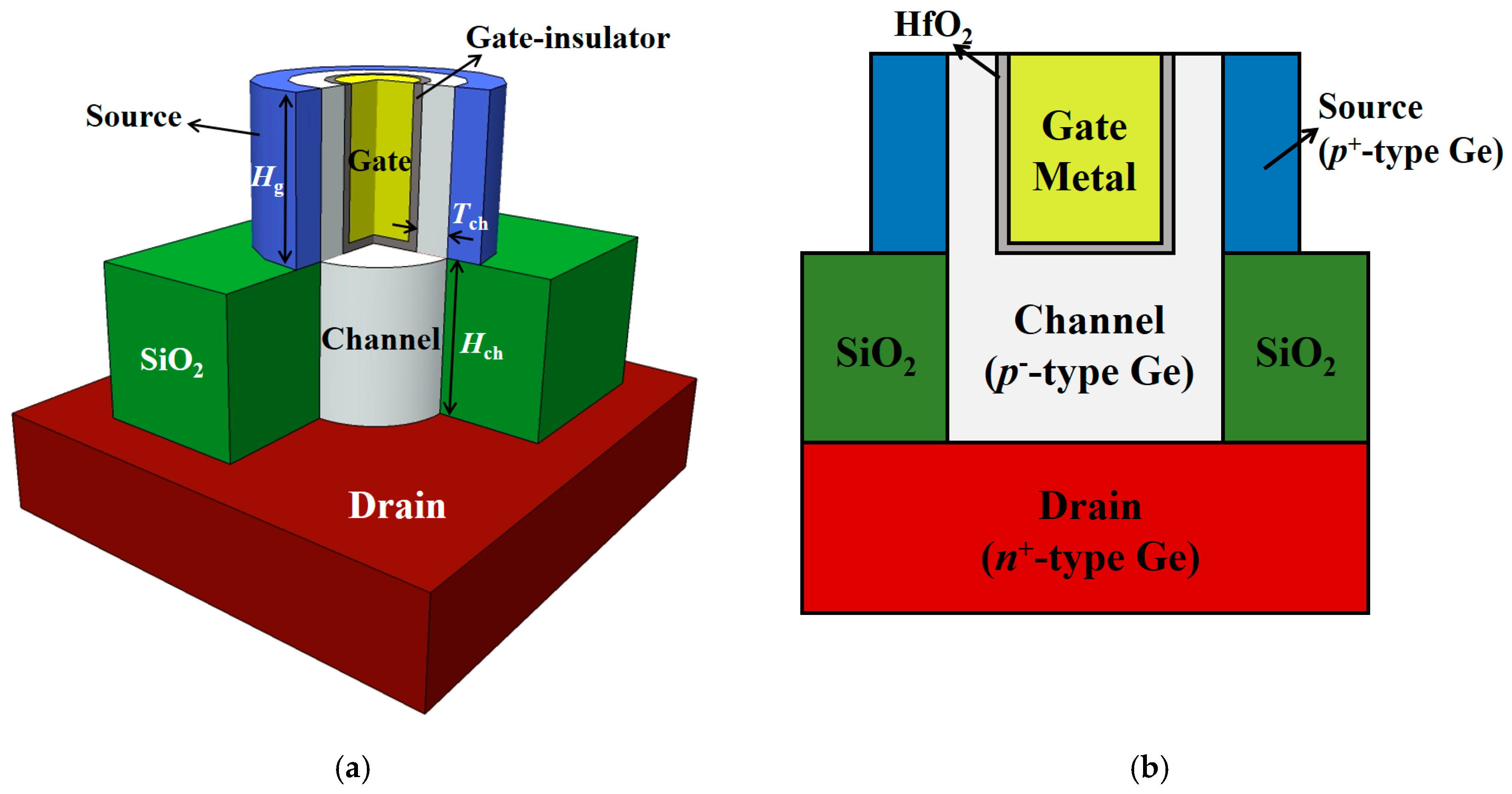

2. Device Structure and Description

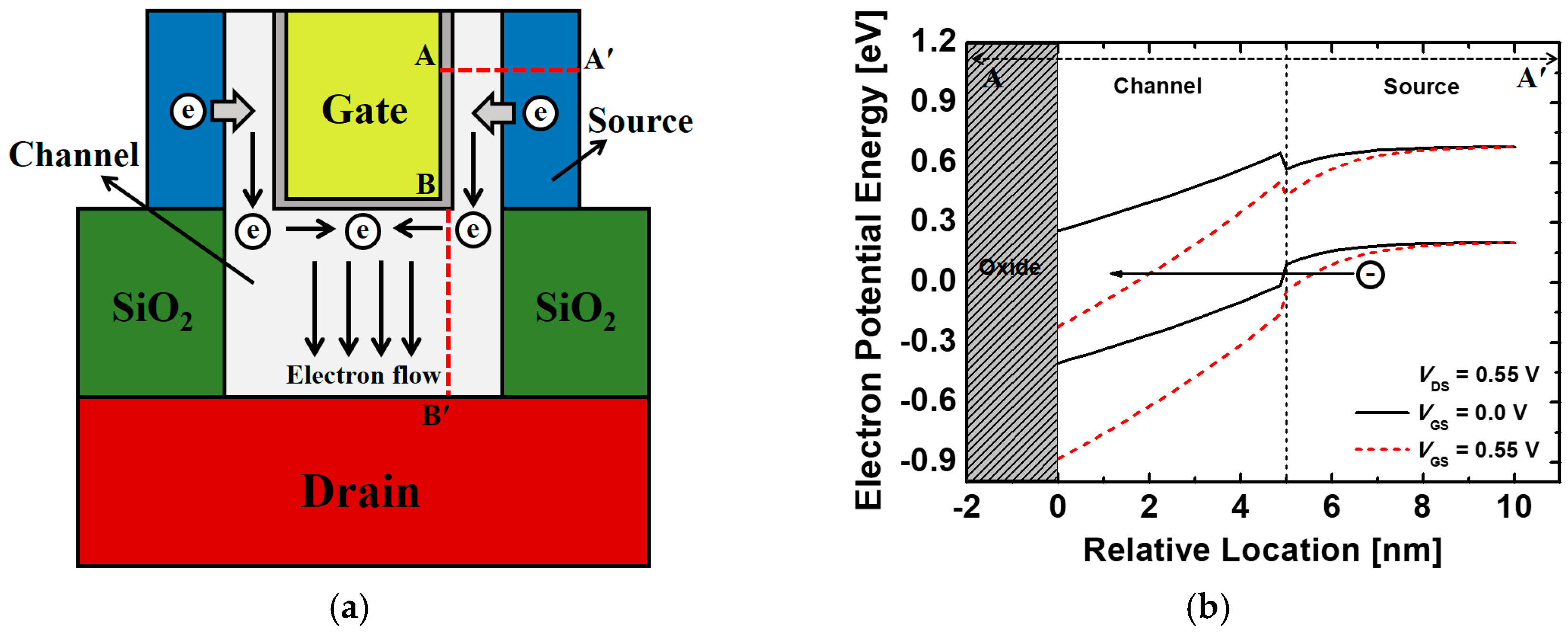

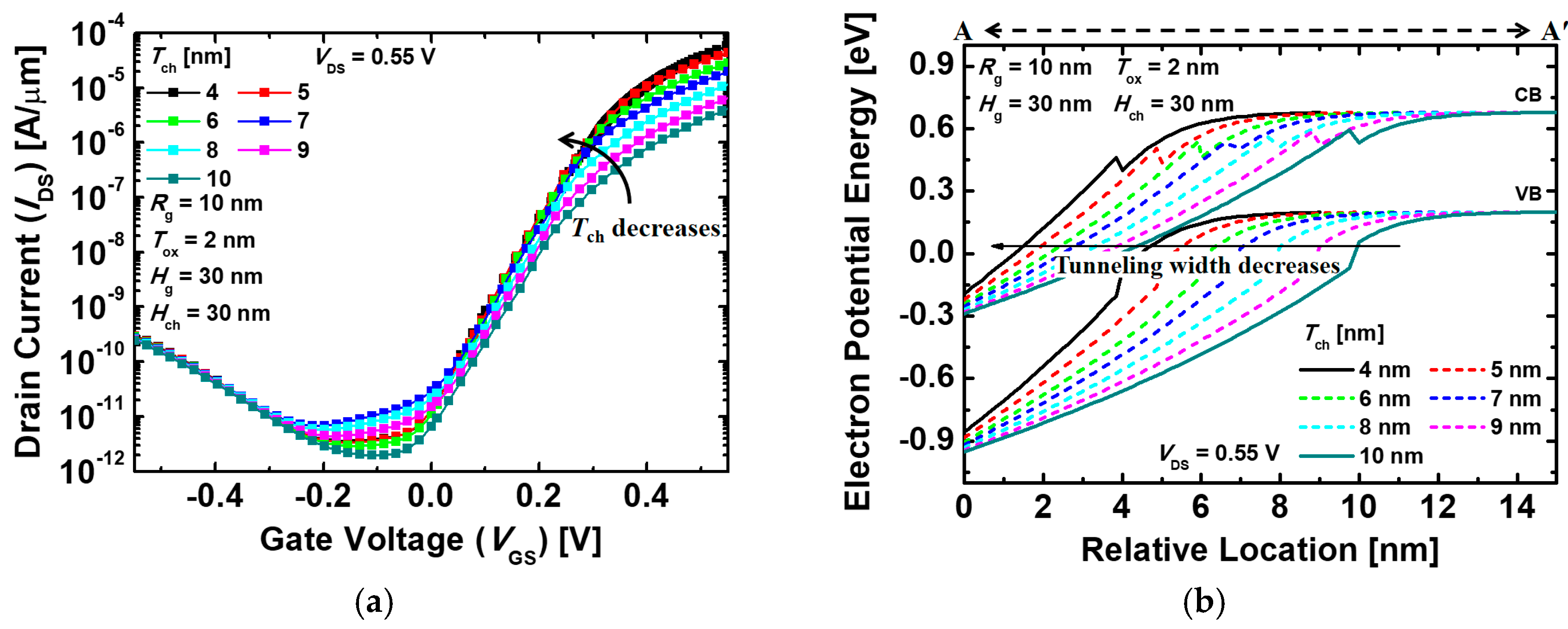

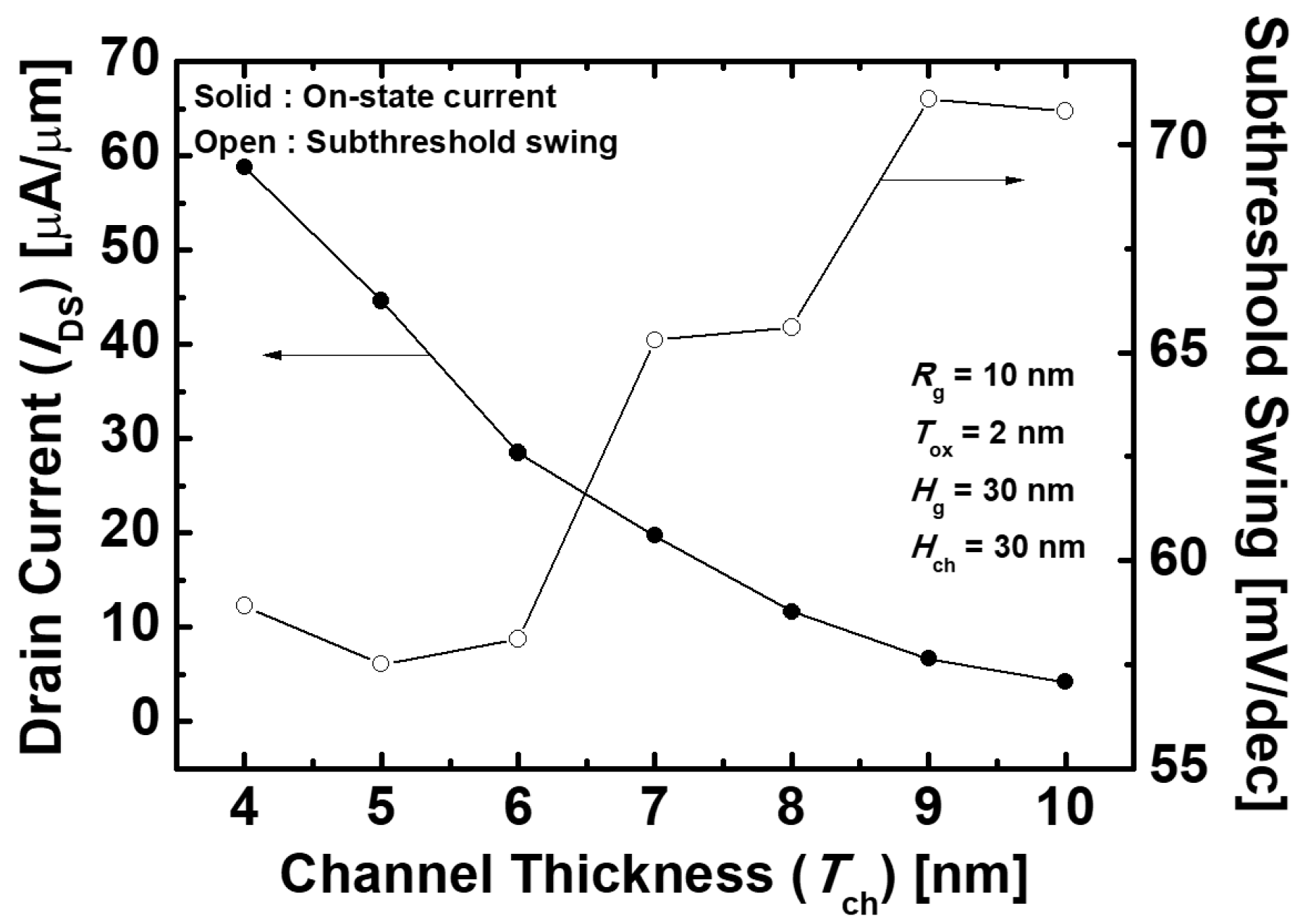

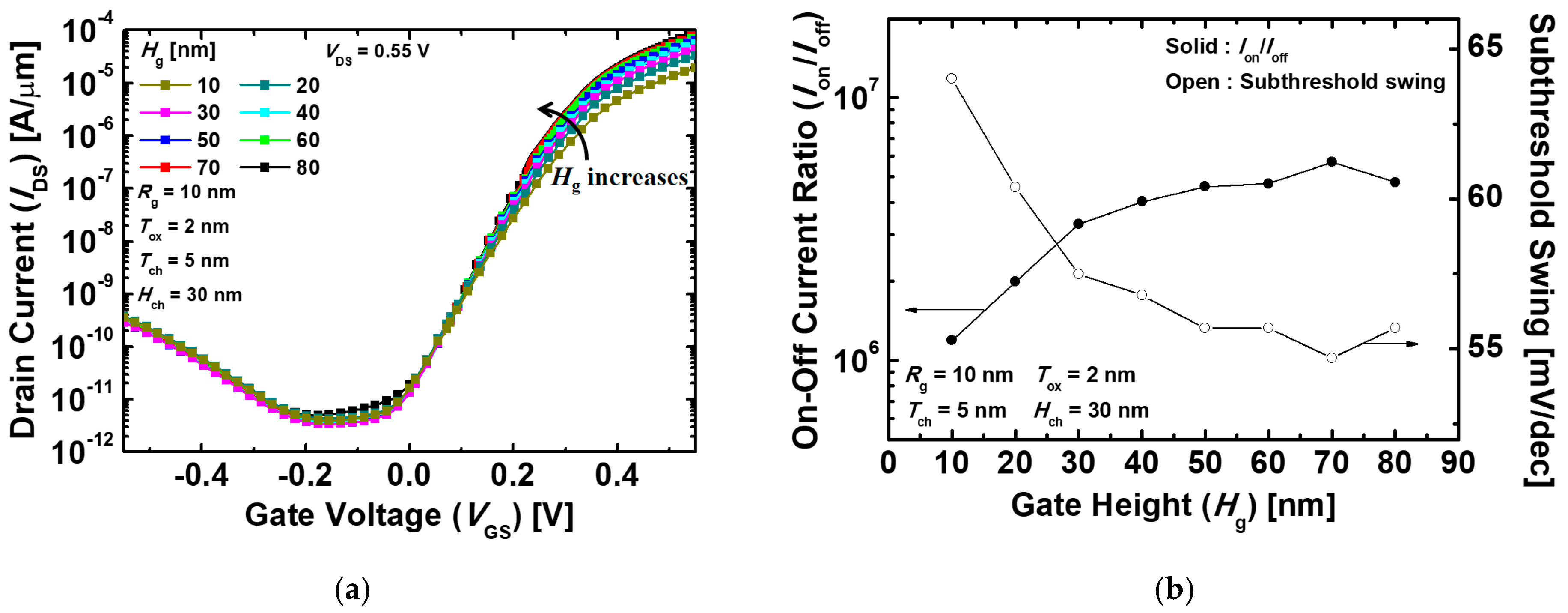

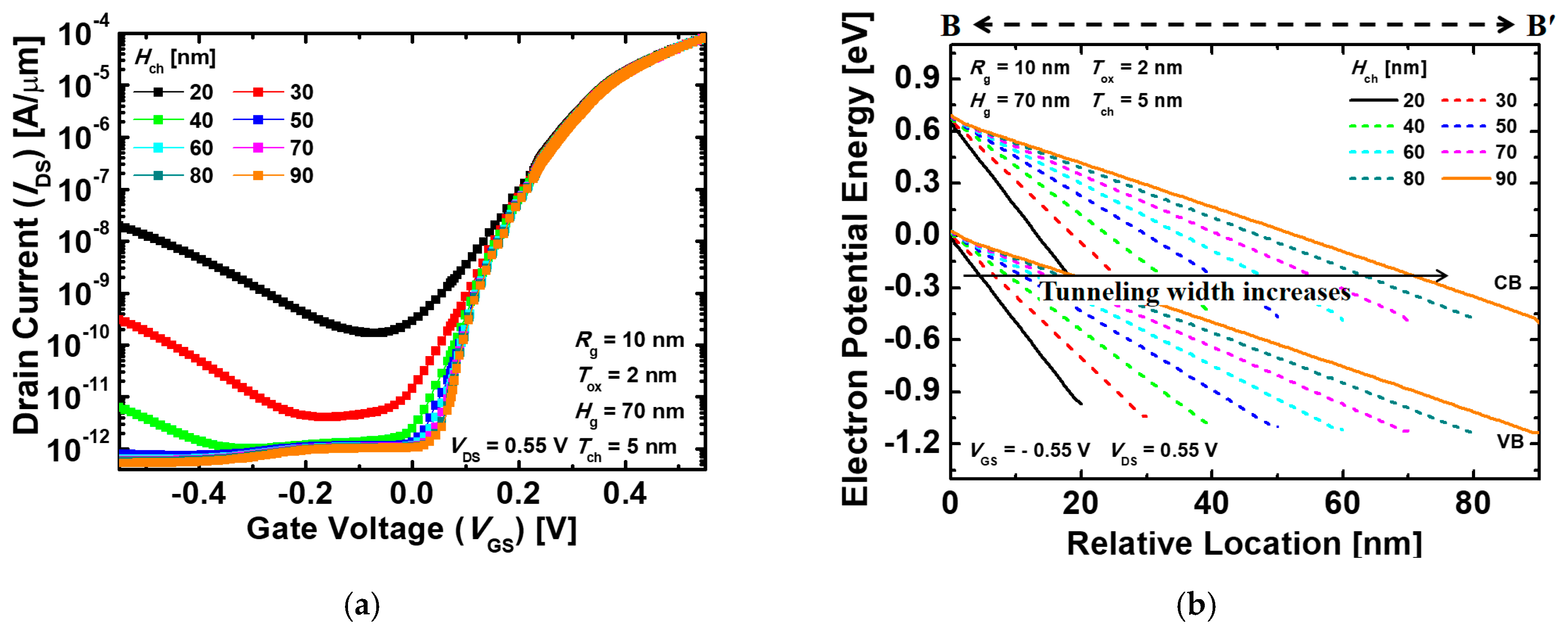

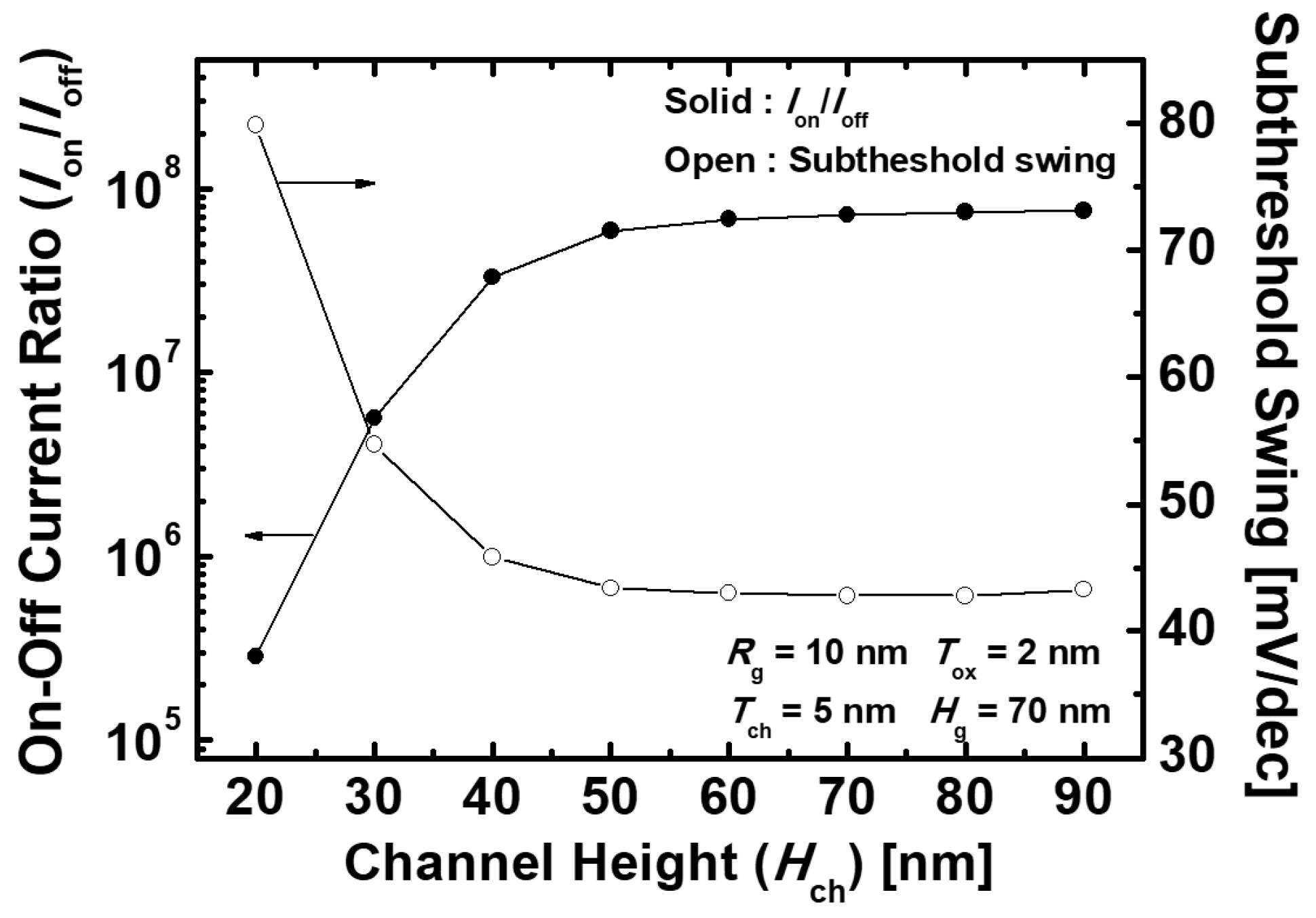

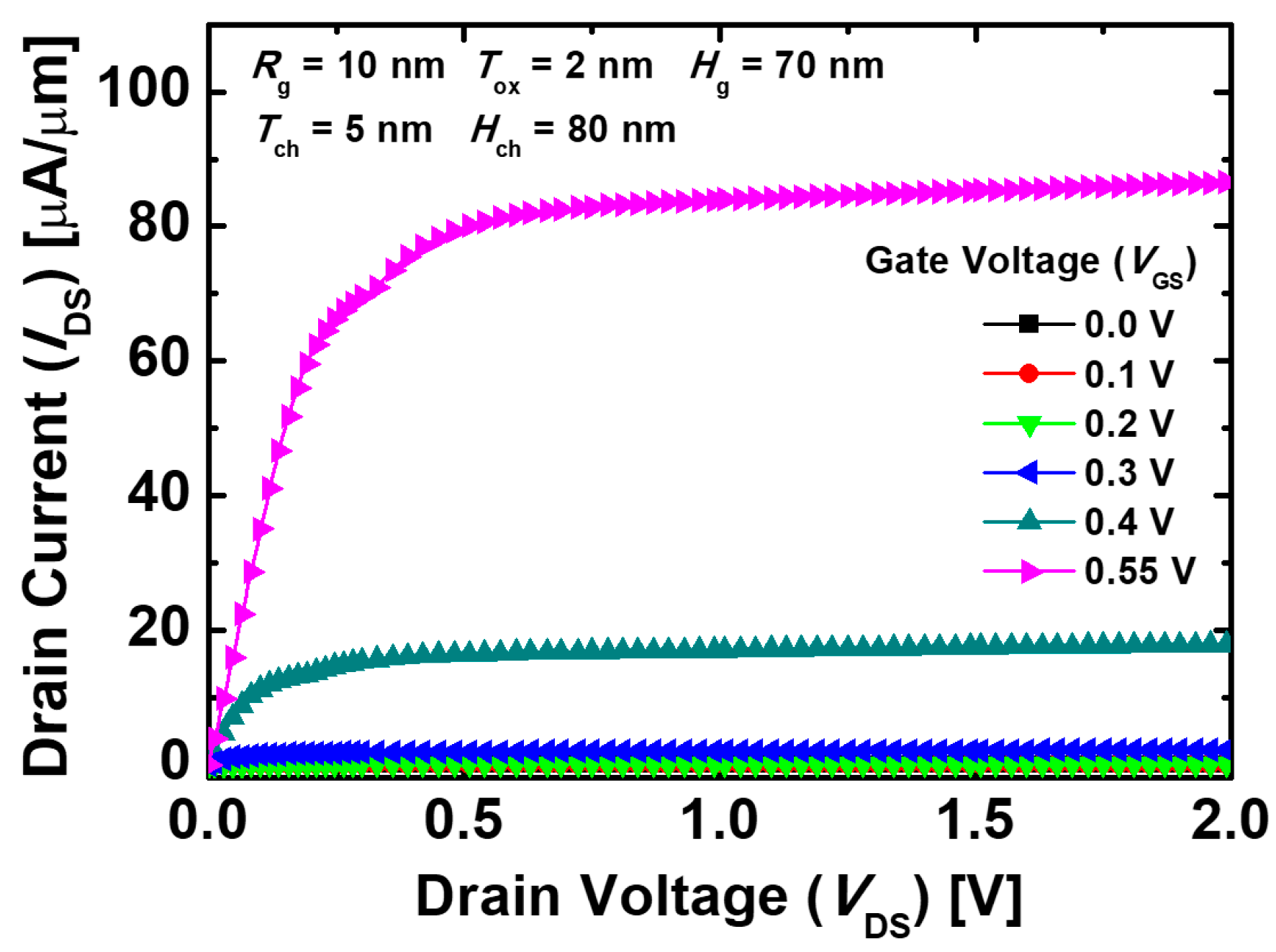

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Acknowledgments

Conflicts of Interest

References

- Avci, U.E.; Rios, R.; Kuhn, K.; Young, I.A. Comparison of performance, switching energy and process variations for the TFET and MOSFET in logic. In Proceedings of the 2011 Symposium on VLSI Technology-Digest of Technical Papers, Honolulu, HL, USA, 14–16 June 2011; pp. 124–125. [Google Scholar]

- Davari, B.; Dennard, R.H.; Shahidi, G.G. CMOS scaling for high performance and low power-the next ten years. Proc. IEEE 1995, 83, 595–606. [Google Scholar] [CrossRef]

- Khatami, Y.; Banerjee, K. Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Electron Devices 2009, 85, 2752–2761. [Google Scholar] [CrossRef]

- Choi, W.Y.; Park, B.G.; Lee, J.D.; Liu, T.J.K. Tunneling field-effect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 2007, 28, 743–745. [Google Scholar] [CrossRef]

- Nirschl, T.; Wang, P.F.; Weber, C.; Sedlmeir, J.; Heinrich, R.; Kakoschke, R.; Schrufer, K.; Holz, J.; Pacha, C.; Schulz, T.; et al. The tunneling field effect transistor (TFET) as an add-on for ultra-low-voltage analog and digital processes. In Proceedings of the 2004 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 13–15 December 2004; pp. 195–198. [Google Scholar]

- Wang, P.F.; Hilsenbeck, K.; Nirschl, T.; Oswald, M.; Stepper, C.; Weis, M.; Schmitt-Landsiedel, D.; Hansch, W. Complementary tunneling transistor for low power application. Solid-State Electron. 2004, 48, 2281–2286. [Google Scholar] [CrossRef]

- Avci, U.E.; Kuhn, K.J.; Young, I.A. Comparison of power and performance for the TFET and MOSFET and considerations for P-TFET. In Proceedings of the 2011 11th IEEE International Conference on Nanotechnology, Portland, OR, USA, 15–18 August 2011; pp. 869–872. [Google Scholar]

- Vladimirescu, A.; Amara, A.; Anghel, C. An analysis on the ambipolar current in Si double-gate tunnel FETs. Solid-State Electron. 2012, 70, 67–72. [Google Scholar]

- Moselund, K.E.; Ghoneim, H.; Bjork, M.T.; Schmid, H.; Karg, S.; Lortscher, E.; Riess, W.; Riel, H. Comparison of VLS grown Si NW tunnel FETs with different gate stacks. In Proceedings of the 2009 European Solid State Device Research Conference, Athens, Greece, 14–18 September 2009; pp. 448–451. [Google Scholar]

- Narang, R.; Saxena, M.; Gupta, R.S.; Gupta, M. Assessment of ambipolar behavior of a tunnel FET and influence of structural modifications. J. Semicond. Technol. Sci. 2012, 12, 482–491. [Google Scholar] [CrossRef]

- Wan, J.; Le, R.C.; Zaslavsky, A.; Cristoloveanu, S. Tunneling FETs on SOI: Suppression of ambipolar leakage, low-frequency noise behavior, and modeling. Solid-State Electron. 2011, 65, 226–233. [Google Scholar] [CrossRef]

- Krishnamohan, T.; Kim, D.; Raghunathan, S.; Saraswat, K. Double-gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and ≪60mV/dec subthreshold slope. In Proceedings of the 2008 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 15–17 December 2008; pp. 1–3. [Google Scholar]

- Schenk, A.; Sant, S.; Moselund, K.; Riel, H. III–V-based hetero tunnel FETs: A simulation study with focus on non-ideality effects. In Proceedings of the 2016 Joint International EUROSOI Workshop and International Conference on Ultimate Integration on Silicon (EUROSOI-ULIS), Vienna, Austria, 25–27 January 2016; pp. 9–12. [Google Scholar]

- Hu, V.P.; Wang, C. Optimization of III–V heterojunction tunnel FET with non-uniform channel thickness for performance enhancement and ambipolar leakage suppression. Jpn. J. Appl. Phys. 2018, 57, 04FD18. [Google Scholar] [CrossRef]

- Dubey, P.K.; Kaushik, B.K. T-Shaped III-V Heterojunction Tunneling Field-Effect Transistor. IEEE Trans. Electron Devices 2017, 64, 3120–3125. [Google Scholar] [CrossRef]

- Walke, A.M.; Vandooren, A.; Rooyackers, R.; Leonelli, D.; Hikavyy, A.; Loo, R.; Verhulst, A.S.; Kao, K.; Huyghebaert, C.; Groeseneken, G.; et al. Fabrication and analysis of a Si/Si0.55Ge0.45 Heterojunction Line Tunnel FET. IEEE Trans. Electron Devices 2014, 61, 707–715. [Google Scholar] [CrossRef]

- Nah, J.; Liu, E.S.; Varahramyan, K.M.; Tutuc, E. Ge-SixGe1−x core-shell nanowire tunneling field-effect transistors. IEEE Trans. Electron Devices 2010, 57, 1883–1888. [Google Scholar] [CrossRef]

- Shih, P.C.; Hou, W.C.; Li, J.Y. A U-gate InGaAs/GaAsSb heterojunction TFET of tunneling normal to the gate with separate control over ON- and OFF-state current. IEEE Electron Device Lett. 2017, 38, 1751–1754. [Google Scholar] [CrossRef]

- Yang, Z. Tunnel field-effect transistor with an L-shaped gate. IEEE Electron Device Lett. 2016, 37, 839–842. [Google Scholar] [CrossRef]

- Seo, J.H.; Yoon, Y.J.; Lee, S.; Lee, J.H.; Cho, S.; Kang, I.M. Design and analysis of Si-based arch-shaped gate-all-around (GAA) tunneling field-effect transistor (TFET). Curr. Appl. Phys. 2015, 15, 208–212. [Google Scholar] [CrossRef]

- Bagga, N.; Kumar, A.; Dasgupta, S. Demonstration of a novel two source region tunnel FET. IEEE Trans. Electron Devices 2017, 64, 5256–5262. [Google Scholar] [CrossRef]

- Imenabadi, R.M.; Saremi, M.; Vandenberghe, W.G. A novel PNPN-like Z-shaped tunnel field-effect transistor with improved ambipolar behavior and RF performance. IEEE Trans. Electron Devices 2017, 64, 4752–4758. [Google Scholar] [CrossRef]

- Ko, E.; Lee, H.; Park, J.D.; Shin, C. Vertical tunnel FET: Design optimization with triple metal-gate layers. IEEE Trans. Electron Devices 2016, 63, 5030–5035. [Google Scholar] [CrossRef]

- Yoon, J.S.; Kim, K.; Meyyappan, M.; Baek, C.K. Bandgap engineering and strain effects of core-shell tunneling field-effect transistors. IEEE Trans. Electron Devices 2018, 65, 277–281. [Google Scholar] [CrossRef]

- Hu, C. Modern Semiconductor Devices for Integrated Circuits, International ed.; Prentice Hall: Upper Saddle River, NJ, USA, 2009; p. 206. [Google Scholar]

- Sentaurus User’s Manual; Version L-2016.03; Synopsys Inc.: Mountain View, CA, USA, 2016.

- Martino, M.D.; Martino, J.A.; Agopian, P.G. Drain induced barrier tunneling on TFETs with different source/drain engineering. In Proceedings of the 2014 29th Symposium on Microelectronics Technology and Devices (SBMicro), Aracaju, Brazil, 1–5 September 2014; pp. 1–4. [Google Scholar]

- Patel, J.; Sharma, D.; Yadav, S.; Lemtur, A.; Suman, P. Performance improvement of nano wire TFET by hetero-dielectric and hetero-material: At device and circuit level. Microelectron. J. 2019, 85, 72–82. [Google Scholar] [CrossRef]

- Kumar, N.; Mushtaq, U.; Amin, S.I.; Anand, S. Design and performance analysis of Dual-Gate All around Core-Shell Nanotube TFET. Superlattice Microstruct. 2019, 125, 356–364. [Google Scholar] [CrossRef]

- Li, W.; Wang, S.; Chen, S.; Yang, Z. Design of High performance Si/SiGe Heterojunction Tunneling FETs with a T-Shaped Gate. Nanoscale Res. Lett. 2017, 12, 198. [Google Scholar] [CrossRef] [PubMed]

- Vanlalawmpuia, K.; Bhowmick, B. Investigation of a Ge-Source Vertical TFET with Delta-Doped Layer. IEEE Trans. Electron Devices 2019, 66, 4439–4445. [Google Scholar] [CrossRef]

| Parameter | This Work | SiGe-S-NW-TFET [28] | Si-Based Nanotube TFET [29] | Si/SiGe HTG-TFET [30] | Ge-Source vTFET [31] |

|---|---|---|---|---|---|

| Ion (μA/μm) | 80.9 (at VGS = 0.55 V) | 11.66 (at VGS = 1.0 V) | 5.0 (at VGS = 1.5 V) | 7.02 (at VGS = 0.5 V) | 27.6 (at VGS = 0.5 V) |

| Vt (V) | 0.21 | 0.37 | 0.9 | 0.28 | 0.20 |

| VDD (V) | 0.55 | 0.8 | 1.2 | 0.5 | 0.5 |

| SS (mV/dec) | 42.8 | 23.75 | 58.3 | 44.64 | 21.2 |

© 2019 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Jang, W.D.; Yoon, Y.J.; Cho, M.S.; Jung, J.H.; Lee, S.H.; Jang, J.; Bae, J.-H.; Kang, I.M. Design and Optimization of Germanium-Based Gate-Metal-Core Vertical Nanowire Tunnel FET. Micromachines 2019, 10, 749. https://doi.org/10.3390/mi10110749

Jang WD, Yoon YJ, Cho MS, Jung JH, Lee SH, Jang J, Bae J-H, Kang IM. Design and Optimization of Germanium-Based Gate-Metal-Core Vertical Nanowire Tunnel FET. Micromachines. 2019; 10(11):749. https://doi.org/10.3390/mi10110749

Chicago/Turabian StyleJang, Won Douk, Young Jun Yoon, Min Su Cho, Jun Hyeok Jung, Sang Ho Lee, Jaewon Jang, Jin-Hyuk Bae, and In Man Kang. 2019. "Design and Optimization of Germanium-Based Gate-Metal-Core Vertical Nanowire Tunnel FET" Micromachines 10, no. 11: 749. https://doi.org/10.3390/mi10110749

APA StyleJang, W. D., Yoon, Y. J., Cho, M. S., Jung, J. H., Lee, S. H., Jang, J., Bae, J.-H., & Kang, I. M. (2019). Design and Optimization of Germanium-Based Gate-Metal-Core Vertical Nanowire Tunnel FET. Micromachines, 10(11), 749. https://doi.org/10.3390/mi10110749