4. Stability of the Effective Work Function for La-Based High-k Materials

In this section, the stability of the effective work functions (φeff) for p-metals on La-based high-

k materials is studied in detail for various annealing ambients and gate dielectric structures, because it has been widely reported that φeff for p-metals (such as Pt) on Hf-based high-

k materials depends strongly on the annealing ambient [

26,

27,

28]. The factors and the interfaces responsible for the variation of φeff will be discussed [

29].

La

2Hf

2O

7 (LHO) was selected as typical La-based high-

k materials for the comparison with LaAlO

3 (LAO). It is reported that LHO has been also grown directly on Si [

30]. LAO and LHO films were deposited on a 5-nm-thick thermal oxide layer covering 3-inch p-Si wafers or HF-treated p-Si wafers by PLD using a KrF excimer laser. LaAlO

3 single crystal pellets were used as the deposition target for LAO, while La

2Hf

2O

7 sintered pellets were used as the deposition target for LHO.

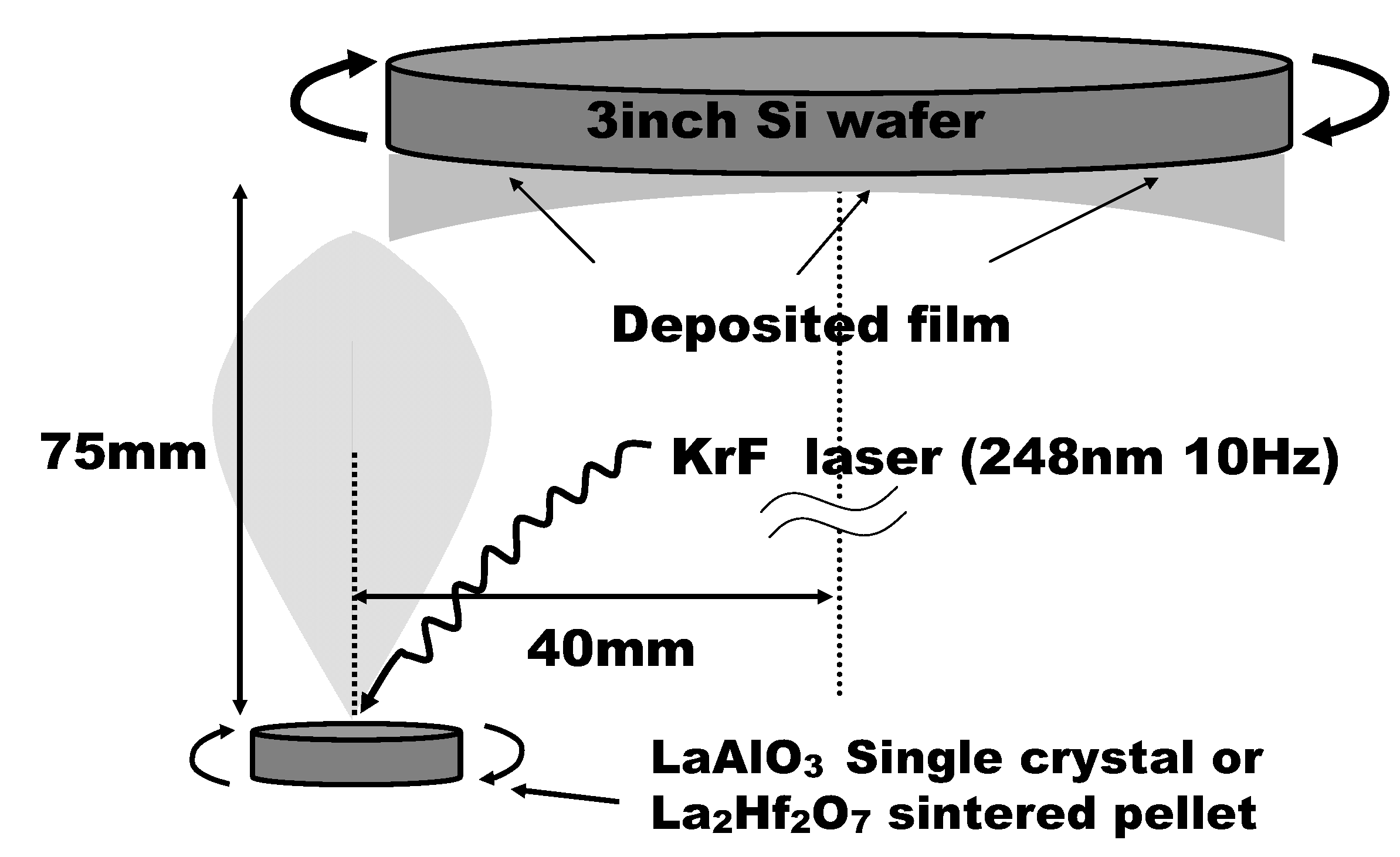

Figure 19 shows a schematic representation of the PLD system used in the experiments. As can be seen in the figure, deposition targets were set below the circumference of the wafer to deposit a film whose thickness increases from the center of the wafer to the circumference, enabling a gradual change of EOT values for accurate estimation of φeff. Pt was selected as a typical p-metal material. Pt films were deposited on LAO and LHO by e-beam evaporation through shadow masks to define the capacitor area, and MIS capacitors were fabricated. After the deposition of Pt, forming gas (H

2/N

2 = 10%) annealing (FGA) was performed at 450 °C for 30 min. Some specimens were additionally annealed in an O

2 ambient, N

2 ambient, or Ar ambient at 400 °C for 30 min after FGA. C-V measurements were carried out for the MIS capacitors. To estimate the elemental depth profile of each dielectric stack, Auger electron spectroscopy (AES) measurements were performed.

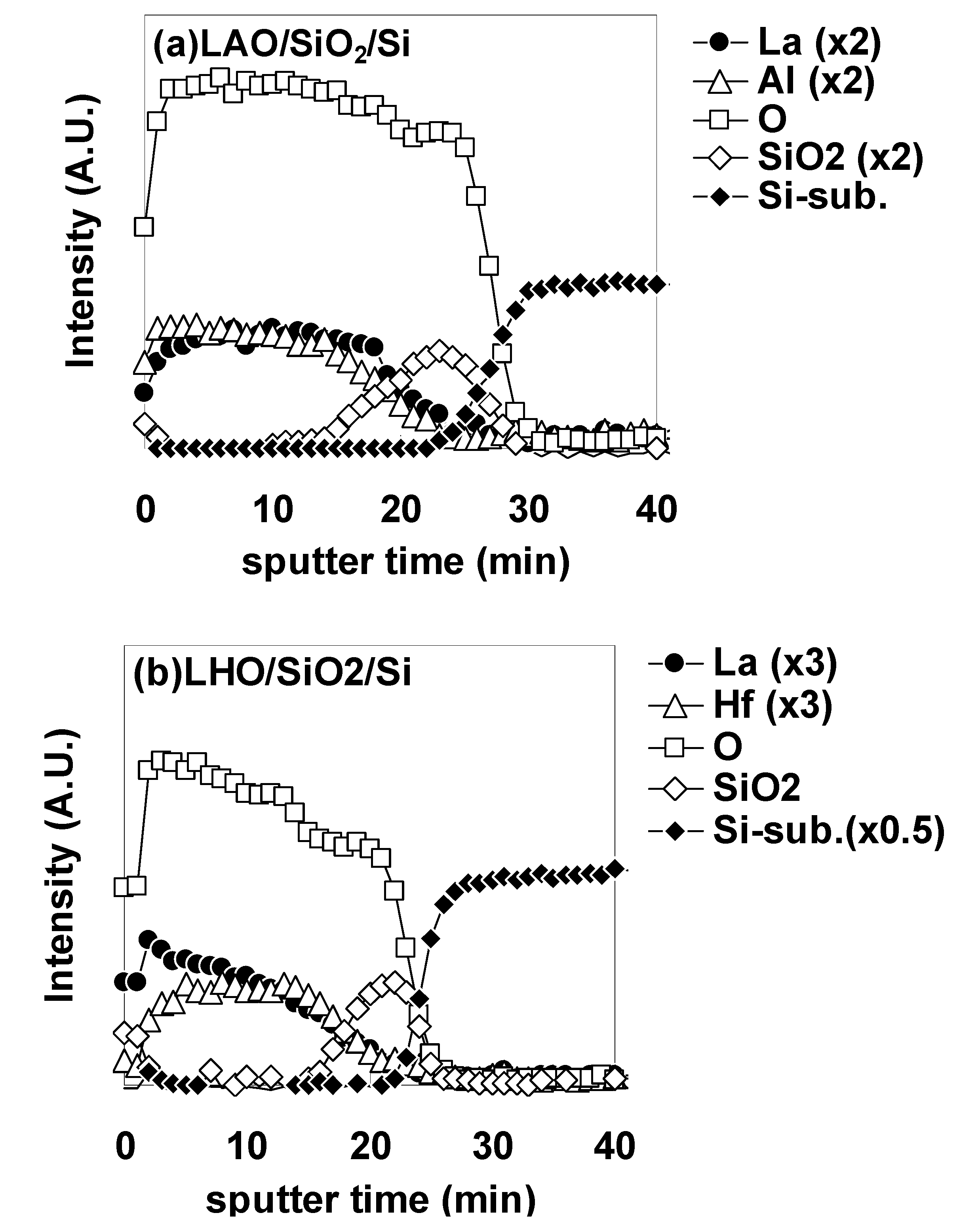

Figure 20 shows the typical depth profiles of the (a) LAO/SiO

2/Si and (b) LHO/SiO

2/Si stacks. Target-factor analysis (TFA) was performed for the Si peaks in order to separate the composite peaks into Si oxide (SiO

2) and Si metal (Si-substrate). As can be seen in

Figure 20, the underlying SiO

2 layer is clearly detected for both LAO and LHO.

Figure 19.

Schematic representation of the PLD system used in the experiments. The film thickness increases with the distance from the center of the wafer.

Figure 19.

Schematic representation of the PLD system used in the experiments. The film thickness increases with the distance from the center of the wafer.

Figure 20.

Typical depth profiles of the (a) LAO/SiO2/Si and (b) La2Hf2O7 (LHO)/SiO2/Si stacks. The detected Auger electron kinetic energies were selected so as to avoid overlapping of peaks. Target-factor analysis (TFA) was performed for the Si peaks in order to separate the composite peaks into Si oxide (SiO2) and Si metal (Si-substrate).

Figure 20.

Typical depth profiles of the (a) LAO/SiO2/Si and (b) La2Hf2O7 (LHO)/SiO2/Si stacks. The detected Auger electron kinetic energies were selected so as to avoid overlapping of peaks. Target-factor analysis (TFA) was performed for the Si peaks in order to separate the composite peaks into Si oxide (SiO2) and Si metal (Si-substrate).

4.1. Differences in the Annealing-Ambient-Dependence of φeff for Pt/LAO/SiO2/Si and Pt/LHO/SiO2/Si

To investigate whether or not the changes in φeff observed after FGA only and after additional O

2 annealing in Hf-based high-

k materials [

26,

27,

28] also occur for La-based high-

k materials, the C-V characteristics were examined after FGA only and after additional O

2 annealing. Measurements were performed for gate stacks with an SiO

2 interfacial layer (as in most of the reports on Hf-based high-

k materials).

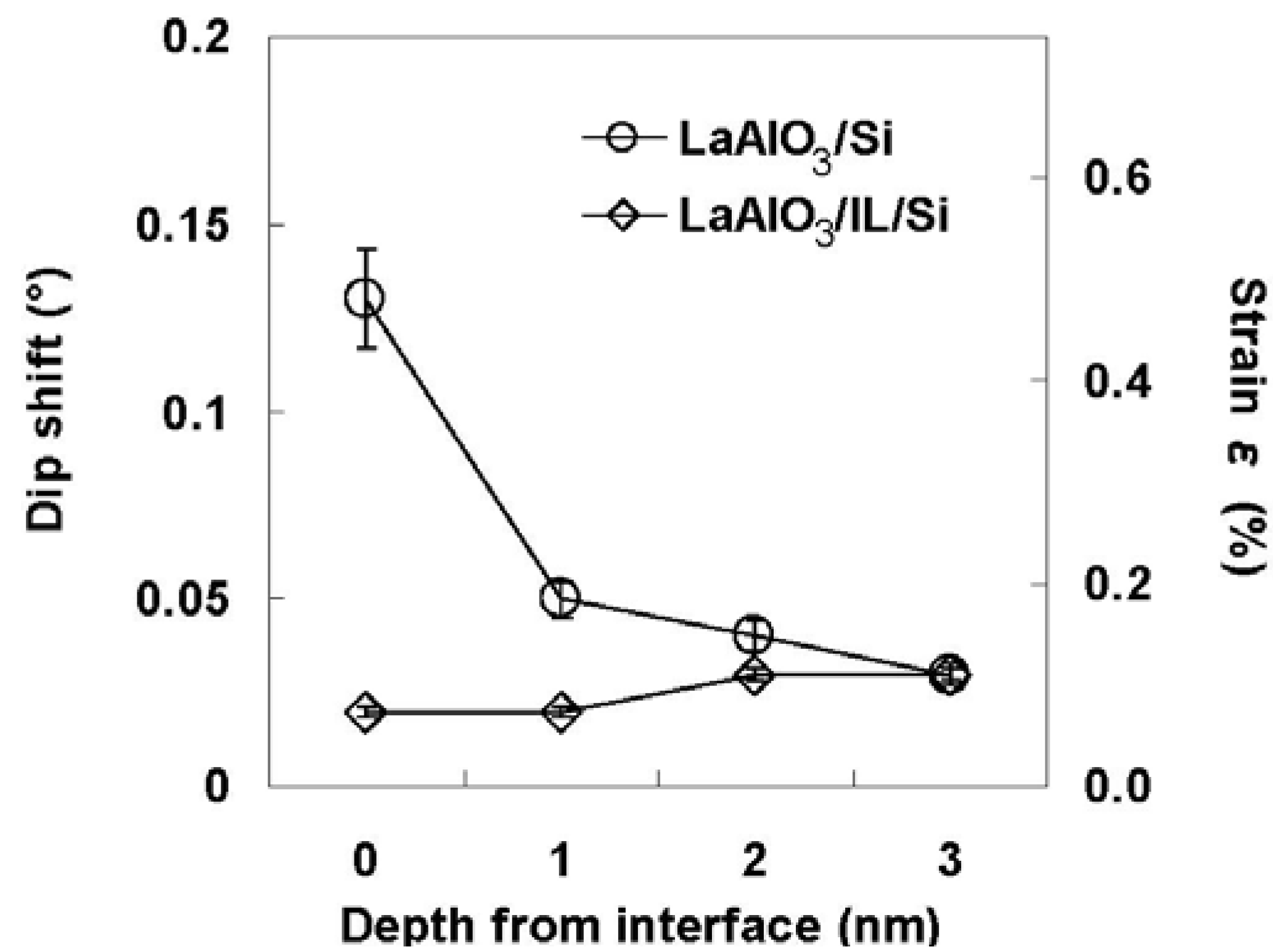

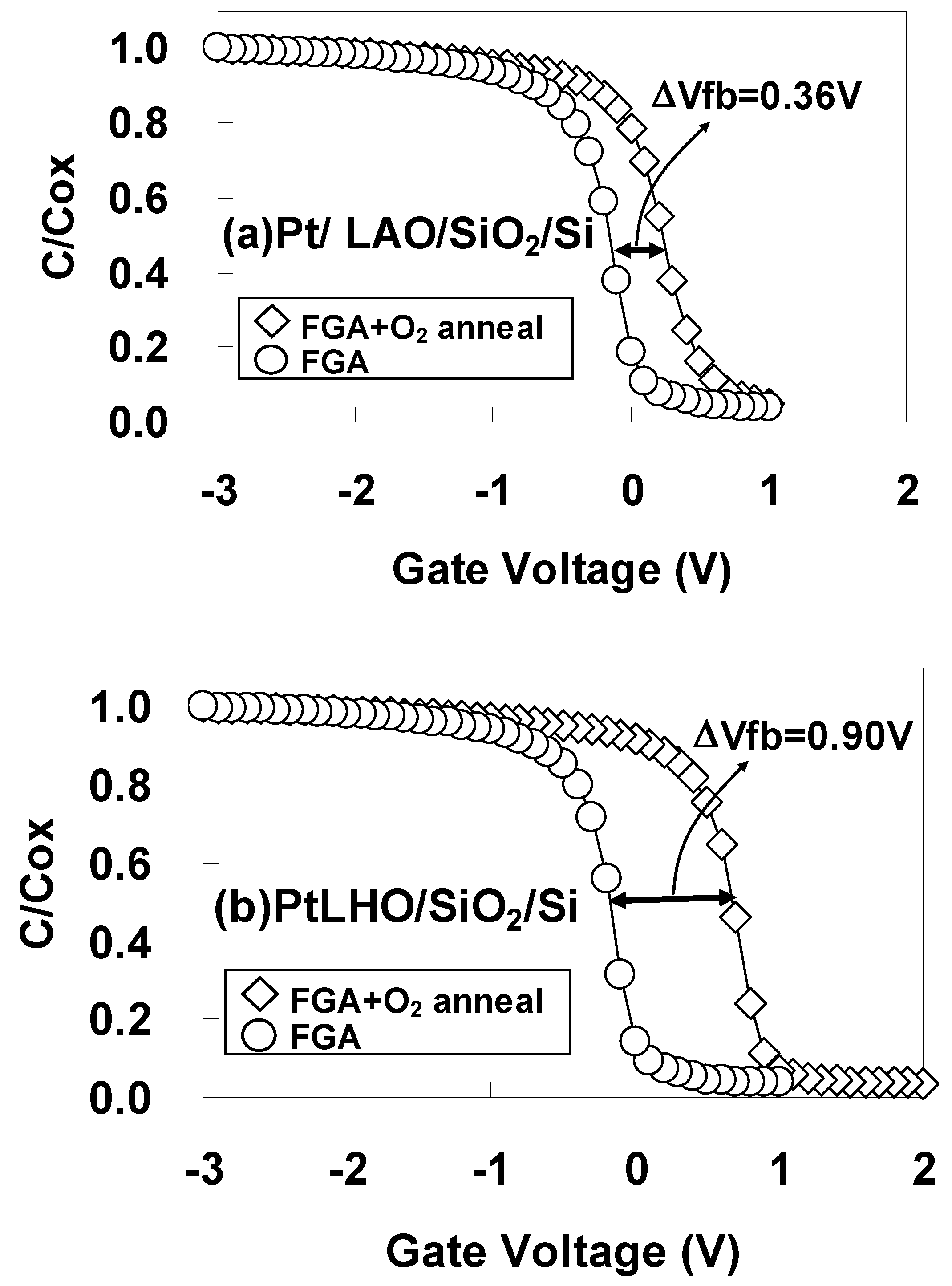

Figure 21 shows the C-V curves for the highest capacitances (as a typical example) for (a) Pt/LAO/SiO

2/Si and (b) Pt/LHO/SiO

2/Si MOS capacitors after FGA only and after additional O

2 annealing. As can be seen in

Figure 21, well-behaved C-V curves were obtained in all the cases, but there was a large difference in the annealing ambient dependences of these capacitors. While the difference in the Vfb values after FGA only and after additional O

2 annealing (ΔVfb) did not exceed 0.36 eV for the Pt/LAO/SiO

2/Si stack, a significantly larger Vfb difference of 0.90 eV was observed for the Pt/LHO/SiO

2/Si stack.

Figure 21.

C-V curves for the highest capacitances for (a) Pt/LAO/SiO2/Si and (b) Pt/LHO/SiO2/Si MOS capacitors after forming gas annealing (FGA) only and after additional O2 annealing.

Figure 21.

C-V curves for the highest capacitances for (a) Pt/LAO/SiO2/Si and (b) Pt/LHO/SiO2/Si MOS capacitors after forming gas annealing (FGA) only and after additional O2 annealing.

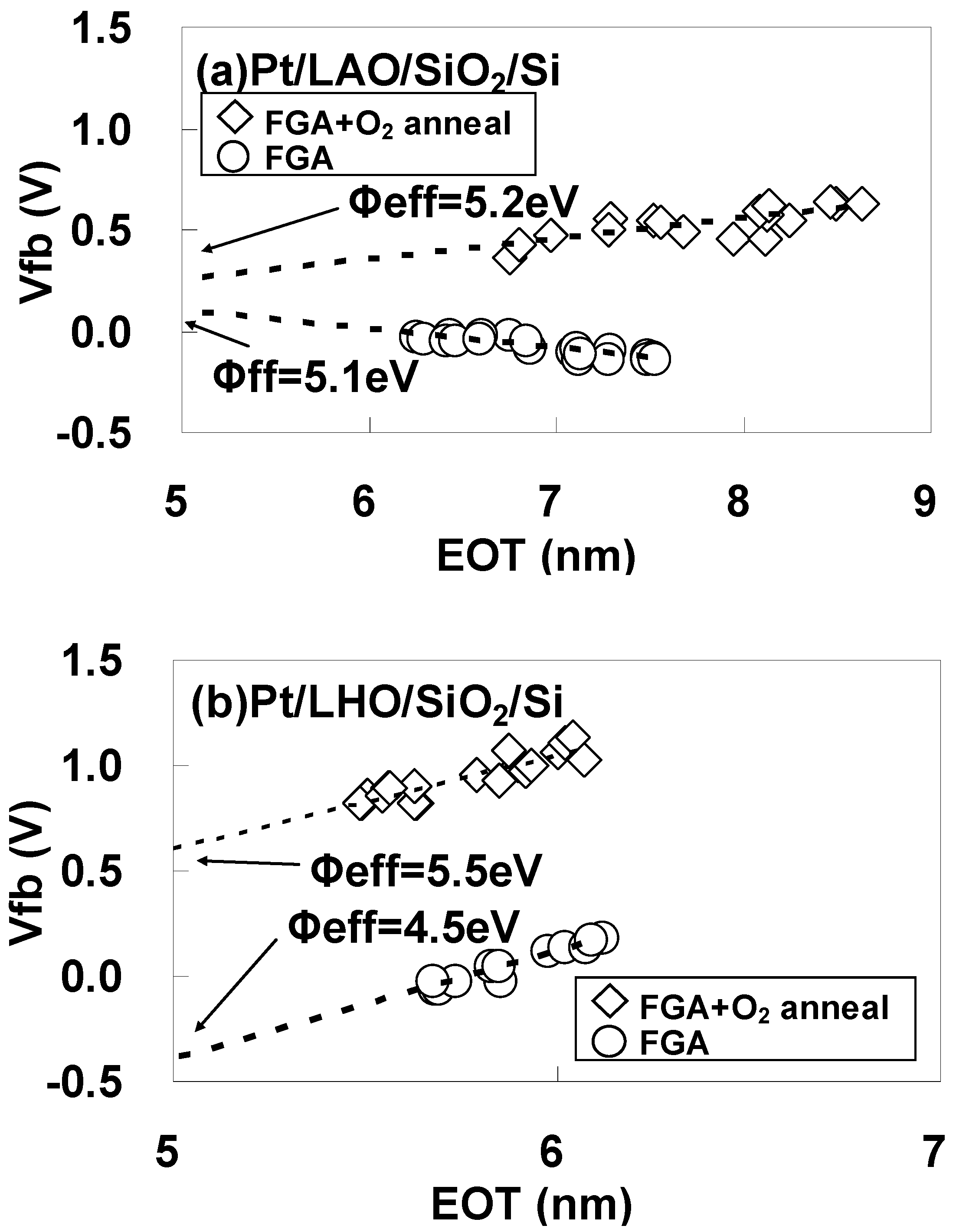

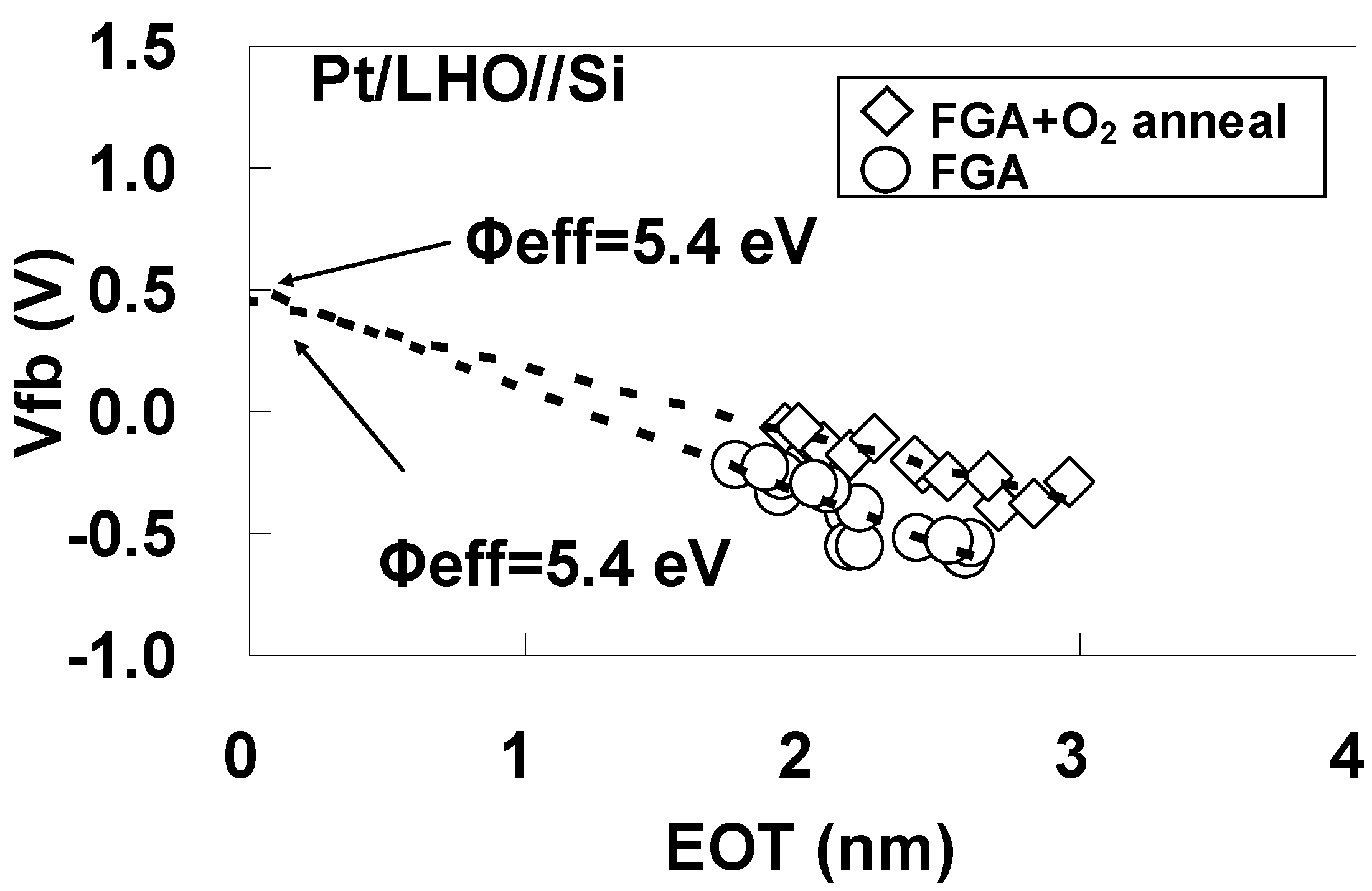

To estimate φeff accurately, the dependence of Vfb on EOT was obtained after FGA only and after additional O

2 annealing for (a) Pt/LAO/SiO

2/Si and (b) Pt/LHO/SiO

2/Si MOS capacitors as shown in

Figure 22. The estimated φeff values are also shown in the figures. As can be seen, the φeff behavior differs for these two kinds of stacks. In

Figure 22(a), it can be seen that the Pt/LAO/SiO

2/Si stack has a relatively high φeff, close to the vacuum work function of Pt (5.6 eV), even after FGA, and the φeff increase caused by the additional O

2 annealing is small. However, the behavior for the Pt/LHO/SiO

2/Si stack is quite different, as can be seen in

Figure 22(b). The φeff for the Pt/LHO/SiO

2/Si stack after FGA is as low as 4.5 eV, which is much lower than the values for the Pt/LAO/SiO

2/Si stack and the vacuum work function of Pt. Thus, the lowering of φeff in the LHO/SiO

2/Si stack by the FGA process, which was reported in reference [

31], was confirmed. It was, however, newly found that additional O

2 annealing enables recovery of φeff to a value close to the vacuum work function of Pt, as can be seen in

Figure 22(b). This anomalous behavior of φeff in the LHO/SiO

2/Si stack is thought to be caused by differences in the dipole contribution to φeff depending on the annealing ambient. The origin and locations of these dipoles are discussed below.

Figure 22.

Dependence of Vfb on EOT after FGA only and after additional O2 annealing for (a) Pt/LAO/SiO2/Si and (b) Pt/LHO/SiO2/Si MOS capacitors. φeff was estimated from the point of intersection of the EOT = 5 nm vertical line with the extrapolated experimental data by assuming that a fixed charge was responsible for the local slope of the plot at the interface between the 5-nm SiO2 layer and LAO or LHO. This assumption is based on the experimental result that the dependence of Vfb on the SiO2 thickness was small for Pt/SiO2/Si capacitors (data not shown).

Figure 22.

Dependence of Vfb on EOT after FGA only and after additional O2 annealing for (a) Pt/LAO/SiO2/Si and (b) Pt/LHO/SiO2/Si MOS capacitors. φeff was estimated from the point of intersection of the EOT = 5 nm vertical line with the extrapolated experimental data by assuming that a fixed charge was responsible for the local slope of the plot at the interface between the 5-nm SiO2 layer and LAO or LHO. This assumption is based on the experimental result that the dependence of Vfb on the SiO2 thickness was small for Pt/SiO2/Si capacitors (data not shown).

4.2. Physical Origin of the Annealing-Ambient-Dependence of φeff for the Pt/LHO/SiO2/Si Stack

The oxygen atoms themselves and the thermal process during O

2 annealing could both be possible contributing factors to the dramatic recovery of φeff seen in

Figure 22(b) as a result of additional O

2 annealing. In order to distinguish between these two factors, additional N

2 annealing and additional Ar annealing were performed instead of additional O

2 annealing for Pt/LHO/SiO

2/Si MOS capacitors under the same temperature and time conditions as for O

2 annealing (450 °C, 30 min).

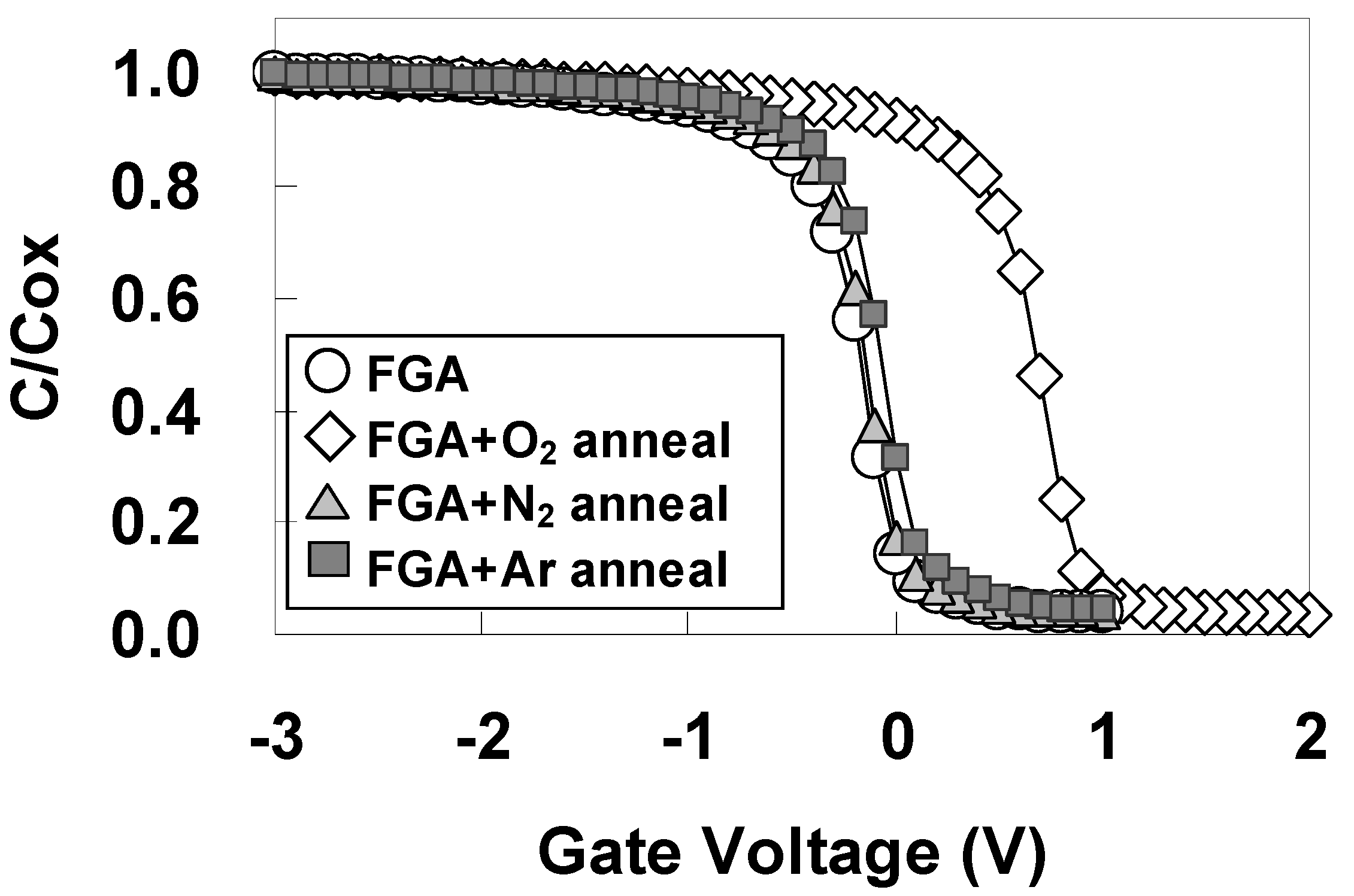

Figure 23 shows the C-V curves for the highest capacitances (as a typical example) after additional N

2 and Ar annealing for Pt/LHO/SiO

2/Si MOS capacitor, with the curves after FGA only and after additional O

2 annealing shown again for comparison. As can be seen in

Figure 23, in contrast to the case of additional O

2 annealing, neither additional N

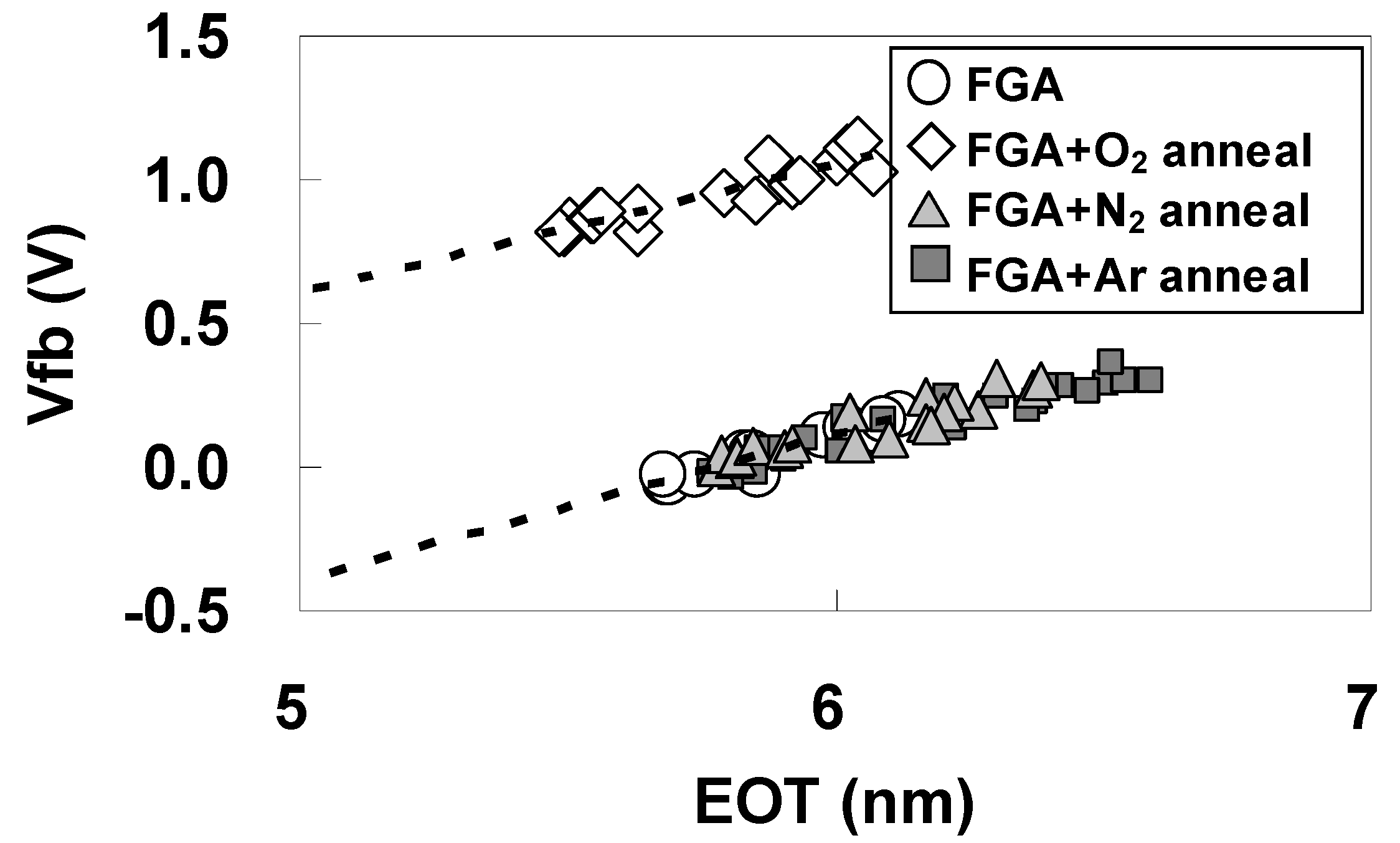

2 annealing nor additional Ar annealing has much effect on the C-V characteristics, including Vfb. The EOT dependences of Vfb after additional N

2 annealing and additional Ar annealing for Pt/LHO/SiO

2/Si MOS capacitors are also similar to that after FGA only as can be seen in

Figure 24, indicating that φeff is not affected by either N

2 annealing or Ar annealing. Thus, the thermal process itself does not affect φeff. These results indicate that oxygen-vacancy-related dipoles caused by FGA are responsible for lowering of φeff, and oxygen annealing inactivates these dipoles through re-oxidation.

Figure 23.

C-V curves for the highest capacitances after additional N2 and Ar annealing. The curves after only FGA and after additional O2 annealing are shown again for comparison.

Figure 23.

C-V curves for the highest capacitances after additional N2 and Ar annealing. The curves after only FGA and after additional O2 annealing are shown again for comparison.

Figure 24.

Dependence of Vfb on EOT after additional N2 and Ar annealing. The curves after only FGA and after additional O2 annealing are shown again for comparison.

Figure 24.

Dependence of Vfb on EOT after additional N2 and Ar annealing. The curves after only FGA and after additional O2 annealing are shown again for comparison.

It should be noted that while the φeff in the Pt/LHO/SiO

2/Si stack changes with additional O

2 annealing, the positive slopes of the EOT dependences of Vfb are unaffected by the variation in annealing ambient as can be seen in

Figure 22(b) and

Figure 24. Oxygen vacancies generally produce positive charges, resulting in a negative slope of the EOT dependences of Vfb. Considering this, it is thought that the positive slopes of the EOT dependences of Vfb are the result of the existence of large amounts of negative fixed charges in the Pt/LHO/SiO

2/Si stack, and that these negative charges are unaffected by the use of different annealing ambients. On the other hand, the positive charges produced by oxygen vacancies are unlikely to affect the slope, because they are thought to be negligible in comparison with negative fixed charges. Since this type of unstable φeff phenomenon was not observed in the Pt/LAO/SiO

2 stack, LAO is considered to be less susceptible to oxygen-vacancy formation than LHO.

Next, in order to determine the locations of the oxygen-vacancy-related dipoles in the Pt/LHO/SiO

2/Si stack, a stack without the SiO

2 interfacial layer (Pt/LHO/Si) was fabricated by LHO deposition on an HF-treated Si surface, and the same experiments as for the stack with the SiO

2 interfacial layer were performed.

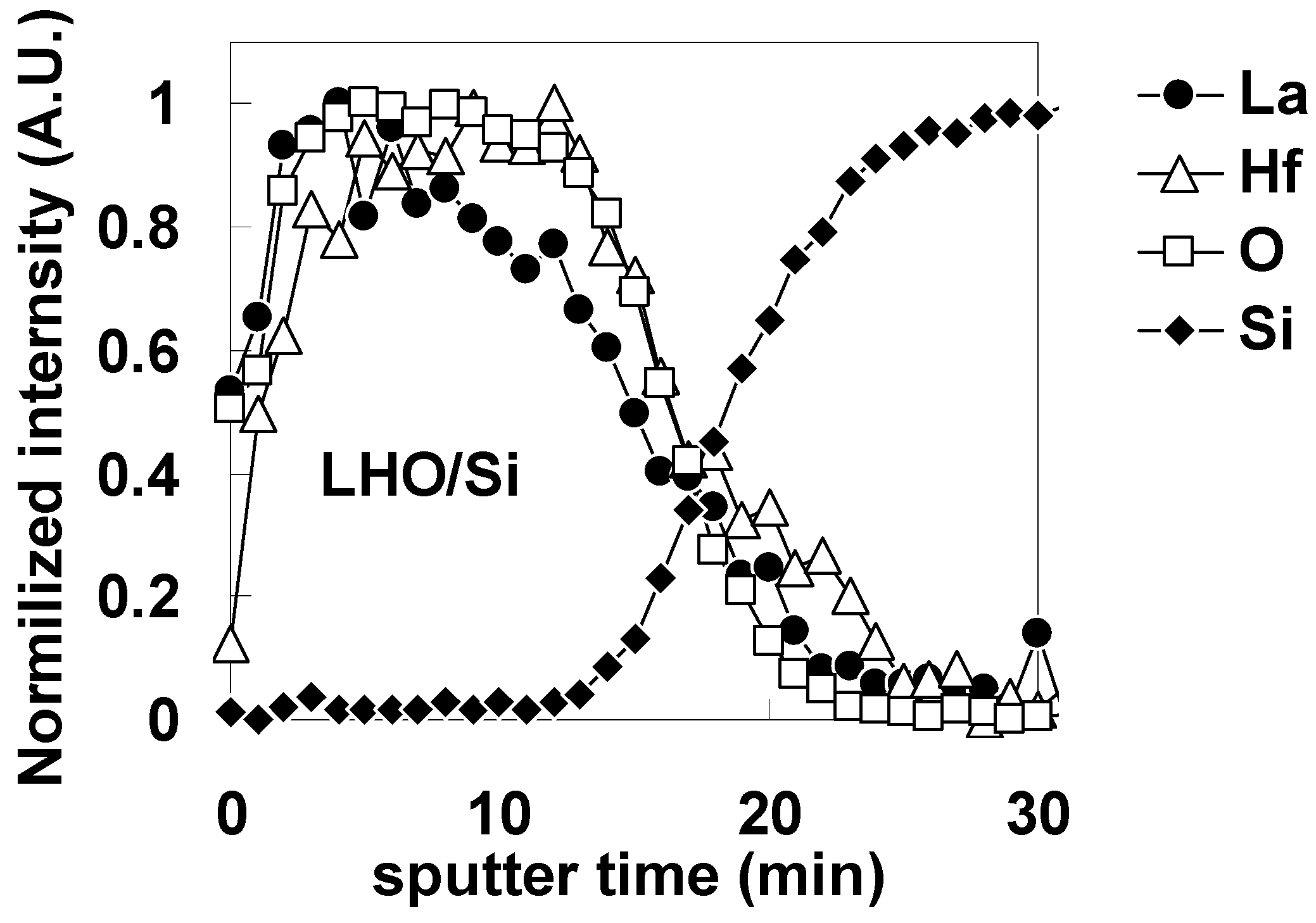

Figure 25 shows the AES depth profile for the LHO/Si stack. As can be seen in

Figure 25, a sharp LHO/Si interface was obtained. TFA revealed that the Si peak was composed of a single component, only Si metal (Si substrate), indicating a very thin (if any) interfacial layer in the stack.

Figure 25.

Auger electron spectroscopy (AES) depth profile for the LHO/Si stack. The vertical axis is normalized to show the sharpness of the interface more clearly.

Figure 25.

Auger electron spectroscopy (AES) depth profile for the LHO/Si stack. The vertical axis is normalized to show the sharpness of the interface more clearly.

Figure 26 shows the C-V curves for the highest capacitances (as a typical example) for Pt/LHO/Si MOS capacitors after FGA only and after additional O

2 annealing. In contrast to the result for the stack with the SiO

2 layer (

Figure 21(b)), the Vfb difference between these curves is small.

Figure 26.

C-V curves with the highest capacitances for Pt/LAO/Si MOS capacitors after FGA only and after additional O2 annealing.

Figure 26.

C-V curves with the highest capacitances for Pt/LAO/Si MOS capacitors after FGA only and after additional O2 annealing.

To estimate φeff accurately, the dependence of Vfb on EOT was obtained after FGA only and after additional O

2 annealing for Pt/LHO/Si MOS capacitors as shown in

Figure 27. The estimated φeff values are also shown in the figure. The φeff values after FGA only and after additional O

2 annealing were both 5.4 eV, which is close to the vacuum work function of Pt. This behavior is completely different from that of the stack with the SiO

2 layer (

Figure 22(b)).

Figure 27.

Dependence of Vfb on EOT for the specimens after FGA only and after additional O2 annealing. φeff was estimated from the point of intersection of the Y axis with the extrapolated experimental data by assuming that a fixed charge was responsible for the local slope of the plot at the interface between LHO and the Si substrate.

Figure 27.

Dependence of Vfb on EOT for the specimens after FGA only and after additional O2 annealing. φeff was estimated from the point of intersection of the Y axis with the extrapolated experimental data by assuming that a fixed charge was responsible for the local slope of the plot at the interface between LHO and the Si substrate.

The above results indicate that the LHO/Si and Pt/LHO interfaces do not include the oxygen-vacancy-related dipoles that are thought to be responsible for lowering φeff. Based on these findings, it can be concluded that the oxygen-vacancy-related dipoles observed in the Pt/LHO/SiO2/Si stack are located at the LHO/SiO2 interface. In addition, considering the φeff stability of LAO mentioned above, it is likely that the oxygen-vacancy-related dipoles observed in the Pt/LHO/SiO2/Si stack are caused by Hf atoms. Also, the reported φeff instability of Hf-based high-k materials, in which oxygen vacancies probably form as a result of FGA or high-temperature annealing at around 1000 °C, may have the same mechanism as that observed in the Pt/LHO/SiO2/Si stack in this study.

5. Impact of the Lanthanum Aluminate Composition on Vfb

In this section, the variation of the flat-band voltage (Vfb) behavior with the La/(La+Al) atomic ratio will be examined and the proposed guidelines for achieving a dual high-

k gate stack structure using an La-Al-O dielectric system will be discussed. La oxide and Al oxide are promising materials for threshold voltage (Vth) tuning in high-

k gate dielectrics [

32,

33,

34]. Therefore, an La-Al-O ternary oxide system is considered to consist of materials applicable to a range of LSI process technologies now. However, the impacts of the La-Al-O composition on Vfb have not yet been investigated. We therefore carefully investigated the flat-band voltage (Vfb) behavior as a function of the La/(La+Al) atomic ratio [

35].

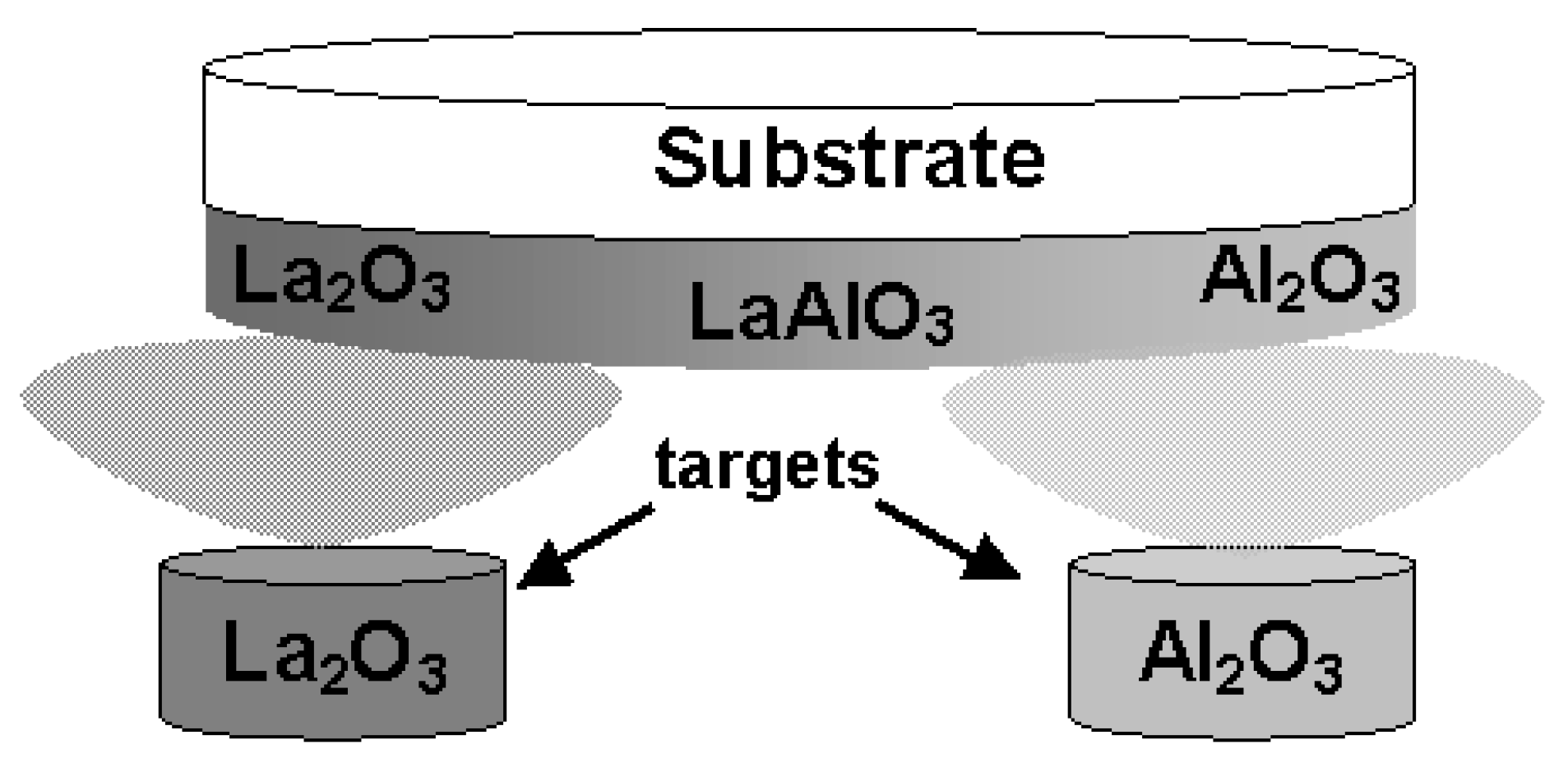

La-Al-O gate dielectric films were deposited on HF-treated p-Si(100) wafers at 600 °C by PLD. Sintered pellets of La

2O

3 and Al

2O

3 were used as deposition targets. These targets were set above each wafer edge as illustrated in

Figure 28 in order to deposit a film whose composition changes gradually with position along a diameter of the wafer. In addition, film thickness also changed keeping constant La/(La + Al) along the direction perpendicular to the direction changing La/(La+Al).

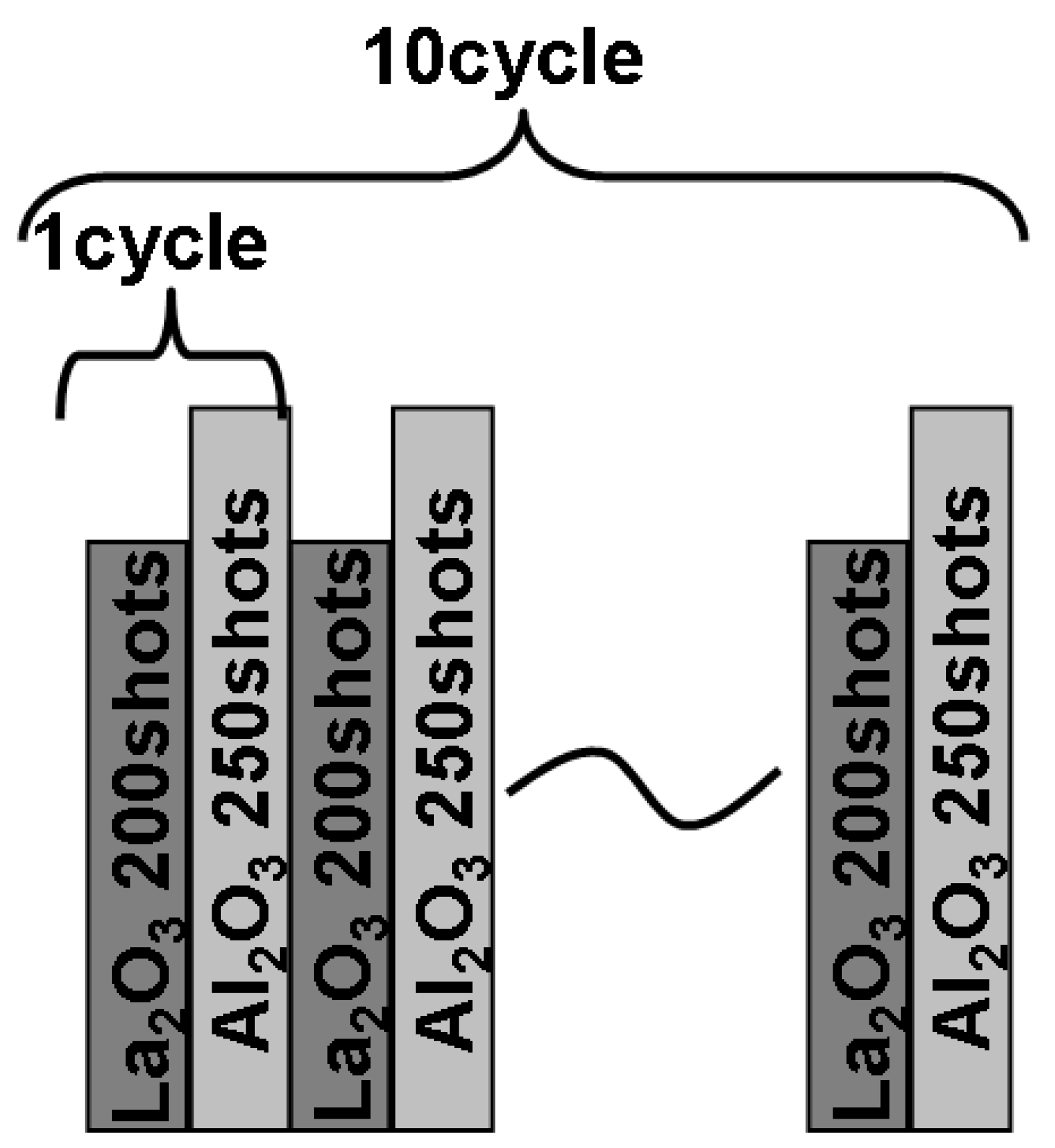

Figure 29 shows the laser irradiation sequence. Ten cycles of alternate laser irradiation (300 mJ, 10 Hz) were performed for the La

2O

3 and Al

2O

3 targets to achieve a uniform composition in the depth direction. Each cycle consisted of 200 shots for the La

2O

3 target and 250 shots for the Al

2O

3 target.

Figure 28.

Schematic diagram of the positional relationships between the targets and substrate.

Figure 28.

Schematic diagram of the positional relationships between the targets and substrate.

Figure 29.

Laser irradiation sequence.

Figure 29.

Laser irradiation sequence.

To estimate the atomic ratio of La/(La+Al) at different positions on the wafer, AES measurements were performed along the diameter of the wafer. After the fabrication of capacitors with Mo gates, forming gas (H

2/N

2 = 0.03) annealing was performed at 450 °C for 30 min. An Mo/SiO

2/Si gate stack capacitor was prepared as a reference. Gate dielectric stacks in which La-Al-O film was deposited on a 5-nm-thick (nominal thickness) thermal oxide (SiO

2) interfacial layer were also fabricated to examine the contribution of the SiO

2 interfacial layer to the Vfb shift [

34]. In order to clarify the mechanism of the Vfb shift caused by the difference in composition, X-ray photoelectron spectroscopy (XPS) measurements were performed.

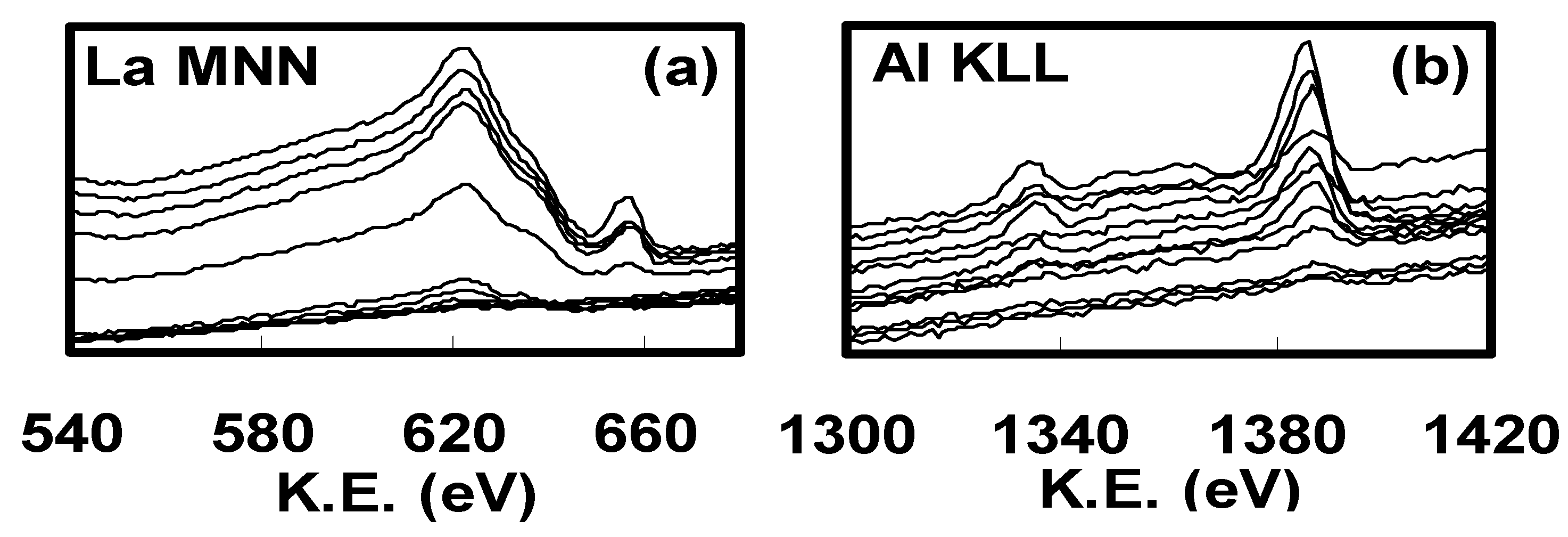

Figure 30 shows the AES spectra of (a) La MNN and (b) Al KLL along the wafer diameter for the specimen without the underlying 5-nm SiO

2 interfacial layer.

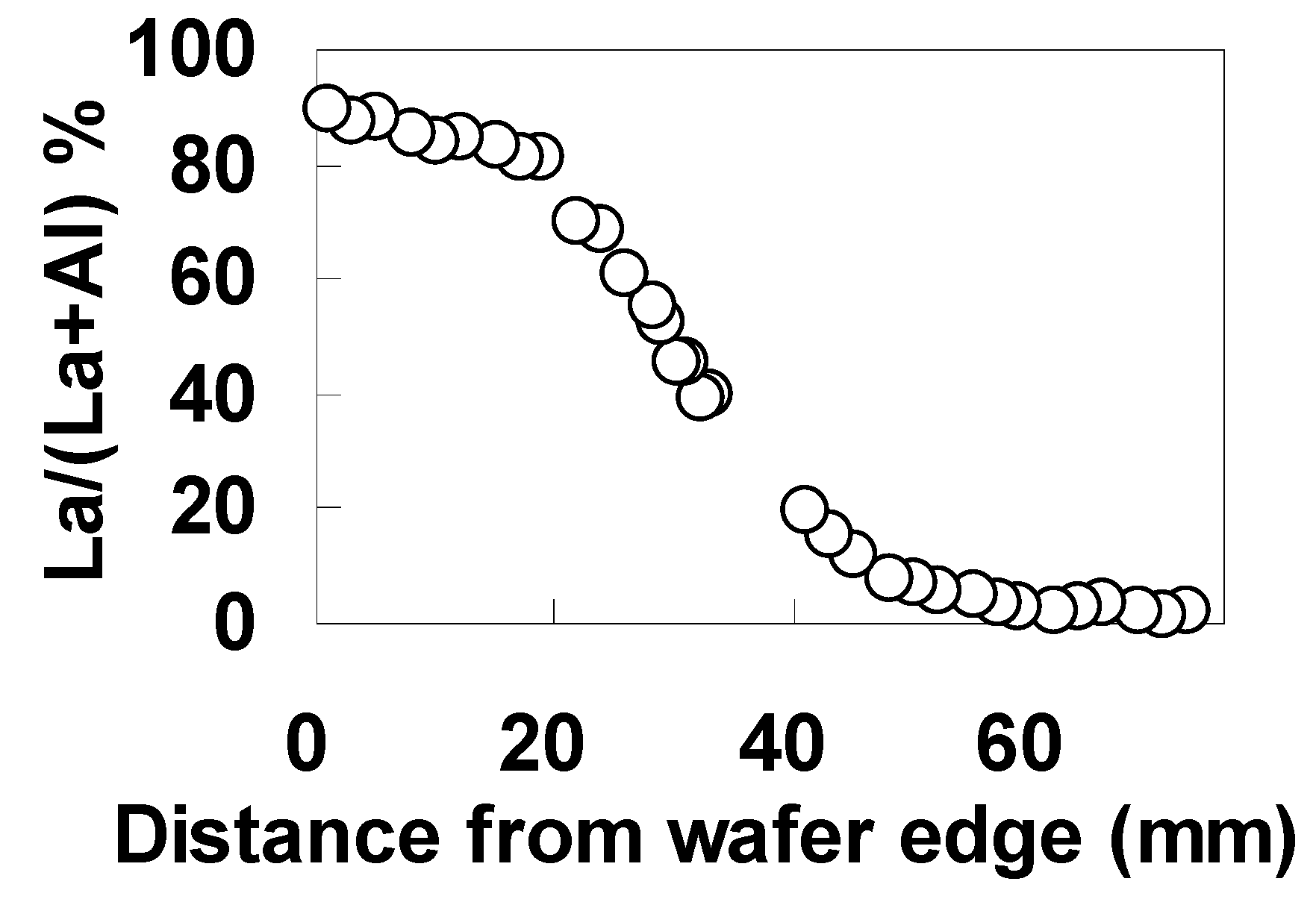

Figure 31 shows the dependence of La/(La+Al) on the position on the wafer estimated from the intensities of AES spectra shown in

Figure 30. Here, the atomic ratio was corrected using a standard specimen with La:Al:O = 1:1:3. As can be seen in

Figure 31, the ratio of La/(La+Al) changed gradually along the diameter of the wafer, from 90% to close to 2%. Similar results to those in

Figure 31 were also obtained for the specimen with the underlying 5-nm SiO

2 layer.

Figure 30.

AES spectra along the diameter of the wafer for (a) La MNN and (b) Al KLL.

Figure 30.

AES spectra along the diameter of the wafer for (a) La MNN and (b) Al KLL.

Figure 31.

Dependence of La/(La+Al) on the position on the wafer.

Figure 31.

Dependence of La/(La+Al) on the position on the wafer.

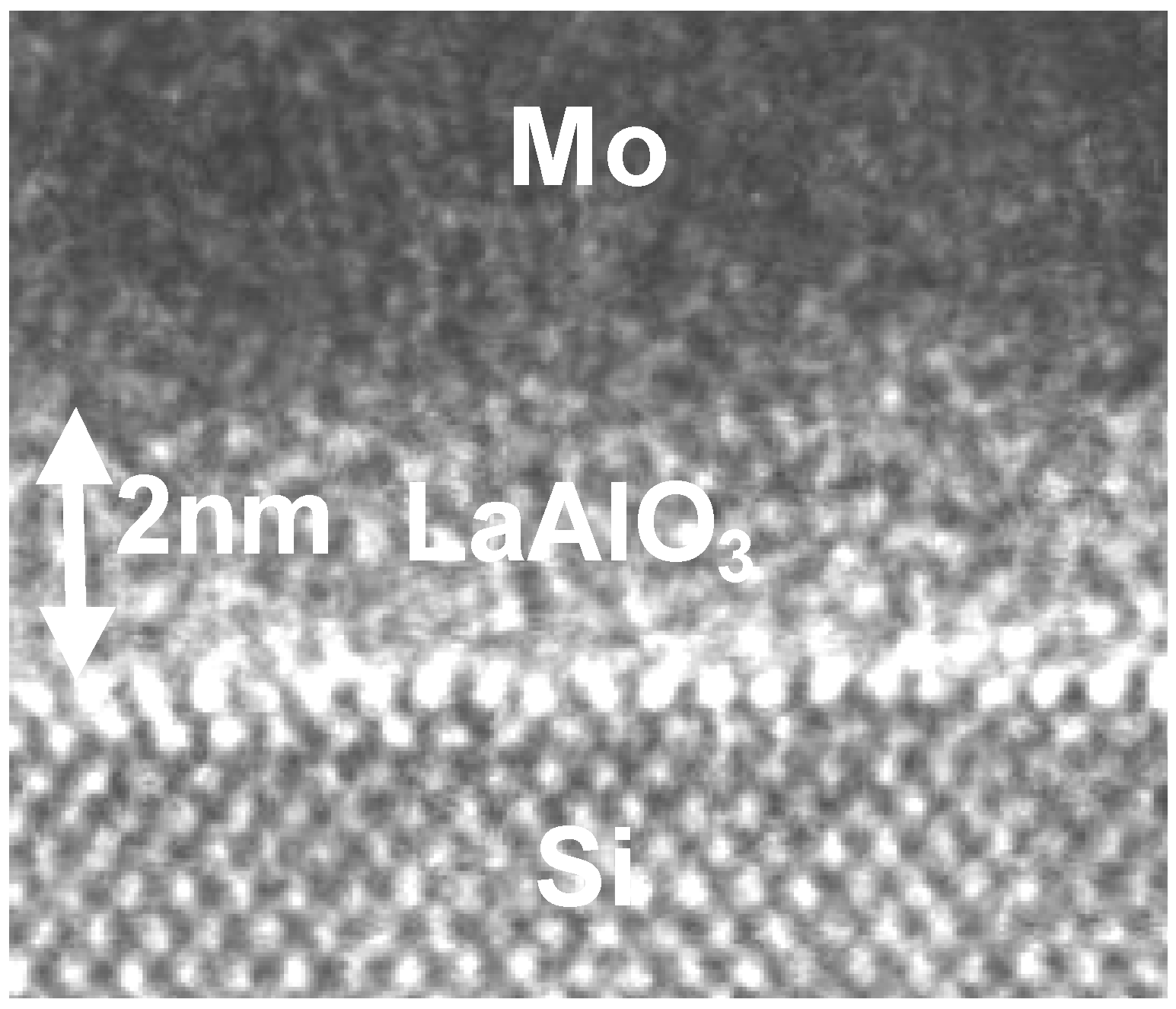

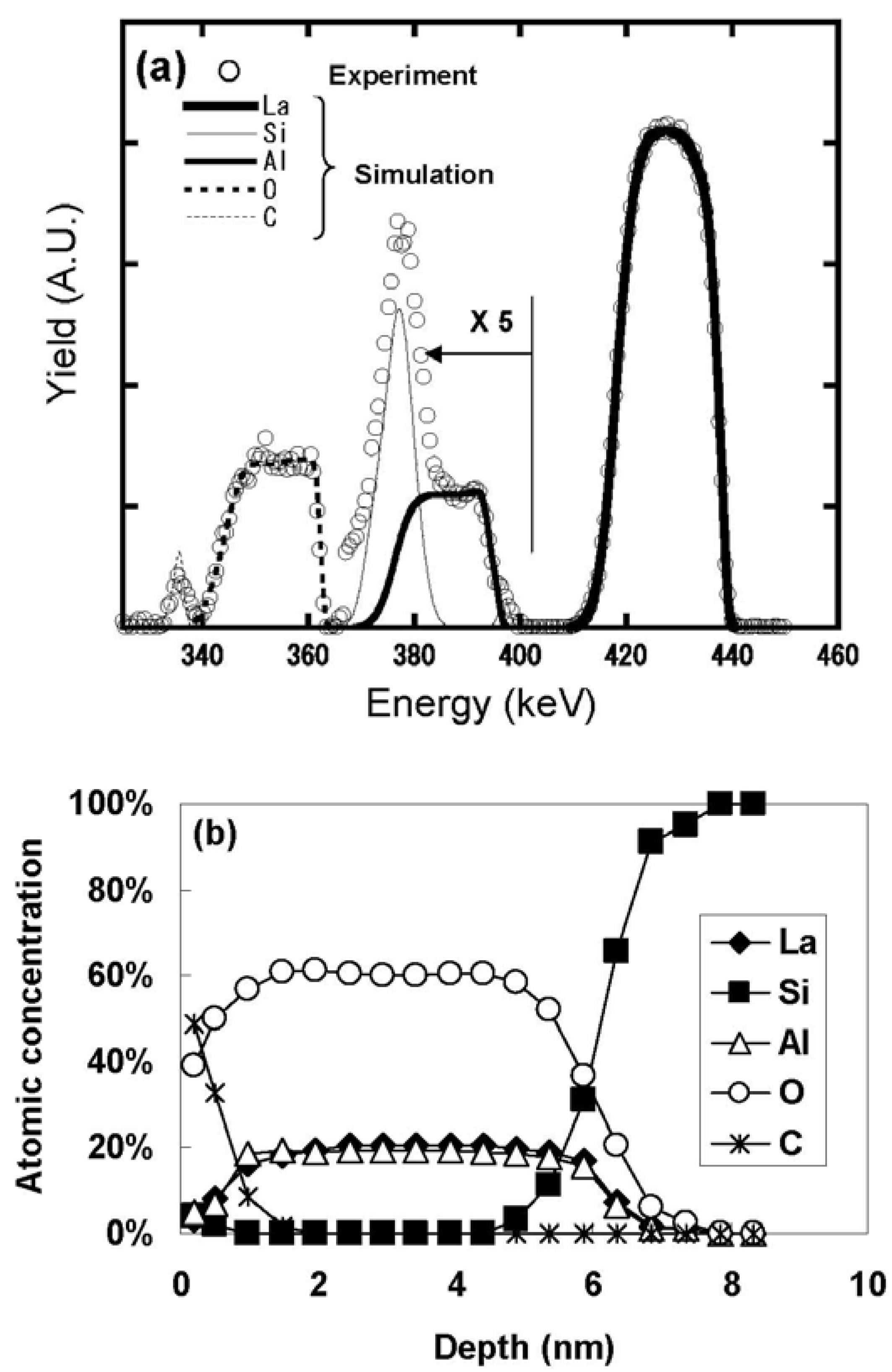

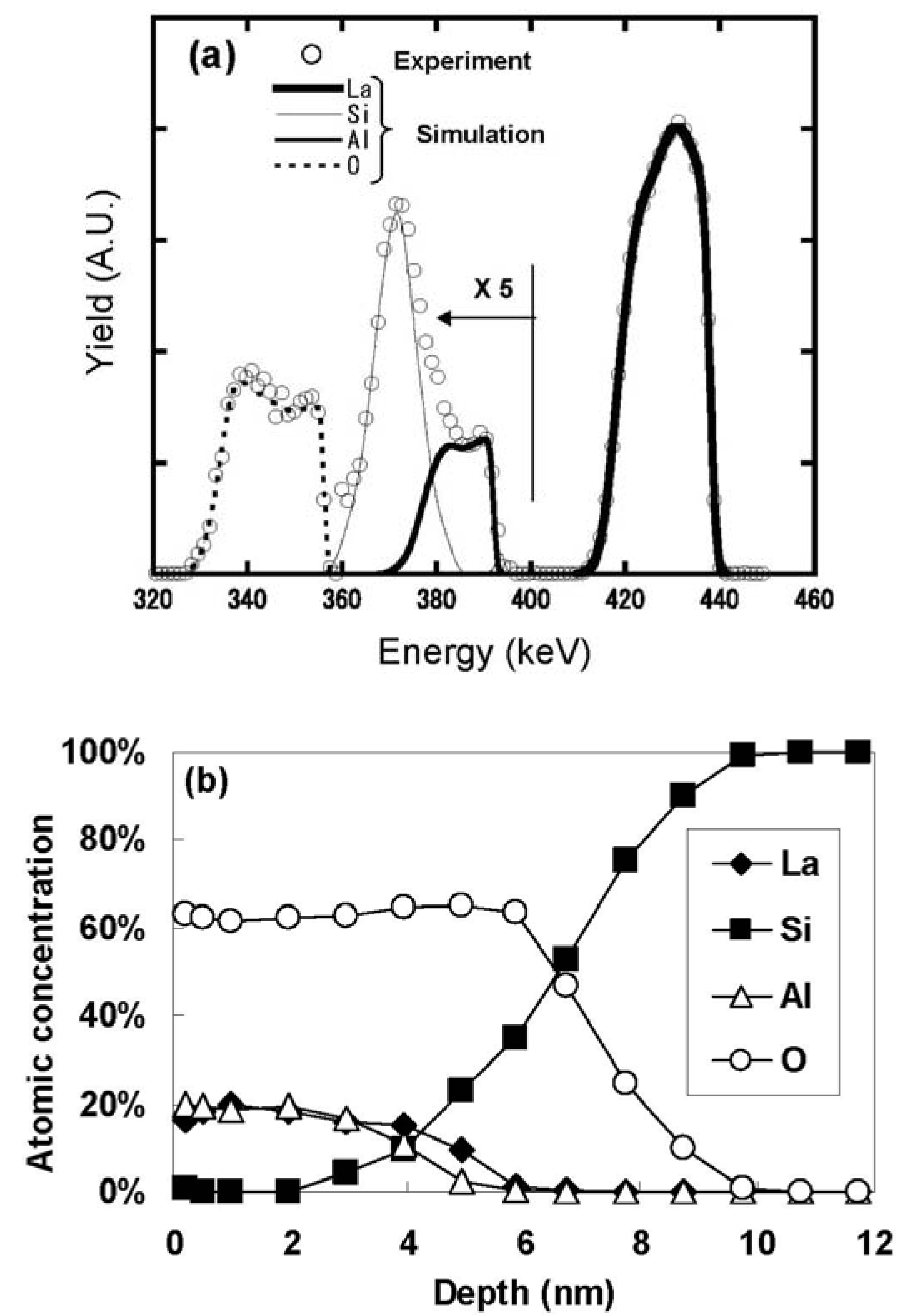

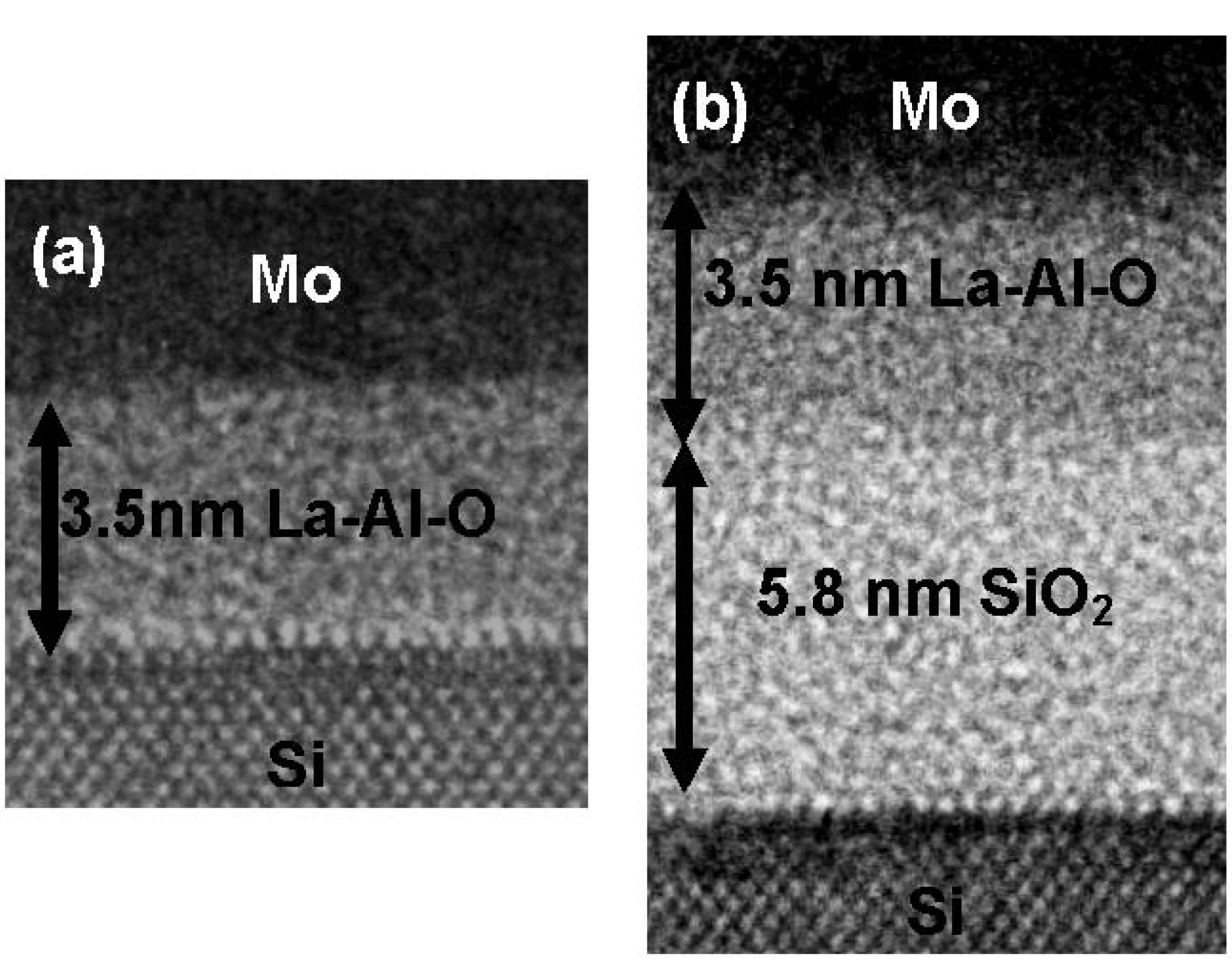

Figure 32 shows TEM images for (a) Mo/La-Al-O/Si and (b) Mo/La-Al-O/SiO

2/Si gate stacks in which La/(La+Al) = 50%. The thicknesses of the La-Al-O films ((a) and (b)) and the SiO

2 layer (b) are shown in the images. The only difference between these images is the existence of the SiO

2 layer between the La-Al-O film and the Si substrate in

Figure 32(b). The contrast of the La-Al-O films is uniform in both cases, indicating that the alternately deposited ultrathin La

2O

3 layers and Al

2O

3 layers were well-mixed with each other during the deposition process at 600 °C.

Figure 32.

TEM images for (a) Mo/La-Al-O/Si and (b) Mo/La-Al-O/SiO2/Si gate stacks with La/(La+Al) = 50%.

Figure 32.

TEM images for (a) Mo/La-Al-O/Si and (b) Mo/La-Al-O/SiO2/Si gate stacks with La/(La+Al) = 50%.

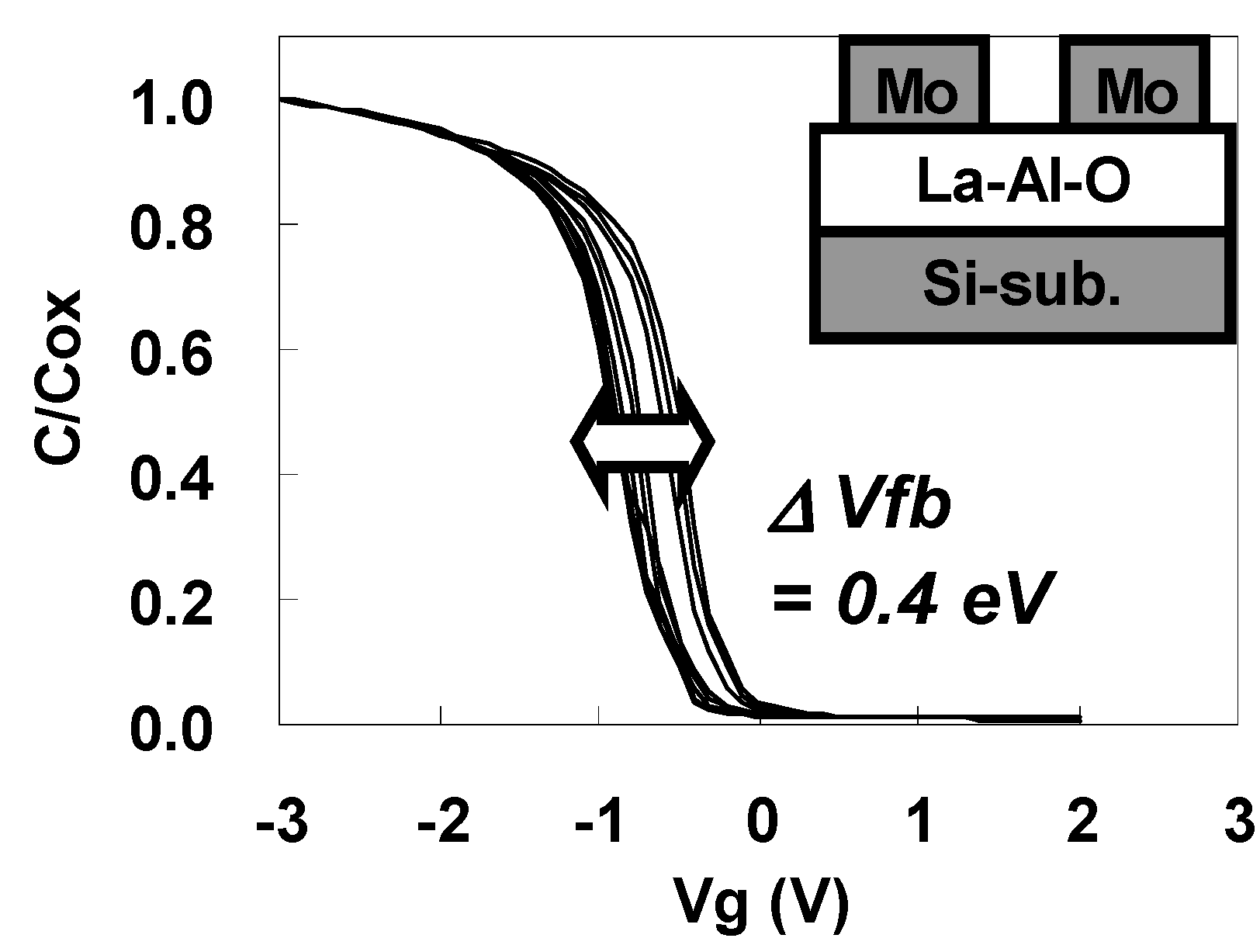

Figure 33 shows the C-V curves for the Mo/La-Al-O/Si gate stack capacitors taken along the wafer diameter over which the composition was changed. Vfb is shifted in the positive direction as La/(La+Al) decreases and in the negative direction as La/(La+Al) increases. The maximum difference of Vfb (ΔVfb) between the obtained C-V curves shown in

Figure 6 was 0.4 eV.

Figure 33.

C-V curves for Mo/La-Al-O/Si gate stack capacitors along the wafer diameter over which the composition was changed.

Figure 33.

C-V curves for Mo/La-Al-O/Si gate stack capacitors along the wafer diameter over which the composition was changed.

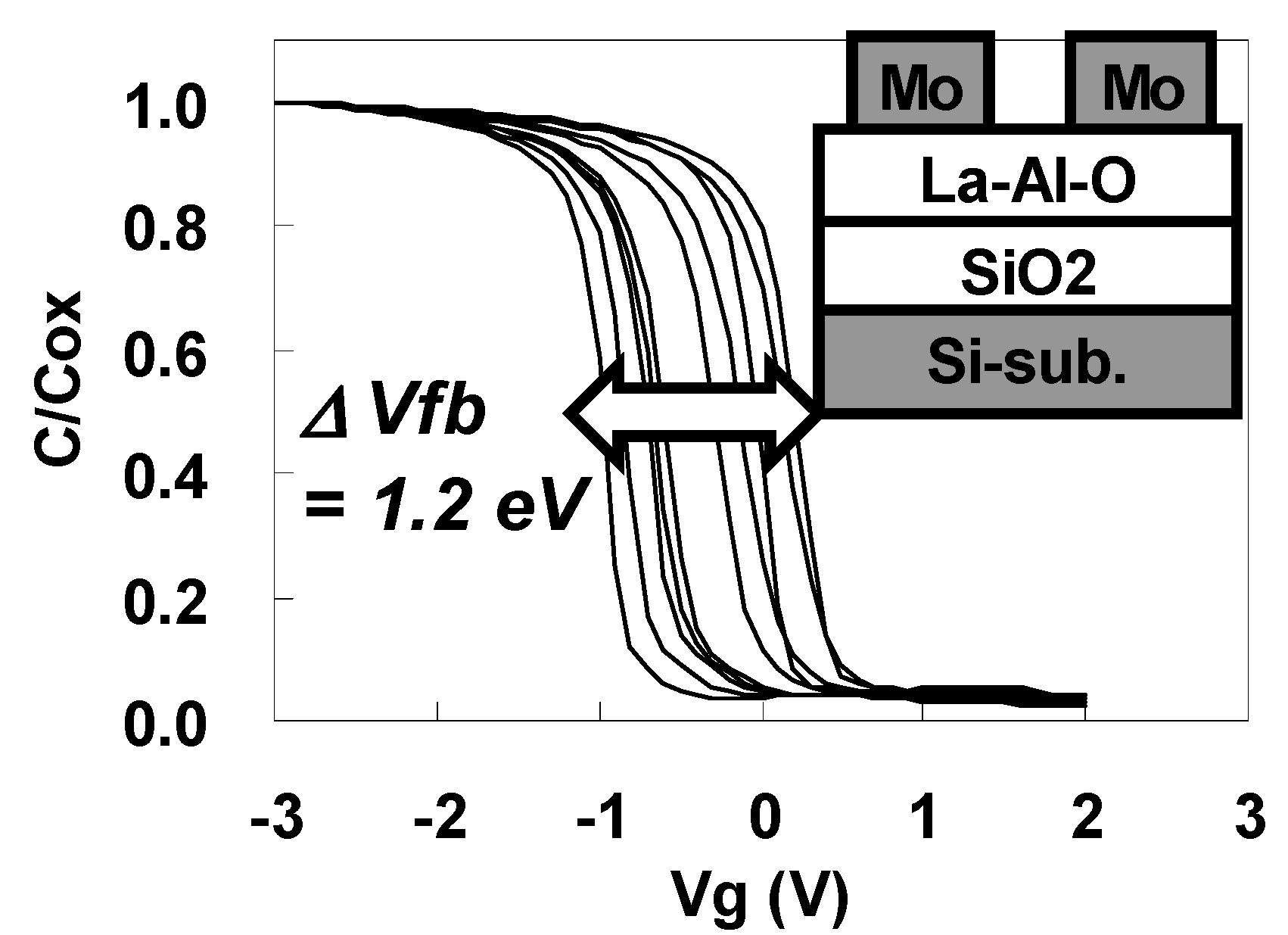

Figure 34 shows the C-V curves for the Mo/La-Al-O/SiO

2/Si gate stack capacitors taken along the wafer diameter over which the composition was changed. As can be seen by comparing

Figure 33 and

Figure 34, insertion of the SiO

2 changes the Vfb behavior dramatically. A large ΔVfb of 1.2 eV, greater than the bandgap energy of Si (1.12 eV), was observed for Mo/La-Al-O/SiO

2/Si stacks. These results suggest that the La-Al-O/SiO

2 interface makes a strong contribution to the Vfb shift.

Figure 34.

C-V curves for Mo/La-Al-O/SiO2/Si gate stack capacitors along the wafer diameter over which the composition was changed.

Figure 34.

C-V curves for Mo/La-Al-O/SiO2/Si gate stack capacitors along the wafer diameter over which the composition was changed.

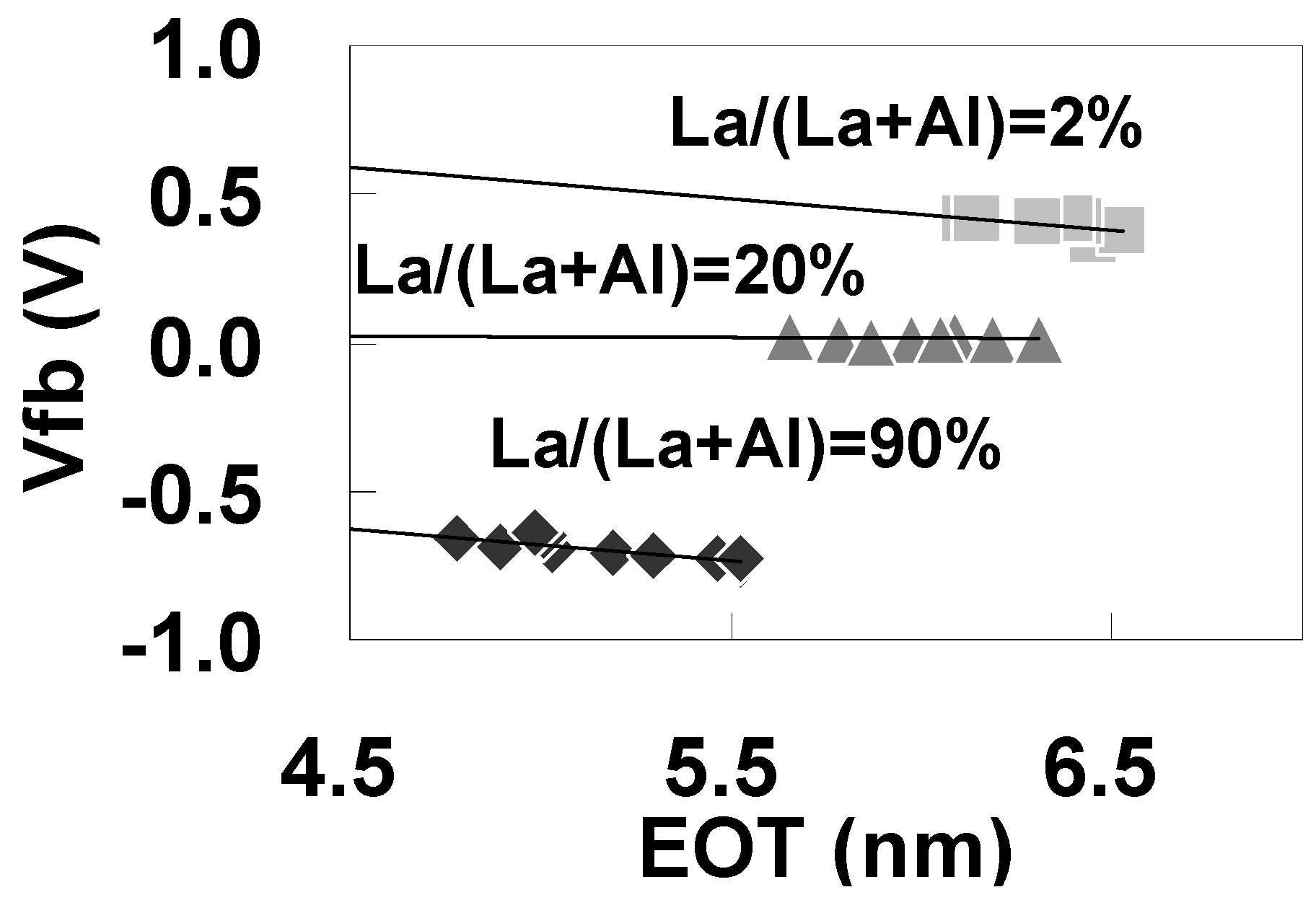

It is well known that Vfb is affected by interfacial dipoles and fixed charges. To identify the factors causing the Vfb shift, the dependence of Vfb on the La-Al-O film thickness was investigated.

Figure 35 shows the dependence of Vfb on EOT for Mo/La-Al-O/SiO

2/Si stacks with La/(La+Al) = 2%, 20%, and 90%. No significant difference in the slopes is seen in

Figure 35 for the different La/(La+Al) values, suggesting that there is no contribution of the fixed charges in the stacks to the change in Vfb with La/(La+Al). Thus, it can be concluded that dipoles at the La-Al-O/SiO

2 interface are mainly responsible for the large ΔVfb observed in

Figure 34. A similar relationship between EOT and Vfb was also observed for the Mo/La-Al-O/Si stacks.

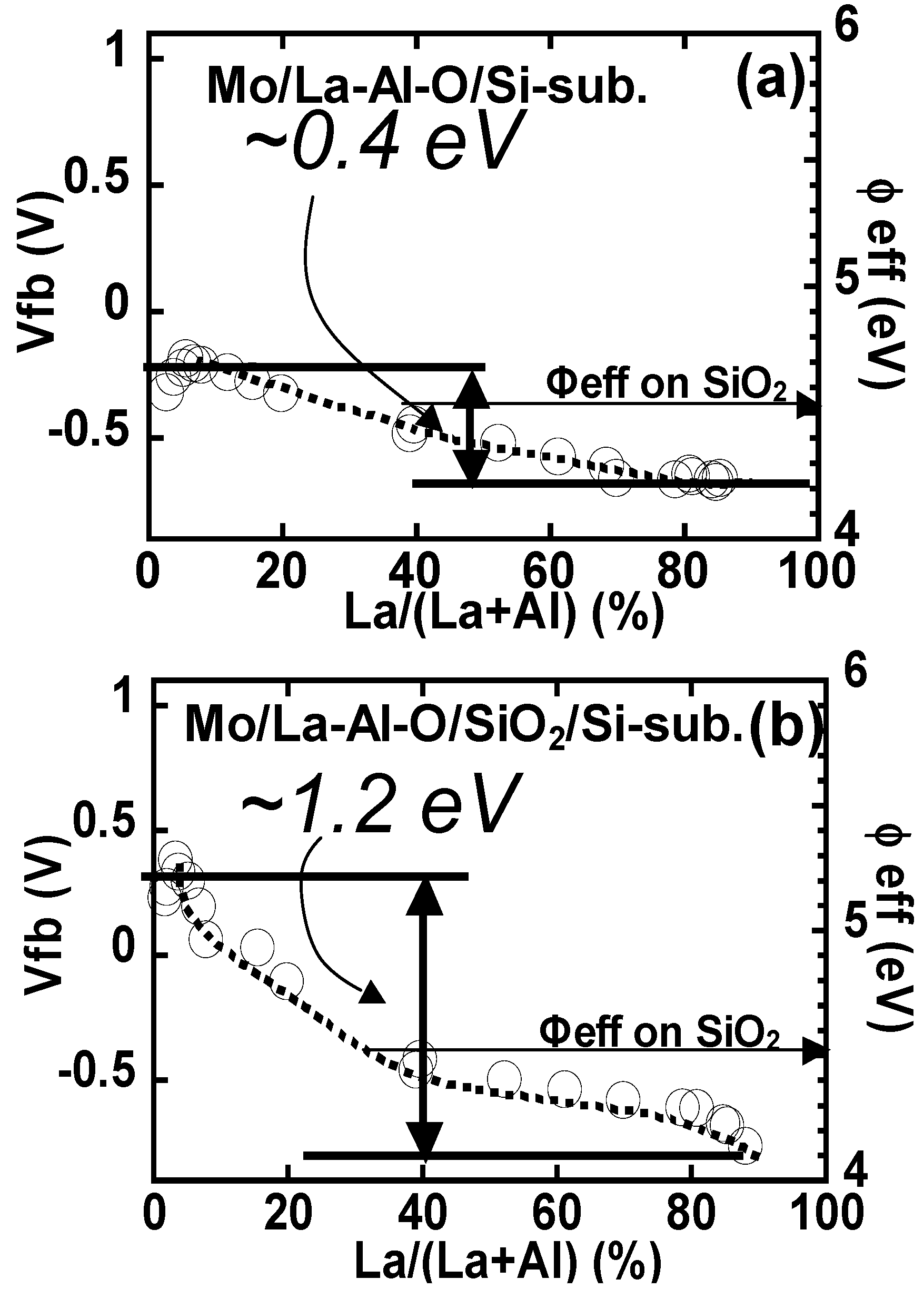

Figure 36 shows the plots of Vfb and the effective work function (φeff) as functions of La/(La+Al) for (a) Mo/La-Al-O/Si and (b) Mo/La-Al-O/SiO

2/Si gate stack capacitors. The same φeff as for the reference SiO

2 film (4.54 eV; approximately equal to the intrinsic value) was obtained when La/(La+Al) was approximately 30%. This result suggests that interfacial dipoles with opposite orientations (due to the La and Al atoms) coexist at the La-Al-O/SiO

2 interface, and the effects of these dipoles on Vfb cancel each other at an La/(La+Al) of approximately 30%. The dependence of Vfb on La/(La+Al) becomes weak above 30%, indicating that in La-Al-O systems it may be possible to use a wide La/(La+Al) range for Vth tuning of n-MISFETs.

Figure 35.

Dependence of Vfb on EOT for Mo/La-Al-O/SiO2/Si stacks with La/(La+Al) = 2%, 20%, and 90%. C-V measurements were performed in the direction perpendicular to the direction of La/(La+Al) variation.

Figure 35.

Dependence of Vfb on EOT for Mo/La-Al-O/SiO2/Si stacks with La/(La+Al) = 2%, 20%, and 90%. C-V measurements were performed in the direction perpendicular to the direction of La/(La+Al) variation.

Figure 36.

Plots of Vfb and φeff as functions of La/(La+Al) for (a) Mo/La-Al-O/Si and (b) Mo/La-Al-O/SiO2/Si gate stack capacitors.

Figure 36.

Plots of Vfb and φeff as functions of La/(La+Al) for (a) Mo/La-Al-O/Si and (b) Mo/La-Al-O/SiO2/Si gate stack capacitors.

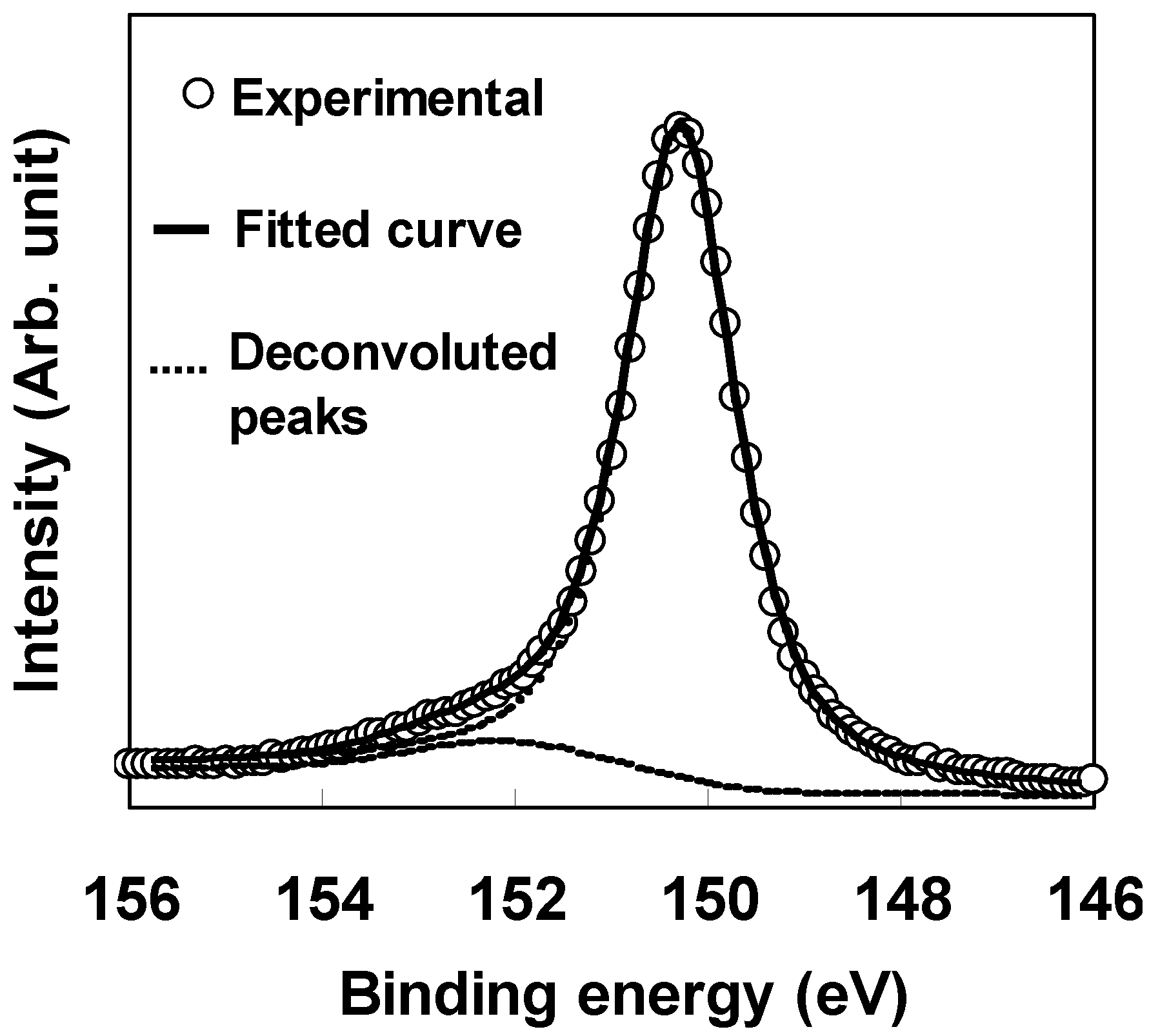

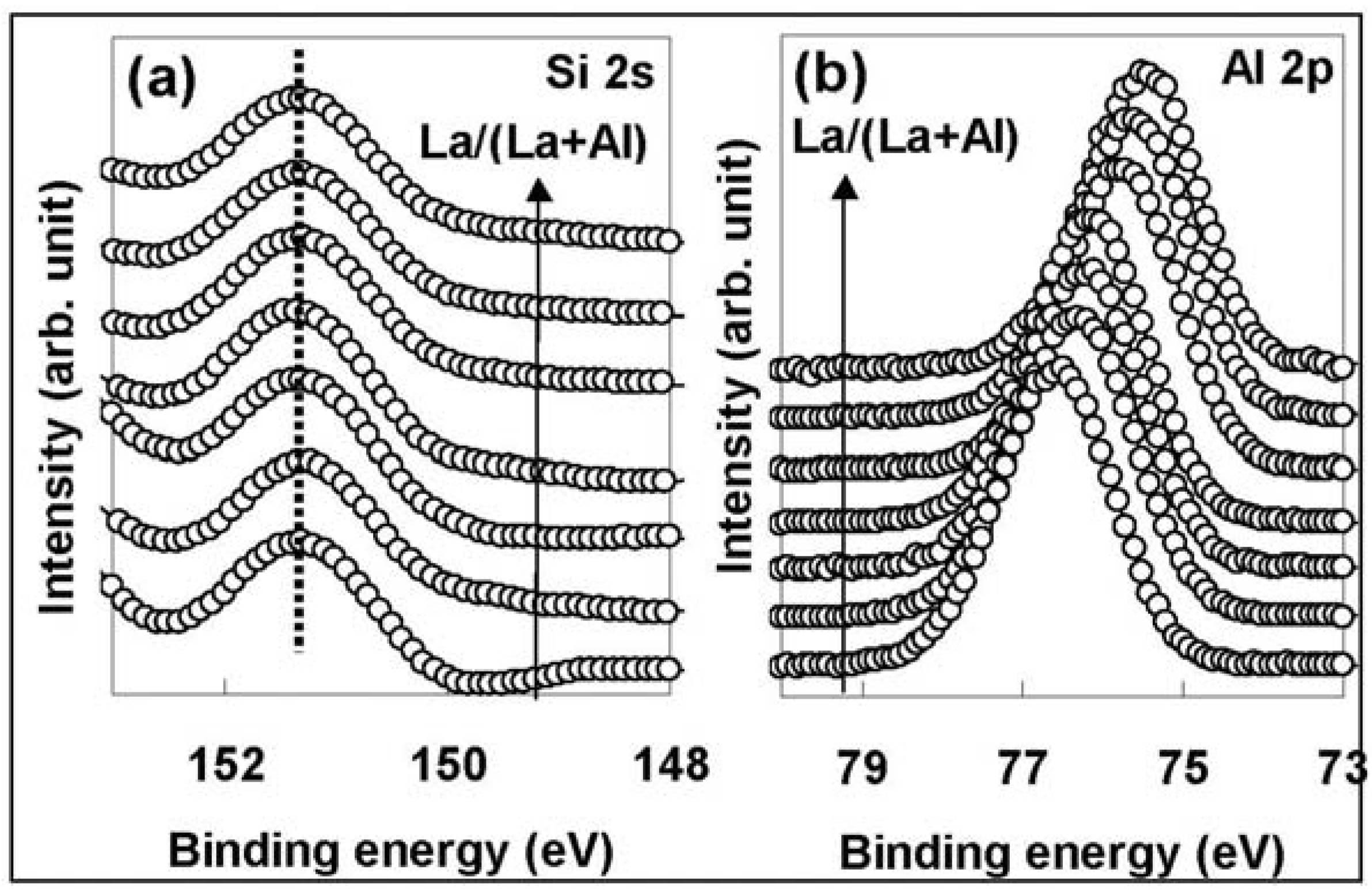

The contribution of the dipoles to the change in Vfb with La/(La+Al) was also clarified by the dependence of the energy band alignment between the La-Al-O film and the Si substrate on La/(La+Al), which was investigated by measuring the energy difference between Al 2p for the La-Al-O film and Si 2s for the Si substrate using XPS. The absence of peak shifts caused by variation of the X-ray irradiation time during the XPS measurements was confirmed.

Figure 37 shows the XPS spectra for (a) Si 2s from Si substrate and (b) Al 2p from La-Al-O film for La/(La+Al) values ranging from 2.8% to 75.4%, with the peak heights normalized to unity for comparison. As can seen in

Figure 37(b), there is a clear negative binding energy shift of Al 2p relative to Si 2s with the increase of La/(La+Al), indicating that the valence band offset (ΔEv) decreases with the increase of La/(La+Al).

Figure 37.

XPS spectra for (a) Si 2s from Si substrate and (b) Al 2p from La-Al-O film for La/(La+Al) values ranging from 2.8% to 75.4%.

Figure 37.

XPS spectra for (a) Si 2s from Si substrate and (b) Al 2p from La-Al-O film for La/(La+Al) values ranging from 2.8% to 75.4%.

On the other hand, with regard to the stack without the SiO

2 interfacial layer, a recent report indicates that the binding energy of Al 2p and ΔEv at the La-Al-O/Si interface show little dependence on La/(La+Al) at La/(La+Al) values of between 25% and 50% [

36]. Therefore, it can be concluded that the La/(La+Al)-dependent voltage drop between the La-Al-O film and Si substrate occurs because of insertion of the SiO

2 layer. This behavior is in good agreement with the dipole-induced Vfb shift mechanism referred to above.

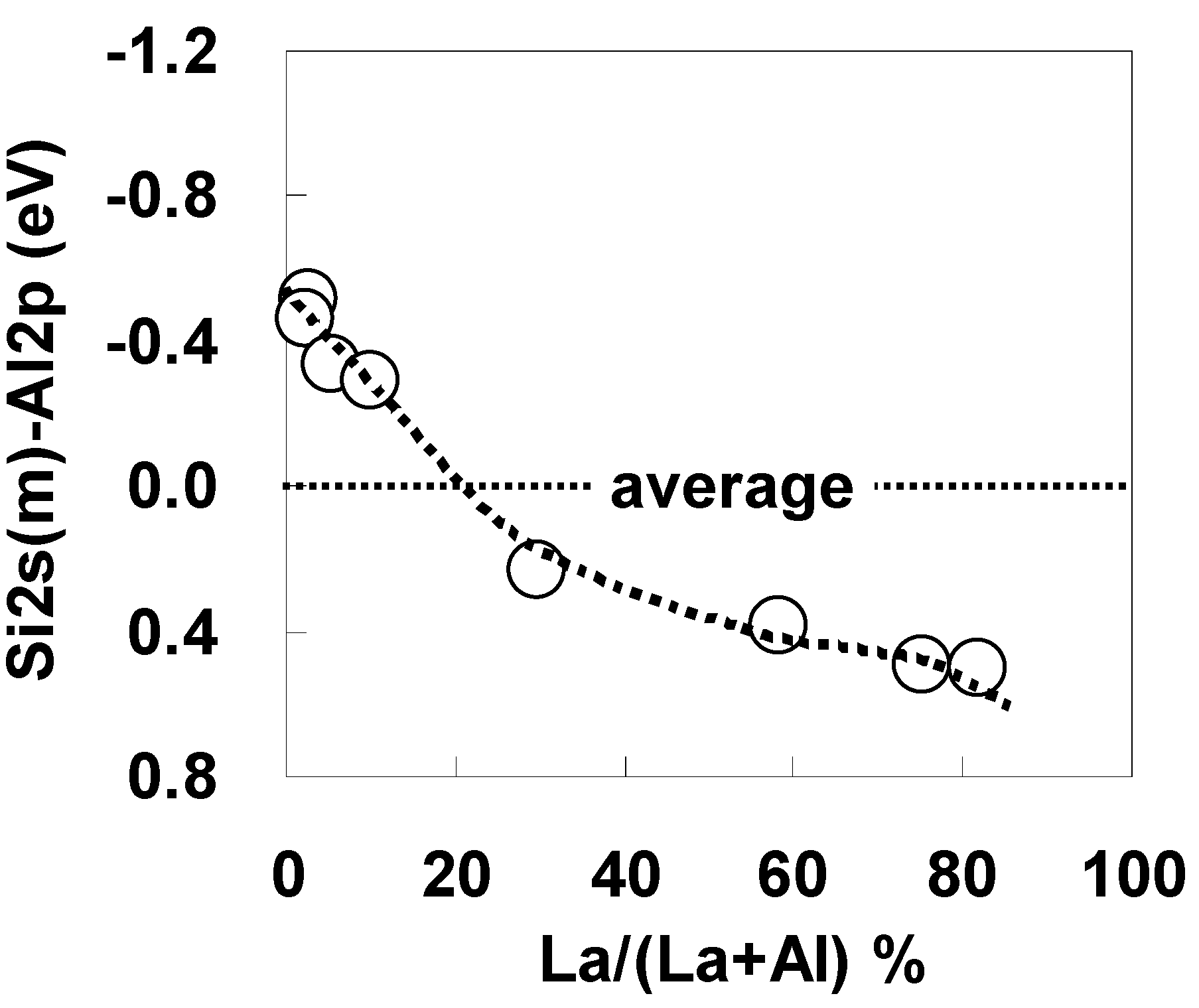

Figure 38 shows the La/(La+Al) dependence of the energy difference between Al 2p and Si 2s. Note that the vertical axis of the graph represents the energy difference as the divergence from the average value. The behavior shown in

Figure 38 is remarkably similar to that in

Figure 36(b). This agreement indicates that there is no influence of carrier trapping during the voltage sweep for C-V measurements on the Vfb shift and the existence of dipoles in the stack.

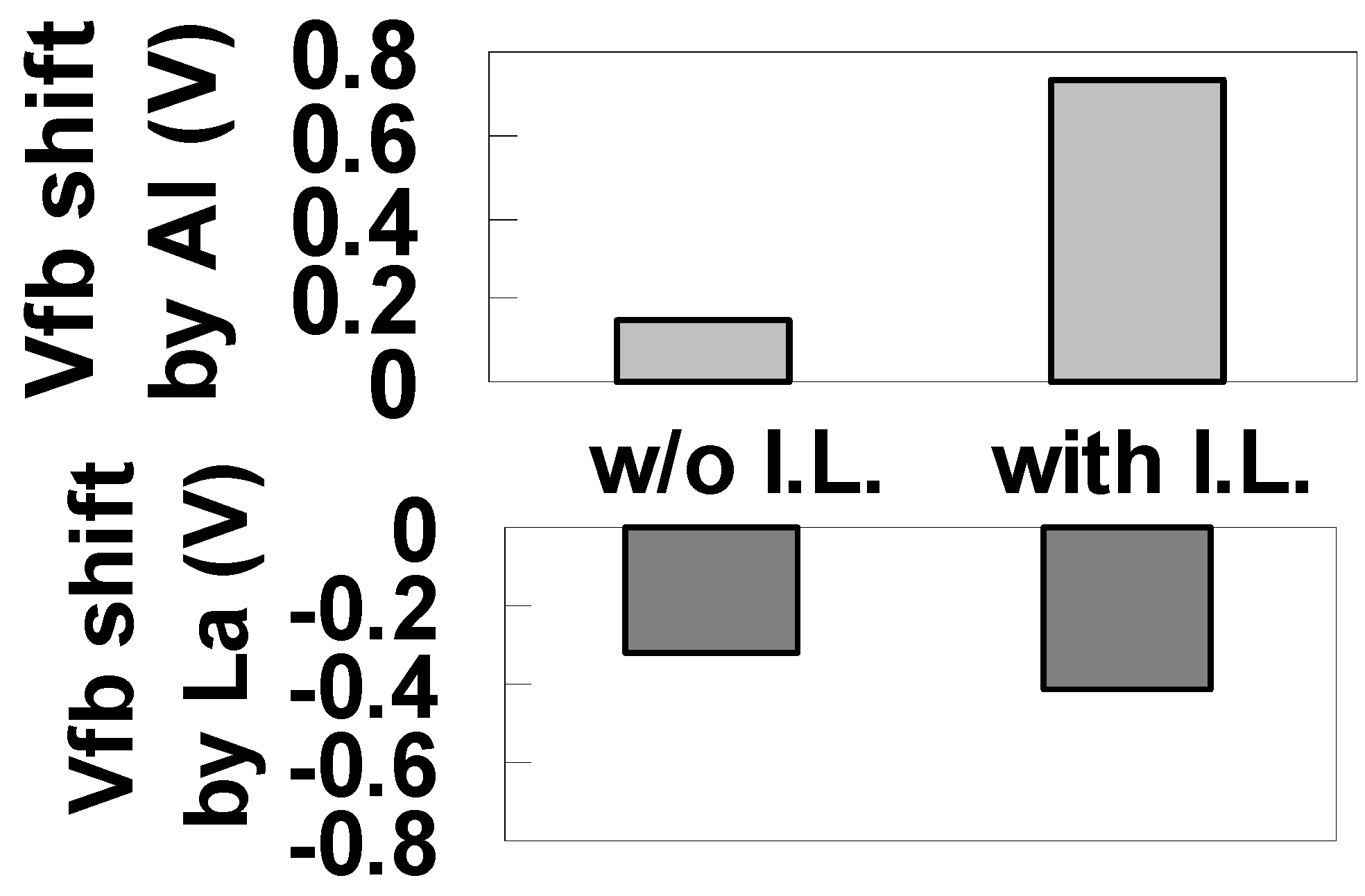

Figure 39 illustrates the maximum ΔVfb induced by (a) Al and (b) La relative to the intrinsic value for SiO

2 film for the Mo/La-Al-O/SiO

2/Si and Mo/La-Al-O/Si gate stacks. Although the shift induced by Al without SiO

2 was small, a large positive shift was induced by SiO

2 insertion, indicating that SiO

2 insertion is effective for Vth tuning of p-MISFETs. On the other hand, the negative shift induced by La without SiO

2 was relatively large, and the increase in shift caused by the insertion of SiO

2 was small.

Figure 38.

La/(La + Al) dependence of the energy difference between Al 2p and Si 2s. The vertical axis of the graph represents the energy difference as the divergence from the average value (average for all specimens).

Figure 38.

La/(La + Al) dependence of the energy difference between Al 2p and Si 2s. The vertical axis of the graph represents the energy difference as the divergence from the average value (average for all specimens).

Figure 39.

Bar graphs illustrating the maximum Vfb shift induced by (a) Al and (b) La relative to the intrinsic value for SiO2 film for the Mo/La-Al-O/SiO2/Si (with I.L.) and Mo/La-Al-O/Si (w/o I.L.) gate stacks.

Figure 39.

Bar graphs illustrating the maximum Vfb shift induced by (a) Al and (b) La relative to the intrinsic value for SiO2 film for the Mo/La-Al-O/SiO2/Si (with I.L.) and Mo/La-Al-O/Si (w/o I.L.) gate stacks.

Based on the findings above, we propose the following dipole model. Although an La-induced dipole forms at the interface with both Si and SiO

2, the effect is slightly stronger at the SiO

2 interface than at the Si interface. In addition, the effect of the Al-induced dipole becomes large when an SiO

2 layer is inserted. Furthermore, comparison of cases with and without SiO

2 in

Figure 38 indicates that the moment induced at the SiO

2 interface by Al is slightly larger than that induced by La. These results suggest that careful control of the interface layer is needed for Vth tuning of p-MISFETs with Al.

6. Gate-First TiN/LaAlO3 n-MOSFETs with Sulfur-Implanted Schottky Source/Drain Fabricated Using a Low-Temperature Process

As in the case of most high-

k dielectrics on Si substrate, when a conventional gate-first process with high-temperature annealing at around 1000 °C for the activation of implants is applied to a gate stack with LaAlO

3 film, the Si easily diffuses from the substrate into the dielectric, resulting in the formation of undesirable low-permittivity silicates and the consequent degradation of the EOT value. In this section, a successfully fabricated gate-first and SCE-tolerant n-MOSFET with deep sub-nm EOT that uses both TiN/LaAlO

3 gate stack and Schottky source/drain technologies will be demonstrated [

37].

The n-MOSFETs used in this study were fabricated as follows. LaAlO

3 gate dielectric films were deposited on LOCOS-isolated Si(100) wafers at 600 °C by PLD after dilute HF treatment. TiN film with a thickness of 60 nm was deposited as a gate electrode material on the LaAlO

3 film by the sputtering method. The TiN gate pattern was formed by reactive ion etching (RIE) with the conditions specified in reference [

38]. After forming the gate pattern, an SiO

2 side wall with a thickness of 9.6 nm was formed on the wafers at 380 °C by atmospheric pressure plasma chemical vapor deposition. Then, the SiO

2 layers on the gate and source/drain area were etched by RIE using CHF

3 plasma. After wet etching pretreatment using dilute HCl, NiSi-salicide was formed by depositing 20 nm of Ni by the sputtering method followed by rapid thermal annealing in an N

2 ambient at 450 °C for 1 min. Unreacted Ni was removed by wet etching using a 1:2 H

2O

2:H

2SO

4 solution. The wafers were then implanted with sulfur ions (implantation energy: 23 keV, fluence: 2 × 10

15/cm

2). The implantation energy of 23 keV was selected to adjust the projection range (Rp) so that the center of the NiSi layer (in the depth direction) was set as the target depth for implantation. After implantation, drive-in annealing for the implanted sulfur was performed in an N

2 ambient for 1 min at 450 °C [

39]. The substrate impurity concentration was estimated from C-V measurements to be 1.6 × 10

14/cm

3. In order to clarify the effect of the Schottky source/drain on the SCE immunity for a conventional MOSFET, no additional implantation, such as channel implantation or halo implantation, was performed.

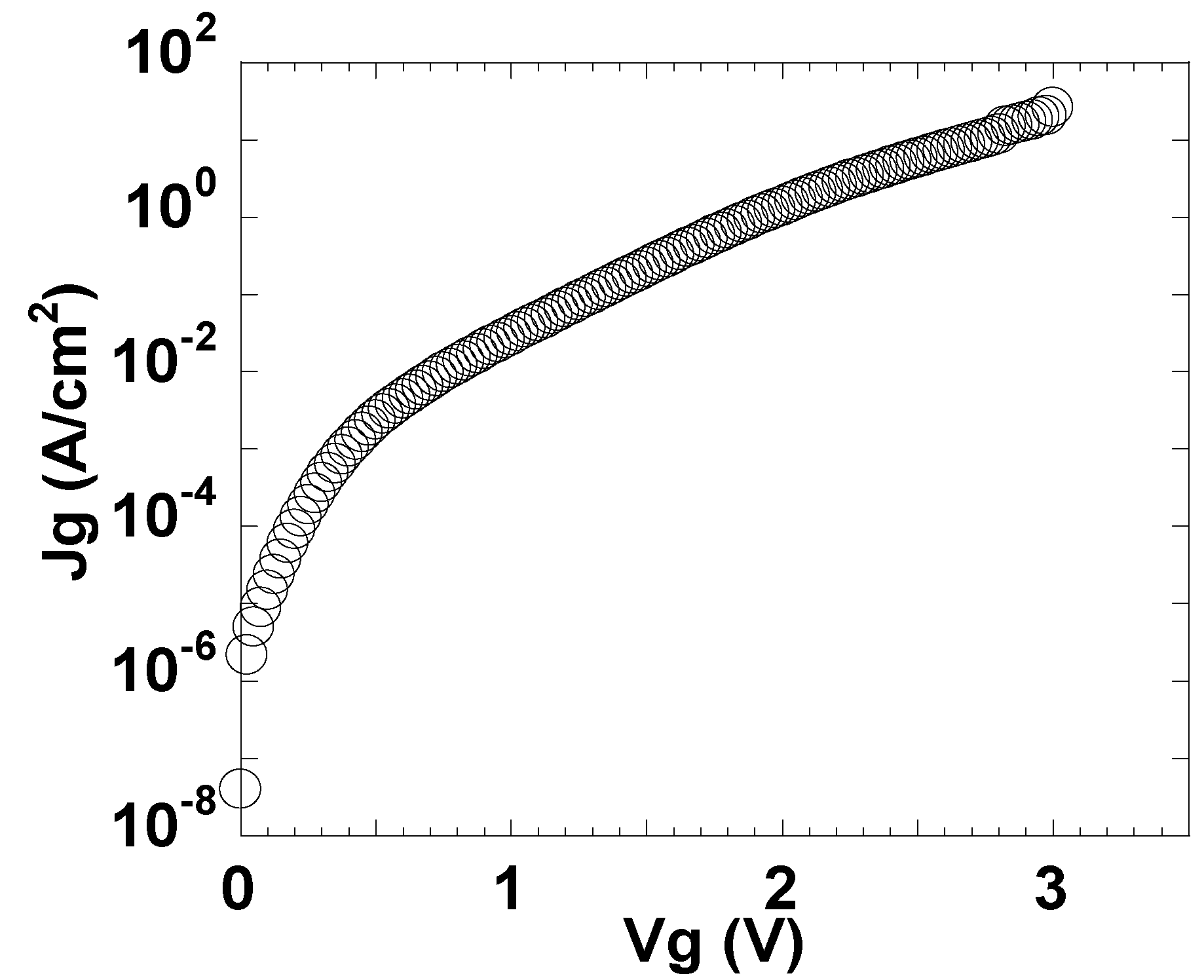

6.1. Successful Fabrication of Gate-First n-MOSFET with Deep Sub-nm EOT

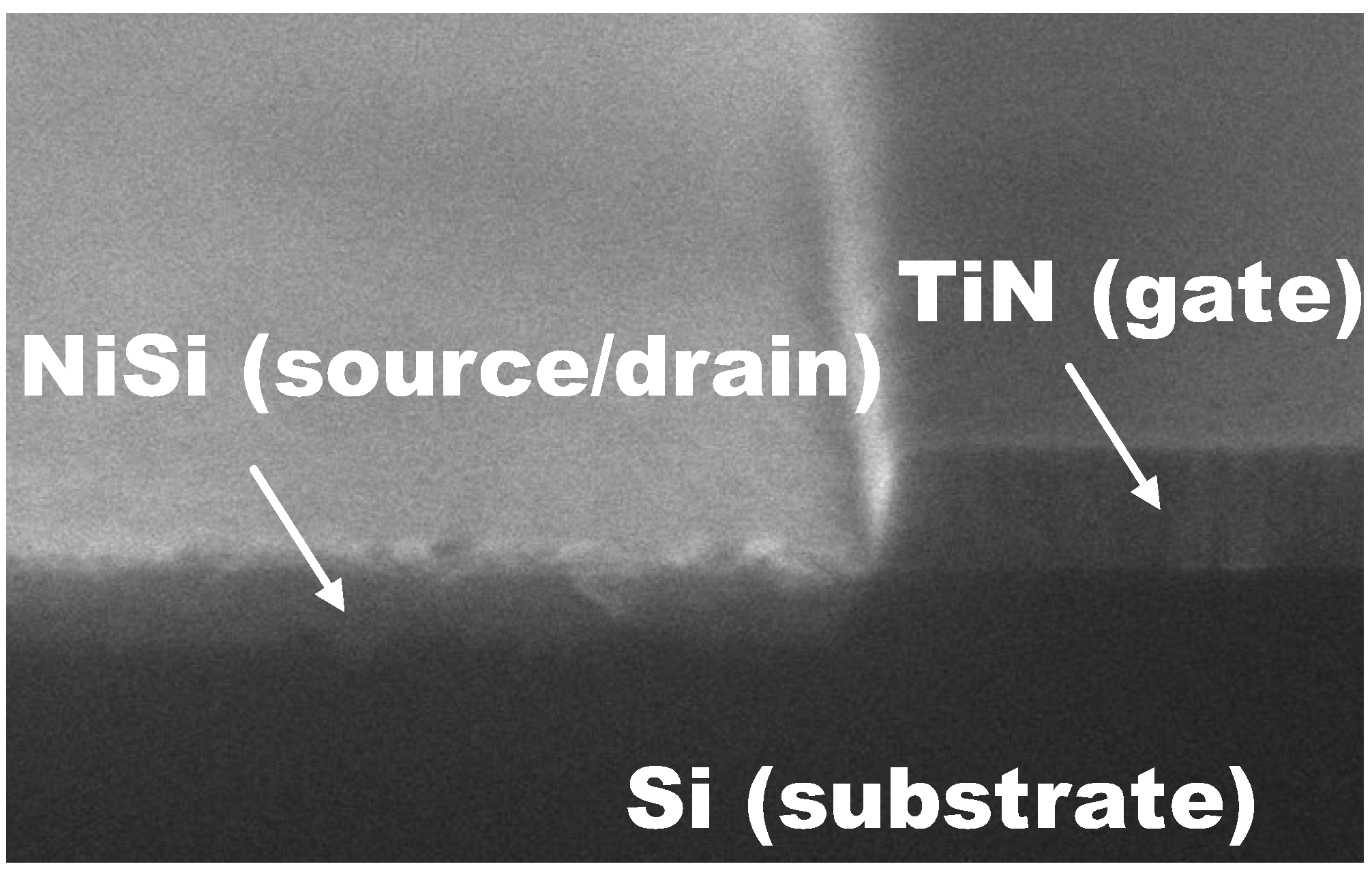

Figure 40 shows a scanning electron microscopy (SEM) image of the fabricated n-MOSFET (perspective view). It was confirmed that the gate pattern was successfully fabricated with a taper angle of almost 90° and that no severe agglomeration of NiSi could be observed. AES depth-profile analysis revealed that nickel monosilicide was formed in the source/drain region.

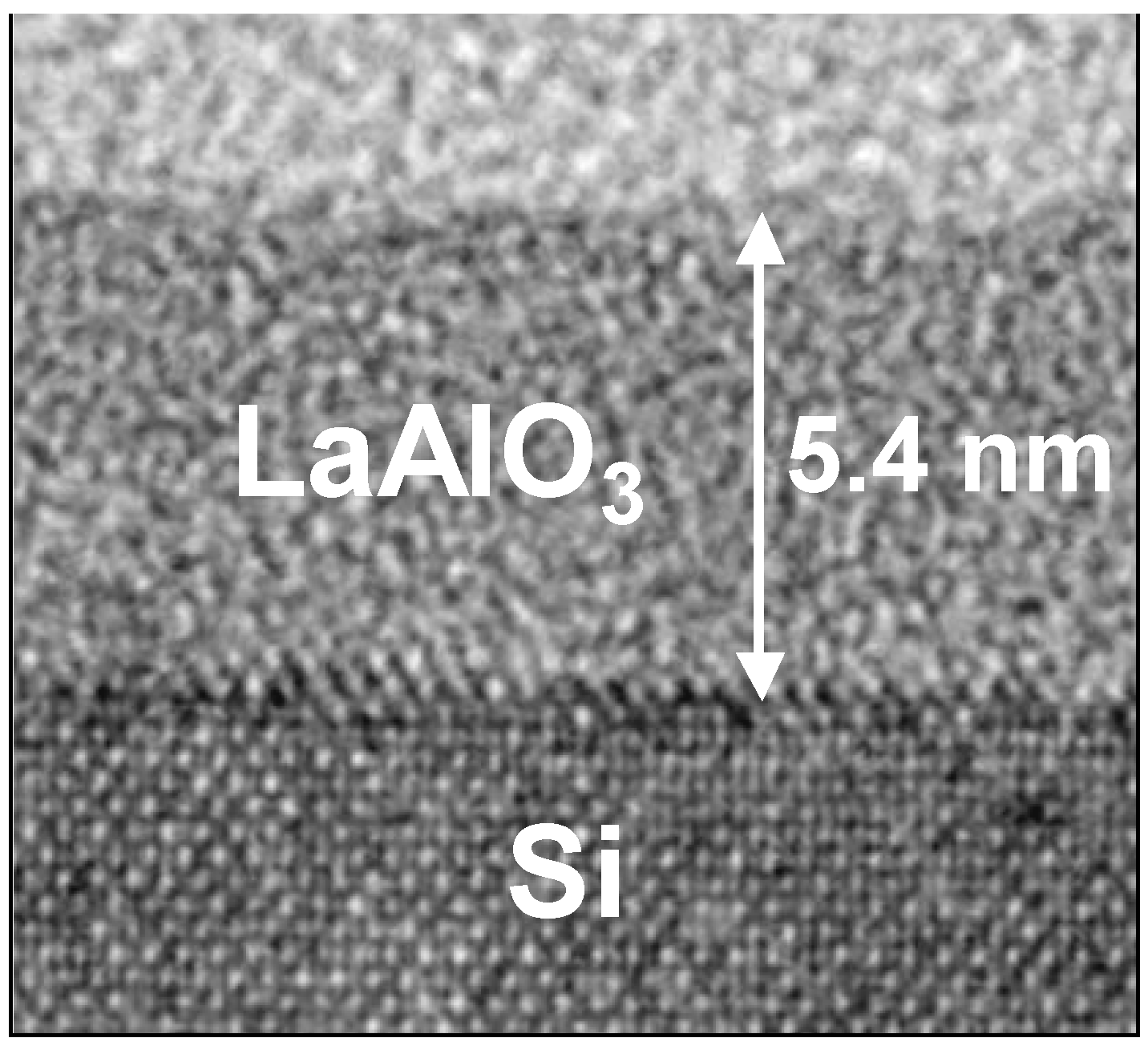

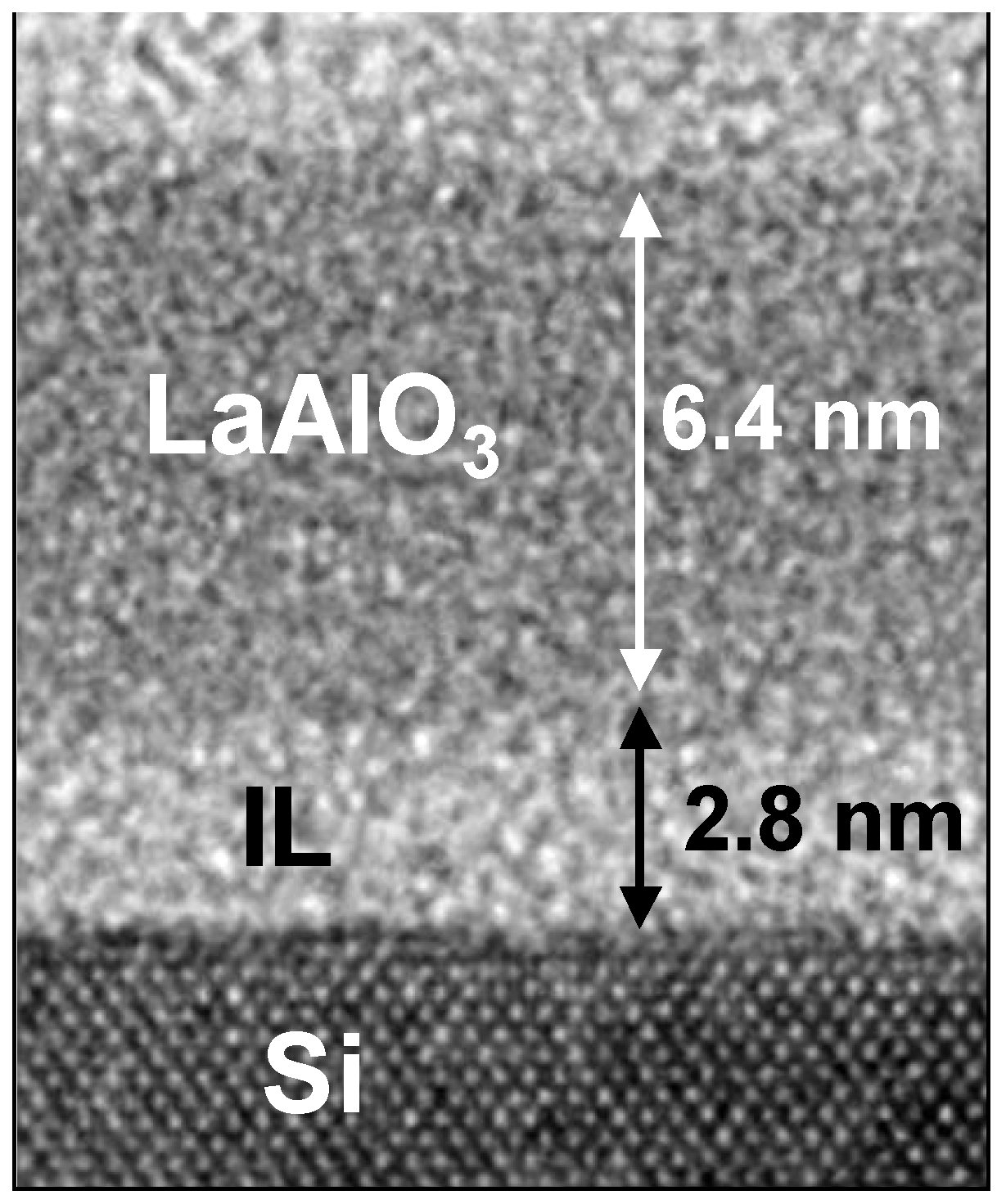

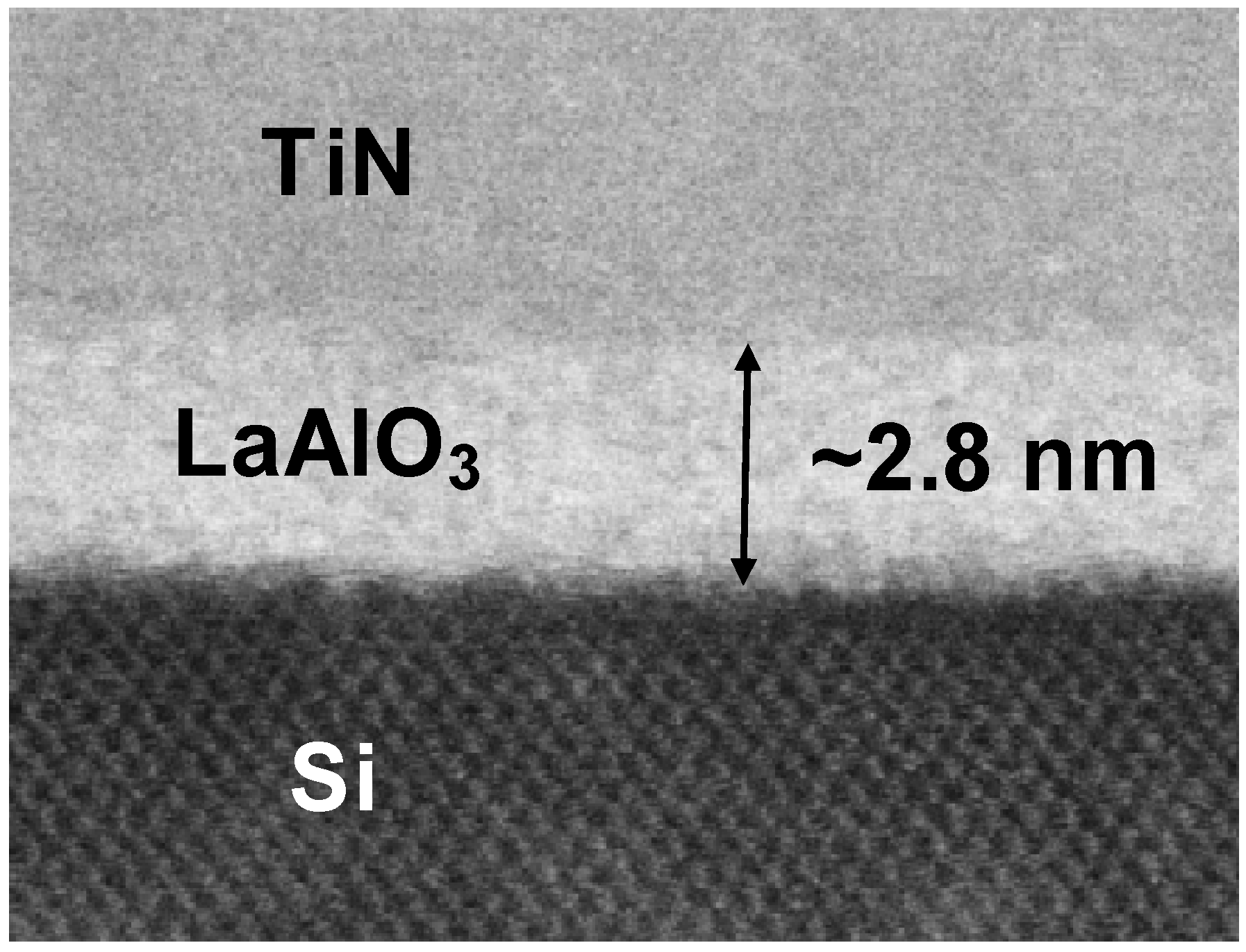

Figure 41 shows a cross-sectional scanning transmission electron microscopy (STEM) image of the TiN/LaAlO

3/Si gate stack. The physical film thickness of LaAlO

3 was estimated to be about 2.8 nm. As expected, thanks to the low-temperature fabrication process, no interfacial layer of SiO

2 or silicate was observed in the gate stack.

Figure 40.

Perspective-view SEM image of an n-MOSFET incorporating both metal gate/high-k gate stack and sulfur-implanted Schottky source/drain technologies.

Figure 40.

Perspective-view SEM image of an n-MOSFET incorporating both metal gate/high-k gate stack and sulfur-implanted Schottky source/drain technologies.

Figure 41.

Cross-sectional STEM image of a metal gate/high-k (TiN/LaAlO3) gate stack.

Figure 41.

Cross-sectional STEM image of a metal gate/high-k (TiN/LaAlO3) gate stack.

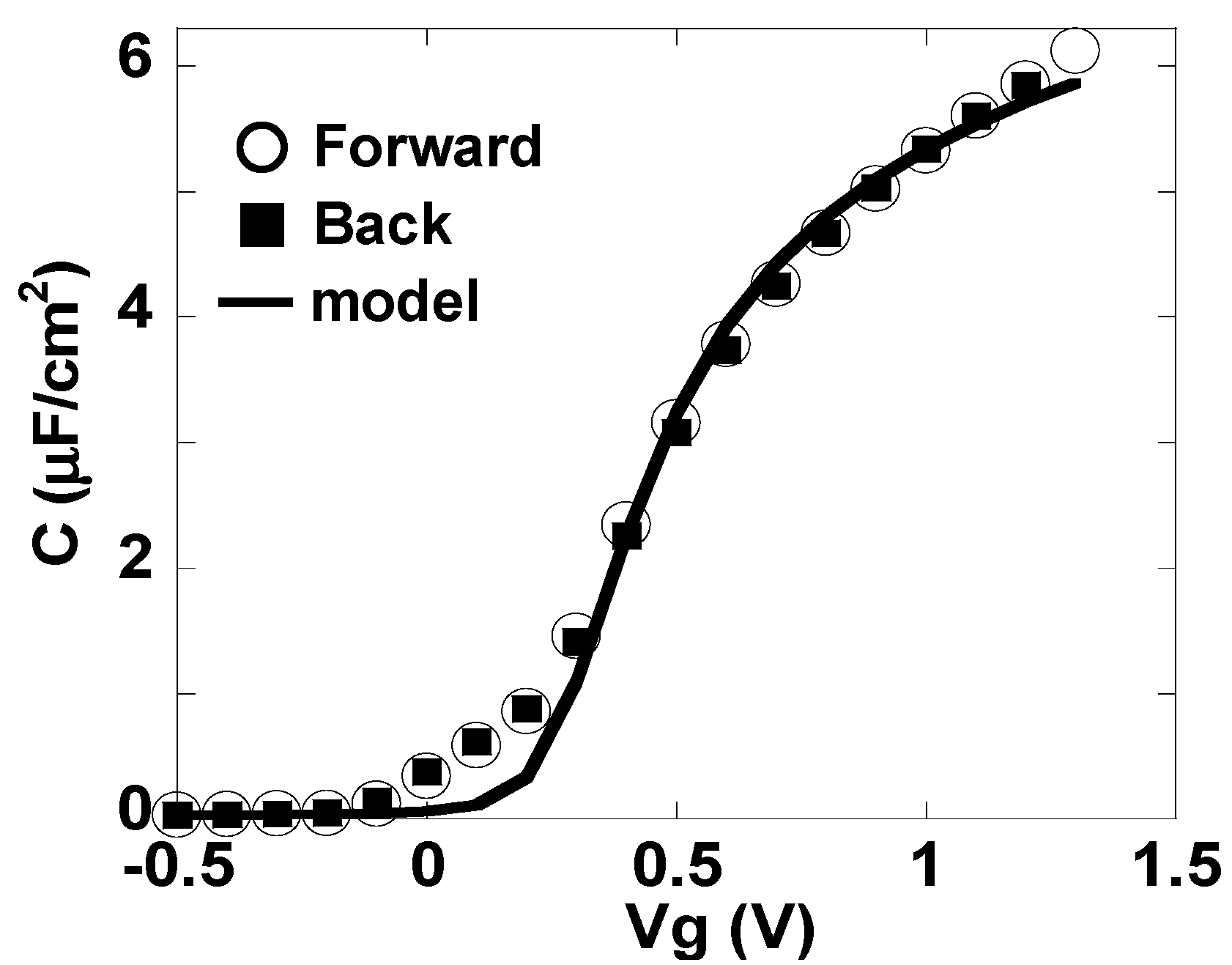

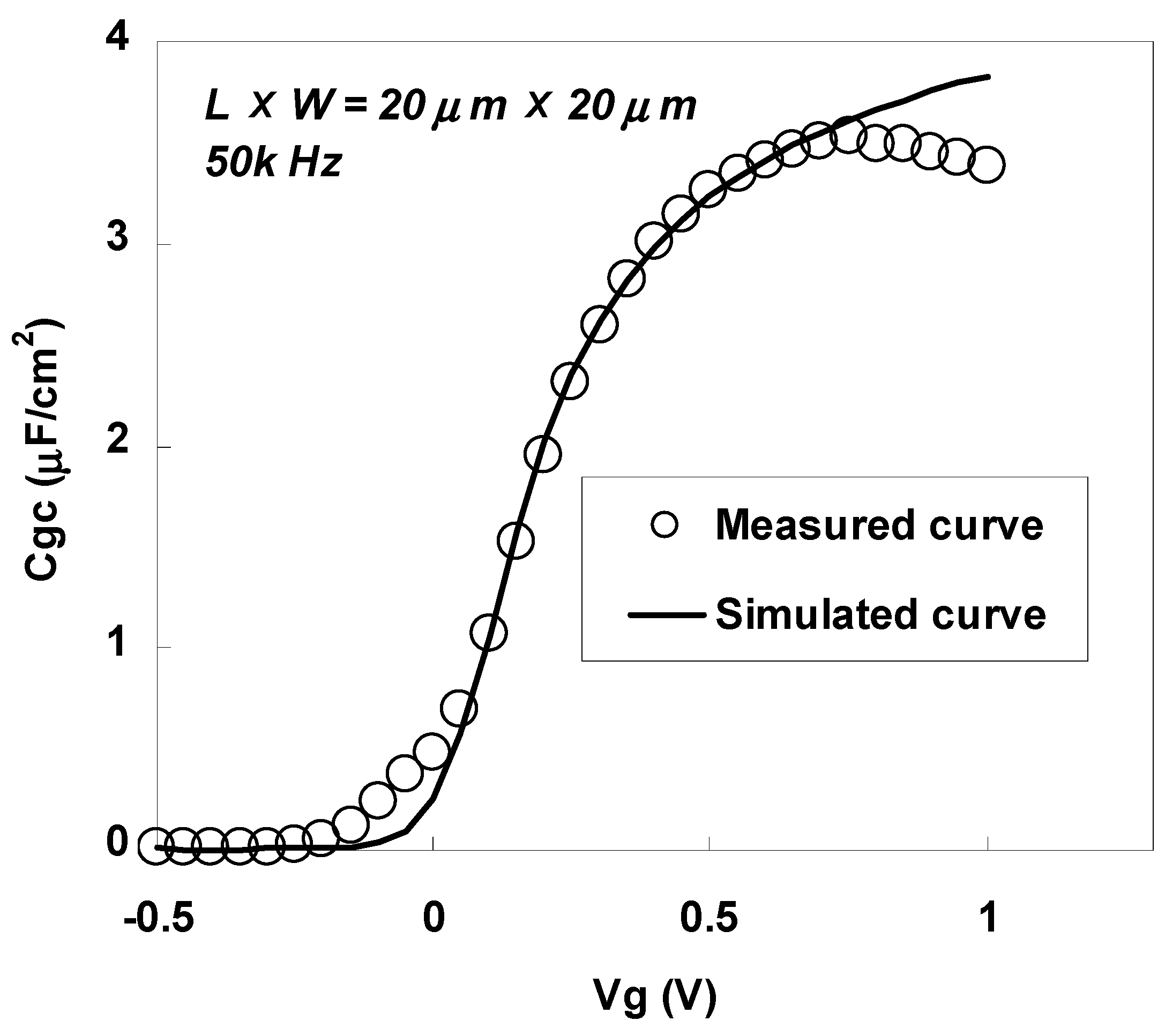

Figure 42 shows the gate-to-channel capacitance (Cgc)-Vg characteristics for an n-MOSFET with LXW = 20 μm × 20 μm, which was annealed at 450 °C after sulfur implantation. The measurement was performed at a frequency of 50 kHz. A fitted simulation curve is also shown in the figure [

8]. The measured capacitance was observed to be lossy in the high electric field region due to the high gate leakage current. However, the inversion thickness and EOT estimated by comparison with the simulated curve were as small as 0.90 nm and 0.58 nm, respectively. The obtained EOT was smaller than that reported in a previous study on TaN/LaTiO n-MOSFETs using the gate-first process [

40]. These small values of the inversion thickness and EOT are inherent to the LaAlO

3 high-

k dielectric, but cannot be achieved when conventional source/drain technology is used for the gate-first process, because the Si atoms from the substrate easily diffuse into the LaAlO

3 layer during high-temperature annealing for the formation of pn junctions, resulting in undesirable lowering of the permittivity.

Figure 42.

Cgc-Vg characteristics for an n-MOSFET annealed at 450 °C after sulfur implantation.

Figure 42.

Cgc-Vg characteristics for an n-MOSFET annealed at 450 °C after sulfur implantation.

6.2. Comparison of MOSFET Characteristics between Sulfur-Implanted Schottky Source/Drain MOSFETs and Conventional MOSFETs

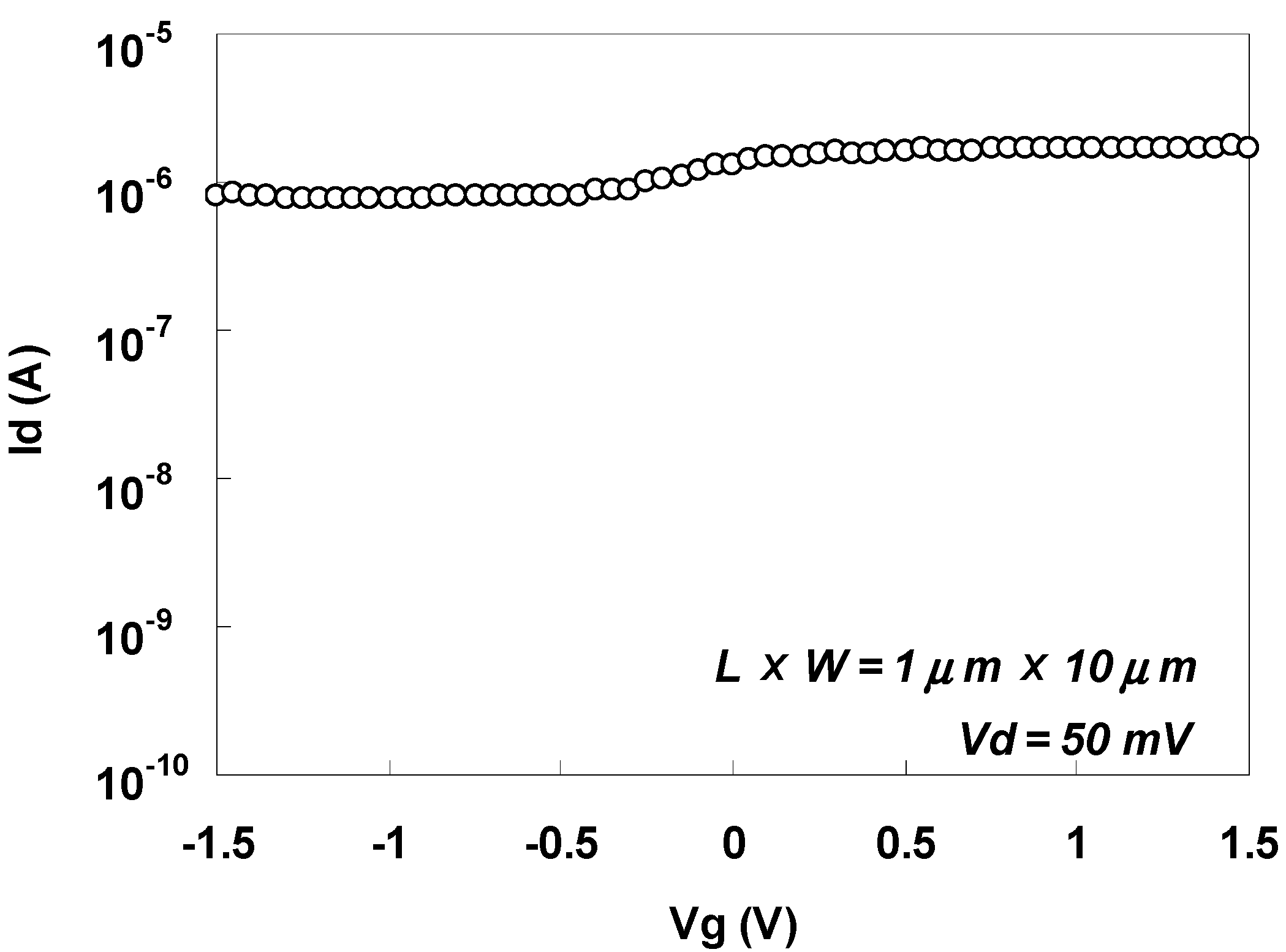

Figure 43 shows the Id-Vg characteristics immediately after implantation of sulfur for an n-MOSFET with LXW = 1 μm × 10 μm. As can be seen in the figure, off-leakage suppression was small, resulting in a small Ion/Ioff ratio. The main component of the large off-leakage current was the reverse current of the Schottky diode because the NiSi/p-Si Schottky barrier height for holes was small. This behavior is similar to that before sulfur implantation (data not shown).

Figure 43.

Id-Vg characteristics for an n-MOSFET immediately after implantation of sulfur.

Figure 43.

Id-Vg characteristics for an n-MOSFET immediately after implantation of sulfur.

The effect of sulfur implantation can be seen only when it diffuses into the NiSi/Si interface as a result of drive-in annealing followed by modulation of the NiSi/Si Schottky barrier height [

39,

41].

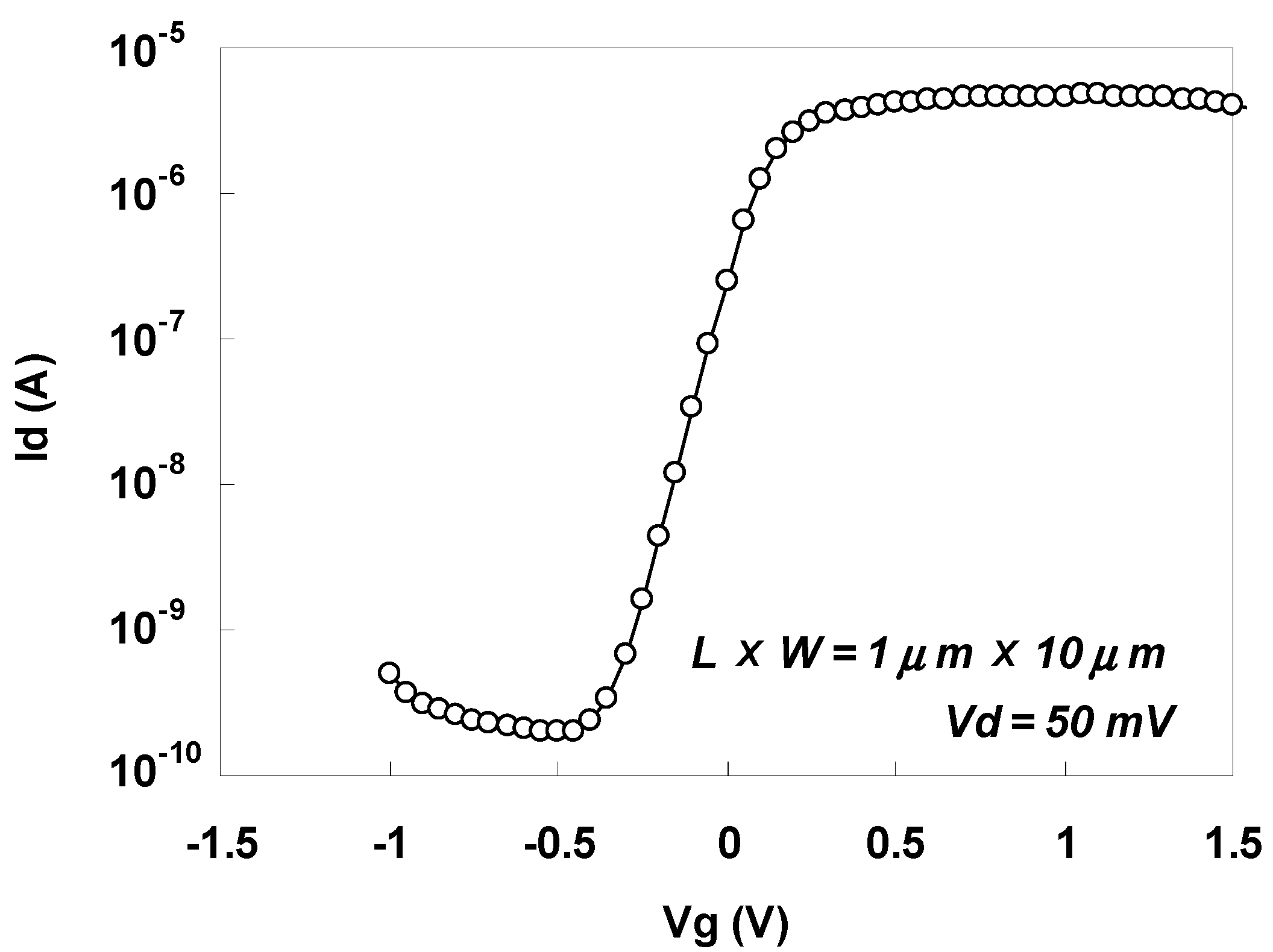

Figure 44 shows the Id-Vg characteristics for an n-MOSFET annealed for 1 min at 450 °C after sulfur implantation. As can be seen by comparing

Figure 44 with

Figure 43, both the drive-current and the suppression of off-leakage were dramatically improved by drive-in annealing, and well-behaved Id-Vg characteristics were obtained.

Figure 44.

Id-Vg characteristics for an n-MOSFET annealed for 1 min at 450 °C after sulfur implantation.

Figure 44.

Id-Vg characteristics for an n-MOSFET annealed for 1 min at 450 °C after sulfur implantation.

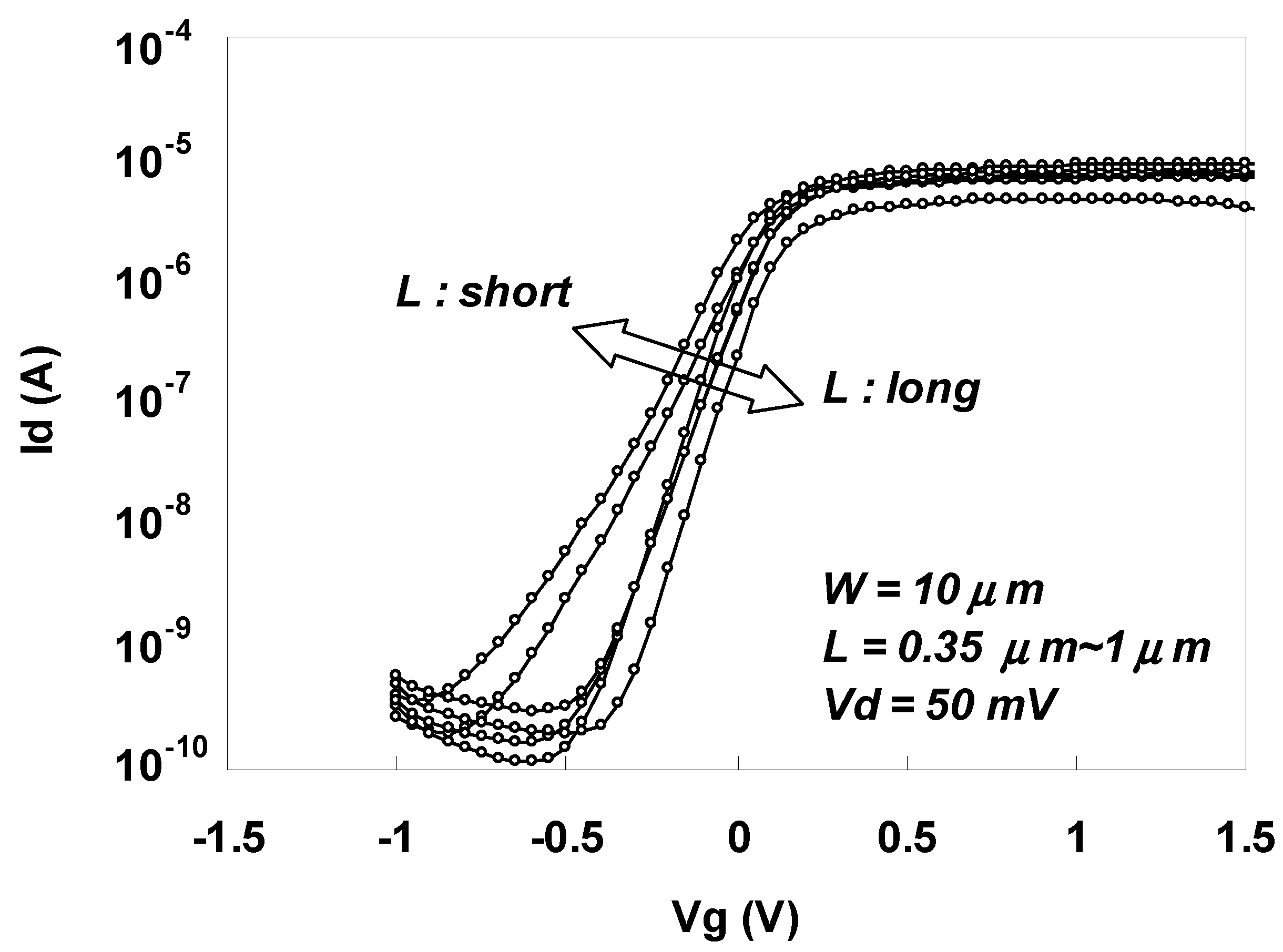

Figure 45 shows the Id-Vg characteristics for gate lengths ranging from 0.35 μm to 1.0 μm for n-MOSFETs annealed for 1 min at 450 °C after sulfur implantation. The characteristics were well behaved as a whole, and a current on/off ratio of more than 4 orders of magnitude was obtained.

Figure 45.

Id-Vd characteristics for an n-MOSFET annealed 1 minat 450 °C after sulfur implantation.

Figure 45.

Id-Vd characteristics for an n-MOSFET annealed 1 minat 450 °C after sulfur implantation.

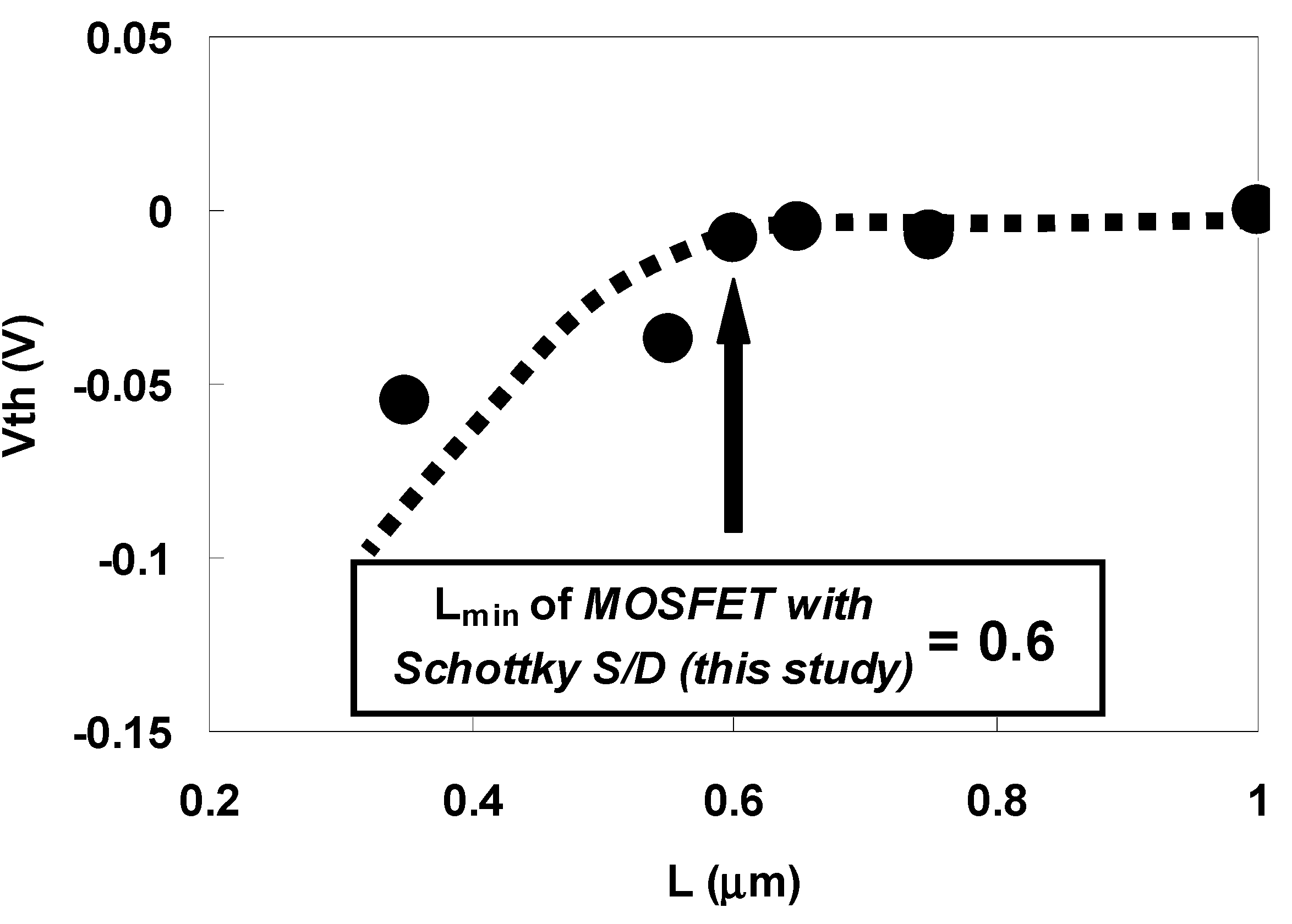

The main performance advantage of Schottky source/drain contacts is the immunity against SCE due to a shallower junction. Therefore, the minimum channel length (L

min) for which long channel subthreshold behavior can be observed was investigated using the gate length (L) dependence of Vth (Vth roll-off characteristics) of the n-MOSFET with Schottky source/drain used in this study. The estimated L

min was compared with that of a conventional MOSFET obtained from the following well-known empirical relationship [

42]:

where r

j is the junction depth, d is the equivalent oxide thickness, and (Ws + Wd) is the sum of source and drain depletion widths.

For the n-MOSFET with Schottky source/drain used in this study, rj was around 48 nm (average value obtained from the cross-sectional SEM image), d was 0.58 nm as mentioned earlier, and (Ws + Wd) was 5.23 μm (calculated from the substrate impurity concentration and applied drain voltage).

Figure 46 shows the gate length (L) dependence of Vth (Vth roll-off characteristics) for the sulfur-implanted n-MOSFET with Schottky source/drain. Note that Vth is normalized against its value at a gate length of 1 μm for a clearer comparison. As can be seen in the figure, a significant negative Vth shift due to the dependence of SCE on the gate length was clearly observed when L was less than 0.6 μm, indicating that L

min for the Schottky source/drain n-MOSFET used in this study was around 0.6 μm. On the other hand, based on Equation (3), a shallow rj of 29 nm is needed in a conventional MOSFET to obtain the same L

min as that for a Schottky source/drain MOSFET with an rj of 48 nm. This result clearly demonstrates the advantage of n-MOSFETs that use Schottky source/drain contacts over n-MOSFETS that use conventional source/drain contacts.

Figure 46.

Id-Vg characteristics for gate lengths ranging from 0.35 μm to 1.0 μm for n-MOSFETs annealed for 1 min at 450 °C after sulfur implantation.

Figure 46.

Id-Vg characteristics for gate lengths ranging from 0.35 μm to 1.0 μm for n-MOSFETs annealed for 1 min at 450 °C after sulfur implantation.