Defects Contributing to Hysteresis in Few-Layer and Thin-Film MoS2 Memristive Devices

Abstract

:1. Introduction

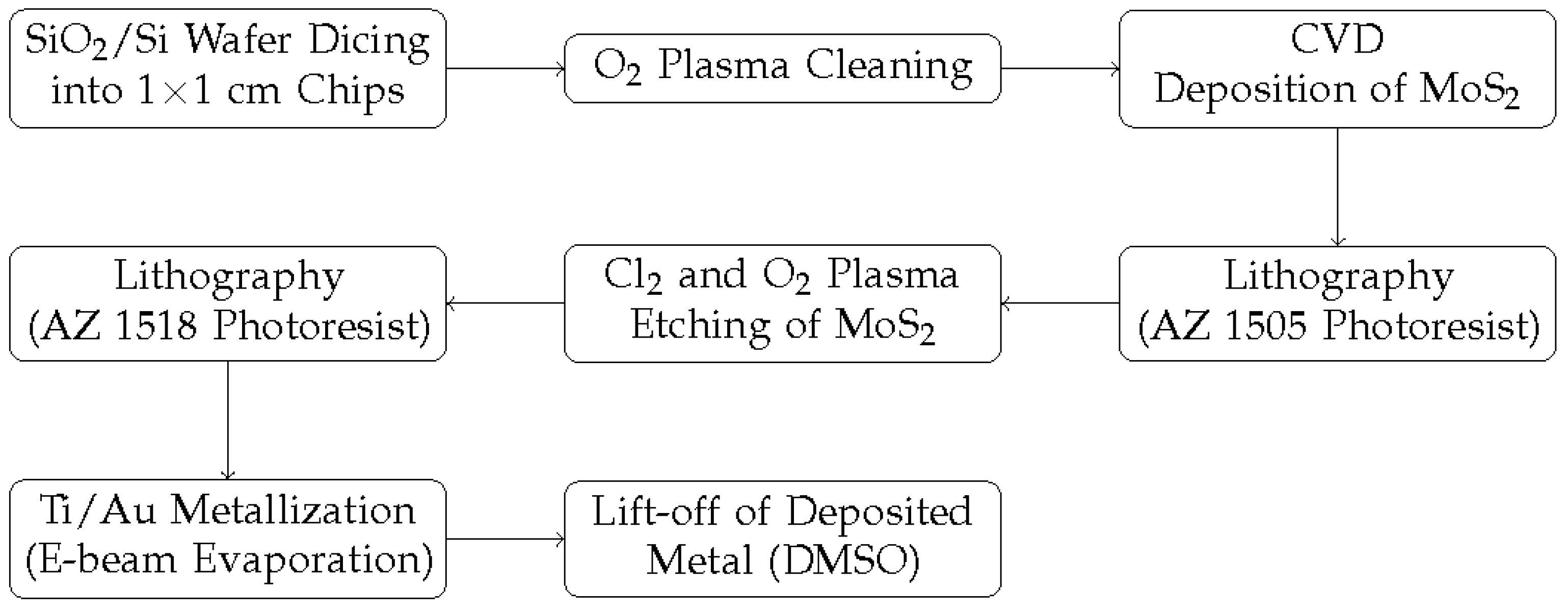

2. Materials and Methods

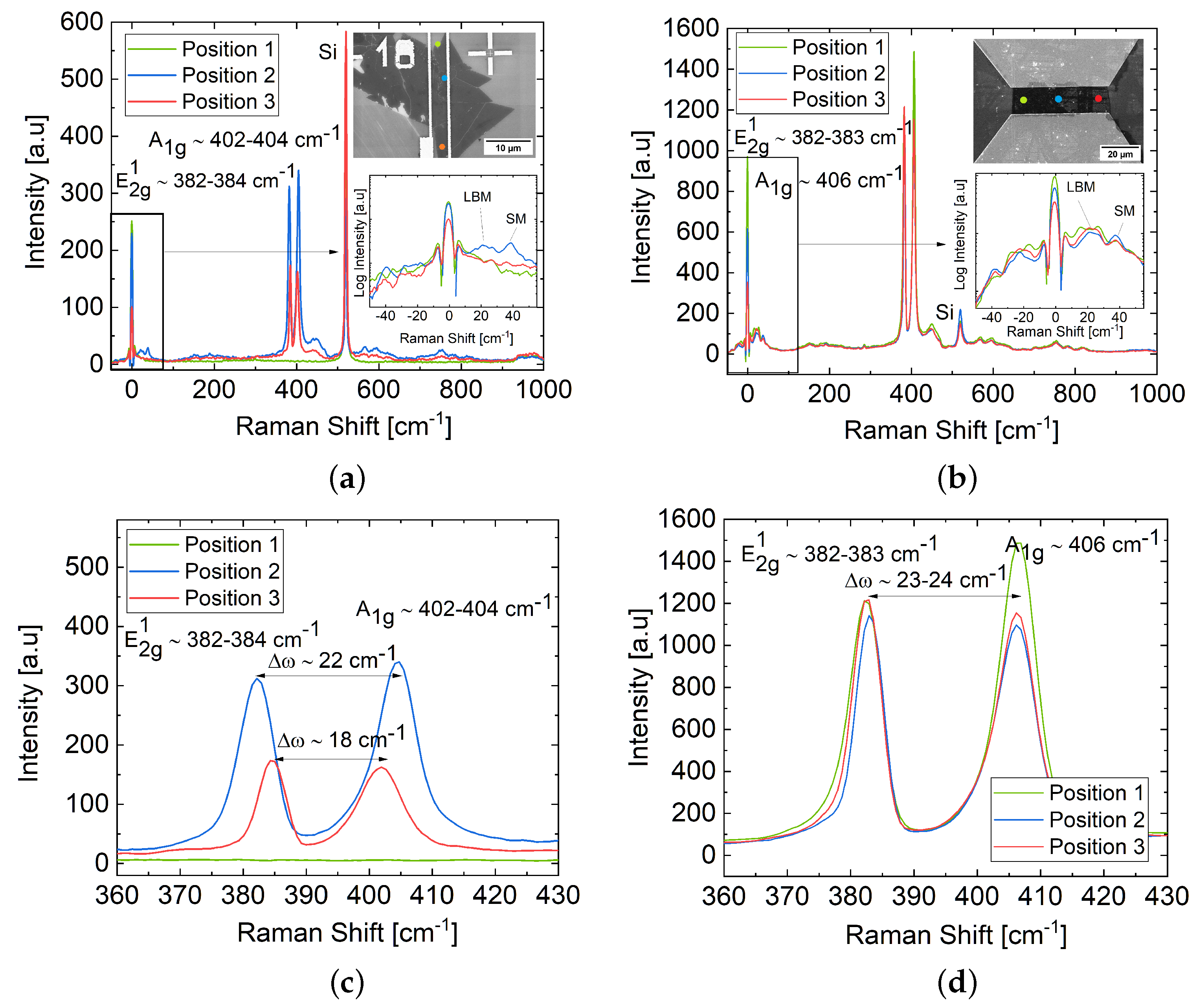

2.1. Material Characterization

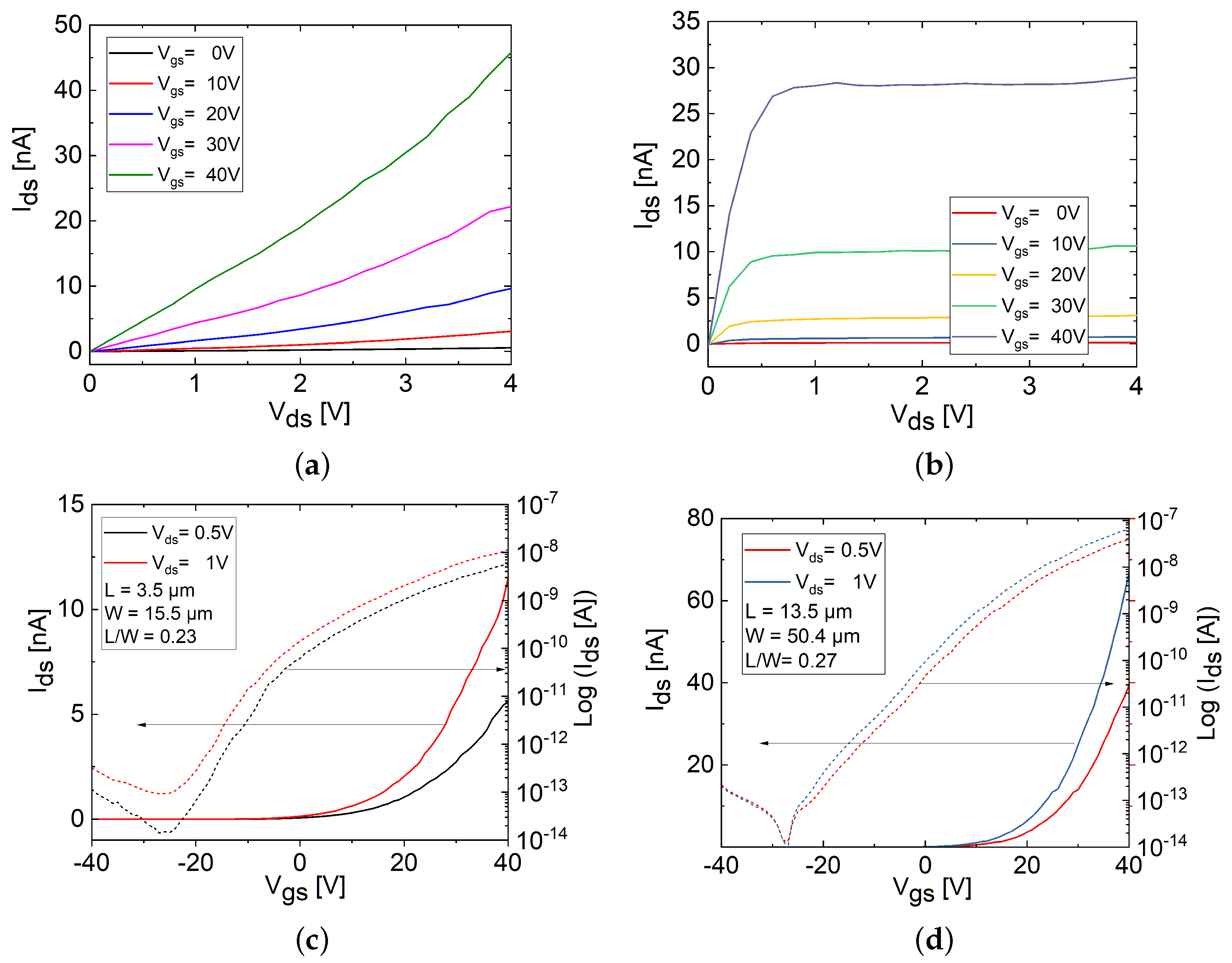

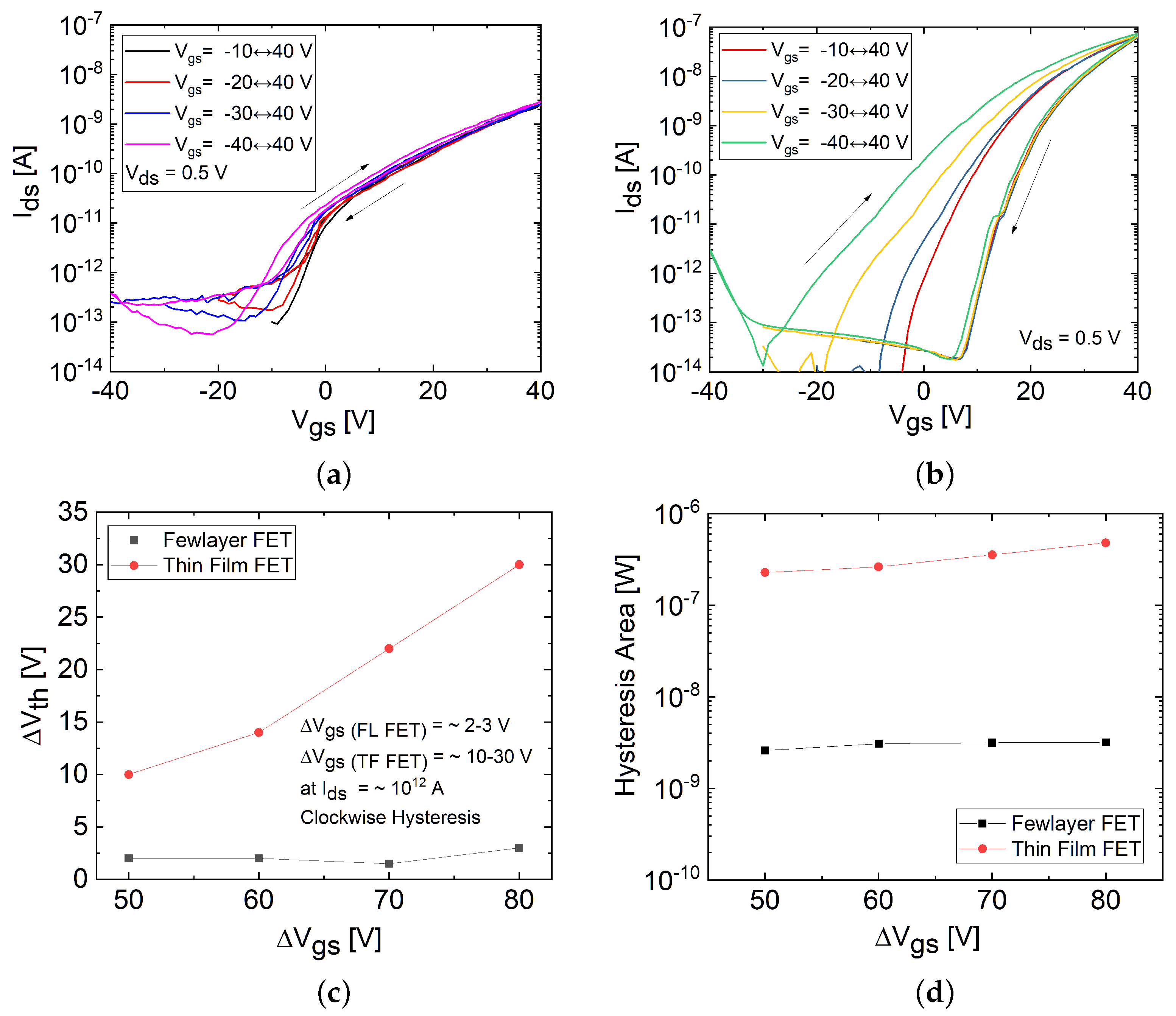

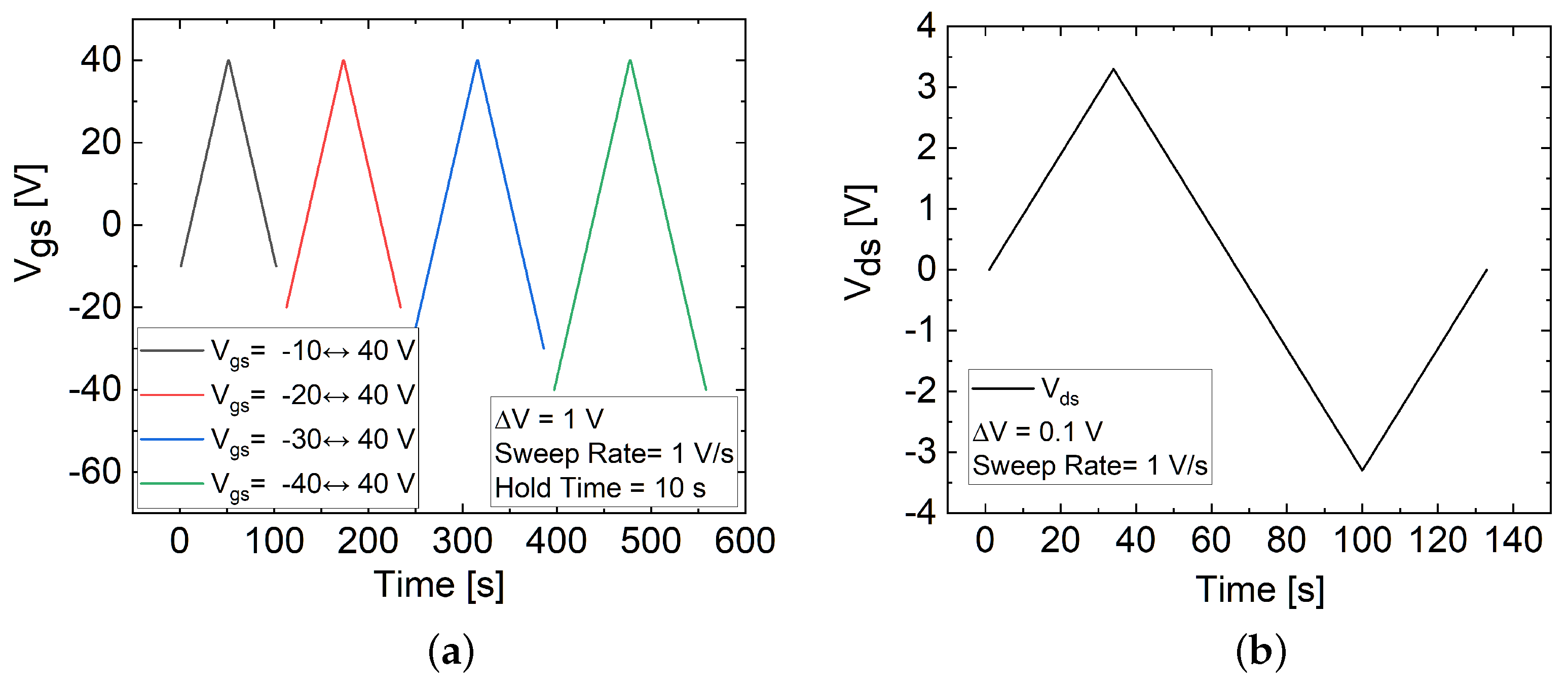

2.2. Electrical Characterization

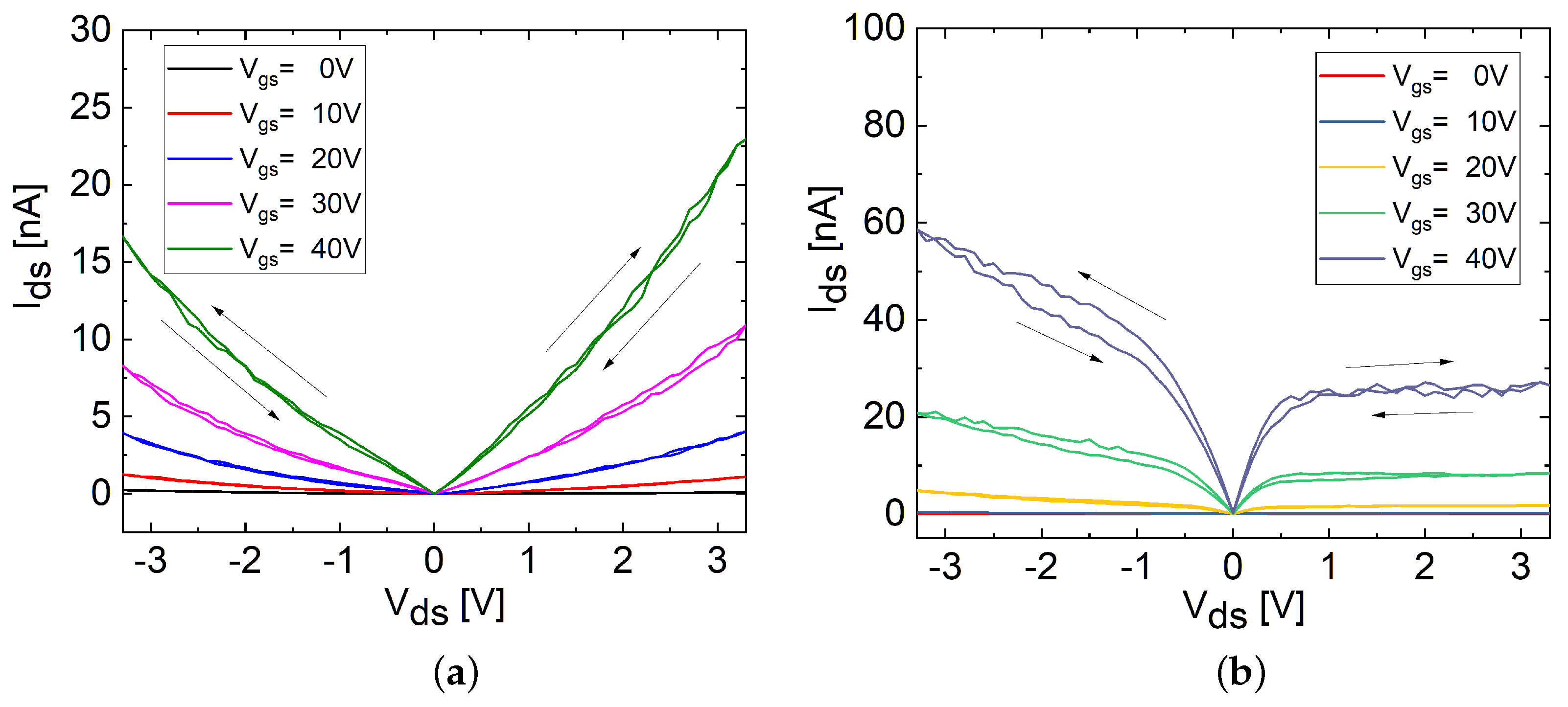

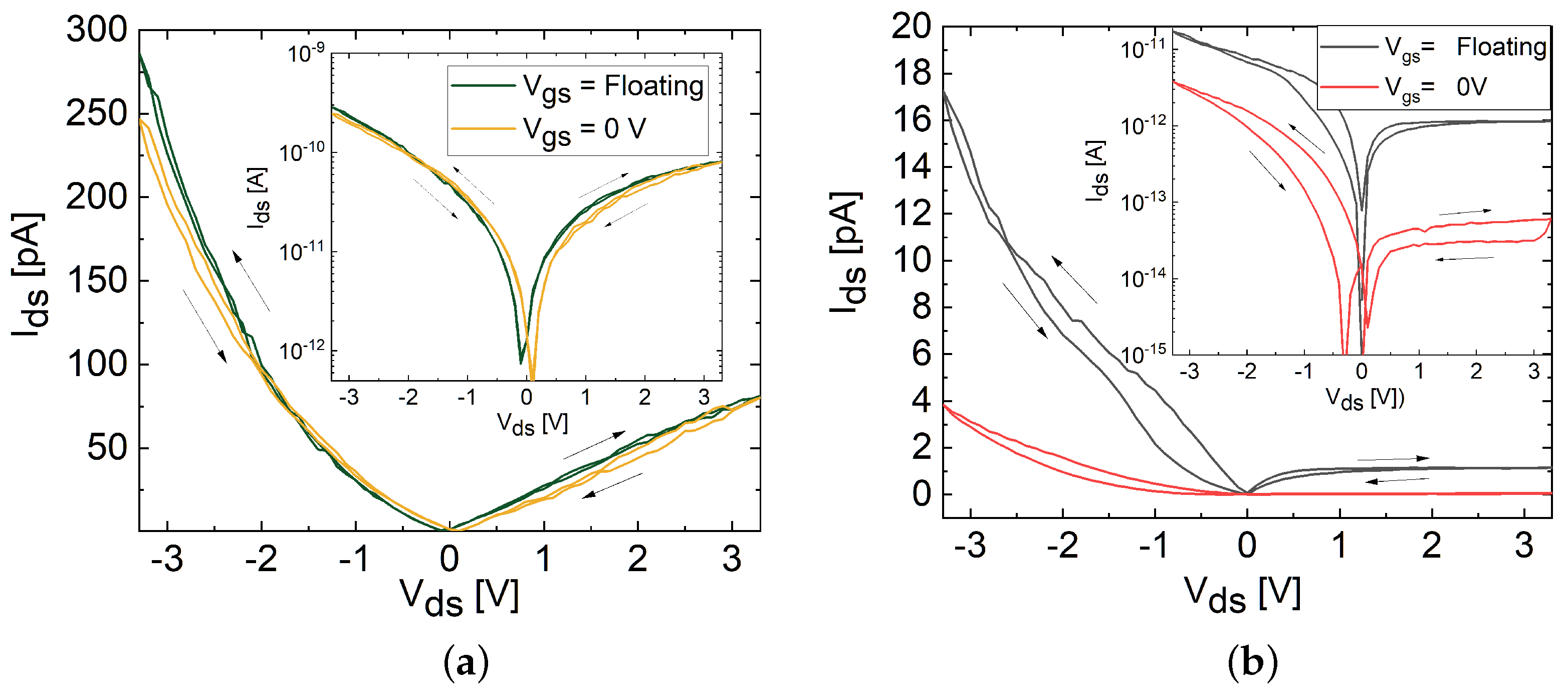

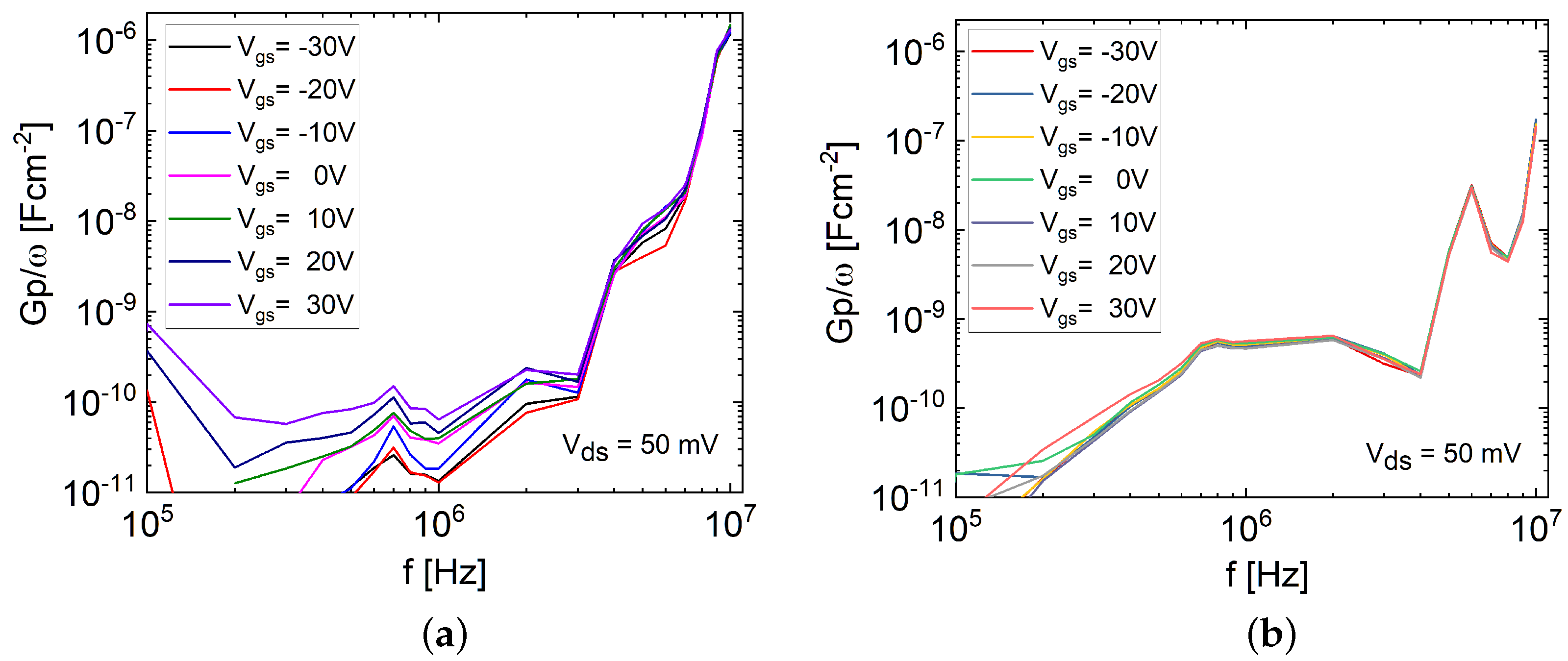

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Schwierz, F.; Pezoldt, J.; Granzner, R. Two-dimensional materials and their prospects in transistor electronics. Nanoscale 2015, 7, 8261–8283. [Google Scholar] [CrossRef]

- Desai, S.B.; Madhvapathy, S.R.; Sachid, A.B.; Llinas, J.P.; Wang, Q.; Ahn, G.H.; Pitner, G.; Kim, M.J.; Bokor, J.; Hu, C.; et al. MoS2 transistors with 1-nanometer gate lengths. Science 2016, 354, 99–102. [Google Scholar] [CrossRef]

- Di Bartolomeo, A.; Genovese, L.; Giubileo, F.; Iemmo, L.; Luongo, G.; Foller, T.; Schleberger, M. Hysteresis in the transfer characteristics of MoS2 transistors. 2D Mater. 2017, 5, 015014. [Google Scholar] [CrossRef]

- Ganatra, R.; Zhang, Q. Few-layer MoS2: A promising layered semiconductor. ACS Nano 2014, 8, 4074–4099. [Google Scholar] [CrossRef]

- Lemme, M.C.; Akinwande, D.; Huyghebaert, C.; Stampfer, C. 2D materials for future heterogeneous electronics. Nat. Commun. 2022, 13, 1392. [Google Scholar] [CrossRef]

- Majumdar, K.; Hobbs, C.; Kirsch, P.D. Benchmarking transition metal dichalcogenide MOSFET in the ultimate physical scaling limit. IEEE Electron Device Lett. 2014, 35, 402–404. [Google Scholar] [CrossRef]

- Yu, Z.; Ong, Z.Y.; Li, S.; Xu, J.B.; Zhang, G.; Zhang, Y.W.; Shi, Y.; Wang, X. Analyzing the carrier mobility in transition-metal dichalcogenide MoS2 field-effect transistors. Adv. Funct. Mater. 2017, 27, 1604093. [Google Scholar] [CrossRef]

- Franklin, A.D. Nanomaterials in transistors: From high-performance to thin-film applications. Science 2015, 349, aab2750. [Google Scholar] [CrossRef]

- Zhang, L.; Gong, T.; Wang, H.; Guo, Z.; Zhang, H. Memristive devices based on emerging two-dimensional materials beyond graphene. Nanoscale 2019, 11, 12413–12435. [Google Scholar] [CrossRef]

- Yin, L.; Cheng, R.; Wen, Y.; Liu, C.; He, J. Emerging 2D Memory Devices for In-Memory Computing. Adv. Mater. 2021, 33, 2007081. [Google Scholar] [CrossRef]

- Rai, A.; Movva, H.C.; Roy, A.; Taneja, D.; Chowdhury, S.; Banerjee, S.K. Progress in contact, doping and mobility engineering of MoS2: An atomically thin 2D semiconductor. Crystals 2018, 8, 316. [Google Scholar] [CrossRef]

- Huh, W.; Lee, D.; Lee, C.H. Memristors based on 2D materials as an artificial synapse for neuromorphic electronics. Adv. Mater. 2020, 32, 2002092. [Google Scholar] [CrossRef]

- Jeong, Y.; Sung, J.Y.; Choi, Y.; Jin, J.S.; Yoon, J.H.; Heo, S.; Hayakawa, R.; Wakayama, Y. Structural characterization and transistor properties of thickness-controllable MoS2 thin films. J. Mater. Sci. 2019, 54, 7758–7767. [Google Scholar] [CrossRef]

- Mathew, S.; Narasimha, S.; Reiprich, J.; Scheler, T.; Häahnlein, B.; Thiele, S.; Stauffenberg, J.; Kurtash, V.; Abedin, S.; Manske, E.; et al. Formation and Characterization of Three-Dimensional Tetrahedral MoS2 Thin Films by Chemical Vapor Deposition. Cryst. Growth Des. 2022, 22, 5229–5238. [Google Scholar] [CrossRef]

- Marquez, C.; Salazar, N.; Gity, F.; Galdon, J.C.; Navarro, C.; Duffy, R.; Hurley, P.; Gamiz, F. Performance and reliability in back-gated CVD-grown MoS2 devices. Solid-State Electron. 2021, 186, 108173. [Google Scholar] [CrossRef]

- Late, D.J.; Liu, B.; Matte, H.R.; Dravid, V.P.; Rao, C. Hysteresis in single-layer MoS2 field effect transistors. ACS Nano 2012, 6, 5635–5641. [Google Scholar] [CrossRef] [PubMed]

- Prasad, P.; Garg, M.; Chandni, U. Tailoring the transfer characteristics and hysteresis in MoS2 transistors using substrate engineering. Nanoscale 2020, 12, 23817–23823. [Google Scholar] [CrossRef]

- Huang, K.; Zhao, M.; Sun, B.; Liu, X.; Liu, J.; Chang, H.; Zeng, Y.; Liu, H. Transition from hopping to band-like transport in weakly coupled multilayer MoS2 field effect transistors. ACS Appl. Electron. Mater. 2020, 2, 971–979. [Google Scholar] [CrossRef]

- Zhou, Z.; Yang, F.; Wang, S.; Wang, L.; Wang, X.; Wang, C.; Xie, Y.; Liu, Q. Emerging of two-dimensional materials in novel memristor. Front. Phys. 2022, 17, 1–14. [Google Scholar] [CrossRef]

- Shu, J.; Wu, G.; Guo, Y.; Liu, B.; Wei, X.; Chen, Q. The intrinsic origin of hysteresis in MoS2 field effect transistors. Nanoscale 2016, 8, 3049–3056. [Google Scholar] [CrossRef]

- Kaushik, N.; Mackenzie, D.M.; Thakar, K.; Goyal, N.; Mukherjee, B.; Boggild, P.; Petersen, D.H.; Lodha, S. Reversible hysteresis inversion in MoS2 field effect transistors. npj 2D Mater. Appl. 2017, 1, 34. [Google Scholar] [CrossRef]

- Park, Y.; Baac, H.W.; Heo, J.; Yoo, G. Thermally activated trap charges responsible for hysteresis in multilayer MoS2 field-effect transistors. Appl. Phys. Lett. 2016, 108, 083102. [Google Scholar] [CrossRef]

- Kim, J.; Jeong, J.; Lee, S.; Jeong, S.; Roh, Y. Analysis of asymmetrical hysteresis phenomena observed in TMD-based field effect transistors. AIP Adv. 2018, 8, 095114. [Google Scholar] [CrossRef]

- Mathew, S.; Reiprich, J.; Narasimha, S.; Abedin, S.; Kurtash, V.; Thiele, S.; Hähnlein, B.; Scheler, T.; Flock, D.; Jacobs, H.O.; et al. Three-Dimensional MoS2 Nanosheet Structures: CVD Synthesis, Characterization, and Electrical Properties. Crystals 2023, 13, 448. [Google Scholar] [CrossRef]

- Lee, C.; Yan, H.; Brus, L.; Heinz, T.; Hone, J.; Ryu, S. Anomalous Lattice Vibrations of Single- and Few-Layer MoS2. ACS Nano 2010, 4, 2695–2700. [Google Scholar] [CrossRef] [PubMed]

- Li, H.; Zhang, Q.; Yap, C.C.R.; Tay, B.K.; Edwin, T.H.T.; Olivier, A.; Baillargeat, D. From bulk to monolayer MoS2: Evolution of Raman scattering. Adv. Funct. Mater. 2012, 22, 1385–1390. [Google Scholar] [CrossRef]

- Jeong, S.; Shin, H.Y.; Shin, R.; Jo, W.; Yoon, S.; Rübhausen, M. Raman scattering studies of the lattice dynamics in layered MoS2. J. Korean Phys. Soc. 2015, 66, 1575–1580. [Google Scholar] [CrossRef]

- O’Brien, M.; McEvoy, N.; Hanlon, D.; Hallam, T.; Coleman, J.N.; Duesberg, G.S. Mapping of low-frequency Raman modes in CVD-grown transition metal dichalcogenides: Layer number, stacking orientation and resonant effects. Sci. Rep. 2016, 6, 19476. [Google Scholar] [CrossRef] [PubMed]

- Choi, W.; Cho, M.Y.; Konar, A.; Lee, J.H.; Cha, G.B.; Hong, S.C.; Kim, S.; Kim, J.; Jena, D.; Joo, J.; et al. High-detectivity multilayer MoS2 phototransistors with spectral response from ultraviolet to infrared. Adv. Mater. 2012, 24, 5832–5836. [Google Scholar] [CrossRef] [PubMed]

- Qiu, H.; Xu, T.; Wang, Z.; Ren, W.; Nan, H.; Ni, Z.; Chen, Q.; Yuan, S.; Miao, F.; Song, F.; et al. Hopping transport through defect-induced localized states in molybdenum disulphide. Nat. Commun. 2013, 4, 2642. [Google Scholar] [CrossRef]

- Zou, X.; Xu, J.; Huang, H.; Zhu, Z.; Wang, H.; Li, B.; Liao, L.; Fang, G. A comparative study on top-gated and bottom-gated multilayer MoS2 transistors with gate stacked dielectric of Al2O3/HfO2. Nanotechnology 2018, 29, 245201. [Google Scholar] [CrossRef]

- Kurtash, V.; Mathew, S.; Thiele, S.; Scheler, T.; Reiprich, J.; Hähnlein, B.; Stauffenberg, J.; Manske, E.; Narasimha, S.; Abedin, S.; et al. Hysteresis Associated with Intrinsic-Oxide Traps in Gate-Tunable Tetrahedral CVD-MoS2 Memristor. In Proceedings of the 2022 IEEE 22nd International Conference on Nanotechnology (NANO), Palma de Mallorca, Spain, 4–8 July 2022; pp. 527–530. [Google Scholar] [CrossRef]

- Guo, Y.; Wei, X.; Shu, J.; Liu, B.; Yin, J.; Guan, C.; Han, Y.; Gao, S.; Chen, Q. Charge trapping at the MoS2-SiO2 interface and its effects on the characteristics of MoS2 metal-oxide-semiconductor field effect transistors. Appl. Phys. Lett. 2015, 106, 103109. [Google Scholar] [CrossRef]

- Schroder, D.K. Semiconductor Material and Device Characterization; John Wiley & Sons: Hoboken, NJ, USA, 2015. [Google Scholar]

- Mitta, S.B.; Choi, M.S.; Nipane, A.; Ali, F.; Kim, C.; Teherani, J.T.; Hone, J.; Yoo, W.J. Electrical characterization of 2D materials-based field-effect transistors. 2D Mater. 2020, 8, 012002. [Google Scholar] [CrossRef]

- Dev, D.; Krishnaprasad, A.; Kalita, H.; Das, S.; Rodriguez, V.; Calderon Flores, J.; Zhai, L.; Roy, T. High quality gate dielectric/MoS2 interfaces probed by the conductance method. Appl. Phys. Lett. 2018, 112, 232101. [Google Scholar] [CrossRef]

| Parameter | Units | FL-FET | TF-FET |

|---|---|---|---|

| ( = 40 V) | nA | ∼6 | ∼40 |

| ( = V) | fA | ∼18 | ∼15 |

| - | ∼ | ∼ | |

| (Linear Extrapolation) | V | 12 | 22 |

| cm2/Vs | 0.02 | 0.17 |

| Parameters | FL MoS2 FET | TF MoS2 FET |

|---|---|---|

| [states/cm2-eV] | ||

| [states/cm2-eV] | ||

| [states/cm2-eV] | ∼ | ∼ |

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Abedin, S.; Kurtash, V.; Mathew, S.; Thiele, S.; Jacobs, H.O.; Pezoldt, J. Defects Contributing to Hysteresis in Few-Layer and Thin-Film MoS2 Memristive Devices. Materials 2024, 17, 1350. https://doi.org/10.3390/ma17061350

Abedin S, Kurtash V, Mathew S, Thiele S, Jacobs HO, Pezoldt J. Defects Contributing to Hysteresis in Few-Layer and Thin-Film MoS2 Memristive Devices. Materials. 2024; 17(6):1350. https://doi.org/10.3390/ma17061350

Chicago/Turabian StyleAbedin, Saadman, Vladislav Kurtash, Sobin Mathew, Sebastian Thiele, Heiko O. Jacobs, and Jörg Pezoldt. 2024. "Defects Contributing to Hysteresis in Few-Layer and Thin-Film MoS2 Memristive Devices" Materials 17, no. 6: 1350. https://doi.org/10.3390/ma17061350