Demonstration of 10 nm Ferroelectric Al0.7Sc0.3N-Based Capacitors for Enabling Selector-Free Memory Array

Abstract

1. Introduction

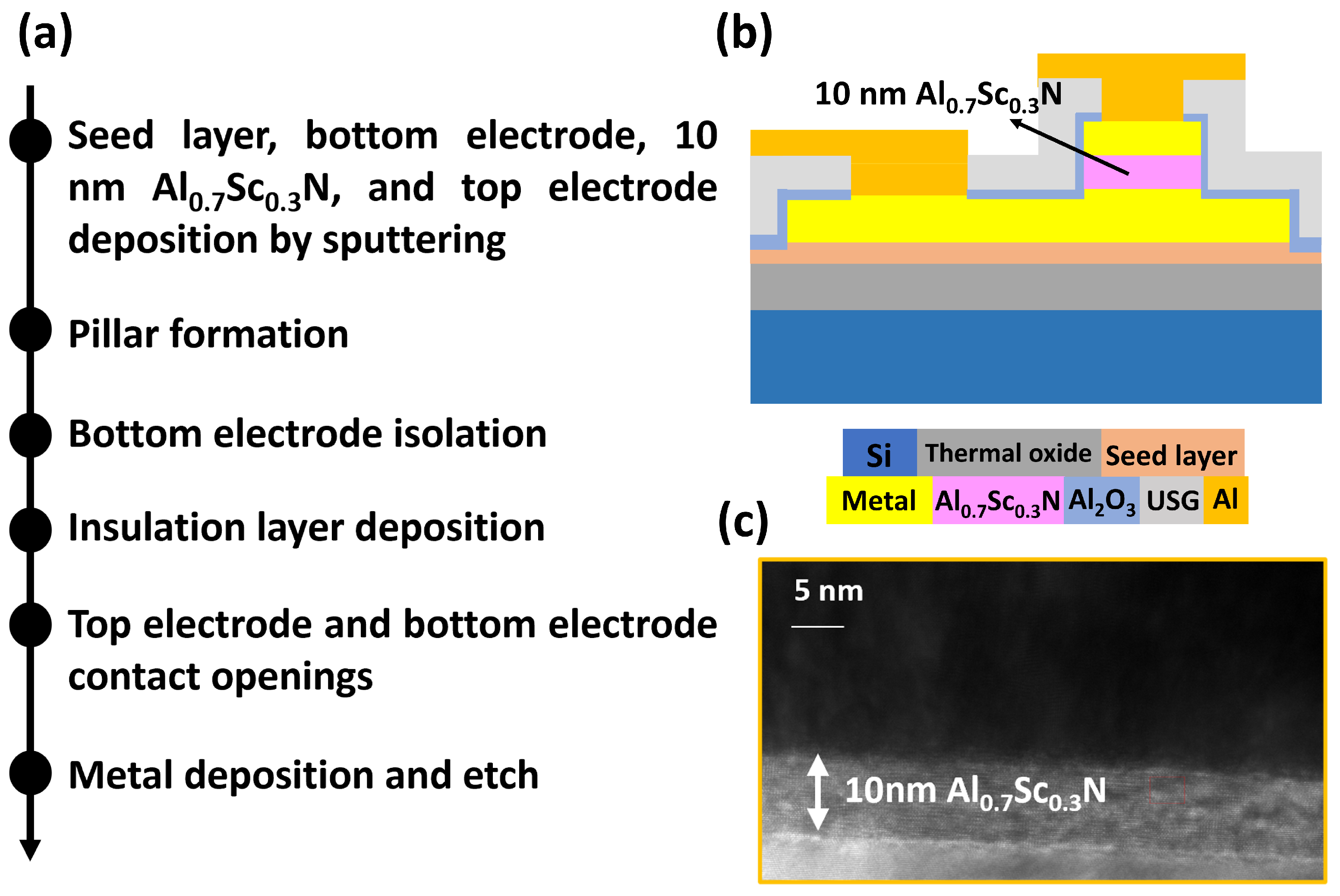

2. Experiment and Method

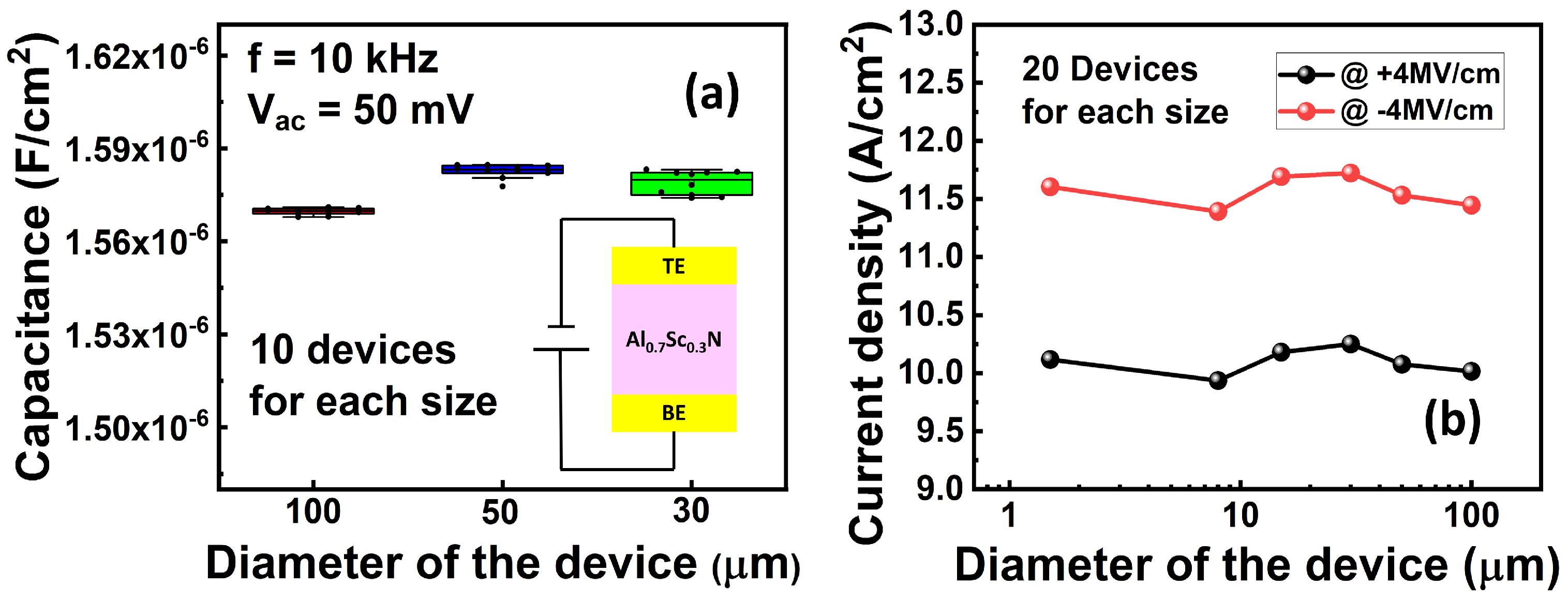

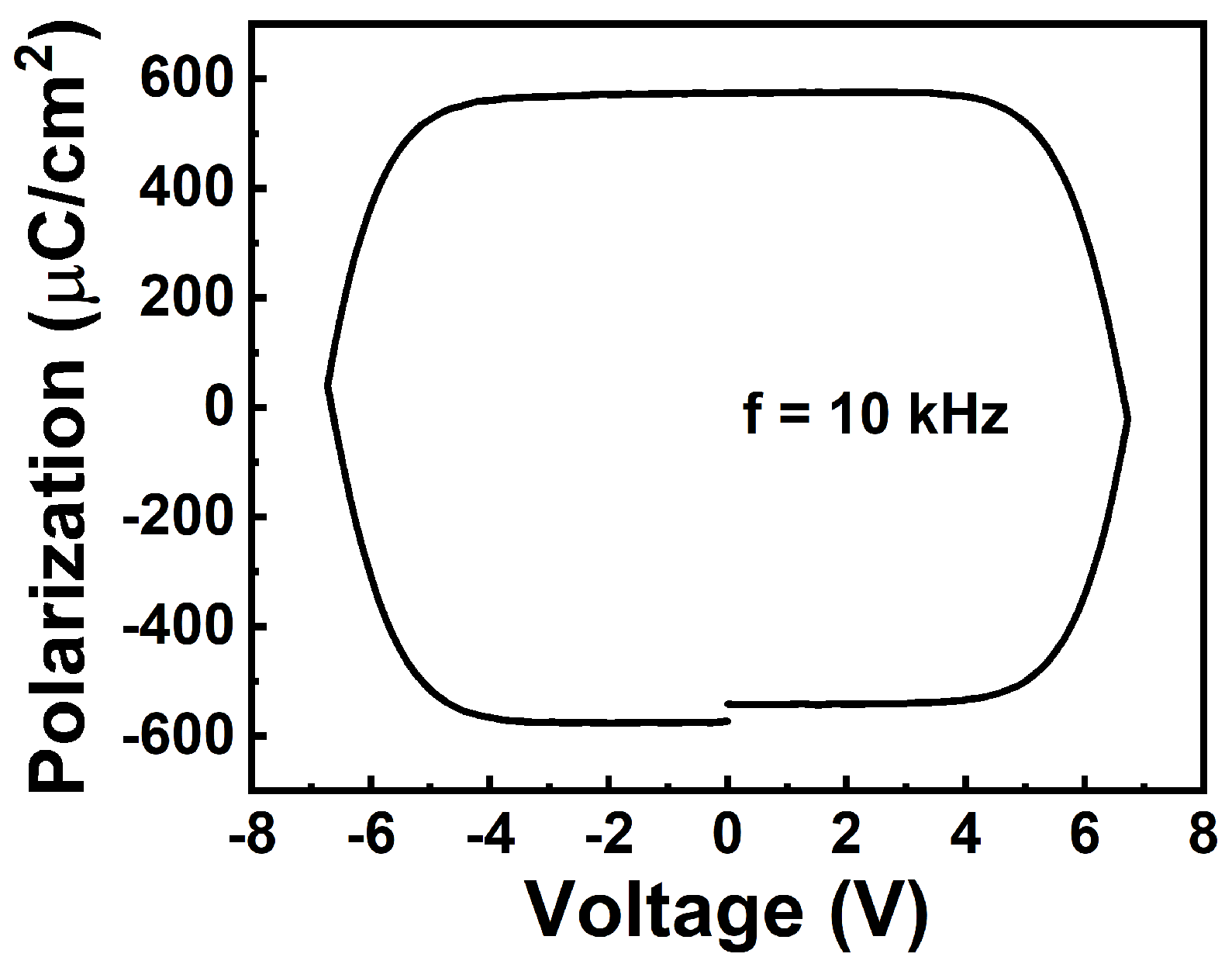

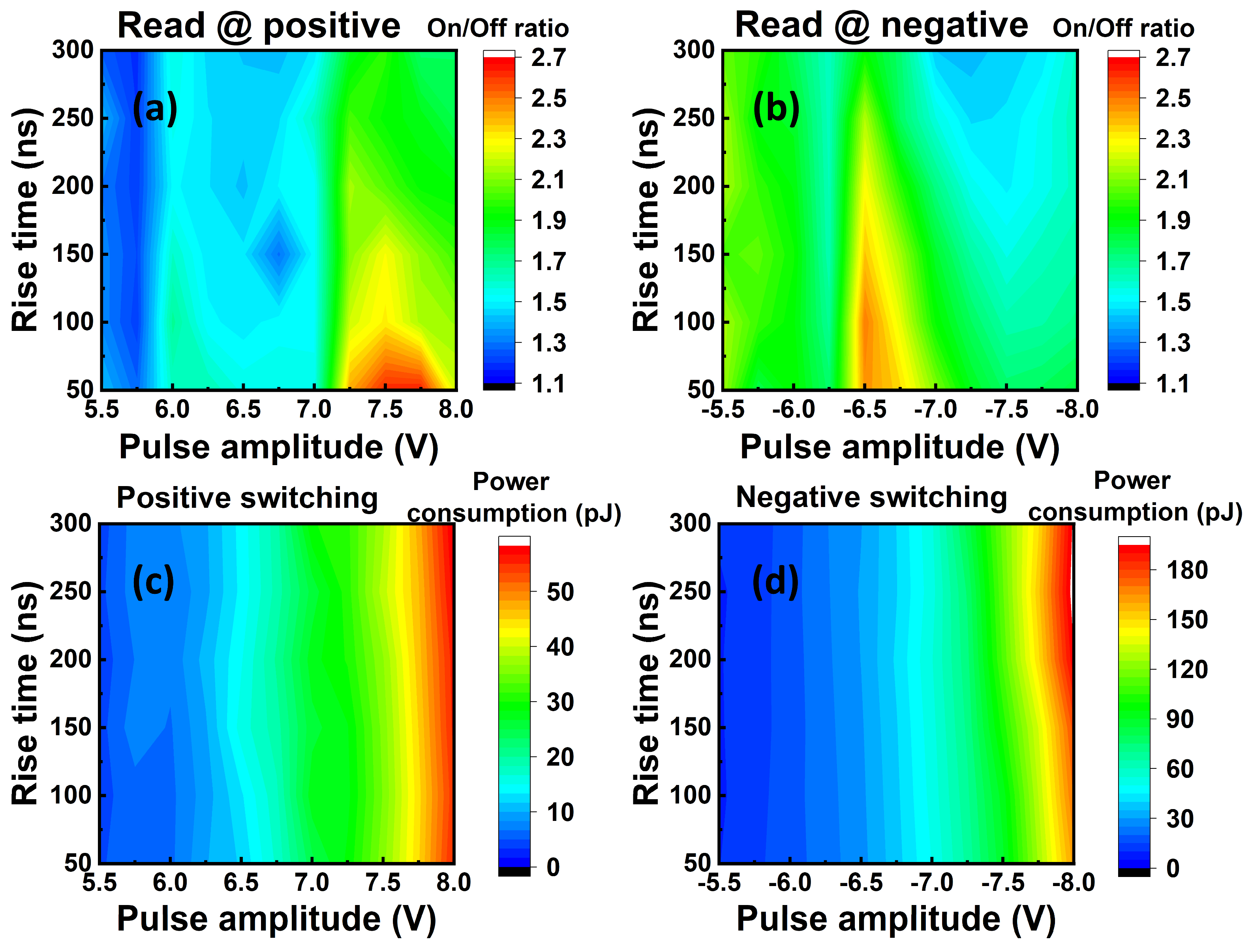

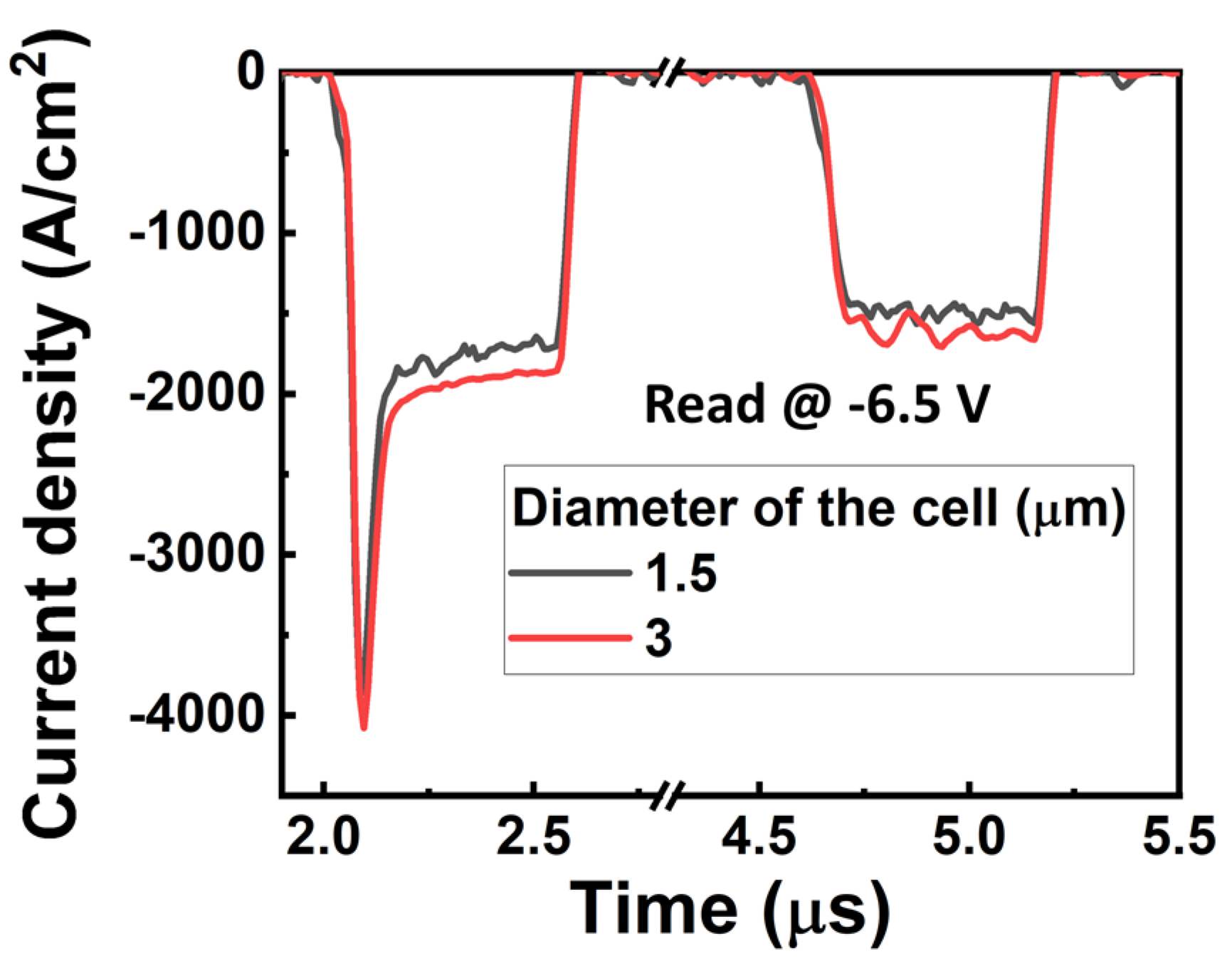

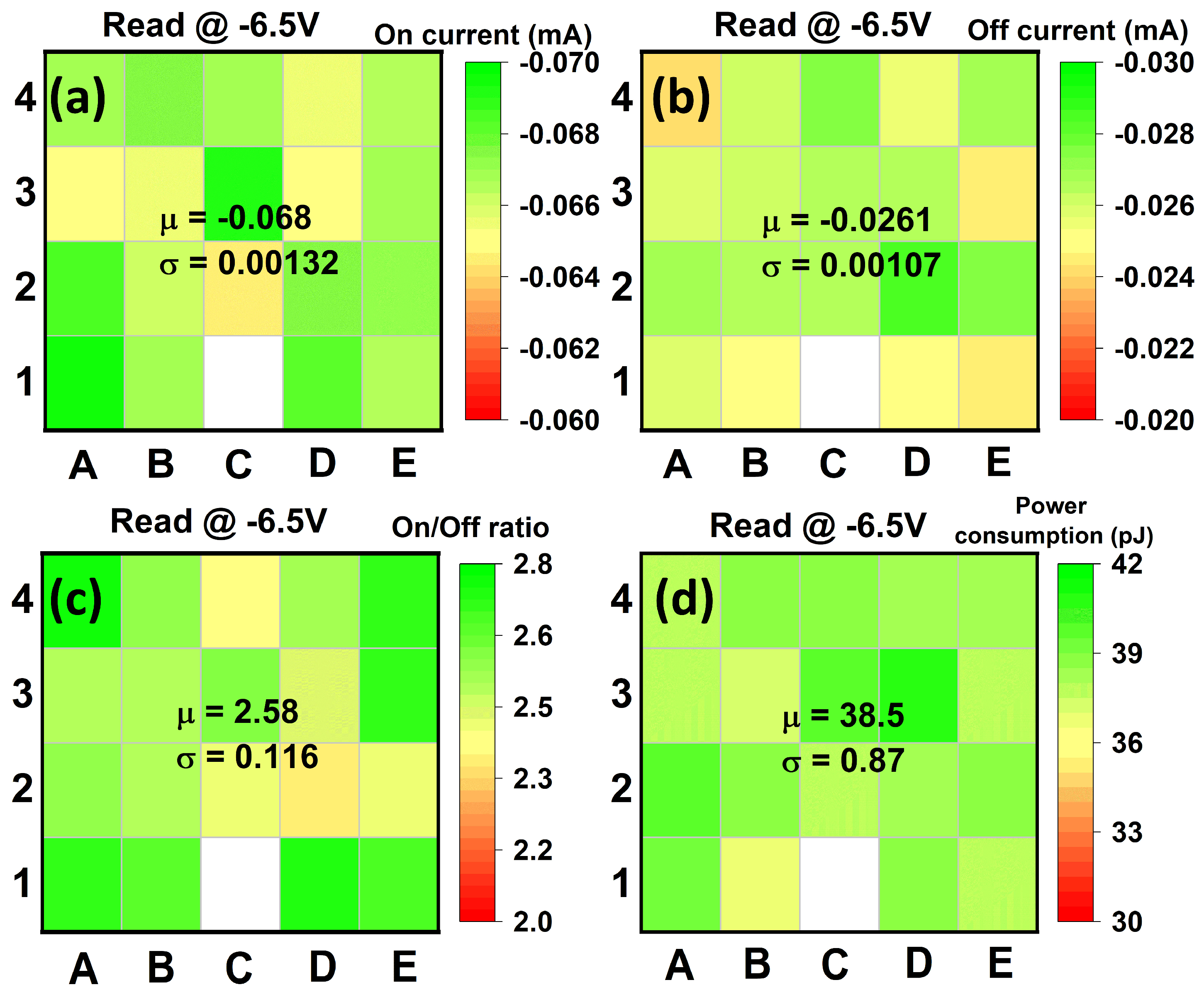

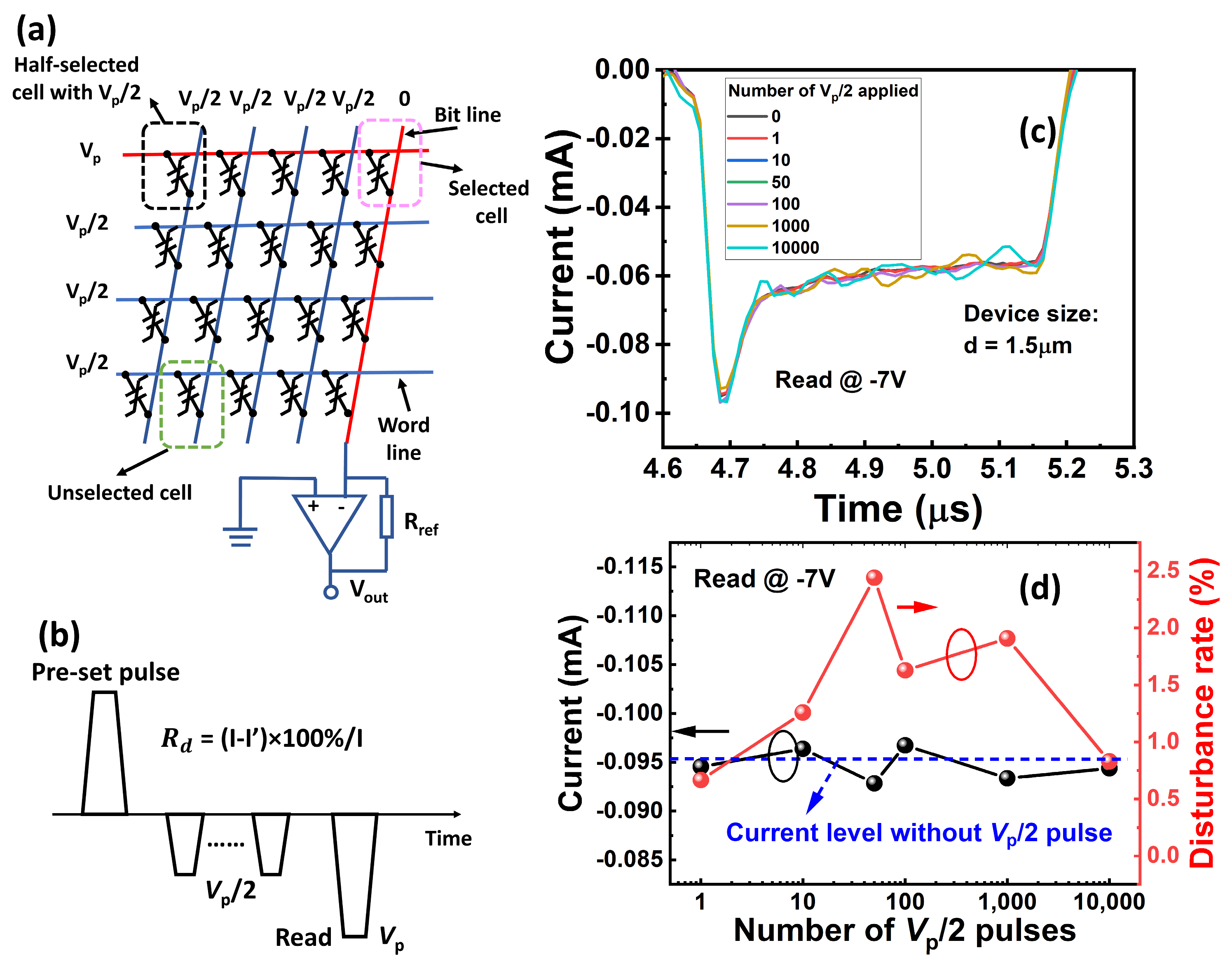

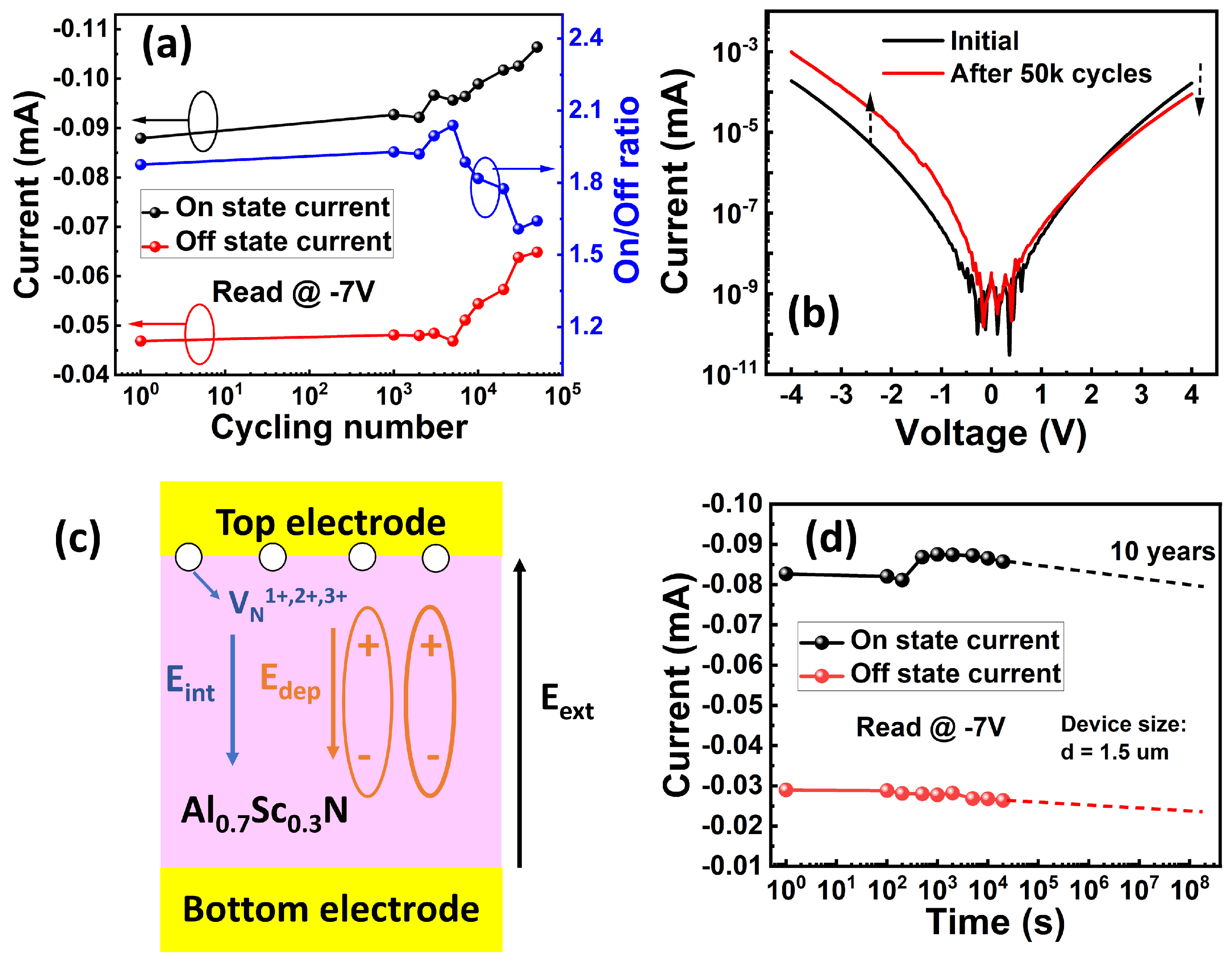

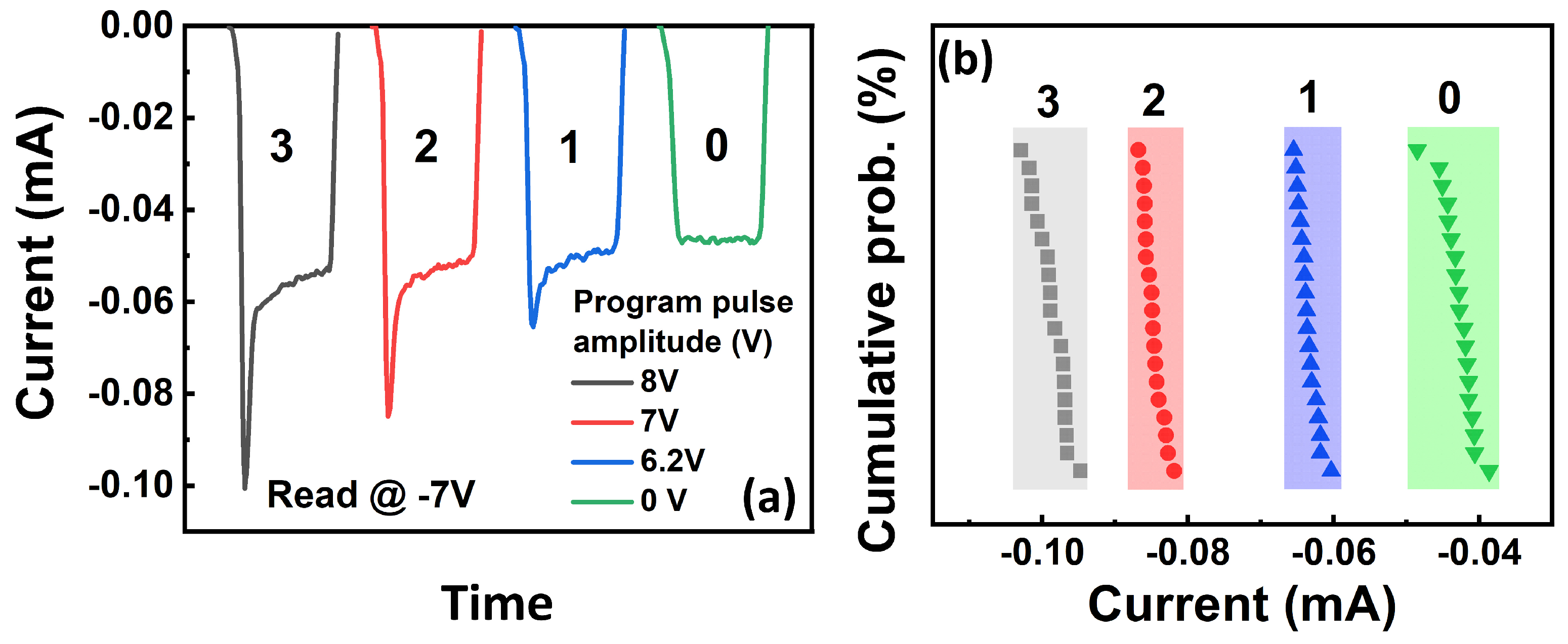

3. Results and Discussion

4. Conclusions

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

References

- Mikolajick, T.; Dehm, C.; Hartner, W.; Kasko, I.; Kastner, M.J.; Nagel, N.; Moert, M.; Mazure, C. FeRAM Technology for High Density Applications. Microelectron. Reliab. 2001, 41, 947–950. [Google Scholar] [CrossRef]

- Francois, T.; Grenouillet, L.; Coignus, J.; Blaise, P.; Carabasse, C.; Vaxelaire, N.; Magis, T.; Aussenac, F.; Loup, V.; Pellissier, C.; et al. Demonstration of BEOL-compatible Ferroelectric Hf0.5Zr0.5O2 Scaled FeRAM Co-integrated with 130nm CMOS for Embedded NVM Applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 15.7.1–15.7.4. [Google Scholar]

- Okuno, J.; Kunihiro, T.; Konishi, K.; Maemura, H.; Shuto, Y.; Sugaya, F.; Materano, M.; Ali, T.; Kuehnel, K.; Seidel, K.; et al. SoC Compatible 1T1C FeRAM Memory Array Based on Ferroelectric Hf0.5Zr0.5O2. In Proceedings of the 2020 IEEE Symposium on VLSI Technology, Honolulu, HI, USA, 16–19 June 2020. [Google Scholar]

- Francois, T.; Coignus, J.; Makosiej, A.; Giraud, B.; Carabasse, C.; Barbot, J.; Martin, S.; Castellani, N.; Magis, T.; Grampeix, H.; et al. 16kbit HfO2:Si-based 1T-1C FeRAM arrays demonstrating high performance operation and solder reflow compatibility. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 33.1.1–33.1.4. [Google Scholar]

- Chen, W. Selector-Free cross-point memory architecture based on ferroelectric MFM capacitors. In Proceedings of the 2019 IEEE 11th International Memory Workshop (IMW), Monterey, CA, USA, 12–15 May 2019. [Google Scholar]

- Fichtner, S.; Wolff, N.; Lofink, F.; Kienle, L.; Wagner, B. AlScN: A III-V Semiconductor Based Ferroelectric. J. Appl. Phys. 2019, 125, 114103. [Google Scholar] [CrossRef]

- Mikolajick, T.; Slesazeck, S.; Mulaosmanovic, H.; Park, M.H.; Fichtner, S.; Lomenzo, P.D.; Hoffmann, M.; Schroeder, U. Next Generation Ferroelectric Materials for Semiconductor Process Integration and Their Applications. J. Appl. Phys. 2021, 129, 100901. [Google Scholar] [CrossRef]

- Yasuoka, S.; Shimizu, T.; Tateyama, A.; Uehara, M.; Yamada, H.; Akiyama, M.; Hiranaga, Y.; Cho, Y.; Funakubo, H. Effects of Deposition Conditions on the Ferroelectric Properties of (Al1−xScx)N Thin Films. J. Appl. Phys. 2020, 128, 114103. [Google Scholar] [CrossRef]

- Chen, L.; Liu, C.; Li, M.; Song, W.; Wang, W.; Wang, Z.; Wang, N.; Zhu, Y. Scandium-Doped Aluminum Nitride for Acoustic Wave Resonators, Filters, and Ferroelectric Memory Applications. ACS Appl. Electron. Mater. 2022, 5, 612–622. [Google Scholar] [CrossRef]

- Tsai, S.L.; Hoshii, T.; Wakabayashi, H.; Tsutsui, K.; Chung, T.K.; Chang, E.Y.; Kakushima, K. On the Thickness Scaling of Ferroelectricity in Al0.78Sc0.22N Films. Jpn. J. Appl. Phys. 2021, 60, SBBA05. [Google Scholar] [CrossRef]

- Yang, W.; Chen, L.; Li, M.; Liu, F.; Liu, X.; Liu, C.; Kang, J. Stress Effect on the Leakage Current Distribution of Ferroelectric Al0.7Sc0.3N Across the Wafer. Appl. Phys. Lett. 2023, 123, 132903. [Google Scholar] [CrossRef]

- Chen, L.; Liu, C.; Wang, Z.; Li, M.; Song, W.; Wang, W.; Zhu, Y. In-wafer stress-dependent leakage current in ferroelectric scandium-doped aluminum nitride. In Proceedings of the 2023 IEEE International Symposium on Applications of Ferroelectrics (ISAF), Cleveland, OH, USA, 23–27 July 2023; pp. 1–3. [Google Scholar]

- Yazawa, K.; Drury, D.; Zakutayev, A.; Brennecka, G.L. Reduced Coercive Field in Epitaxial Thin Film of Ferroelectric Wurtzite Al0.7Sc0.3N. Appl. Phys. Lett. 2021, 118, 162903. [Google Scholar] [CrossRef]

- Drury, D.; Yazawa, K.; Zakutayev, A.; Hanrahan, B.; Brennecka, G.L. High-temperature Ferroelectric Behavior of Al0.7Sc0.3N. Micromachines 2022, 13, 887. [Google Scholar] [CrossRef]

- Mizutani, R.; Yasuoka, S.; Shiraishi, T.; Shimizu, T.; Uehara, M.; Yamada, H.; Akiyama, M.; Sakata, O.; Funakubo, H. Thickness Scaling of (Al0.8Sc0.2)N Films with Remanent Polarization Beyond 100μC/cm–2 around 10 nm in Thickness. Appl. Phys. Express 2021, 14, 105501. [Google Scholar] [CrossRef]

- Olsson, R.H.; Tang, Z.; D’Agati, M. Doping of aluminum nitride and the impact on thin film piezoelectric and ferroelectric device performance. In Proceedings of the 2020 IEEE Custom Integrated Circuits Conference (CICC), Boston, MA, USA, 22–25 March 2020; pp. 1–6. [Google Scholar]

- Rassay, S.; Hakim, F.; Li, C.; Forgey, C.; Choudhary, N.; Tabrizian, R. A Segmented-Target Sputtering Process for Growth of Sub-50 nm Ferroelectric Scandium–Aluminum–Nitride Films with Composition and Stress Tuning. Phys. Status Solidi RRL 2021, 15, 2100087. [Google Scholar] [CrossRef]

- Pirro, M.; Zhao, X.; Herrera, B.; Simeoni, P.; Rinaldi, M. Effect of Substrate-RF on Sub-200 nm Al0.7Sc0.3N Thin Films. Micromachines 2022, 13, 877. [Google Scholar] [CrossRef]

- Chen, L.; Wang, Z.; Liu, C.; Li, M.; Song, W.; Wang, W.; Varghese, B.; Lee, H.K.; Lin, H.; Zhu, Y. Leakage mechanism of ferroelectric Al0.7Sc0.3N ultra-thin film. In Proceedings of the 2023 IEEE International Symposium on Applications of Ferroelectrics (ISAF), Cleveland, OH, USA, 23–27 July 2023; pp. 1–3. [Google Scholar]

- Liu, X.; Wang, D.; Kim, K.H.; Katti, K.; Zheng, J.; Musavigharavi, P.; Miao, J.; Stach, E.A.; Olsson III, R.H.; Jariwala, D. Post-CMOS Compatible Aluminum Scandium Nitride/2D Channel Ferroelectric Field-effect-transistor Memory. Nano Lett. 2021, 21, 3753–3761. [Google Scholar] [CrossRef] [PubMed]

- Kim, K.H.; Oh, S.; Fiagbenu, M.M.A.; Zheng, J.; Musavigharavi, P.; Kumar, P.; Trainor, N.; Aljarb, A.; Wan, Y.; Kim, H.M.; et al. Scalable CMOS Back-end-of-line-compatible AlScN/two-dimensional Channel Ferroelectric field-effect Transistors. Nat. Nanotechnol. 2023, 18, 1044–1050. [Google Scholar] [CrossRef] [PubMed]

- Liu, C.; Wang, Q.; Yang, W.; Cao, T.; Chen, L.; Li, M.; Liu, F.; Loke, D.K.; Kang, J.; Zhu, Y. Multiscale Modeling of Al0.7Sc0.3N-based FeRAM: The steep switching, leakage and selector-free array. In Proceedings of the 2021 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 11–16 December 2021; pp. 8.1.1–8.1.4. [Google Scholar]

- Chen, L.; Liu, C.; Li, M.; Song, W.; Wang, W.; Chen, Z.; Samanta, S.; Lee, H.K.; Zhu, Y. Bipolar and unipolar cycling behavior in ferroelectric scandium-doped aluminum nitride. In Proceedings of the 2022 IEEE International Symposium on Applications of Ferroelectrics (ISAF), Tours, France, 27 June–1 July 2022; pp. 1–3. [Google Scholar]

- Wang, P.; Wang, D.; Vu, N.M.; Chiang, T.; Heron, J.T.; Mi, Z. Fully Epitaxial Ferroelectric ScAlN Grown by Molecular Beam Epitaxy. Appl. Phys. Lett. 2021, 118, 223504. [Google Scholar] [CrossRef]

- Wang, D.; Wang, P.; Mondal, S.; Xiao, Y.; Hu, M.; Mi, Z. Impact of Dislocation Density on the Ferroelectric Properties of ScAlN Grown by Molecular Beam Epitaxy. Appl. Phys. Lett. 2022, 121, 042108. [Google Scholar] [CrossRef]

- Kim, S.J.; Mohan, J.; Summerfelt, S.R.; Kim, J. Ferroelectric Hf0.5Zr0.5O2 Thin Films: A Review of Recent Advances. Jom 2019, 71, 246–255. [Google Scholar] [CrossRef]

- Chen, L.; Song, W.; Wang, W.; Lee, H.K.; Chen, Z.; Zhao, W.; Zhu, Y. KrF Excimer Laser Annealing with an Ultra-Low Laser Fluence for Enabling Ferroelectric HfZrO. IEEE Electron. Device Lett. 2023, 44, 32–35. [Google Scholar] [CrossRef]

- Chen, L.; Wang, L.; Peng, Y.; Feng, X.; Sarkar, S.; Li, S.; Li, B.; Liu, L.; Han, K.; Gong, X.; et al. A van der Waals Synaptic Transistor Based on Ferroelectric Hf0.5Zr0.5O2 and 2D Tungsten Disulfide. Adv. Electron. Mater. 2020, 6, 2000057. [Google Scholar] [CrossRef]

- Schönweger, G.; Wolff, N.; Islam, M.R.; Gremmel, M.; Petraru, A.; Kienle, L.; Kohlstedt, H.; Fichtner, S. In-Grain Ferroelectric Switching in Sub-5 nm Thin Al0.74Sc0.26N Films at 1 V. Adv. Sci. 2023, 10, 2302296. [Google Scholar] [CrossRef]

- Zheng, J.X.; Fiagbenu, M.M.A.; Esteves, G.; Musavigharavi, P.; Gunda, A.; Jariwala, D.; Stach, E.A.; Olsson, R.H. Ferroelectric Behavior of Sputter Deposited Al0.72Sc0.28N Approaching 5 nm Thickness. Appl. Phys. Lett. 2023, 122, 222901. [Google Scholar] [CrossRef]

- Wang, D.; Wang, P.; Mondal, S.; Hu, M.; Wang, D.; Wu, Y.; Ma, T.; Mi, Z. Thickness Scaling Down to 5 nm of Ferroelectric ScAlN on CMOS Compatible Molybdenum Grown by Molecular Beam Epitaxy. Appl. Phys. Lett. 2023, 122, 052101. [Google Scholar] [CrossRef]

- Akiyama, M.; Kano, K.; Teshigahara, A. Influence of Growth Temperature and Scandium Concentration on Piezoelectric Response of Scandium Aluminum Nitride Alloy Thin Films. Appl. Phys. Lett. 2009, 95, 162107. [Google Scholar] [CrossRef]

- Jain, P.; Arslan, U.; Sekhar, M.; Lin, B.C.; Wei, L.; Sahu, T.; Alzate-Vinasco, J.; Vangapaty, A.; Meterelliyoz, M.; Strutt, N.; et al. 13.2 A 3.6Mb 10.1Mb/mm2 embedded non-volatile ReRAM macro in 22nm FinFET technology with adaptive forming/set/reset schemes yielding down to 0.5 V with sensing time of 5ns at 0.7V. In Proceedings of the 2019 IEEE International Solid-State Circuits Conference (ISSCC), San Francisco, CA, USA, 17–21 February 2019; pp. 212–214. [Google Scholar]

- Alzate, J.G.; Arslan, U.; Bai, P.; Brockman, J.; Chen, Y.J.; Das, N.; Fischer, K.; Ghani, T.; Heil, P.; Hentges, P.; et al. 2 MB array-level demonstration of STT-MRAM process and performance towards L4 cache applications. In Proceedings of the 2019 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 7–11 December 2019; pp. 2.4.1–2.4.4. [Google Scholar]

- Ni, K.; Grisafe, B.; Chakraborty, W.; Saha, A.K.; Dutta, S.; Jerry, M.; Smith, J.A.; Gupta, S.; Datta, S. In-memory computing primitive for sensor data fusion in 28 nm HKMG FeFET technology. In Proceedings of the 2018 IEEE International Electron Devices Meeting (IEDM), San Francisco, CA, USA, 1–5 December 2018; pp. 16.1.1–16.1.4. [Google Scholar]

- Okuno, J.; Kunihiro, T.; Konishi, K.; Maemura, H.; Shuto, Y.; Sugaya, F.; Materano, M.; Ali, T.; Lederer, M.; Kuehnel, K.; et al. High-endurance and low-voltage operation of 1T1C FeRAM arrays for nonvolatile memory application. In Proceedings of the 2021 IEEE International Memory Workshop (IMW), Dresden, Germany, 16–19 May 2021; pp. 1–3. [Google Scholar]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2024 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Chen, L.; Liu, C.; Lee, H.K.; Varghese, B.; Ip, R.W.F.; Li, M.; Quek, Z.J.; Hong, Y.; Wang, W.; Song, W.; et al. Demonstration of 10 nm Ferroelectric Al0.7Sc0.3N-Based Capacitors for Enabling Selector-Free Memory Array. Materials 2024, 17, 627. https://doi.org/10.3390/ma17030627

Chen L, Liu C, Lee HK, Varghese B, Ip RWF, Li M, Quek ZJ, Hong Y, Wang W, Song W, et al. Demonstration of 10 nm Ferroelectric Al0.7Sc0.3N-Based Capacitors for Enabling Selector-Free Memory Array. Materials. 2024; 17(3):627. https://doi.org/10.3390/ma17030627

Chicago/Turabian StyleChen, Li, Chen Liu, Hock Koon Lee, Binni Varghese, Ronald Wing Fai Ip, Minghua Li, Zhan Jiang Quek, Yan Hong, Weijie Wang, Wendong Song, and et al. 2024. "Demonstration of 10 nm Ferroelectric Al0.7Sc0.3N-Based Capacitors for Enabling Selector-Free Memory Array" Materials 17, no. 3: 627. https://doi.org/10.3390/ma17030627

APA StyleChen, L., Liu, C., Lee, H. K., Varghese, B., Ip, R. W. F., Li, M., Quek, Z. J., Hong, Y., Wang, W., Song, W., Lin, H., & Zhu, Y. (2024). Demonstration of 10 nm Ferroelectric Al0.7Sc0.3N-Based Capacitors for Enabling Selector-Free Memory Array. Materials, 17(3), 627. https://doi.org/10.3390/ma17030627