Al2O3 Layers Grown by Atomic Layer Deposition as Gate Insulator in 3C-SiC MOS Devices

Abstract

1. Introduction

2. Materials and Methods

3. Discussion

4. Conclusions

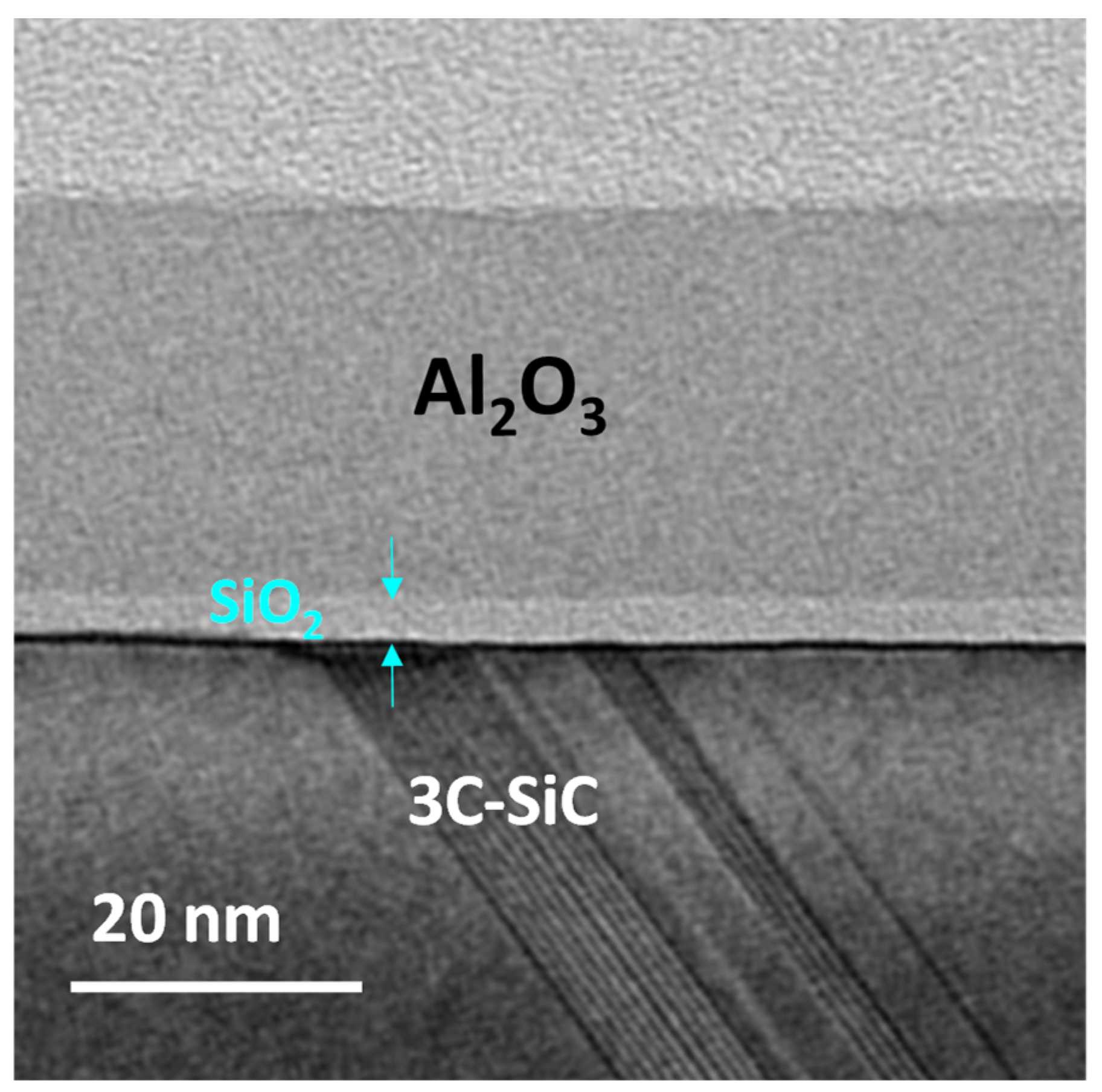

- A thin (5 nm) SiO2 IL between the Al2O3 and the 3C-SiC is useful to ensure the quality of ALD growth and to maximize the insulator/semiconductor band offset;

- The Al2O3 is a valid alternative to the conventional thermally grown single SiO2 as gate insulator for 3C-SiC MOS-based devices. In fact, the Al2O3 layers showed a high permittivity (~8), which produced a significant reduction in the negative flat band voltage shift that is usually observed with SiO2;

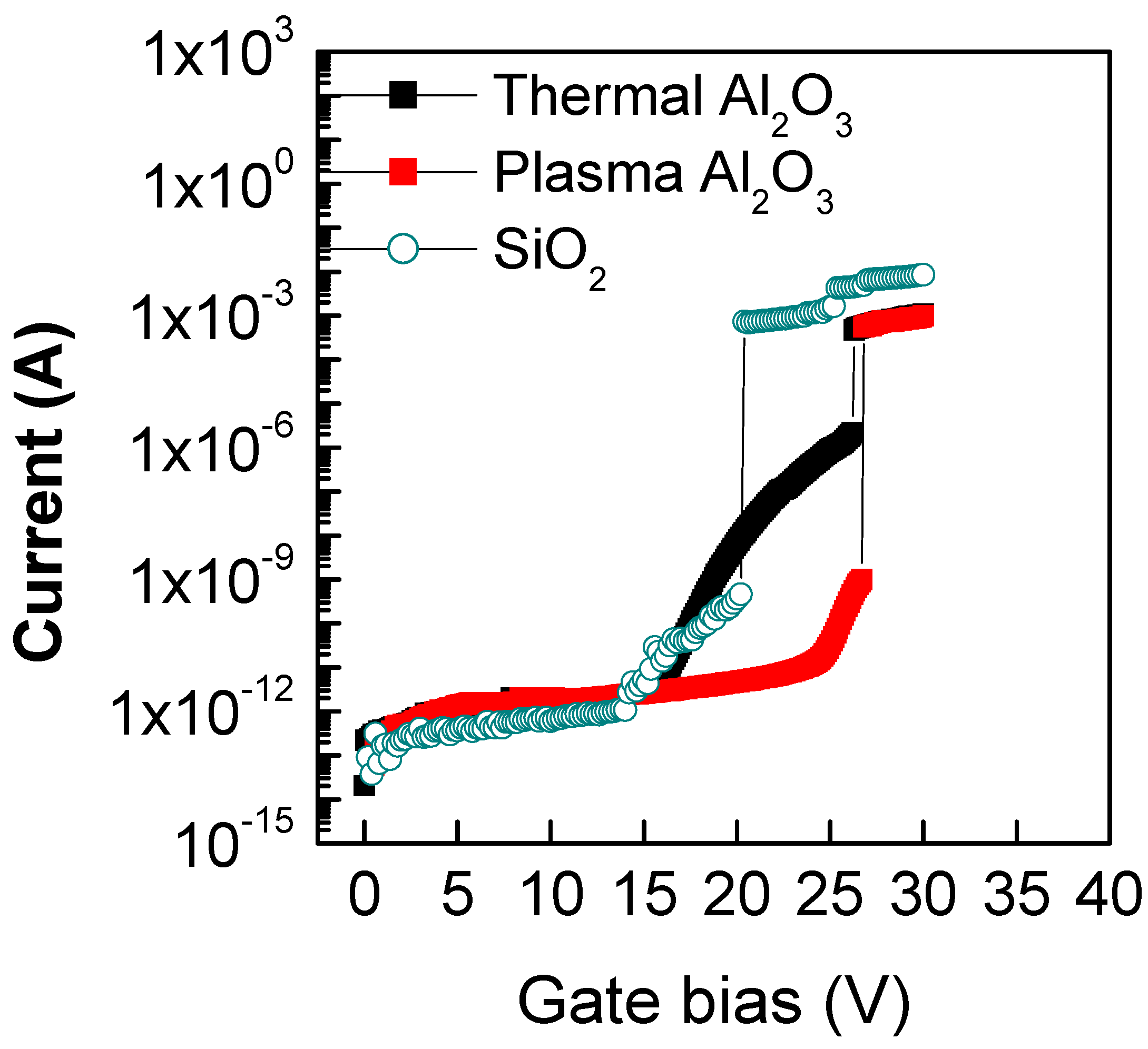

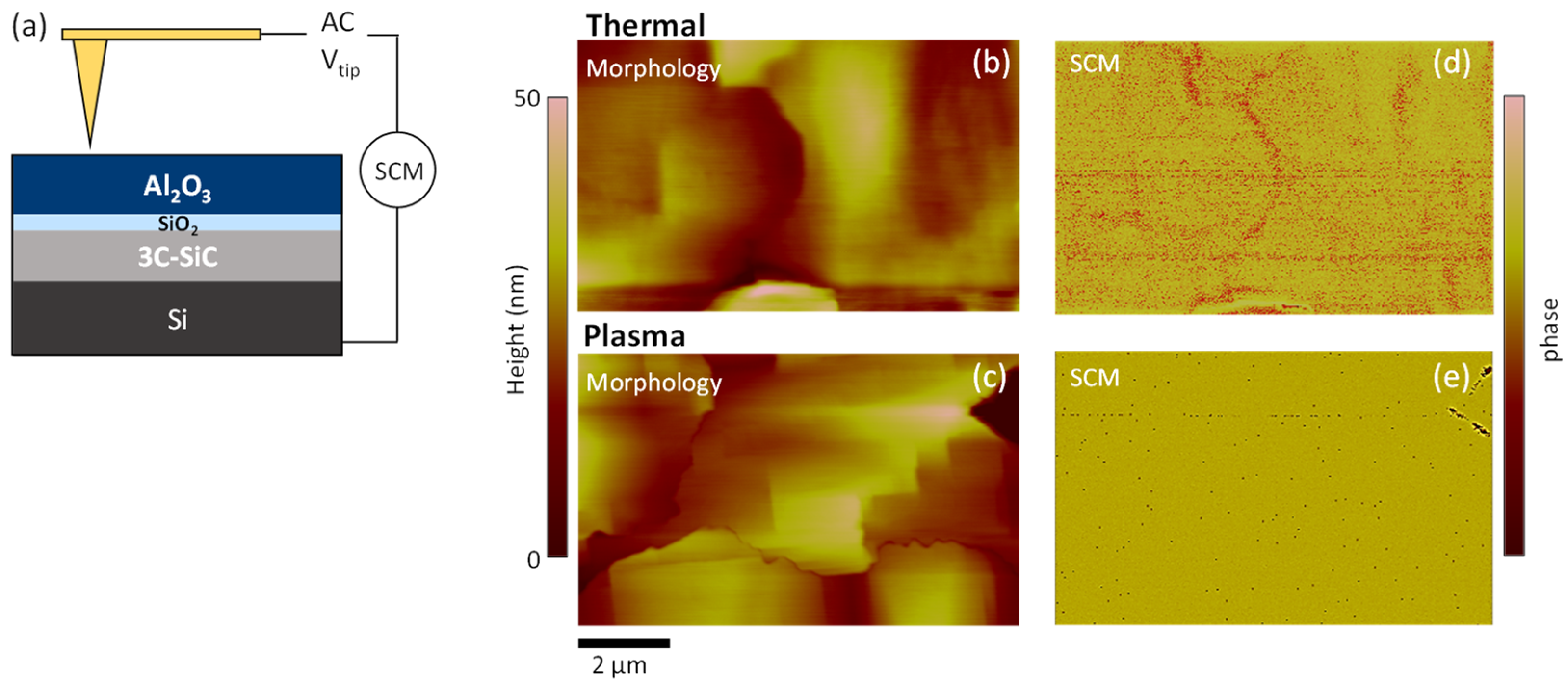

- A different electrical behavior was found between thermal- and plasma-enhanced Al2O3 both by investigations on macroscopic MOS capacitors and at the nanoscale using SCM analysis. In fact, although both systems ensure an electrical breakdown over 26 V, the T-Al2O3/SiO2/3C-SiC stack exhibits early leakage phenomena already from 15 V. Moreover, the T-Al2O3/SiO2/3C-SiC is characterised by a non-uniform SCM map compared to the PE-Al2O3/SiO2/3C-SiC. This difference can be correlated to a different Al2O3 quality obtained through the two different oxidation processes (T- or PE-), resulting in an inhomogeneous charge trapping behavior and permittivity.

Author Contributions

Funding

Institutional Review Board Statement

Informed Consent Statement

Data Availability Statement

Acknowledgments

Conflicts of Interest

Abbreviations

| ALD | Atomic Layer Deposition |

| T-ALD | Thermal-ALD |

| PE-ALD | Plasma Enanched-ALD |

| NIOTs | Near Interface Oxide Traps |

| MOSFET | Metal Oxide Semiconductor Field Effect Transistor |

| MOS | Metal Oxide Semiconductor |

| IL | Interlayer |

| High-κ | High permittivity (κ) dielectrics |

| TEM | Transmission Electron Microscopy |

| AFM | Atomic Force Microscopy |

| SCM | Scanning Capacitance Microscopy |

References

- Levinshein, M.; Sergey, L.; Shur, M. Properties of Advanced Semiconductor Materials: GaN, AIN, InN, BN, SiC, SiGe, 1st ed.; John Wiley & Sons, Inc.: New York, NY, USA, 2001. [Google Scholar]

- Bimberg, D.; Altarelli, M.; Lipari, N. A calculation of valence band masses, exciton and acceptor energies and the ground state properties of the electron-hole liquid in cubic SiC. Solid State Commun. 1981, 40, 437–440. [Google Scholar] [CrossRef]

- Itoh, A.; Akita, H.; Kimoto, T.; Matsunami, H. High quality 4H-SiC homoepitaxial layers grown by step controlled epitaxy. Appl. Phys. Lett. 1994, 65, 1400–1402. [Google Scholar] [CrossRef]

- Arvanitopoulos, A.E.; Antoniou, M.; Perkins, S.; Jennings, M.; Guadas, M.B.; Gyftakis, K.N.; Lophitis, N. On the Suitability of 3C-Silicon Carbide as an Alternative to 4H-Silicon Carbide for Power Diodes. IEEE Trans. Ind. Appl. 2019, 55, 4080–4090. [Google Scholar] [CrossRef]

- La Via, F.; Severino, A.; Anzalone, R.; Bongiorno, C.; Litrico, G.; Mauceri, M.; Schoeler, M.; Schuh, P.; Wellmann, P. From thin film to bulk 3C-SiC growth: Understanding the mechanism of defects reduction. Mater. Sci. Semicond. Process. 2018, 78, 57–68. [Google Scholar] [CrossRef]

- Roccaforte, F.; Greco, G.; Fiorenza, P.; Di Franco, S.; Giannazzo, F.; La Via, F.; Zielinski, M.; Mank, H.; Jokubavicius, V.; Yakimova, R. Towards vertical Schottky diodes on bulk cubic silicon carbide (3C-SiC). Appl. Surf. Sci. 2022, 606, 154896. [Google Scholar] [CrossRef]

- Giannazzo, F.; Greco, G.; Di Franco, S.; Fiorenza, P.; Deretzis, I.; La Magna, A.; Bongiorno, C.; Zimbone, M.; La Via, F.; Zielinski, M.; et al. Impact of Stacking Faults and Domain Boundaries on the Electronic Transport in Cubic Silicon Carbide Probed by Conductive Atomic Force Microscopy. Adv. Electron. Mater. 2020, 6, 1901171. [Google Scholar] [CrossRef]

- Renz, A.B.; Li, F.; Vavasour, O.J.; Gammon, P.M.; Dai, T.; Baker, G.W.C.; La Via, F.; Zielinski, M.; Zhang, L.; Grant, N.E.; et al. Initial investigations into the MOS interface of freestanding 3C-SiC layers for device applications. Semicond. Sci. Technol. 2021, 36, 055006. [Google Scholar] [CrossRef]

- Afanasev, V.V.; Bassler, M.; Pensl, G.; Schulz, M. Intrinsic SiC/SiO2 Interface States. Phys. Status Solidi (A) 1997, 162, 321–337. [Google Scholar] [CrossRef]

- Li, F.; Roccaforte, F.; Greco, G.; Fiorenza, P.; La Via, F.; Pérez-Tomas, A.; Evans, J.E.; Fisher, C.A.; Monaghan, F.A.; Mawby, P.A.; et al. Status and Prospects of Cubic Silicon Carbide Power Electronics Device Technology. Materials 2021, 14, 5831. [Google Scholar] [CrossRef]

- Esteve, R. Fabrication and Characterization of 3C- and 4H-SiC MOSFETs. Ph.D. Thesis, KTH Royal Institute of Technology, School of Information and Communication Technology (ICT), Integrated Devices and Circuits, Stockholm, Sweden, 2011. [Google Scholar]

- Lee, K.K.; Ishida, Y.; Ohshima, T.; Kojima, K.; Tanaka, Y.; Takahashi, T.; Okumura, H.; Arai, K.; Kamiya, T. N-Channel MOSFETs Fabricated on Homoepitaxy-Grown 3C-SiC Films. IEEE Electron Device Lett. 2003, 24, 466–468. [Google Scholar]

- Roccaforte, F.; Fiorenza, P.; Greco, G.; Vivona, M.; Nigro, R.L.; Giannazzo, F.; Patti, A.; Saggio, M. Recent advances on dielectrics technology for SiC and GaN power devices. Appl. Surf. Sci. 2014, 301, 9–18. [Google Scholar] [CrossRef]

- Lophitis, N.; Arvanitopoulos, A.; Jennings, M.R.; Mawby, P.A.; Antoniou, M. On the 3C-SiC/SiO2 n-MOS interface and the creation of a calibrated model for the Electrons’ Inversion Layer Mobility covering a wide range of operating temperatures and applied gate voltage. In Proceedings of the IEEE Workshop on Wide Bandgap Power Devices and Applications in Europe (WiPDA Europe), Coventry, UK, 18–20 September 2022. [Google Scholar]

- Ciobanu, F.; Pensl, G.; Nagasawa, H.; Schöner, A.; Dimitrijev, S.; Cheong, K.Y.; Afanas’ev, V.V.; Wagner, G. Traps at the Interface of 3C-SiC/SiO2-MOS-Structures. In Materials Science Forum; Trans Tech Publications Ltd.: Zurich, Switzerland, 2003; Volume 433, pp. 551–554. [Google Scholar]

- Oka, R.; Yamamoto, K.; Akamine, H.; Wang, D.; Nakashima, H.; Hishiki, S.; Kawamura, K. High interfacial quality metal-oxide-semiconductor capacitor on (111) oriented 3C-SiC with Al2O3 interlayer and its internal charge analysis. Jpn. J. Appl. Phys. 2020, 59, SGGD17. [Google Scholar] [CrossRef]

- Cherkaoui, K.; Blake, A.; Gomeniuk, Y.Y.; Lin, J.; Sheehan, B.; White, M.; Hurley, P.K.; Ward, P.J. Investigating positive oxide charge in the SiO2/3C-SiC MOS system. AIP Adv. 2018, 8, 085323. [Google Scholar] [CrossRef]

- Baliga, B.J. Silicon Carbide Power Devices; World Scientific Publishing Co. Pte. Ltd.: Singapore, 2005. [Google Scholar]

- Lo Nigro, R.; Fiorenza, P.; Greco, G.; Schilirò, E.; Roccaforte, F. Structural and Insulating Behaviour of High-Permittivity Binary Oxide Thin Films for Silicon Carbide and Gallium Nitride Electronic Devices. Materials 2022, 15, 830. [Google Scholar] [CrossRef]

- Gao, K.Y.; Seyller, T.; Ley, L.; Ciobanu, F.; Pensl, G.; Tadich, A.; Riley, J.D.; Leckey, R.G.C. Al2O3 prepared by atomic layer deposition as gate dielectric on 6H-SiC(0001). Appl. Phys. Lett. 2003, 83, 1830. [Google Scholar] [CrossRef]

- Yu, Y.; Jun, H.; Yun, D.Y.; An, K.; Zhan, C.; Yu, X. Influences of high-temperature annealing on atomic layer deposited Al2O3/4H-SiC. Chin. Phys. B 2013, 22, 07810. [Google Scholar]

- Lin, H.C.; Ye, P.D.; Wilk, G.D. Leakage current and breakdown electric-field studies on ultrathin atomic-layer-deposited Al2O3 on GaAs. Appl. Phys. Lett. 2005, 87, 182904. [Google Scholar] [CrossRef]

- Avice, M.; Grossner, U.; Pintilie, I.; Svesson, G.; Servidori, M.; Nipoti, R.; Nilsen, O.; Fjellvag, H. Low Density of Near-Interface Traps at the Al2O3/4H-SiC Interface with Al2O3 Made by Low Temperature Oxidation of Al. Mater. Sci. Forum 2007, 897, 135–138. [Google Scholar]

- Kääriäinen, T.; Cameron, D.; Kääriäinen, M.-L.; Sherman, A. Atomic Layer Deposition, Principles Characteristics and Nanotechnolody Applications; Scrivener, M., Carmical, P., Eds.; John Wiley & Sons: Hoboken, NJ, USA, 2013. [Google Scholar]

- Johnson, R.W.; Hultqvist, A.; Bent, S.F. A brief review of atomic layer deposition: From fundamentals to applications. Mater. Today 2014, 17, 236–246. [Google Scholar] [CrossRef]

- George, S.M. Atomic Layer Deposition: An Overview. Chem. Rev. 2009, 110, 111–131. [Google Scholar] [CrossRef]

- Niinistö, L.; Päiväsaari, J.; Niinistö, J.; Putkonen, M.; Nieminen, M. Advanced electronic and optoelectronic materials by Atomic Layer Deposition: An overview with special emphasis on recent progress in processing of high-k dielectrics and other oxide materials. Phys. Status Solidi (A) 2004, 201, 1443–1452. [Google Scholar] [CrossRef]

- Oviroh, P.O.; Akbarzadeh, R.; Pan, D.; Coetzee, R.A.M.; Jen, T.-C. New development of atomic layer deposition: Processes, methods and applications. Sci. Technol. Adv. Mater. 2019, 20, 465–496. [Google Scholar] [CrossRef] [PubMed]

- Cheong, K.Y.; Moon, J.H.; Eom, D.; Kim, H.J.; Bahng, W.; Kim, N.-K. Electronic Properties of Atomic-Layer-Deposited Al2O3/Thermal-Nitrided SiO2 Stacking Dielectric on 4H SiC. Electrochem. Solid-State Lett. 2007, 10, H69–H71. [Google Scholar] [CrossRef]

- Schilirò, E.; Lo Nigro, R.; Fiorenza, P.; Roccaforte, F. Negative charge trapping effects in Al2O3 films grown by atomic layer deposition onto thermally oxidized 4H-SiC. AIP Adv. 2016, 6, 075021. [Google Scholar] [CrossRef]

- van Hemmen, J.L.; Heil, S.B.S.; Klootwijk, J.H.; Roozeboom, F.; Hodson, C.J.; Van de Sanden, M.C.M.; Kessels, W.M.M. Plasma and thermal ALD of Al2O3 in a commercial 200 mm ALD reactor. J. Electrochem. Soc. 2007, 154, G165–G169. [Google Scholar] [CrossRef]

- Dingemans, G.; Seguin, R.; Engelhart, P.; van de Sanden, M.C.M.; Kessels, W.M.M. Silicon surface passivation by ultrathin Al2O3films synthesized by thermal and plasma atomic layer deposition. Phys. Status Solidi (RRL) Rapid Res. Lett. 2010, 4, 10–12. [Google Scholar] [CrossRef]

- Profijt, H.B.; Potts, S.E.; Van De Sanden, M.C.M.; Kessels, W.M.M. Plasma-Assisted Atomic Layer Deposition: Basics, Opportunities, and Challenges. J. Vac. Sci. Technol. A 2011, 29, 050801. [Google Scholar] [CrossRef]

- Hoex, B.; Schmidt, J.; Pohl, P.; van de Sanden, M.C.M.; Kessels, W.M.M. On the c-Si surface passivation mechanism by the negative-charge-dielectric Al2O3. J. Appl. Phys. 2008, 104, 044903. [Google Scholar] [CrossRef]

- Kotomin, E.; Popov, A. Radiation-induced point defects in simple oxides. Nucl. Instrum. Methods Phys. Res. Sect. B Beam Interact. Mater. At. 1998, 141, 1–15. [Google Scholar] [CrossRef]

- Anzalone, R.; Privitera, S.; Camarda, M.; Alberti, A.; Mannino, G.; Fiorenza, P.; Di Franco, S.; La Via, F. Interface state density evaluation of high quality hetero-epitaxial 3C–SiC(001) for high-power MOSFET applications. Mater. Sci. Eng. B 2015, 198, 14–19. [Google Scholar] [CrossRef]

- Fiorenza, P.; Schilirò, E.; Giannazzo, F.; Bongiorno, C.; Zielinski, M.; La Via, F.; Roccaforte, F. On the origin of the premature breakdown of thermal oxide on 3C-SiC probed by electrical scanning probe microscopy. Appl. Surf. Sci. 2020, 526, 146656. [Google Scholar] [CrossRef]

- Newsome, D.A.; Sengupta, D.; Foroutan, H.; Russo, M.F.; van Duin, A.C.T. Oxidation of Silicon Carbide by O2 and H2O: A ReaxFF Reactive Molecular Dynamics Study, Part I. J. Phys. Chem. C 2012, 116, 16111–16121. [Google Scholar] [CrossRef]

- Sze, S.M. Physics of Semiconductor Devices; Wiley-Interscience: Hoboken, NJ, USA, 1981; pp. 849–850. [Google Scholar]

- Kim, D.K.; Jeong, K.S.; Kang, Y.S.; Kang, H.-K.; Cho, S.W.; Kim, S.-O.; Suh, D.; Kim, S.; Cho, M.-H. Controlling the defects and transition layer in SiO2 films grown on 4H-SiC via direct plasma-assisted oxidation. Sci. Rep. 2016, 6, 34945. [Google Scholar] [CrossRef] [PubMed]

- Jinesh, K.B.; van Hemmen, J.L.; van de Sanden, M.C.M.; Roozeboom, F.; Klootwijk, J.H.; Besling, W.F.A.; Kessels, W.M.M. Dielectric Properties of Thermal and Plasma-Assisted Atomic Layer Deposited Al2O3 Thin Films. J. Electrochem. Soc. 2011, 158, G21–G26. [Google Scholar] [CrossRef]

- Haeberle, J.; Henkel, K.; Gargouri, H.; Naumann, F.; Gruska, B.; Arens, M.; Tallarida, M.; Schmeißer, D. Ellipsometry and XPS comparative studies of thermal and plasma enhanced atomic layer deposited Al2O3-films. Beilstein J. Nanotechnol. 2013, 4, 732–742. [Google Scholar] [CrossRef]

- Schilirò, E.; Fiorenza, P.; Greco, G.; Monforte, F.; Condorelli, G.G.; Roccaforte, F.; Giannazzo, F.; Nigro, R.L. Early Growth Stages of Aluminum Oxide (Al2O3) Insulating Layers by Thermal- and Plasma-Enhanced Atomic Layer Deposition on AlGaN/GaN Heterostructures. ACS Appl. Electron. Mater. 2021, 4, 406–415. [Google Scholar] [CrossRef]

- Li, F.; Qiu, S.; Jennings, M.R.; Mawby, P.A. Fabrication and Dielectric Breakdown of 3C-SiC/SiO2 MOS Capacitors. In Proceedings of the 2019 IEEE 12th International Symposium on Diagnostics for Electrical Machines, Power Electronics and Drives (SDEMPED), Toulouse, France, 27–30 August 2019; pp. 344–350. [Google Scholar]

- Yanev, V.; Rommel, M.; Bauer, A.J.; Frey, L. Characterization of thickness variations of thin dielectric layers at the nanoscale using scanning capacitance microscopy. J. Vac. Sci. Technol. B 2011, 29, 01A401. [Google Scholar] [CrossRef]

- Goghero, D.; Raineri, V.; Giannazzo, F. Study of interface states and oxide quality to avoid contrast reversal in scanning capacitance microscopy. Appl. Phys. Lett. 2002, 81, 1824–1826. [Google Scholar] [CrossRef]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).

Share and Cite

Schilirò, E.; Fiorenza, P.; Lo Nigro, R.; Galizia, B.; Greco, G.; Di Franco, S.; Bongiorno, C.; La Via, F.; Giannazzo, F.; Roccaforte, F. Al2O3 Layers Grown by Atomic Layer Deposition as Gate Insulator in 3C-SiC MOS Devices. Materials 2023, 16, 5638. https://doi.org/10.3390/ma16165638

Schilirò E, Fiorenza P, Lo Nigro R, Galizia B, Greco G, Di Franco S, Bongiorno C, La Via F, Giannazzo F, Roccaforte F. Al2O3 Layers Grown by Atomic Layer Deposition as Gate Insulator in 3C-SiC MOS Devices. Materials. 2023; 16(16):5638. https://doi.org/10.3390/ma16165638

Chicago/Turabian StyleSchilirò, Emanuela, Patrick Fiorenza, Raffaella Lo Nigro, Bruno Galizia, Giuseppe Greco, Salvatore Di Franco, Corrado Bongiorno, Francesco La Via, Filippo Giannazzo, and Fabrizio Roccaforte. 2023. "Al2O3 Layers Grown by Atomic Layer Deposition as Gate Insulator in 3C-SiC MOS Devices" Materials 16, no. 16: 5638. https://doi.org/10.3390/ma16165638

APA StyleSchilirò, E., Fiorenza, P., Lo Nigro, R., Galizia, B., Greco, G., Di Franco, S., Bongiorno, C., La Via, F., Giannazzo, F., & Roccaforte, F. (2023). Al2O3 Layers Grown by Atomic Layer Deposition as Gate Insulator in 3C-SiC MOS Devices. Materials, 16(16), 5638. https://doi.org/10.3390/ma16165638