Integration of Electrodeposited Ni-Fe in MEMS with Low-Temperature Deposition and Etch Processes

Abstract

:1. Introduction

2. Selective Copper Seed Etch

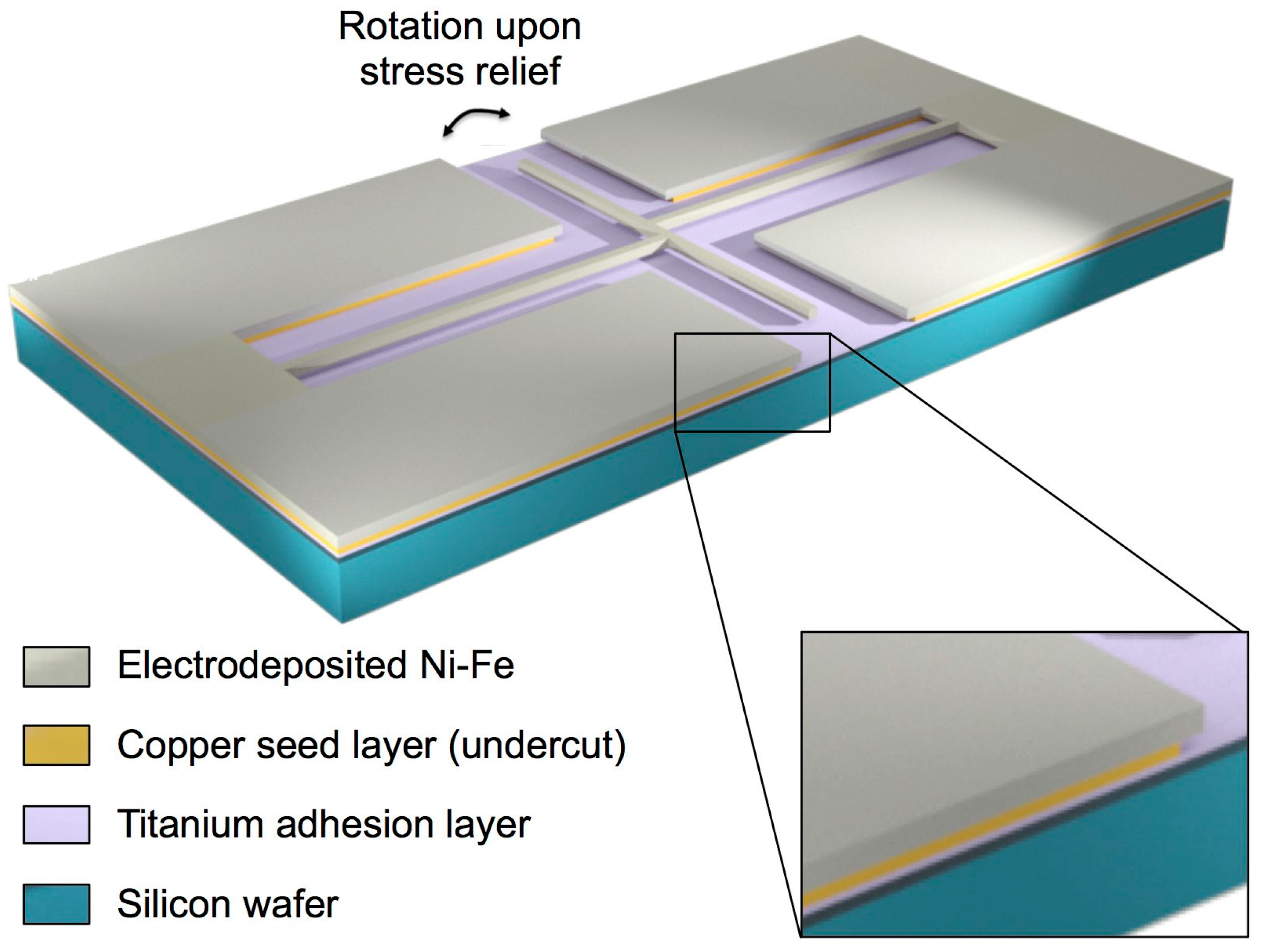

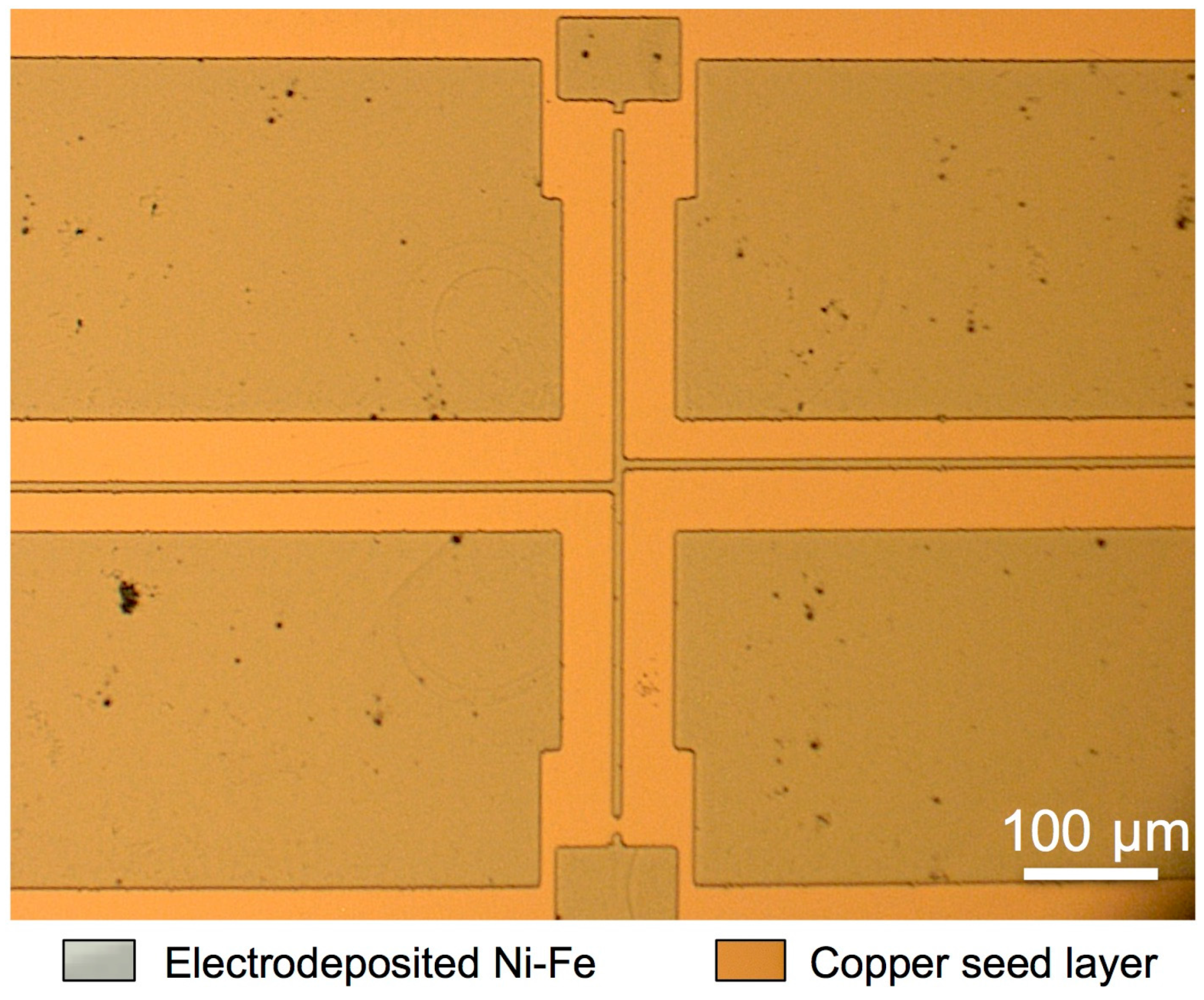

2.1. Test Structures

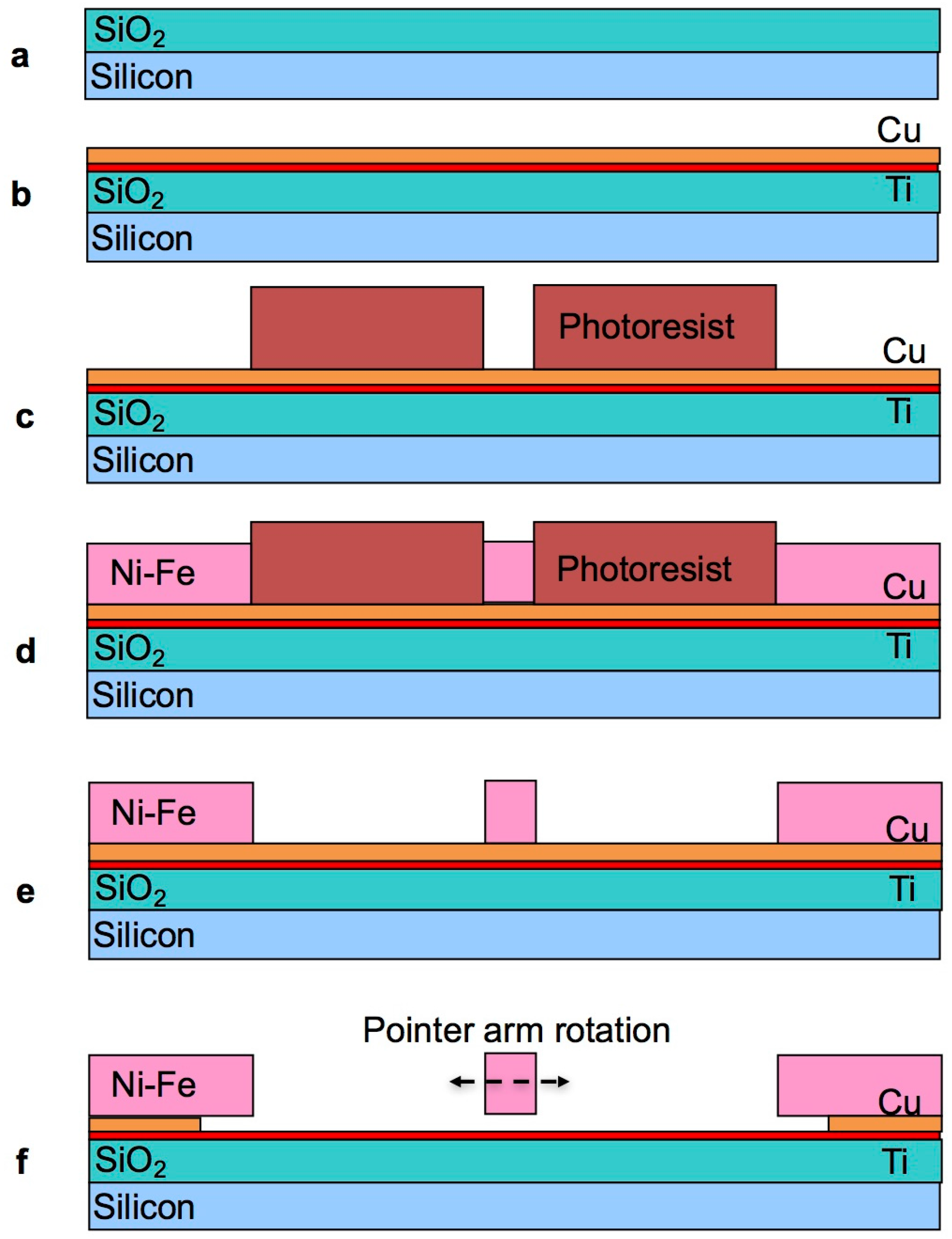

2.2. Fabrication

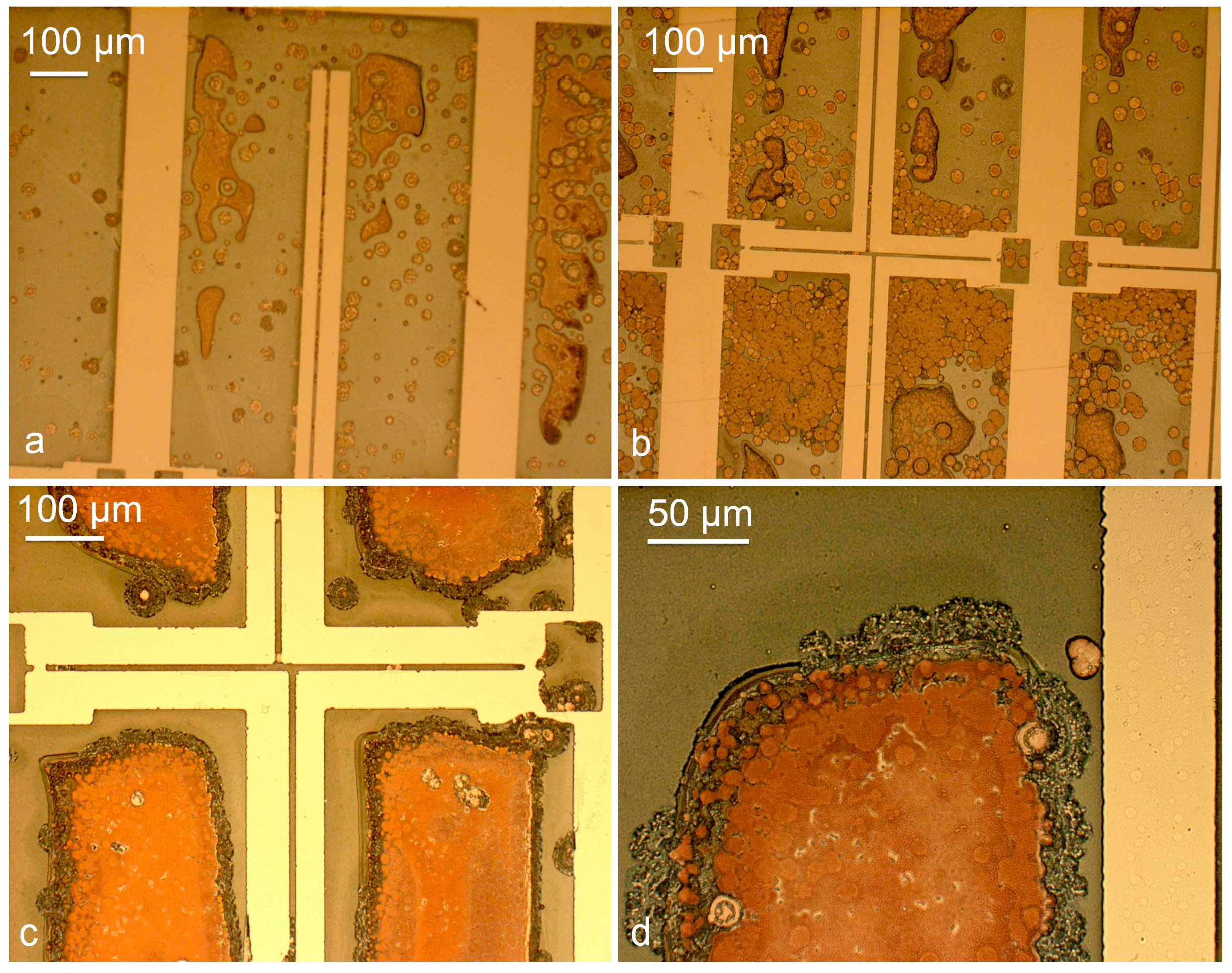

2.3. Development of the Selective Etching Process

3. Selective Sacrificial Layer Etching

3.1. Sacrificial Material

3.2. Selective Wet Etching of Sacrificial SiO2

4. Surface Micromachining with Vapour HF Etch

4.1. Test Structures

4.2. Release of the Cantilevers

5. Conclusions

Supplementary Materials

Acknowledgments

Author Contributions

Conflicts of Interest

References

- Daniel, L.; Sullivan, C.R.; Sanders, S.R. Design of microfabricated inductors. In Proceedings of the PESC Record, 27th Annual IEEE Power Electronics Specialists Conference, Baveno, Italy, 23–27 June 1996; Volume 2, pp. 1447–1455.

- Sullivan, C.R.; Sanders, S.R. Design of microfabricated transformers and inductors for high-frequency power conversion. IEEE Trans. Power Electron. 1996, 11, 228–238. [Google Scholar] [CrossRef]

- Myung, N.V.; Park, D.-Y.; Yoo, B.-Y.; Sumodjo, P.T.A. Development of electroplated magnetic materials for MEMS. J. Magn. Magn. Mater. 2003, 265, 189–198. [Google Scholar] [CrossRef]

- Mathúna, C.Ó.; Wang, N.; Kulkarni, S.; Roy, S. Review of Integrated Magnetics for Power Supply on Chip (PwrSoC). IEEE Trans. Power Electron. 2012, 27, 4799–4816. [Google Scholar] [CrossRef]

- Luo, J.K.; Pritschow, M.; Flewitt, A.J.; Spearing, S.M.; Fleck, N.A.; Milne, W.I. Effects of Process Conditions on Properties of Electroplated Ni Thin Films for Microsystem Applications. J. Electrochem. Soc. 2006, 153, D155–D161. [Google Scholar] [CrossRef]

- Arai, K.I.; Honda, T. Micromagnetic actuators. Robotica 1996, 14, 477–481. [Google Scholar] [CrossRef]

- Niarchos, D. Magnetic MEMS: Key issues and some applications. Sens. Actuators A Phys. 2003, 106, 255–262. [Google Scholar] [CrossRef]

- Flynn, D.; Toon, A.; Allen, L.; Dhariwal, R.; Desmulliez, M.P.Y. Characterization of Core Materials for Microscale Magnetic Components Operating in the Megahertz Frequency Range. IEEE Trans. Magn. 2007, 43, 3171–3180. [Google Scholar] [CrossRef]

- Wu, Y.B.; Ding, G.F.; Wang, H.; Zhang, C.C. Efficient solution to selective wet etching of ultra-thick copper sacrificial layer with high selective etching ratio. In Proceedings of the 2011 16th International Solid-State Sensors, Actuators and Microsystems Conference, Beijing, China, 5–9 June 2011; pp. 1388–1391.

- Quemper, J.-M.; Nicolas, S.; Gilles, J.P.; Grandchamp, J.P.; Bosseboeuf, A.; Bourouina, T.; Dufour-Gergam, E. Permalloy electroplating through photoresist molds. Sens. Actuators A Phys. 1999, 74, 1–4. [Google Scholar] [CrossRef]

- Cohen, U.; Hsie, W.C. Selective Chemical Removal of Coil Seed-Layer in Thin Film Head Magnetic Transducer. U.S. Patent 5,059,278 A, 22 October 1991. [Google Scholar]

- Asai, O.; Hanazono, M. Electrolytic Etching Method. U.S. Patent 3,905,883 A, 16 September 1975. [Google Scholar]

- Saulnier, T.A. Ferric chloride Etching Solutions. U.S. Patent 2,684,892 A, 27 July 1954. [Google Scholar]

- French, P.J. Development of surface micromachining techniques compatible with on-chip electronics. J. Micromech. Microeng. 1996, 6, 197. [Google Scholar] [CrossRef]

- Taylor, W.P.; Brand, O.; Allen, M.G. Fully integrated magnetically actuated micromachined relays. J. Microelectromech. Syst. 1998, 7, 181–191. [Google Scholar] [CrossRef]

- Ruan, M.; Shen, J.; Wheeler, C.B. Latching micromagnetic relays. J. Microelectromech. Syst. 2001, 10, 511–517. [Google Scholar] [CrossRef]

- Cho, I.-J.; Yoon, E. Design and fabrication of a single membrane push-pull SPDT RF MEMS switch operated by electromagnetic actuation and electrostatic hold. J. Micromech. Microeng. 2010, 20, 035028. [Google Scholar] [CrossRef]

- Glickman, M.; Tseng, P.; Harrison, J.; Niblock, T.; Goldberg, I.B.; Judy, J.W. High-Performance Lateral-Actuating Magnetic MEMS Switch. J. Microelectromech. Syst. 2011, 20, 842–851. [Google Scholar] [CrossRef]

- Gray, G.D., Jr.; Prophet, E.M.; Zhu, L.; Kohl, P.A. Magnetically bistable actuator: Part 2. Fabrication and performance. Sens. Actuators A Phys. 2005, 119, 502–511. [Google Scholar] [CrossRef]

- Bagolini, A.; Pakula, L.; Scholtes, T.L.M.; Pham, H.T.M.; French, P.J.; Sarro, P.M. Polyimide sacrificial layer and novel materials for post-processing surface micromachining. J. Micromech. Microeng. 2002, 12, 385. [Google Scholar] [CrossRef]

- Girard, R. The Electrodeposition of Thin Magnetic Permalloy Films. J. Appl. Phys. 1967, 38, 1423–1430. [Google Scholar] [CrossRef]

- Hadian, S.E.; Gabe, D.R. Residual stresses in electrodeposits of nickel and nickel–iron alloys. Surf. Coat. Technol. 1999, 122, 118–135. [Google Scholar] [CrossRef]

- Yang, M.M.; Aboaf, J.A. rf-diode sputtered Permalloy film. J. Appl. Phys. 1989, 66, 3734–3740. [Google Scholar] [CrossRef]

- Murray, J.; Schiavone, G.; Smith, S.; Terry, J.; Mount, A.R.; Walton, A.J. Characterisation of electroplated NiFe films using test structures and wafer mapped measurements. In Proceedings of the 2011 IEEE ICMTS International Conference on Microelectronic Test Structures, Amsterdam, The Netherlands, 4–7 April 2011; pp. 63–68.

- Schiavone, G.; Bunting, A.S.; Desmulliez, M.P.Y.; Walton, A.J. Fabrication of Electrodeposited Ni #x2013;Fe Cantilevers for Magnetic MEMS Switch Applications. J. Microelectromech. Syst. 2015, 24, 870–879. [Google Scholar]

- Schiavone, G.; Murray, J.; Smith, S.; Desmulliez, M.P.Y.; Mount, A.R.; Walton, A.J. A wafer mapping technique for residual stress in surface micromachined films. J. Micromech. Microeng. 2016, 26, 095013. [Google Scholar] [CrossRef]

- Schiavone, G.; Desmulliez, M.P.Y.; Smith, S.; Murray, J.; Murray, J.; Sirotkin, E.; Terry, J.G.; Mount, A.R.; Walton, A.J. Quantitative wafer mapping of residual stress in electroplated NiFe films using independent strain and Young’s modulus measurements. In Proceedings of the 2012 IEEE International Conference on Microelectronic Test Structures, San Diego, CA, USA, 19–22 March 2012; pp. 105–110.

- Madou, M.J. Manufacturing Techniques for Microfabrication and Nanotechnology; CRC Press: Boca Raton, FL, USA, 2011; Available online: https://www.crcpress.com/Manufacturing-Techniques-for-Microfabrication-and-Nanotechnology/Madou/p/book/9781420055191 (accessed on 9 February 2017).

- Allen, D.M. Photochemical Machining: From “manufacturing’s best kept secret” to a $6 billion per annum, rapid manufacturing process. CIRP Ann. Manuf. Technol. 2004, 53, 559–572. [Google Scholar] [CrossRef]

- Osborne, J.R. Variable Sloped Etching of Thin Film Heads. U.S. Patent 4,351,698 A, 28 September 1982. [Google Scholar]

- Stichel, W. Materials selection for corrosion control. Hrsg. von S.L. Chawla und R.K. Gupta, 508 S., zahlreiche Tabellen und Grafiken. ASM International Materials Park, OH 44073, USA, £ 104,00. ISBN 0-87170-479-9. Mater. Corros. 1995, 46, 249. [Google Scholar] [CrossRef]

- Williams, K.R.; Gupta, K.; Wasilik, M. Etch rates for micromachining processing-Part II. J. Microelectromech. Syst. 2003, 12, 761–778. [Google Scholar] [CrossRef]

- Byun, Y.H.; Kim, H.I.; Song, Y.S.; Yoon, J.K.; Chung, C.W. Chemical Etching of NiFe and IrMn Thin Films. J. Ind. Eng. Chem. 2002, 8, 257–261. [Google Scholar]

- Wu, X.H.; Li, W.; Lam, S.-T.; Chang, H.C.; Ju, K.; Chang, J.-W. Etching Process to Selectively Remove Copper Plating Seed Layer. U.S. Patent 6,767,477 B2, 27 July 2004. [Google Scholar]

- Lin, C.W.-C.; Yee, I.Y.K. Copper Etching Solution and Method. U.S. Patent 4,952,275, 28 August 1990. [Google Scholar]

- Fritschi, R.; Frédérico, S.; Hibert, C.; Flückiger, P.; Renaud, P.; Tsamados, D.; Boussey, J.; Chovet, A.; Ng, R.K.M.; Udrea, F.; et al. High tuning range AlSi RF MEMS capacitors fabricated with sacrificial amorphous silicon surface micromachining. Microelectron. Eng. 2004, 73–74, 447–451. [Google Scholar] [CrossRef]

- Frederico, S.; Hibert, C.; Fritschi, R.; Fluckiger, P.; Renaud, P.; Ionescu, A.M. Silicon sacrificial layer dry etching (SSLDE) for free-standing RF MEMS architectures. In Proceedings of the IEEE the Sixteenth Annual International Conference on Micro Electro Mechanical Systems, 2003 MEMS-03, Kyoto, Japan, 19–23 January 2003; pp. 570–573.

- Sugiyama, S.; Tabata, O.; Shimaoka, K.; Asahi, R. Micromachined sensors using polysilicon sacrificial layer etching technology. In Proceedings of the 1994 IEEE International Electron Devices Meeting, San Francisco, CA, USA, 11–14 December 1994; pp. 127–130.

- Metzger, L.; Fischer, F.; Mokwa, W. Polysilicon sacrificial layer etching using ClF3 for thin film encapsulation of silicon acceleration sensors with high aspect ratio. Sens. Actuators A Phys. 2007, 133, 259–265. [Google Scholar] [CrossRef]

- Ma, S.; Li, Y.; Sun, X.; Yu, X.; Jin, Y. Study of polyimide as sacrificial layer with O2 plasma releasing for its application in MEMS capacitive FPA fabrication. In Proceedings of the 2009 International Conference on Electronic Packaging Technology High Density Packaging, Beijing, China, 10–13 August 2009; pp. 526–529.

- Pham, H.T.M.; Bagolini, A.; de Boer, C.R.; Laros, J.M.W.; Pakula, L.; French, P.J.; Sarro, P.M. Polyimide sacrificial layer for an all-dry post-process surface micromachining module. In Proceedings of the 2003 12th International Conference on TRANSDUCERS, Solid-State Sensors, Actuators and Microsystems, Boston, MA, USA, 8–12 June 2003; Volume 1, pp. 813–816.

- Huang, W.-L.; Ren, Z.; Lin, Y.-W.; Chen, H.-Y.; Lahann, J.; Nguyen, C.T.C. Fully monolithic CMOS nickel micromechanical resonator oscillator. In Proceedings of the 2008 IEEE 21st International Conference on Micro Electro Mechanical Systems, Tucson, AZ, USA, 13–17 January 2008; pp. 10–13.

- Bühler, J.; Steiner, F.-P.; Baltes, H. Silicon dioxide sacrificial layer etching in surface micromachining. J. Micromech. Microeng. 1997, 7, R1. [Google Scholar] [CrossRef]

- Witvrouw, A.; Du Bois, B.; De Moor, P.; Verbist, A.; Van Hoof, C.A.; Bender, H.; Baert, C. Comparison between wet HF etching and vapor HF etching for sacrificial oxide removal. Proc. SPIE 2000, 4174, 130–141. [Google Scholar]

- Cianci, E.; Schina, A.; Minotti, A.; Quaresima, S.; Foglietti, V. Dual frequency PECVD silicon nitride for fabrication of CMUTs’ membranes. Sens. Actuators A Phys. 2006, 127, 80–87. [Google Scholar] [CrossRef]

- Huang, H.; Winchester, K.J.; Suvorova, A.; Lawn, B.R.; Liu, Y.; Hu, X.Z.; Dell, J.M.; Faraone, L. Effect of deposition conditions on mechanical properties of low-temperature PECVD silicon nitride films. Mater. Sci. Eng. A 2006, 435–436, 453–459. [Google Scholar] [CrossRef]

- Puech, M.; Thevenoud, J.M.; Gruffat, J.M.; Launay, N.; Arnal, N.; Godinat, P. Fabrication of 3D packaging TSV using DRIE. In Proceedings of the 2008 Symposium on Design, Test, Integration and Packaging of MEMS/MOEMS, Nice, France, 9–11 April 2008; pp. 109–114.

- Archard, D.; Giles, K.; Price, A.; Burgess, S.; Buchanan, K. Low temperature PECVD of dielectric films for TSV applications. In Proceedings of the 2010 60th Electronic Components and Technology Conference (ECTC), Las Vegas, NV, USA, 1–4 June 2010; pp. 764–768.

- Deshmukh, S.C.; Aydil, E.S. Investigation of low temperature SiO2 plasma enhanced chemical vapor deposition. J. Vac. Sci. Technol. B Microelectron. Nanometer Struct. Process. Meas. Phenom. 1996, 14, 738–743. [Google Scholar] [CrossRef]

- Van de Ven, E.P.; Connick, I.W.; Harrus, A.S. Advantages of dual frequency PECVD for deposition of ILD and passivation films. In Proceedings of the Seventh International IEEE Conference on VLSI Multilevel Interconnection, Santa Clara, CA, USA, 12–13 June 1990; pp. 194–201.

- Guan, D.; Bruccoleri, A.R.; Heilmann, R.K.; Schattenburg, M.L. Stress control of plasma enhanced chemical vapor deposited silicon oxide film from tetraethoxysilane. J. Micromech. Microeng. 2014, 24, 027001. [Google Scholar] [CrossRef]

- Schiavone, G.; Desmulliez, M.P.Y.; Walton, A.J. Integrated Magnetic MEMS Relays: Status of the Technology. Micromachines 2014, 5, 622–653. [Google Scholar] [CrossRef]

- Schiavone, G.; Smith, S.; Murray, J.; Terry, J.G.; Desmulliez, M.P.Y.; Walton, A.J. Micromechanical test structures for the characterisation of electroplated NiFe cantilevers and their viability for use in MEMS switching devices. In Proceedings of the 2013 IEEE International Conference on Microelectronic Test Structures (ICMTS), Osaka, Japan, 25–28 March 2013; pp. 13–18.

| Component | Concentration (gL−1) |

|---|---|

| NiCl2·6H2O | 110 |

| FeCl2·4H2O | 8 |

| H3BO3 | 25 |

| Saccharin | 1 |

| Na dodecyl sulphate | 0.1 |

| HCl | 5 |

| Component | Quantity |

|---|---|

| (NH4)2S2O8 | 50 gL−1 |

| C6H8O7 | 50 gL−1 |

| NaOH | 1 M |

| Process Parameter | Value |

|---|---|

| SiH4 flow rate | 6 sccm |

| N2O flow rate | 1420 sccm |

| RF frequency | 380 kHz |

| RF power | 60 W |

| Wafer holder temperature | 120 °C |

| Gas inlet unit temperature | 120 °C |

| Chamber pressure | 550 mTorr |

| Deposition time | 53 min |

| Process Parameter | Value |

|---|---|

| N2 flow rate | 1900 sccm |

| SiH4 flow rate | 120 sccm |

| NH3 flow rate | 8 sccm |

| RF frequency | 13.56 MHz |

| RF power | 60 W |

| Wafer holder temperature | 200 °C |

| Gas inlet unit temperature | 200 °C |

| Chamber pressure | 550 mTorr |

| Deposition time | 7.5 min |

| Etchant | Material | Approximate Etch Rate |

|---|---|---|

| 1:2 [BOE 10:1] in DI water | PECVD SiO2 | 1500 nm/min |

| 1:2 [BOE 10:1] in DI water | PECVD Si3N4 | 20 nm/min |

| 1:10 [BOE 10:1] in DI water | PECVD SiO2 | 160 nm/min |

| 1:10 [BOE 10:1] in DI water | PECVD Si3N4 | not detected |

© 2017 by the authors. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license ( http://creativecommons.org/licenses/by/4.0/).

Share and Cite

Schiavone, G.; Murray, J.; Perry, R.; Mount, A.R.; Desmulliez, M.P.Y.; Walton, A.J. Integration of Electrodeposited Ni-Fe in MEMS with Low-Temperature Deposition and Etch Processes. Materials 2017, 10, 323. https://doi.org/10.3390/ma10030323

Schiavone G, Murray J, Perry R, Mount AR, Desmulliez MPY, Walton AJ. Integration of Electrodeposited Ni-Fe in MEMS with Low-Temperature Deposition and Etch Processes. Materials. 2017; 10(3):323. https://doi.org/10.3390/ma10030323

Chicago/Turabian StyleSchiavone, Giuseppe, Jeremy Murray, Richard Perry, Andrew R. Mount, Marc P. Y. Desmulliez, and Anthony J. Walton. 2017. "Integration of Electrodeposited Ni-Fe in MEMS with Low-Temperature Deposition and Etch Processes" Materials 10, no. 3: 323. https://doi.org/10.3390/ma10030323

APA StyleSchiavone, G., Murray, J., Perry, R., Mount, A. R., Desmulliez, M. P. Y., & Walton, A. J. (2017). Integration of Electrodeposited Ni-Fe in MEMS with Low-Temperature Deposition and Etch Processes. Materials, 10(3), 323. https://doi.org/10.3390/ma10030323