Abstract

Sensors in many applications must select the largest element in a sequence of currents. This can be performed in an analog way by the Winner-Take-All (WTA) circuit. This paper considers the classic version of the WTA Lazzaro circuit, working with MOS devices in a subthreshold regime. Since the separation of the gainer by analytically computable “decision levels” has recently been introduced, this paper aims to numerically verify and discuss these levels and their dependence on circuit and device parameters. For , the threshold voltage of MOS devices, which is primarily responsible for differences between components (mismatch), its relationship with the output voltages is theoretically demonstrated and numerically checked.

1. Introduction

Winner-Take-All (WTA) circuits are one of the most important building blocks in analog parallel signal processing, such as spatial acquisition and tracking, sound localization, image processing and neuromorphic systems [1,2,3,4,5,6,7]. The main function of a WTA is to select the highest input signal among multiple inputs, so two-input WTAs can also be used as half-wave and full-wave rectifiers [8,9,10]. Many WTA proposals can be found in the literature, such as voltage-mode configurations based on differential pair structures [11,12] or on inhibitory and local excitatory feedback loop circuits [13,14,15,16]. The first approach suffers from complexity and a high power comsumption, whereas the second approach has potential stability issues due to positive feedback.

In recent years, the processing of nanoamps has become increasingly important. These currents can come from sensors inside the human body—[17], from chemical reaction sensors, from motion tracking or from computer memory—[18]—to name just a few examples. In fact, the analog processing of very small signals was used in “neuromorphic” circuits initiated by Carver Mead at Caltech in the early 1990s [19,20]. In that context, the first W (inner) T(ake) A(ll) circuit appeared, known today as the “Lazzaro Circuit”—[21]. Its simplicity that leads to space savings on integrated chips has distinguished it technologically. Many improvements to the Lazzaro circuit have been proposed in the meantime [22,23], but the basic principle and configuration have not changed.

In [24], Sekerkiran et al. proposed a modified version of Lazzaro’s WTA, which improved the resolution without requiring positive feedback, thus avoiding major stability issues. Their approach consisted of using an aditional transistor per cell to increase the open loop gain and, therefore, improve resolution. However, both Lazzaro’s and Sekerkiran’s WTAs need a high voltage swing at the input nodes to turn on the winning cell, which results in a slow response to abrupt input current changes.

The parameters of MOS and their interconnections must be as identical as possible. Integrated circuit technology, engaged in a race to reduce the size of chips and circuits, cannot ensure the strict identity of the parameters on the same chip or on different chips. Thus appears the so-called “mismatch”—[22,23,24,25], whose size is a criterion for the performance of the chips. It is all the more important as the circuit works with lower currents. In this way, the study of the variation in the performances of the circuits with MOS transistors working in the subthreshold (or weak inversion) when the model parameters slide around the design value is decisive.

This paper considers the original Lazzaro circuit, working in the subthreshold as a selector of the maximum current rank. For the list of output voltages, a parallel paper co-authored by the present author—[26,27]—introduced a “higher decision level”. Above it, only the highest rank (winner) in the output list must be placed. Similarly, a “lower decision level” must be above the second-largest rank and under the higher level. Both levels were rigorously defined and used to introduce the resolution performance of the selector.

In fact, we need two notions of resolution. One for the input lists—the input resolution—and one for the selection result—the output resolution. To be sensitive and efficient, a WTA fed with “crowded” lists must select the output through a “wide” separation. Below, after introducing the circuit static model in Section 1, we present the theoretical questions about decision levels and about the resolution in Section 3 and Section 4. In Section 5, the monotonic dependence of the winner size on the threshold voltage of MOS devices is proven. Section 6 contains numerically computed examples. Analytically computed decision levels and resolutions are extensively checked and analyzed.

2. The Circuit Model

For the subthreshold regime—i.e., when and —we use the usual MOS model [28] with the usual notations:

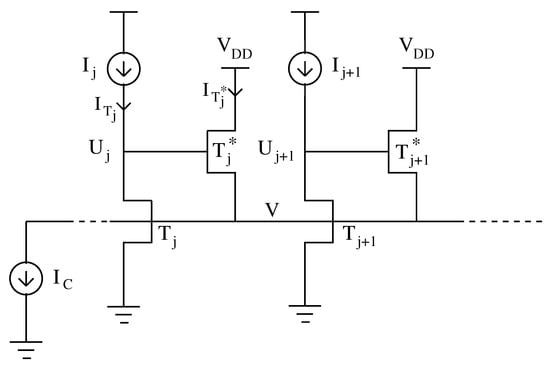

Then, the steady state of the Lazzaro WTA circuit in Figure 1 (with all devices in the subthreshold) can be obtained by and where and are the currents for and , respectively. Thus, we will move on to the following:

where

Figure 1.

Two cells of Lazzaro WTA. are input currents; are output voltages; is the bias current.

In the above equations, the MOS parameters are , k and while , and are outside constant sources. For an input list of currents , Equation (3) provides the common potential V with which Equation (2) gives the output voltages .

Obviously, we have to make sure that all transistors and work in the subthreshold, which means [26,29] V and must be restricted to

As we prove in [26], the following restrictions are sufficient:

where is the absolute maximum of currents allowed for processing. For and , see below. Let us note that the right side in (9) is not a restriction.

Finally, let us mention that, in [29], for the dynamic model of our circuit, the invariance of the solution in a weak inversion region as well as its asymptotic stability have been studied.

3. Decision Levels

To explain the issue of decision levels, let us start with a simple example.

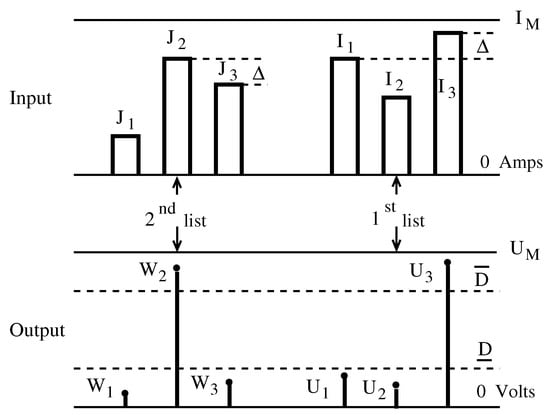

Let us consider our WTA in the particular case of , fed with the infinite number of lists in , that is, lists with three currents, no bigger that and separated from each other by the minimum distance . The first list with the (decreasing) order arrives at the WTA input—see Figure 2. The goal is to signal the “winning” rank of the largest current , even in the extreme case when “the loser”—which is the second-largest current —is at the minimum distance , and is so small that the two are not distinguishable on the scale.

Figure 2.

The input list yields the output list ; the input list yields the output list . The winning ranks are “3” in the first case and “2” in the second, since and surpass .

The WTA circuit translates the reading of the winner rank to the output list of voltages , which has the same order . However, the winner is now split from the loser by a gap , which is sufficiently large on the scale.

In fact, we have to have . is called “the upper decision level” and has the property that it is surpassed only by the winner. Thus, the outputs are compared with —see Figure 2—and rank 3 will be the unique winner.

Furthermore, is called “the lower decision level”, and all the “losers” ( and here) are under it. The distance is significant on the scale , where is the maximum voltage. Returning to Figure 2, let us consider a second list from applied at the input. Suppose that and the winner rank “2” has to be signaled. This is performed by obtaining the output voltages arranged as , where the only rank surpassing the upper decision level is “2”, the winner. The losers are below the lower decision level . The processing should be similar for any list from when using the same decision levels and and the same circuit parameters.

For the input list written in the terminal order, let us denote a permutation of the indices such that the currents in are in decreasing order:

Then, from (2), it is clear that the output voltages are in the same decreasing order, i.e.,

Both and are called “winner” while both and are called “loser”. To and to as well, we use the same name, “losers”.

We will assume that the input currents belong to the class , i.e., their components are inside the interval and are mutually separated by distance at least. To abbreviate the writing, from here on, we will denote this class simply by . Thus,

This leads to the existence of intervals in which each current is forced to belong:

Here, for each ,

and

We put

the list of maximum currents of each rank from (10). Note that the intervals in (14) do not overlap. All possible lists at the input (i.e., satisfying (7)–(10)) have in common the number of elements N, the maximum current and a measure of the agglomeration of the currents . Let us denote by this (infinite) family of input lists.

The raison d’tre of the WTA circuit is to identify the rank of the highest current in list I and to achieve this for any input list in without changing the parameters or configuration.

A recent co-work by the author of this paper—[26]—has introduced two “decision levels”, and , which split the output list as follows:

Here, is defined as the smallest winner of the output lists when all inputs in are applied. Similarly, D is the highest loser for all inputs in . The main attraction of these particular levels consists of the fact that they can be obtained “semi-analytically”.

Thus, it is proven that

where

is the -list with currents in (15). This means that the upper decision level is exactly the winner of the output list when the currents in are the input. It is shown that they are the smallest possible currents of each rank, computable as in (15).

Also, we have

where

—see (15) and (16). In other words, the lower decision level is identified as the loser of the output list when the currents in are the input. In addition, (22) shows that the first two currents in are the highest in their class , while all others currents are the lowest possible in their respective rank. After and are evaluated, they are used as inputs in (2)+(3) to compute (numerically) the outputs and . From them, the decision levels and are extracted as in (19) and (21), respectively.

Finally, we need the largest voltage when applying . It can be shown that the maximum output voltage is obtained if we apply—see [26]–at the input

and take the maximum voltage in the output

4. Resolutions

In order to appreciate the WTA performances, apart from the threshold and , we need a measure of the finesse of selecting the winner. First, we need a measure of the “crowding” of the currents at the input.

The family contains lists of currents on the scale, whose cramming is measured by . The difference between the largest and the second-largest current of any list is at least . The coefficient defined by

This will be called “THE INPUT RESOLUTION”. When is very small, perceiving (the winner) and (the loser) as distinct from each other is difficult and prone to error. On the output side, the voltages are similarly arranged on the scale. However, the positions of the w (i.e., winner) and l (i.e., loser) ranks are now controlled by the decision levels and :

and do not change when a new list from arrives. Under constraints in (7)–(10), and are fixed by (19) and (21). Each winner of each list surpasses . Each loser of each list in falls under . The gap compared with the entire will be denoted by and called “THE OUTPUT RESOLUTION”:

The similarity between at input and at output is complete. Both of them indicate how much of the “reading scale” is taken up by the smallest possible size difference between the w and l ranks. The circuit is effective if “it amplifies” the resolution of the input list. The large values for mean that the winning rank is highly distinct. To understand the WTA input–output mechanism, we study the function when and are unchanged. For clarity, we will translate the results obtained so far in terms of , where .

In [26], it is shown that

at least for a part of ’s “spectre”. However, examples show that the ratio is in the order of hundreds at least.

From (27), it follows immediately that

which means that the function is monotonously increasing. This corresponds to “the intuition” that more disjointed current lists are processed more efficiently (i.e., the gap is bigger).

5. Exploring the Mismatch

The threshold voltage is the value of the voltage that controls the transition between the distinct operating regions of the MOS. The value of is influenced by the thickness of the oxide layer, as well as by body doping. Also, depends a lot on the parasitic charge trapped between oxide and silicon. In contrast to this “accidental” charge, some charge can be introduced intentionally through the process called “ion implantation”.

Moreover, it is well known that subthreshold design has dramatically increased the sensitivity to process variation. This fact is taken into account by introducing the variation in the zero current with threshold voltage. Indeed,

where does not depend on —see [28]. Subsequently, we use (33) in models (2) and (3) and try to evaluate the influence of on the output . Fortunately, we can analytically deduce a qualitative behaviour. Namely, we can show that decreases with :

For this, let us denote and such that the function in (4) becomes

Equation (3) with a fixed gives

We easily obtain

Then, (36) gives

6. Numerical Checks–Discussion

6.1. Decision Levels

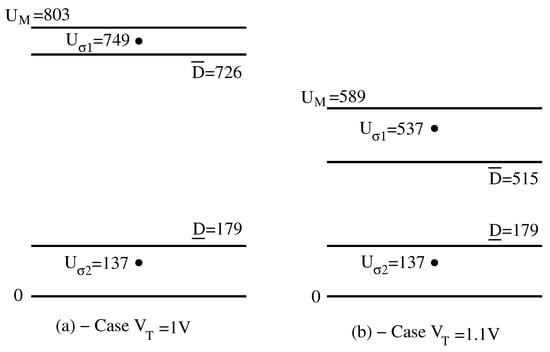

In this paragraph, we deal with the decision levels and on the scale. The known quantities are k, , and (i.e., the MOS device parameters) then N, and (circuit parameters) and and (i.e., class characteristics). All these quantities must satisfy the restrictions (7)–(10). Their numerical values are , V, Amp, V, , Amp, V, nA and nA. We will call this case “Example 1”. Now follows the analytical part of decision levels calculation. Our result is obtained in formula (20), (22) and (23), which give three particular input lists of currents , and . For their calculation, we use (15) and (16), which lead to and , both in nAmps and for . Thus, lists , and from (20), (22) and (23) are now known. At this point, the numerical part of the calculation begins. We solve the 101 equations in (2) and (3) three times corresponding to the inputs , and . We obtain three output sequence , and , respectively, each of 100 voltages. From each of them, we select one component according to (19), (21) and (24). Namely, the largest voltage in is the upper decision level . The second-largest voltage in is the lower decision level . Finally, the largest component in is the maximum possible voltage when any of the lists is processed: . For our circuit and device parameters, we obtain mV, mV and mV, as shown in Figure 3a. So, out of the scale of mV, any winner will be caught in the interval , i.e., in the upper part of . The loser will always be in the interval , i.e., in the lower part of —see Figure 3a. The rest of the scale, i.e., the interval , which represents of the total, is the separation “gap” between the unique winner and the rest of the 99 losers.

Figure 3.

Example 1: , and nAmp. Two cases for V and V. The winner , the loser , the maximum voltage and the decision levels and .

The ratio is the “INPUT RESOLUTION” introduced in Section 4. It shows how crowded the lists we intend to process can be. At the output, we brought the “OUTPUT RESOLUTION” —see Figure 3a.

This means that the input resolution yields an input one of 681 times higher. The ratio is a performance index for WTA.

Now, we change from 1 V to V. For the same parameters, k, , , N, , and , we obtain the lists , and . Solving again the 101 equations from (2) and (3) (this time with V), we obtain mV, mV and mV. Then, —see Figure 3b and the comments in Section 6.2.

6.2. Mismatch

We take the device parameters in Example 1 except for , which is replaced by (33) with Amp. Also, we successively use in (33) as 1 V, 1.02 V, 1.04 V, …, 1.1 V. For the class with nA and nA, , we follow the procedure in Section 6.1 and determine , and for each of these six cases. The results are presented in Table 1.

Table 1.

Example 2 Section 6.2. , , and in mV. Output resolution in percent.

We notice that major effects occur when the threshold voltage increases by —See Figure 3a,b. The maximum voltage decreases drastically by , while the higher decision level decreases by . Remarkably, the lower decision level is hardly influenced by the deviation of . Even more remarkable is that the decrease in the output resolution by 10 percent does not sufficiently reflect the major worsening of the accuracy in the appreciation of the maximum . It turns out that the maximum output voltage must accompany the output resolution parameter in the WTA circuit specifications.

6.3. List Processing

Example 3

With the WTA data from the previous example, let us take a list of 100 currents given by

Among these 100 currents two groups are shown in Table 2 Column 1. The largest current in our list is found at terminal 50. If is the permutation that gives the descending order, then , i.e., nA, as in Table 2 Column 1. Also, the second-largest current is at terminal 99. Thus, , i.e., nA, as in Table 2. Now, we solve the Equations (2) and (3) with the above currents and V. Out of the output , Table 2 Column 2 shows the voltages to and to . It is verified that the order in U is given by the same permutation as currents, such that the winner is mV and the loser is mV—see Table 2 Figure 3. The winner is caught in the interval , while the loser together with all other voltages fall in the interval . The output resolution is , way better than at the input.

7. Conclusions

Finding the maximum in continuous signal strings is a fundamental operation in signal processing. When processing speed is essential, the analog version is preferable. In this framework, the WTA circuit has imposed itself through technological simplicity. Of course, in this case we have to solve the problem of precision in separating the maximum rank (“winner”) from the next rank (“loser”). This paper, in close connection with [26], verifies numerically that “the decision levels” work correctly. For this, the theoretical notions of decision levels, resolution and mismatch are specified first. Then, a class of strings of 100 currents is considered for which the decision levels and input and output resolution are analytically calculated. Numerical processing follows that simulates the operation of the WTA circuit. An ordered string of voltages is obtained at the output. It is verified that the largest element of this string exceeds the upper decision level while the rest of the elements are crowded much further, namely, below the lower decision level. The output resolution compared to the input resolution indicates how much “the winner” is separated, i.e., the effectiveness of the WTA. It is theoretically shown that any of the output voltages decreases monotonically with increases in . It is then verified by numerical calculation that the small increase in the threshold voltage of the MOS transistors leads to a drastic decrease in both the decision levels and the output resolution. Since the manufacturing technology cannot ensure a really constant for series production, this is a major problem in the design of MOS circuits, especially those that work in the subthreshold.

Funding

This research received no external funding.

Institutional Review Board Statement

Not applicable.

Informed Consent Statement

Not applicable.

Data Availability Statement

All of the relevant research data will be made available upon request after the publication of the paper.

Conflicts of Interest

The author declares no conflict of interest.

References

- Badel, S.; Schmid, A.; Leblebici, Y. CMOS realization of two-dimensional mixed analog-digital Hamming distance discriminator circuits for real-time imaging applications. Microelectron. J. 2008, 39, 1817–18280. [Google Scholar] [CrossRef]

- Bigas, M.; Cabruja, E.; Forest, J.; Salvi, J. Review of CMOS image sensors. Microelectron. J. 2006, 37, 433–451. [Google Scholar] [CrossRef]

- Brink, S.; Nease, S.; Hasler, P.; Ramakrishnan, S.; Wunderlich, R.; Basu, A.; Degnan, B. A learning-enabled neuron array IC based upon transistor channel models of biological phenomena. IEEE Trans. Biomed. Circuits Syst. 2012, 7, 71–81. [Google Scholar] [CrossRef] [PubMed]

- Gomes, J.G.R.C.; Petraglia, A.; Mitra, S.K. Sensitivity analysis of multilayer perceptrons applied to focal-plane image compression. IET Circuits Devices Syst. 2007, 1, 79–86. [Google Scholar] [CrossRef]

- Indiveri, G. Neuromorphic Selective Attention Systems. In Proceedings of the International Symposium on Circuits and Systems, Bangkok, Thailand, 25–28 May 2003; Volume III, pp. 770–773. [Google Scholar]

- Izak, R.; Scarbata, G.; Paschke, P. Sound source localization with an integrate-and-fire neural system. In Proceedings of the Seventh International Conference on Microelectronics for Neural, Fuzzy and Bio-Inspired Systems, Granada, Spain, 9 April 1999; pp. 103–109. [Google Scholar]

- Sgrott, O.; Mosconi, D.; Perenzoni, M.; Pedretti, G.; Gonzo, L.; Stoppa, D. A 134-Pixel CMOS Sensor for Combined Time-of-Flight and Optical Triangulation 3-D Imaging. IEEE J. Solid-State Circuits 2010, 45, 1354–1364. [Google Scholar] [CrossRef]

- Koton, J.; Lahiri, A.; Herencsar, N.; Vrba, K. Current-mode precision full-wave rectifier using two WTA cells. In Proceedings of the 2011 34th International Conference on Telecommunications and Signal Processing (TSP), Budapest, Hungary, 18–20 August 2011; pp. 324–327. [Google Scholar]

- Koton, J.; Lahiri, A.; Herencsar, N.; Vrba, K. Current-Mode Dual-Phase Precision Full-Wave Rectifier Using Current-Mode Two-Cell Winner-Takes-All (WTA) Circuit. Radioengineering 2011, 20, 428–432. [Google Scholar]

- Prommee, P.; Chattrakun, K. CMOS WTA maximum and minimum circuits with their applications to analog switch and rectifiers. Microelectron. J. 2011, 42, 52–62. [Google Scholar] [CrossRef]

- Ramirez-Angulo, J.; Molinar-Solis, J.E.; Gupta, S.; Carvajal, R.G.; Lopez-Martin, A.J. A High-Swing, High-Speed CMOS WTA Using Differential Flipped Voltage Followers. IEEE Trans. Circuits Syst. II Express Briefs 2007, 54, 668–672. [Google Scholar] [CrossRef]

- Carvajal, R.G.; Ramirez-Angula, J.; Tombs, J. High-speed high-precision voltage-mode MIN/MAX circuits in CMOS technology. In Proceedings of the 2000 IEEE International Symposium on Circuits and Systems (ISCAS), Geneva, Switzerland, 28–31 May 2000; Volume 5, pp. 13–16. [Google Scholar]

- Baishnab, K.L.; Rahaman, M.; Talukdar, F. A 200 µv resolution and high speed VLSI Winner-take-all circuit for self-organising neural network. In Proceedings of the 2009 International Conference on Methods and Models in Computer Science (ICM2CS), New Delhi, India, 14–15 December 2009; pp. 1–4. [Google Scholar]

- Fish, A.; Milrud, V.; Yadid-Pecht, O. High-speed and high-precision current winner-take-all circuit. IEEE Trans. Circuits Syst. II Exp. Briefs 2005, 52, 131–135. [Google Scholar] [CrossRef]

- Indiveri, G. A Current-Mode Hysteretic Winner-take-all Network, with Excitatory and Inhibitory Coupling. Analog Integr. Circuits Signal Process. 2001, 28, 279–291. [Google Scholar] [CrossRef]

- Massari, N.; Gottardi, M. Low power WTA circuit for optical position detector. Electron. Lett. 2006, 42, 1373–1374. [Google Scholar] [CrossRef]

- Sarpeshkar, R. Ultra Low Power Bioelectronics: Fundamentals, Biomedical Applications, and Bio-Inspired Systems; Cambridge University Press: Cambridge, UK, 2010. [Google Scholar]

- Kim, M.; Twigg, C.M. Rank determination by winner-take-all circuit for rank modulation memory. IEEE Trans. Circuits Syst. II Express Briefs 2016, 63, 326–330. [Google Scholar] [CrossRef]

- Mead, C.A. Neuromorphic electronic systems. Proceeding IEEE 1990, 78, 1629–1636. [Google Scholar] [CrossRef]

- Andreou, A.G.; Boahen, K.A.; Pouliquen, P.O.; Pavasovic, A.; Jenkins, R.E.; Strohbehn, K. Current-mode subthreshold MOS circuits for analog VLSI neural systems. IEEE Trans. Neural Netw. 1991, 2, 205–213. [Google Scholar] [CrossRef] [PubMed]

- Lazzaro, J.; Ryckebush, S.; Mahowald, M.A.; Mead, C.A. Winner-take-all networks of O(N) complexity. In Advances In Neural Information Processing Systems; Touretzky, D.S., Ed.; Morgan Kaufmann: San Mateo, CA, USA, 1989; Volume 1, pp. 703–711. [Google Scholar]

- Sundararajan, G.; Winstead, C. A winner-take-all circuit with improved accuracy and tolerance to mismatch and process variations. In Proceedings of the 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS), Columbus, OH, USA, 4–7 August 2013; pp. 265–268. [Google Scholar]

- Rahiminejad, E.; Saben, M.; Lotfi, R.; Taherzadeh-Sani, M.; Nabki, F. A low-voltage high-precision time-domain winner-take-all circuit. IEEE Trans. Circuits Syst. Express Briefs 2020, 67, 4–8. [Google Scholar] [CrossRef]

- Sekerkiran, B.; Cilingiroglu, U. Improving the resolution of Lazzaro winner-take-all circuit. In Proceedings of the International Conference on Neural Networks (ICNN’97), Houston, TX, USA, 12 June 1997; Volume 2, pp. 1005–1008. [Google Scholar]

- Benjamin, B.V.; Smith, R.L.; Boahen, K.A. An Analytical MOS Device Model with Mismatch and Temperature Variation for Subthreshold Circuits. IEEE Trans. Circuits Syst. II Express Briefs 2023, 70, 1826–1830. [Google Scholar] [CrossRef]

- Marinov, C.A.; Costea, R.L. Designing a Winner–Loser Gap for WTA in Subthreshold. Resolution Performance Revisited. Circuits Syst. Signal Process. 2022, 41, 7145–7171. [Google Scholar] [CrossRef]

- Costea, R.L. Checking Over the Separation Performance for Winner Take All in Subthreshold Regime. In Proceedings of the 2022 International Symposium on Electronics and Telecommunications (ISETC), Timisoara, Romania, 10–11 November 2022; pp. 1–4. [Google Scholar] [CrossRef]

- Tsividis, Y. Mixed Analog Digital VLSI Devices and Technology; World Scientific: Singapore, 2002. [Google Scholar]

- Costea, R.L.; Marinov, C.A. A Consistent Model for Lazzaro Winner-Take-All Circuit With Invariant Subthreshold Behavior. IEEE Trans. Neural Netw. Learn. Syst. 2016, 27, 2375–2385. [Google Scholar] [CrossRef] [PubMed]

Disclaimer/Publisher’s Note: The statements, opinions and data contained in all publications are solely those of the individual author(s) and contributor(s) and not of MDPI and/or the editor(s). MDPI and/or the editor(s) disclaim responsibility for any injury to people or property resulting from any ideas, methods, instructions or products referred to in the content. |

© 2023 by the author. Licensee MDPI, Basel, Switzerland. This article is an open access article distributed under the terms and conditions of the Creative Commons Attribution (CC BY) license (https://creativecommons.org/licenses/by/4.0/).